# 8-BIT CMOS VIDEO DAC

IDT75C18

#### **FEATURES:**

- Graphics-ready

- Pin- and function-compatible with TRW TDC1018

- · 8 bits, 1/2 LSB linearity

- 70, 100, 125MHz models available

- · ECL-compatible inputs

- Low power dissipation < 400mW</li>

- Power supply noise rejection > 50dB

- · Registered data and video controls

- Differential current outputs

- Flexible video controls

- Inherently low glitch energy

- Multiplying mode capability

- Single 5V power supply

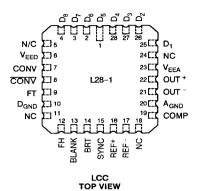

- Available in 24-pin hermetic DIP, 24-pin plastic DIP and 28-pin LCC

- · Military product is compliant to MIL-STD-883, Class B

## DESCRIPTION:

The IDT75C18 is a 70/100/125 MegaSample per Second (MSPS), 8-bit Digital to Analog Converter. It can directly drive a doubly terminated 750 load to levels compatible with RS-343A. Four special controls for blanking, synchronization and highlighting allow the device to be used in typical video applications with no extra components

The IDT75C18 is built using IDT's high-performance CEMOS <sup>™</sup> process. Innovative design methods, which include on-chip data registers and precise matching of propagation delays, as well as an improved segmenting/decoding architecture, significantly reduce glitch energy. The IDT75C18 offers high-performance and low power in a 24-pin hermetic DIP, 24-pin plastic DIP or 28-pin LCC.

The IDT75C18 is pin- and function-compatible with the TRW TDC1018, with the advantage of low power due to CMOS processing. Besides providing higher reliability by running cooler, power supply requirements are reduced. Another advantage of the lower power dissipation is that this part may be packaged in a space-saving, cost-effective, 0.3-inch plastic package.

The IDT75C18 military DAC is manufactured in compliance with the latest revision of MIL-STD-883, Class B, making it ideally suited to military temperature applications demanding the highest level of performance and reliability.

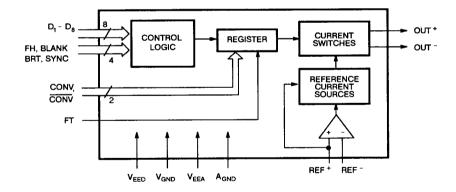

## **FUNCTIONAL BLOCK DIAGRAM**

CEMOS is a trademark of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**DECEMBER 1987**

© 1987 Integrated Device Technology, Inc.

11-1

DSC-5000/-

#### PIN CONFIGURATIONS

DIP TOP VIEW

## **FUNCTIONAL DESCRIPTION** GENERAL INFORMATION

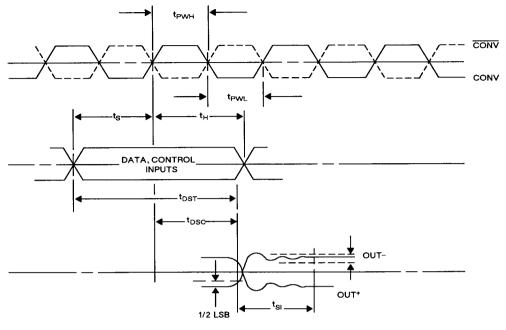

The IDT75C18 output current is proportional to the product of the digital input data and the analog reference current. All the digital inputs, data and control are compatible with standard ECL logic levels. The IDT75C18 is normally operated synchronously with data being latched by the rising edge of the convert clock, CONV. FT, the feedthrough control input, determines the operating mode. When FT is LOW, the part operates in the synchronous mode and the low-to-high transition of the convert clock, CONV, latches data and control values into internal D-type registers. The registered values are then decoded and presented to switched current sinks which produce the appropriate analog output values. When FT is HIGH, the part operates asynchronously and the digital inputs are not latched. The analog output, then, changes in response to the digital inputs without regard to clock. FT is the only asynchronous input and is typically tied to the appropriate DC level.

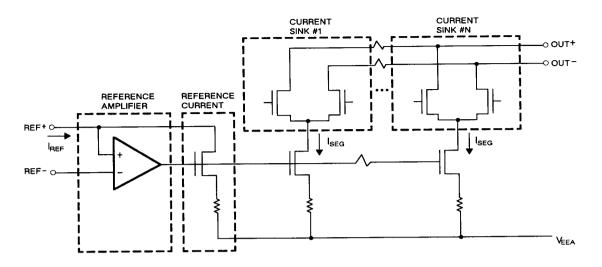

The IDT75C18 uses a 6x2 segmented DAC approach where the six MSBs of the input data are decoded into a parallel "Thermometer" code which produces sixty-four "coarse" output levels. The remaining two LSBs of the input data drive three binary weighted current switches with a total contribution of one-sixty-fourth of full scale. The MSB and LSB currents are summed at the output to produce 256 analog levels.

SYNC, BLANK, FH (Force High) and BRT (BRighT) are special control inputs which drive appropriately weighted current switches. These currents are summed at the output with the level produced by the data inputs to allow for specific levels required by video applications such as the sync pulses and the blanking levels.

#### POWER CONSIDERATIONS

The IDT75C18 operates from separate analog and digital supplies to provide the highest noise immunity on the analog output to digital switching spikes. All power and ground pins must be connected.

#### REFERENCE CONSIDERATIONS

The IDT75C18 has two reference inputs, REF+ and REF-, which are simply the non-inverting and inverting inputs to an internal buffer amplifier. The output of this amplifier serves as the reference for the transistors in the DAC. The feedback loop internally includes current sources which are identical to the current sink transistors, guaranteeing that the reference current will be precisely mirrored in the DAC.

Since the output currents are proportional to the digital data and the reference current, the full-scale output current may be adjusted over a limited range by varying the reference current. In the same vein, the stability of the output depends strongly on the stability of the reference. The reference current is normally applied to REF+, while REF - is usually connected to a negative reference through a resistor equal to the effective impedance seen on REF+.

Through careful design of the reference amplifier, no external compensation capacitor is required and the COMP pin should be left unconnected.

## CONTROLS

The IDT75C18 has four special control inputs: SYNC, BLANK, FH (Force High) and BRT (BRighT), as well as FT (Feed Through control). Typically, the IDT75C18 is operated in the synchronous mode which ensures the lowest output noise. When FT is forced HIGH, the input registers pass the data and control information through without latching, allowing the analog output to change asynchronously.

In the synchronous mode, the control inputs are registered by the rising edge of CONV in the same manner as the data inputs. The controls, like the data, must be stable for a set-up time (ts) before, and a hold time (t<sub>H</sub>) after, the rising edge of CONV. In the asynchronous mode, only the minimum pulse widths are relevant.

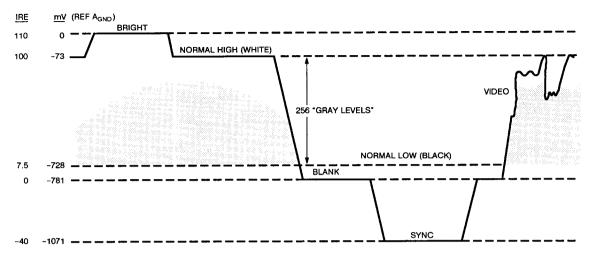

The video controls produce specific output levels which are used for frame synchronization, horizontal blanking, etc. as described in various standards such as RS-343A. The effect of these controls on the analog output is shown below. The internal logic simplifies the use of the controls in video applications. BLANK, SYNC and FH override the data inputs. SYNC overrides all other inputs and produces a full negative level. FH drives the analog output to full-scale producing a reference white level. The BRT control creates a "whiter than white" level by adding 10% of full-scale to the present output value.

## **VIDEO CONTROL OUTPUT VALUES**(4)

| DESCRIPTION | SYNC | BLANK | FH | BRT | DATA | OUT-(mA)(1) | OUT-(V)(2) | OUT-(IRE)(3) |

|-------------|------|-------|----|-----|------|-------------|------------|--------------|

| Sync        | 1    | ×     | Х  | Х   | Х    | 28.57       | -1.071     | -40.0        |

| Blank       | 0    | 1     | Х  | Х   | х    | 20.83       | -0.781     | 0.0          |

| 10% White   | 0    | 0     | 1  | 1   | х    | 0.00        | 0.00       | 110.0        |

| White       | 0    | 0     | 1  | 0   | Х    | 1.95        | -0.073     | 100.0        |

| Black       | 0    | 0     | 0  | 0   | 00   | 19.40       | -0.728     | 7.5          |

| White       | 0    | 0     | 0  | 0   | FF   | 1.95        | -0.073     | 100.0        |

| 10% Black   | 0    | 0     | 0  | 1   | 00   | 17.44       | -0.654     | 17.5         |

| 10% White   | 0    | 0     | 0  | 1   | FF   | 0.00        | 0.00       | 110.0        |

#### NOTES:

- 1. OUT\* is complementary to OUT\*. Current is specified as conventional current when flowing into the device. I<sub>OUT+</sub> = 28.57 I<sub>OUT+</sub>.

- 2. Voltage produced when driving the standard load configuration (37.5 ohms). See Figure 4.

- 3. 140 IRE units = 1.00V

- 4. RS-343A tolerance on all control values is assumed.

#### **DATA INPUTS**

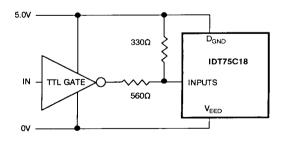

The inputs of the IDT75C18 are single ended, ECL-compatible. Internal pull down resistors force unconnected pins to a logic LOW level.

In the synchronous mode (FT is LOW), the data inputs are registered by the rising edge of CONV. The data inputs must be stable for a set-up time ( $t_{\rm S}$ ) before, and a hold time ( $t_{\rm H}$ ) after, the rising edge of CONV. In the asynchronous mode (FT is HIGH), the input registers are disabled and only the minimum pulse widths are relevant. In this mode, the analog output changes asynchronously in response to the input data.

| SYMBOL                           | FUNCTION         |

|----------------------------------|------------------|

| D <sub>1</sub>                   | Data Bit 1 (MSB) |

| D <sub>2</sub><br>D <sub>3</sub> | •                |

| D₄<br>Da                         | •                |

| D₅<br>D₅                         | •                |

| D <sub>7</sub><br>D <sub>8</sub> | Data Bit 8 (LSB) |

The inputs of the IDT75C18 are voltage comparators with the threshold level set to approximately –1.27V, ensuring the correct logic state when driven by standard ECL outputs. It is possible to overdrive the inputs without harming the device, allowing a direct interface to CMOS logic. In general, the input signals will correctly drive the IDT75C18 as long as they remain between  $V_{\rm EEA}$  and  $A_{\rm GND},\,D_{\rm GND}$  and meet the  $V_{\rm IL}$  and  $V_{\rm IH}$  specifications.

The diagram below shows a simple two resistor level shifter which allows the IDT75C18 to be driven from TTL signals.

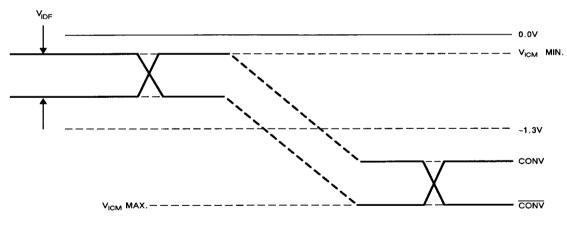

### CLOCK INPUT CONV

The clock input to the IDT75C18 (CONV) is a differential ECL-compatible input. This signal may be driven single ended by connecting  $\overline{\text{CONV}}$  to a suitable bias voltage (VBB) which determines the switching threshold of CONV.

#### ANALOG OUTPUTS

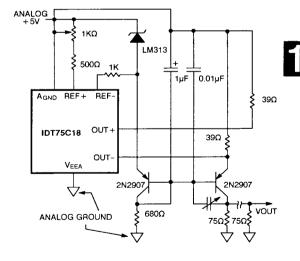

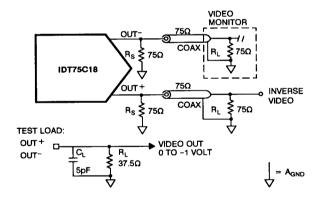

The two analog outputs of the IDT75C18 are high impedance complementary current sinks which are capable of driving a doubly terminated 75 ohm load to standard video levels. The output voltage will be the product of the output current and the effective load impedance and will usually be between 0 and -1V when the  $V_{\rm EE} = -5.2V$ . The outputs sink current from AcND, so that in the positive supply case (interfacing to CMOS or TTL), the output voltage swings between +5V and +4V. In AC coupled applications, this DC bias is unimportant. Shown below is a simple circuit which references the output voltage to the most negative supply.

## ABSOLUTE MAXIMUM RATINGS (1)

| SYMBOL                                       | OL RATING                    |                         | UNIT |  |  |  |

|----------------------------------------------|------------------------------|-------------------------|------|--|--|--|

| POWER SUPPLIES                               |                              |                         |      |  |  |  |

| V <sub>EED</sub>                             | Measured to D <sub>GND</sub> | -7.0 to +0.05           | ٧    |  |  |  |

| V <sub>EEA</sub>                             | Measured to D <sub>GND</sub> | -7.0 to +0.05           | >    |  |  |  |

| A <sub>GND</sub>                             | Measured to D <sub>GND</sub> | -0.5 to +0.5            | ٧    |  |  |  |

| INPUT VOLTAGES                               |                              |                         |      |  |  |  |

| CONV, Data<br>& Controls                     | Measured to D <sub>GND</sub> | V <sub>EED</sub> to 0.5 | ٧    |  |  |  |

| REF Input,<br>Applied Voltage <sup>(2)</sup> | Measured to A <sub>GND</sub> | V <sub>EEA</sub> to 0.5 | ٧    |  |  |  |

| REF Input,                                   | REF +                        | 6.0                     | mA   |  |  |  |

| Applied Current (3,4)                        | REF-                         | 0.5                     | mA   |  |  |  |

| OUTPUT                                       |                              |                         |      |  |  |  |

| Analog Output,<br>Applied Voltage (2)        | Measured to A <sub>GND</sub> | -2.0 to +0.4            | V    |  |  |  |

| Analog Output,<br>Applied Current (3,4)      |                              | 50                      | mA   |  |  |  |

| Short<br>Circuit Duration                    |                              | Unlimited               |      |  |  |  |

| TEMPERATURE                                  |                              |                         |      |  |  |  |

| Operating,                                   | Military                     | -55 to +125             | °C   |  |  |  |

| Ambient                                      | Commercial                   | 0 to +70                | °c   |  |  |  |

| Storage                                      | Military                     | -65 to +150             | °C   |  |  |  |

| Storage                                      | Commercial                   | -55 to +125             | °C   |  |  |  |

#### NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Absolute Maximum Ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- Current is specified as conventional current when flowing into the device.

## **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL                    | PARAMET                                   | ER                           | MIN.         | TYP.  | MAX.         | UNIT     |

|---------------------------|-------------------------------------------|------------------------------|--------------|-------|--------------|----------|

| V <sub>EED</sub>          | Digital Supply<br>(REF D <sub>GND</sub> ) | Voltage                      | -4.9         | -5.2  | -5.5         | v        |

| V <sub>EEA</sub>          | Analog Supply<br>(REF A <sub>GND</sub> )  | Voltage                      | -4.9         | -5.2  | -5.5         | v        |

| V <sub>AGND</sub>         | Analog Ground<br>Voltage (REF D           |                              | -0.1         | 0     | +0.1         | V        |

| V <sub>EEA-</sub><br>VEED | Supply Voltage<br>Differential            | •                            | -0.1         | 0     | +0.1         | v        |

| V <sub>ICM</sub>          | CONV, Common<br>Mode Range                |                              | -0.5         | _     | -2.5         | ٧        |

| V <sub>IDF</sub>          | CONV, Differential<br>Range               |                              | 0.4          | -     | 1.2          | >        |

| V <sub>IL</sub>           | Input Voltage,<br>Logic LOW               |                              | -1.49        |       | _            | v        |

| V <sub>iH</sub>           | Input Voltage,<br>Logic HIGH              |                              | _            |       | -1.045       | ٧        |

| I <sub>REF</sub>          | Reference C<br>Video Sto<br>8-Bit Lin.    | urrent,<br>i. <sup>(1)</sup> | 1.059<br>1.0 | 1,115 | 1.171<br>1.3 | mA<br>mA |

| TA                        | Ambient                                   | MIL.                         | -55          | -     | + 125        | °C       |

| '^                        | Temperature                               | COM'L.                       | 0            | _     | +70          | °c       |

#### NOTE:

Minimum and maximum values allowed by ±5% variation given in RS-343A and RS-170 after initial gain correction of device.

## DC ELECTRICAL CHARACTERISTICS

Specified over the Recommended Operating Conditions unless otherwise stated.

| SYMBOL                                 | PARAMETERS                                    | TEST CONDITIONS                                           | MIN.         | MAX. | UNIT |

|----------------------------------------|-----------------------------------------------|-----------------------------------------------------------|--------------|------|------|

| I <sub>EEA</sub> +<br>I <sub>EED</sub> | Supply Current                                | V <sub>EEA</sub> = V <sub>EED</sub> = Max.,(1)Static      | _            | 125  | mA   |

| C <sub>REF</sub>                       | Equivalent Input C,<br>REF (+), REF (-)       |                                                           | <del>-</del> | 5    | pF   |

| Cı                                     | Input Capacitance,<br>Data & Controls         |                                                           | -            | 5    | pF   |

| V <sub>OCP</sub>                       | Compliance Voltage,<br>+ Output               |                                                           | -1.2         | +0.1 | V    |

| V <sub>OCN</sub>                       | Compliance Voltage, -Output                   |                                                           | -1.2         | +0.1 | v    |

| Ro                                     | Equivalent Out R                              |                                                           | 20           | -    | kΩ   |

| Co                                     | Equivalent Out C                              |                                                           |              | 20   | pF   |

| I <sub>OP</sub>                        | Max. I, + Output                              | V <sub>EEA</sub> = Typ., SYNC = BLANK = 0<br>FH = BRT = 1 | 30           | _    | mA   |

| I <sub>ON</sub>                        | Max. I, -Output                               | V <sub>EEA</sub> = Typ.,SYNC = 1                          | 30           | _    | mA   |

| 4∟                                     | Input Current, Logic<br>LOW, Data & Controls  | $V_{EED} = Max.; V_1 = -1.40V$                            | _            | 200  | μA   |

| I <sub>H-t</sub>                       | Input Current, Logic<br>HIGH, Data & Controls | V <sub>EED</sub> = Max.; V <sub>I</sub> = -1.00V          | _            | 200  | μA   |

| l <sub>ic</sub>                        | Input Current, CONV                           | V <sub>EED</sub> = Max.; -2.5 < V <sub>1</sub> < -0.5     |              | 50   | μA   |

#### NOTE:

#### **AC ELECTRICAL CHARACTERISTICS**

Specified over the Recommended Operating Conditions unless otherwise stated.

| SYMBOL           | PARAMETERS                  | TEST CONDITIONS                                                           | IDT75<br>MIN. | C18x70<br>MAX. | IDT75C<br>MIN. | 18x100<br>MAX. | IDT75C<br>MIN. | 18x125<br>MAX. | UNIT           |

|------------------|-----------------------------|---------------------------------------------------------------------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Fs               | Max. Conversion Rate        | V <sub>EEA</sub> , V <sub>EED</sub> = Min.                                | T -           | 70             | _              | 100            | -              | 125            | MHz            |

| t <sub>PWL</sub> | CONV LOW Time               | V <sub>EEA</sub> , V <sub>EED</sub> = Min.                                | 6             |                | 5              |                | 4              | _ ]            | ns             |

| tpWH             | CONV HIGH Time              | V <sub>EEA</sub> , V <sub>EED</sub> = Min.                                | 6             | _              | 5              | -              | 4              | -              | ns             |

| ts               | Set-up Time, Data & Control | V <sub>EEA</sub> , V <sub>EED</sub> = Min.                                | 8             | _              | 6              | -              | 5              | -              | ns             |

| t <sub>H</sub>   | Hold Time, Data & Control   | V <sub>EEA</sub> , V <sub>EED</sub> = Min.                                | 5             | -              | 1              | -              | 0              | _              | ns             |

| t <sub>DSC</sub> | CONV to OUT Delay           | V <sub>EEA</sub> , V <sub>EED</sub> = Min. FT = 0                         | _             | 14             | _              | 10             | -              | 8              | ns             |

| t <sub>DST</sub> | DATA to OUT Delay           | V <sub>EEA</sub> , V <sub>EED</sub> = Min. FT = 1                         | _             | 20             | -              | 16             |                | 13             | ns             |

| t <sub>SI</sub>  | Current Setting Time        | V <sub>EEA</sub> , V <sub>EED</sub> = Min. FT = 0<br>0.2%<br>0.8%<br>3.2% | -<br>-<br>-   | -<br>-<br>-    | -<br>-<br>-    | -<br>-         | -              | -              | ns<br>ns<br>ns |

| t <sub>RI</sub>  | Current Rise Time           | 10% to 90% of Full Scale                                                  |               | 3.0            | -              | 2.1            | -              | 1.7            | ns             |

<sup>1.</sup> Worst case for all Data and Control States. No termination on I<sub>OUT</sub>+or I<sub>OUT</sub>-.

# SYSTEM PERFORMANCE CHARACTERISTICS

Specified over the Recommended Operating Conditions unless otherwise stated.

| SYMBOL          | PARAMETERS TEST CONDITIONS   |                                                                              | MIN. | MAX.   | UNIT   |  |

|-----------------|------------------------------|------------------------------------------------------------------------------|------|--------|--------|--|

| ELI             | Linearity Error Integral     | V <sub>EEA</sub> , V <sub>EED</sub> , I <sub>REF</sub> = Typ.                | _    | 0.2    | %FS    |  |

| ELD             | Linearity Error Differential | V <sub>EEA</sub> , V <sub>EED</sub> , I <sub>REF</sub> = Typ.                |      | 0.2    | %FS    |  |

| IOF             | Output Offset I              | V <sub>EEA</sub> . V <sub>EED</sub> = Max. SYNC = BLANK = 0,<br>FH = BRT = 1 | -    | ± 10   | μА     |  |

| EG              | Abs. Gain Error              | V <sub>EEA</sub> , V <sub>EED</sub> , I <sub>REF</sub> = Typ.                |      | ±5     | %FS    |  |

| TCG             | Gain Error Tempco            |                                                                              | _    | ±0.024 | %FS/°C |  |

| BWR             | Ref. Bandwidth -3dB          | $\Delta V_{REF} = 1mV$                                                       | 1    |        | MHz    |  |

| DP              | Differential Phase           | 4 x NTSC                                                                     | _    | 1.0    | Deg.   |  |

| DG              | Differential Gain            | 4 x NTSC                                                                     |      | 2.0    | %      |  |

|                 |                              | V <sub>EEA</sub> , V <sub>EED</sub> , I <sub>REF</sub> = Typ. <sup>(1)</sup> | _    | 45     | dB     |  |

| PSRR            | Power Supp. Rej. Ratio       | V <sub>EEA</sub> , V <sub>EED</sub> , I <sub>REF</sub> = Typ. <sup>(2)</sup> | _    | 55     | dB     |  |

| PSS             | Power Supp. Sensitivity      | V <sub>EEA</sub> , V <sub>EED</sub> , I <sub>REF</sub> = Typ.                | -    | 120    | μV/V   |  |

| GC              | Peak Glitch Charge           | Registered Mode Typ. (3, 4)                                                  |      | 800    | fc     |  |

| GI              | Peak Glitch Current          | Registered Mode                                                              | _    | 1.2    | mA     |  |

| GE              | Peak Glitch Energy           | Registered Mode Typ. (4)                                                     | _    | 30     | pV-Sec |  |

| FT <sub>C</sub> | Clock Feedthrough            | Data Constant (5)                                                            | _    | -50    | dB     |  |

| FT <sub>D</sub> | Data Feedthrough             | Clock Constant (5)                                                           |      | -50    | dB     |  |

#### NOTES:

- 1. 20kHz,  $\pm$ 0.3V ripple superimposed on  $V_{\text{EEA}}$ ,  $V_{\text{EED}}$ ; dB relative to full gray scale.

- 2. 60Hz,  $\pm 0.3$ V ripple superimposed on  $V_{EEA}$ ,  $V_{EED}$ ; dB relative to full gray scale.

- 3. f<sub>Coulombs</sub> = microamps x nanoseconds.

- 4.  $37.5\Omega$  load. Because glitches tend to be symmetric, average glitch area approaches zero.

- 5. dB relative to full gray scale, 250MHz bandwidth limit.

Figure 1. Timing Diagram

Figure 2. CONVert, CONVert Switching Levels

Figure 3. Equivalent Output Circuit

Figure 4. Standard Load Configuration

Figure 5. Video Output Waveform for Out- and Standard Load Configuration

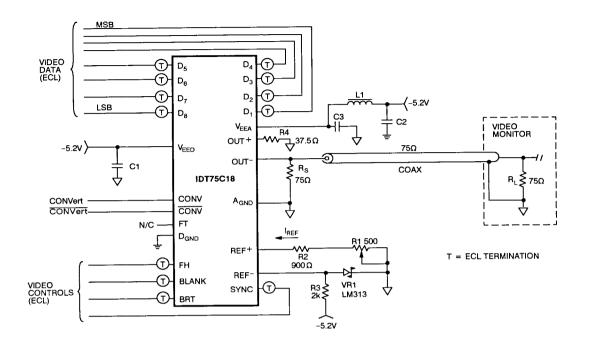

# **PARTS LIST**

| RESISTORS      |                                                                     |                        |               |  |

|----------------|---------------------------------------------------------------------|------------------------|---------------|--|

| R1             | 1kΩ                                                                 | Pot                    | 10 Turn       |  |

| R2             | 900Ω                                                                | 1/8W                   | 1% Metal Film |  |

| R3             | 2.00kΩ                                                              | 1/8W                   | 1% Metal Film |  |

| R4             | 37.5Ω                                                               | 1/8W                   | 1% Metal Film |  |

| CAPACITORS     |                                                                     |                        |               |  |

| C1-C3          | 0.1µF                                                               | 50V                    | Ceramic disc  |  |

| INTEGRATED CII | RCUITS                                                              |                        |               |  |

| U1             | IDT75C18                                                            | IDT75C18 D/A Converter |               |  |

| VOLTAGE REFER  | RENCES                                                              |                        |               |  |

| VR1            | LM113 or LM313                                                      | Bandga                 | p Reference   |  |

| INDUCTORS      |                                                                     |                        |               |  |

| L1             | Ferrite Bead Shield Inductor Fair-Rite<br>P/N 2743001112 or Similar |                        |               |  |

Figure 6. Typical Interface Circuit

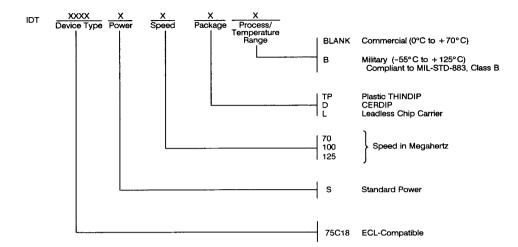

## ORDERING INFORMATION