## **High-speed FSK modem receiver**

**NE5081**

### **DESCRIPTION**

The NE5081 is the receiver chip of a two-chip set designed to operate as an FSK modem (the NE5080 is the transmitter chip). The chips are compatible with the IEEE 802.4 standard for a "Single-Channel Phase-Continuous-FSK Token Bus." The specifications given in this data sheet are those guaranteed when the receiver is tuned to the frequencies given in the 802 standard. However, the receiver will work at other frequencies.

### **FEATURES**

- Meets IEEE 802.4 standard

- Data rates to several Megabaud

- Half- or full-duplex operation

- Low bit rate error (10<sup>-12</sup> typical)

### **APPLICATIONS**

- Local Area Networks

- Point-to-point communications

- Factory automation

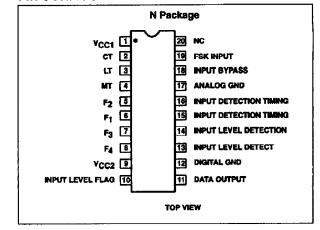

### **PIN CONFIGURATION**

- Process control

- Office automation

### **ORDERING INFORMATION**

| DESCRIPTION                               | TEMPERATURE RANGE | ORDER CODE | DWG # |

|-------------------------------------------|-------------------|------------|-------|

| 20-Pin Plastic Dual In-Line Package (DIP) | 0°C to +70°C      | NE5081N    | 0408B |

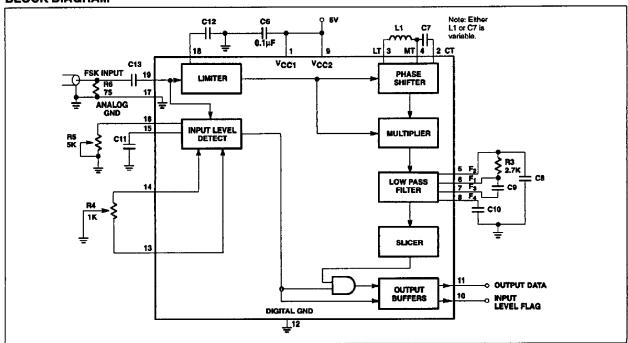

### **BLOCK DIAGRAM**

# High-speed FSK modem receiver

NE5081

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C

| SYMBOL                               | PARAMETER                                                                            | RATING                   | UNIT |  |

|--------------------------------------|--------------------------------------------------------------------------------------|--------------------------|------|--|

| V <sub>CC1</sub><br>V <sub>CC2</sub> | Supply voltage                                                                       | +6                       | V    |  |

| $V_{IN}$                             | Input voltage range                                                                  | -0.3 to +V <sub>CC</sub> | v    |  |

| IDO                                  | Output (Data, Level detect) Max sink current                                         | 20                       | mA   |  |

| PD                                   | Maximum power dissipation, T <sub>A</sub> = 25°C, (still-air) <sup>1</sup> N package | 1690                     | mW   |  |

| TA                                   | Operating temperature range                                                          | 0 to +70                 | °C   |  |

| T <sub>STG</sub>                     | Storage temperature range                                                            | -65 to +150              | °C   |  |

| TSOLD                                | Lead soldering temperature (10 sec. max)                                             | 300                      | °C   |  |

|                                      | Max differential voltage between analog and digital grounds                          | 100                      | mV   |  |

### NOTE:

### DC ELECTRICAL CHARACTERISTICS

$V_{CC1,2} = 4.75-5.25V$ . External LC circuit tuned to 5MHz. Input level detect set at 16mV<sub>RMS</sub>,  $T_A = 0^{\circ}C + 70^{\circ}C$ .

| SYMBOL           | PARAMETER Logic Low Frequency | TEST COMPITIONS                                                                                                      | LIMITS |                                                  |                  | ·                 |

|------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------|------------------|-------------------|

|                  |                               | TEST CONDITIONS                                                                                                      | Min    | Тур                                              | Max              | UNIT              |

| fo               |                               | External LC tuned to 5MHz                                                                                            | 3.67   | 3.75                                             | 3.83             | MHz               |

| f <sub>1</sub>   | Logic High Frequency          | External LC tuned to 5MHz                                                                                            | 6.17   | 6.25                                             | 6.33             | MHz               |

| IN <sub>DL</sub> | Minimum Input Detect Level    | Minimum input level that is detected as carrier (See Note 2 in General Description)                                  | 5      |                                                  | 50               | mV <sub>RMS</sub> |

|                  | Logic Levels:                 |                                                                                                                      | 1      | <del>                                     </del> |                  | <u> </u>          |

| VOL              | Data Output                   | I <sub>OL</sub> = 4.0mA V <sub>IN</sub> > 16mV <sub>RMS</sub> Freq = f <sub>0</sub>                                  |        |                                                  | 0.4              | Ιv                |

| VoH              | Data Output                   | I <sub>OH</sub> = -400μA V <sub>IN</sub> > 16mV <sub>RMS</sub> Freq = f <sub>1</sub>                                 | 2.4    | 1                                                |                  | V                 |

| VOH              | Data Output                   | I <sub>OH</sub> = -400μA V <sub>IN</sub> < 5mV <sub>RMS</sub> Freq = f <sub>O</sub>                                  | 2.4    | }                                                |                  | l v               |

| $v_{OL}$         | Input Detect Flag             | I <sub>OL</sub> = 4.0mA V <sub>IN</sub> = 0V <sub>RMS</sub>                                                          |        | ł                                                | 0.4              | l v               |

| VOH              |                               | I <sub>OH</sub> = -400μΑ V <sub>IN</sub> > 16mV                                                                      | 2.4    |                                                  |                  | l v               |

| lcc              | Supply Current                | $V_{CC} = 5.25V (V_{CC1} \text{ connected to } V_{CC2})$<br>$V_{IN} = 1.0V_{RMS} \text{ Freq} = I_1 \text{ or } I_0$ |        |                                                  | 50               | mA                |

| BER              | Bit Error Rate                | Input Signal > 16mV <sub>RMS</sub> maximum in-band noise = 1.6mV <sub>RMS</sub>                                      |        | 10-12                                            | 10 <sup>-9</sup> |                   |

## AC ELECTRICAL CHARACTERISTICS (AN195, Figure 5 with a 100KHz 1V<sub>P-P</sub>)

| SYMBOL         | PARAMETER      | то                         | FROM              | TEST CONDITIONS | LIMITS |      |     |      |

|----------------|----------------|----------------------------|-------------------|-----------------|--------|------|-----|------|

|                |                |                            |                   |                 | Min    | Тур  | Max | UNIT |

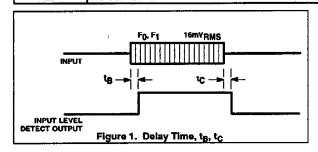

| t <sub>B</sub> | Delay Time     | Input Level<br>Detect Flag | Input On          | Figure 1        |        | 0.05 | 1   | με   |

| tc             | Delay Time     | input Level<br>Detect Flag | Input Off         | Figure 1        | 0.5    | 1.5  | 2.5 | μs   |

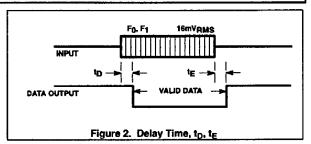

| t <sub>D</sub> | Delay Time     | Output<br>Enabled          | Input On          | Figure 2        |        |      | 2   | μs   |

| ţΕ             | Delay Time     | Output<br>Disabled         | input Off         | Figure 2        | 0.5    | 1.5  | 2.5 | μs   |

|                | Required Delay | Carrier<br>Turn Off        | Valid Data<br>End |                 | 2      |      |     | μs   |

Derate above 25°C as follows:

N package at 13.5mW/°C.

### High-speed FSK modem receiver

NE5081

### **GENERAL DESCRIPTION**

The NE5081 will accept an FSK-encoded signal and provide the demodulated digital data at the output. It is optimized to work at frequencies specified in IEEE 802.4—Token-Passing Single-Channel Phase-Continuous-FSK Bus—(i.e., 3.75MHz and 6.25MHz). However, it will work at other frequencies.

Its normal acceptable input signal level range is from 16mV $_{RMS}$  to 1V $_{RMS}$ . This can be adjusted. $^2$

The receiver will yield an undetected "Bit Error Rate" of  $10^{-9}$  or lower when receiving signals with a 20dB signal-to-noise ratio. It has a maximum output Jitter of  $\pm$  40ns.<sup>3</sup>

#### NOTES

The receiver can be tuned to accept different frequencies by adjustment of the LC circuit shown in Figure 7. However, the external

components have been optimized for 3.75MHz and 6.25MHz. See "Determining Component Values" for use at other frequencies.

2. Input Level Detect

This is a method of turning off the output of the receiver when the input signal falls below an acceptable level. This level is adjustable within the range given in the electrical specification section. The purpose of this function is to minimize the effect of noise on receiver performance and to indicate when there is an acceptable signal present at the input. All specifications given in this data sheet are with the input level detection set at 16mV<sub>PMS</sub>.

3. Jitter (Definition)

This is a measure of the ability of the receiver to accurately reproduce the timing of its FSK-coded digital input. The spec indicates the error band in the timing of a logic level change.

### **FUNCTION TABLE**

| PIN       | FUNCTION                                                                                                                                                                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | V <sub>CC1</sub> : Should be connected to the 5V supply and Pin 9.                                                                                                                                                                       |

| 2         | CT: One end of an external capacitor that is used to tune the receiver.                                                                                                                                                                  |

| 3         | LT: One end of an indicator that is used to tune the receiver.                                                                                                                                                                           |

| 4         | MT: The junction of the capacitor and inductor used for tuning the receiver.                                                                                                                                                             |

| 5         | F2                                                                                                                                                                                                                                       |

| 6         | F1 Pins 5, 6, 7, 8 are used for a low-pass filter to remove carrier                                                                                                                                                                      |

| 7         | F3 harmonics from the data output.                                                                                                                                                                                                       |

| 8         | F4                                                                                                                                                                                                                                       |

| 9         | V <sub>CC2</sub> : Connect to Pin 1 (see Pin 1 function) close to the device.                                                                                                                                                            |

| 10        | Input Level Flag: This pin is used to indicate when there is a signal at the input that is greater than the level set by the input level detection circuitry. A logic high indicates an input greater than the set level.                |

| 11        | Data Output: Supplies T <sup>2</sup> L level data that corresponds to the FSK input received.                                                                                                                                            |

| 12        | Digital Ground: Should be connected to digital ground.                                                                                                                                                                                   |

| 13,<br>14 | Input Level Detect: These pins are used to set the level of input signal that the device will accept as valid.                                                                                                                           |

| . 15      | Input Detection Timing: An external capacitor between this pin and ground is used to determine the time from carrier turn-<br>off to output disable.                                                                                     |

| 16        | Input Detection Timing: Same as Pin 15, except that a resistor goes between this pin and ground. The values of the C and R depend on the carrier frequency. The values given in this data sheet are for a 5MHz carrier center frequency. |

| 17        | Analog Ground: Connect to analog ground close to the device.                                                                                                                                                                             |

| 18        | Input Bypass: A capacitor between this pin and ground is used to bypass the input bias circuitry.                                                                                                                                        |

| 19        | Input: The FSK signal from the cable goes to this pin.                                                                                                                                                                                   |

| 20        | No Connection.                                                                                                                                                                                                                           |