|                             |        |              |      |      |                 |                 | ***            |      | REVI  | SIONS              |                                                                                              |     |       |       |          |      |     |          |            |    |

|-----------------------------|--------|--------------|------|------|-----------------|-----------------|----------------|------|-------|--------------------|----------------------------------------------------------------------------------------------|-----|-------|-------|----------|------|-----|----------|------------|----|

| LTR                         |        | •            |      |      |                 | DESC            | RIPTIO         | ON   |       |                    |                                                                                              |     | С     | ATE ( | YR-MO    | -DA) |     | APP      | ROVE       | D  |

| A                           | pa     |              | 2,3, | 5,6, |                 | . Ed            |                |      |       |                    |                                                                                              |     | 9:    | 1-03  | -22      |      | м.  | Α.       | Frye       |    |

| В                           |        | d dev        |      |      |                 |                 | rmat           | upd  | late, | edi                | tori                                                                                         | al  | 9!    | 5-10  | -16      |      | М.  | Α.       | Frye       | •  |

|                             |        |              |      |      |                 |                 |                |      |       |                    |                                                                                              |     |       |       |          |      |     |          |            |    |

| REV                         |        |              |      |      |                 |                 |                |      |       |                    |                                                                                              |     |       |       | <u> </u> | Γ    | Γ   | <u> </u> | <u> </u>   |    |

| SHEET                       |        |              |      |      |                 |                 |                |      |       |                    |                                                                                              |     |       |       |          |      |     |          |            |    |

| REV                         | В      | В            | В    | В    |                 | ļ               |                |      |       |                    |                                                                                              |     |       |       |          |      |     |          |            |    |

| SHEET                       | 15     | 16           | 17   | 18   |                 |                 |                |      |       |                    |                                                                                              |     |       |       |          |      |     |          |            |    |

| REV STATU                   |        |              |      | RE   | ٧               |                 | В              | В    | В     | В                  | В                                                                                            | В   | В     | В     | В        | В    | В   | В        | В          | В  |

| 01 0112210                  |        |              |      | SHI  | EET             |                 | 1              | 2    | 3     | 4                  | 5                                                                                            | 6   | 7     | 8     | 9        | 10   | 11  | 12       | 13         | 14 |

| PMIC N/A                    |        |              |      |      | PAREI<br>narles | D BY<br>Reusing | 3              |      |       |                    | DEFENSE ELECTRONICS SUPPLY CENTER                                                            |     |       |       |          |      |     |          |            |    |

| STA<br>MICRO                | CIR    | CŲľ          | Т    |      | CKED<br>y Mon   |                 |                |      |       | DAYTON, OHIO 45444 |                                                                                              |     |       |       |          |      |     |          |            |    |

| THIS DRAWI<br>FOR U         | JSE BY | VAILA<br>ALL | BLE  |      | ROVE<br>chael F |                 |                |      |       | PRO                | MICROCIRCUIT, MEMORY, DIGITAL, CMOS,<br>PROGRAMMABLE LOGIC CELL ARRAY, MONOLITHIC<br>SILICON |     |       |       | HIC      |      |     |          |            |    |

| DEPA<br>AND AGE<br>DEPARTME |        | OF THE       |      | DRA  | WING            | APPRC<br>89-1   | OVAL E<br>1-15 | DATE |       | SIZE               |                                                                                              | CAG | E COD | E     | <u> </u> |      |     | 001      |            |    |

| AMSC                        | N/A    |              |      | REV  | ISION           | LEVEL           |                |      |       | 1 .                | 4                                                                                            |     | 726   |       |          | 55   | 62- | -oot     | <b>3</b> 8 |    |

|                             |        |              |      |      | E               | 3               |                |      |       | SHE                | ET                                                                                           | 1   |       | OF    | 1:       | 8    |     |          |            |    |

DESC FORM 193

JUL 94

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-E300-95

**■ 9004708 0014058 995 ■**

| 1 | S.C | ΛD |  |

|---|-----|----|--|

- 1.1 <u>Scope</u>. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

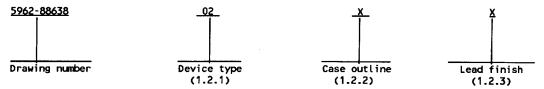

- 1.2 Part or Identifying Number (PIN). The complete PIN shall be as shown in the following example:

1.2.1 <u>Device types</u>. The device types shall identify the circuit function as follows:

| Circuit function                                                                                               | <u>Toggle_speed</u>                                                   |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| x 10, 1800 gate programmable array<br>x 10, 1800 gate programmable array<br>x 10, 1800 gate programmable array | 33 MHz<br>50 MHz<br>70 MHz<br>100 MHz                                 |

|                                                                                                                | x 10, 1800 gate programmable array x 10, 1800 gate programmable array |

1.2.2 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | <u>Descriptive designator</u> | <u>Terminals</u> | Package style            |   |

|----------------|-------------------------------|------------------|--------------------------|---|

| x              | CMGA15-PN                     | 84               | pin grid array package 1 | , |

1.2.3 <u>Lead finish</u>. The lead finish shall be as specified in MIL-STD-883 (see 3.1 herein). Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

1.3 Absolute maximum ratings.

1.4 <u>Recommended operating conditions</u>.

| Case operating temperature range (T <sub>C</sub> )         | -55°C to +125°C                      |

|------------------------------------------------------------|--------------------------------------|

| Supply voltage relative to ground range (V <sub>CC</sub> ) | 4.5 V dc minimum to 5.5 V dc maximum |

| Input voltage range (V <sub>IN</sub> )                     | 0.0 V dc to V <sub>CC</sub>          |

| Output voltage range (V <sub>OUT</sub> )                   | 0.0 V dc to VCC                      |

# 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and bulletin</u>. Unless otherwise specified, the following specification, standards, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

SPECIFICATION

MILITARY

MIL-PRF-38535 - Microcircuits, General Specification for.

1/ 84 actual pins used plus one (1) electrically not connected, locator pin = 85; not maximum listed in appendix C of MIL-M-38510.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                     | 5962-88638 |

|------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>B | SHEET 2    |

DESC FORM 193A JUL 94

9004708 0014059 821

STANDARD

MILITARY

MIL-STD-883

Test Methods and Procedures for Microelectronics.

MIL-STD-1835 - Microcircuit Case Outlines.

BULLETIN

**MILITARY**

MIL-BUL-103

- List of Standard Microcircuit Drawings (SMD's).

(Copies of the specification, standard, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-I-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-I-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-I-38535 is required to identify when the QML flow option is used.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-STD-883 (see 3.1 herein) and herein.

- 3.2.1 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

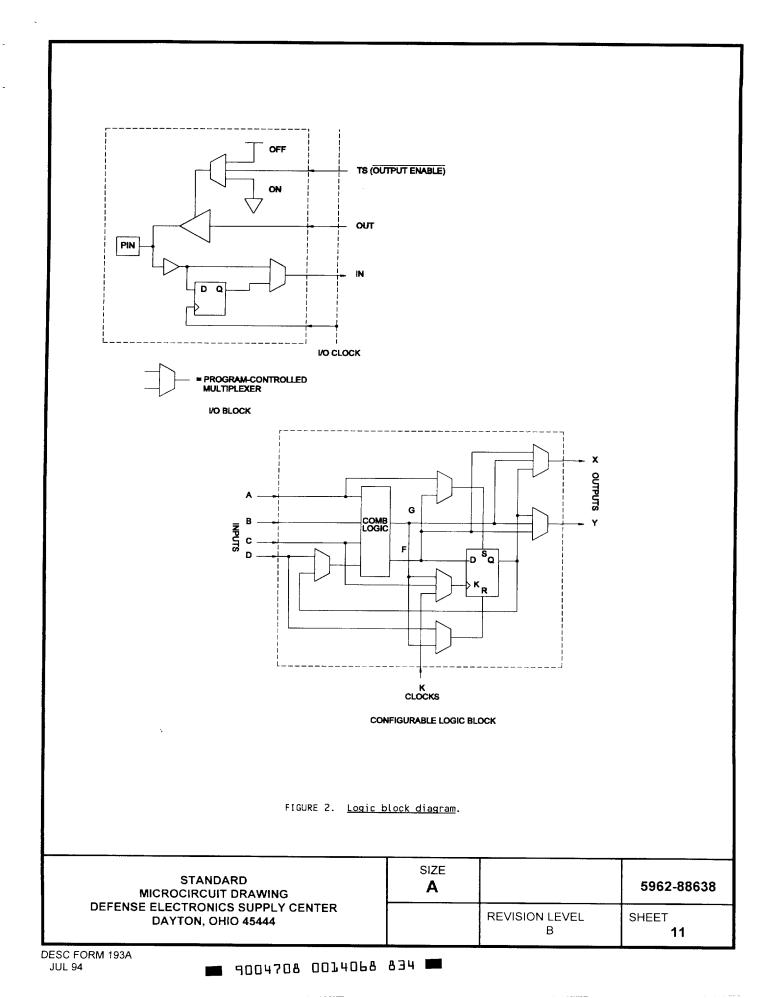

- 3.2.2 Logic block diagrams. The logic block diagram shall be as specified on figure 2.

- 3.2.3 Case outline. The case outline shall be in accordance with 1.2.2 herein.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103 (see 6.7 herein).

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7 herein). The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change</u>. Notification of change to DESC-EC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

DESC FORM 193A JUL 94

9004708 0014060 543 🚃

TABLE I. <u>Electrical performance characteristics</u>.

| Test                                                           | Symbol            | Conditions<br>4.5 V ≤ V <sub>CC</sub> ≤ 5.5<br>-55°C ≤ T <sub>C</sub> ≤ +125                                                                                             | 5 V            | Group A<br>subgroups | Device<br>type | ı                      | Limits              | Unit |

|----------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|----------------|------------------------|---------------------|------|

|                                                                |                   | -55°C ≤ T <sub>C</sub> ≤ +125<br>unless otherwise spe                                                                                                                    | j°C<br>:cified | ,                    | "              | Min                    | Max                 | 7    |

| High level output<br>voltage                                   | V <sub>ОН</sub>   | V <sub>CC</sub> = 4.5 V, I <sub>OH</sub> = -4<br>VIN = V <sub>IHC</sub> minimum,<br>V <sub>IHT</sub> minimum or V <sub>ILC</sub><br>maximum,<br>V <sub>ILt</sub> maximum |                | 1,2,3                | ALL            | 3.7                    |                     | V    |

| Low level output<br>voltage                                    | V <sub>OL</sub>   | V <sub>CC</sub> = 5.5 V, I <sub>OL</sub> = 4.<br>VIn = V <sub>IHC</sub> minimum,<br>V <sub>IHT</sub> minimum or V <sub>ILC</sub><br>maximum,<br>V <sub>ILt</sub> maximum | 0 mA,          | 1,2,3                | All            |                        | 0.4                 | V    |

| Quiescent power supply current                                 | <sup>I</sup> cco  |                                                                                                                                                                          | CMOS           | 1,2,3                | All            |                        | 10                  | 1    |

| Supply Current                                                 |                   | $V_{CC} = V_{IN} = 5.5 \text{ V},$                                                                                                                                       | TTL            |                      | i '            |                        | 15                  | mA   |

| Power-down supply<br>current                                   | I <sub>CCPD</sub> | $V_{CC} = V_{IN} = 5.5 V,$                                                                                                                                               |                | 1,2,3                | ALL            |                        | 0.5                 | mA   |

| Current                                                        | '                 | PWRDWN = 0 V                                                                                                                                                             |                | , 1                  | 1 1            | 1                      |                     |      |

| Power-down supply<br>voltage                                   | v <sub>PD</sub>   | PWRDWN = 0 V<br>see figure 3                                                                                                                                             |                | 1,2,3                | All            | 3.5                    |                     | v    |

| Input leakage<br>current                                       | IIL               | V <sub>IN</sub> = 0 V and 5.5 V,<br>V <sub>CC</sub> = 5.5 V                                                                                                              |                | 1,2,3                | All            | -10                    | +10                 | μA   |

| Output leakage<br>current                                      | <sup>I</sup> oz   | V <sub>IN</sub> = 0 V and 5.5 V,<br>V <sub>CC</sub> = 5.5 V with no l                                                                                                    | oad            | 1,2,3                | All            | -10                    | +10                 | μA   |

| High level input<br>voltage TTL                                | VIHT              |                                                                                                                                                                          |                | 1,2,3                | All            | 2                      |                     | V    |

| Low level input<br>voltage TTL                                 | V <sub>ILT</sub>  |                                                                                                                                                                          |                | 1,2,3                | All            |                        | 0.8                 | V    |

| High level input<br>voltage CMOS                               | V <sub>I HC</sub> |                                                                                                                                                                          |                | 1,2,3                | All            | 0.7<br>V <sub>CC</sub> |                     | V    |

| Low level input<br>voltage CMOS                                | VILC              |                                                                                                                                                                          |                | 1,2,3                | ALL            |                        | 0.2 V <sub>CC</sub> | ٧    |

| Input capacitance<br>except XTL1 and<br>XTL2                   | CIN               | See 4.3.1c                                                                                                                                                               |                | 4                    | All            |                        | 10                  | pF   |

| Input capacitance<br>XTL1 and XTL2                             | CIN               | See 4.3.1c                                                                                                                                                               |                | 4                    | All            |                        | 15                  | pF   |

| Output capacitance                                             | с <sub>оит</sub>  | See 4.3.1c                                                                                                                                                               |                | 4                    | All            |                        | 10                  | рF   |

| Functional test                                                | FT                | See 4.3.1d                                                                                                                                                               |                | 7,8A,8B              | All            |                        |                     |      |

| Interconnect +                                                 | t <sub>B1</sub>   | Measured on 10 columns<br>See figure 3                                                                                                                                   |                | 9,10,11              | 02             |                        | 238                 | ns   |

| t <sub>PID</sub> + t <sub>OPS</sub> + 10(t <sub>ILO</sub> )    |                   | 300 11gui C 3                                                                                                                                                            |                | L                    | 03             |                        | 178                 | 1    |

|                                                                | 1                 |                                                                                                                                                                          |                | F                    | 04             |                        | 119                 | l .  |

| Interconnect +                                                 | t <sub>B2</sub>   |                                                                                                                                                                          | <b>-</b>       | 9,10,11              | 05             | ——                     | 86                  |      |

| tpiQ                                                           | -B2               |                                                                                                                                                                          |                | Y, 10, 11            | 02             | —                      | 288<br>228          | ns   |

| <sup>t</sup> PID<br>+ 10(t <sub>ITO</sub> ) + t <sub>OPS</sub> | 1                 |                                                                                                                                                                          | [              | <u></u>              | 03             |                        | 159                 | i    |

| ,                                                              | 1 1               |                                                                                                                                                                          |                | ⊢                    | 05             | ——                     | 115                 |      |

STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                     | 5962-88638     |

|------------------|---------------------|----------------|

|                  | REVISION LEVEL<br>B | SHEET <b>4</b> |

DESC FORM 193A

JUL 94

■ 9004708 0014061 48T **■**

TABLE I. <u>Electrical performance characteristics</u> - Continued.

| Test                                                                                      | Symbol           | Conditions<br>4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V                                                                                                            | Group A<br>subgroups | Device<br>type | Liı | nits | Unit |

|-------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----|------|------|

|                                                                                           |                  | $4.5 \text{ V} \leq \text{V}_{CC} \leq 5.5 \text{ V}$<br>$-55^{\circ}\text{C} \leq \text{T}_{C} \leq +125^{\circ}\text{C}$<br>unless otherwise specified |                      |                | Min | Max  | 1    |

| Interconnect +                                                                            | t <sub>B3</sub>  | Measured on 10 columns                                                                                                                                   | 9,10,11              | 02             |     | 410  | ns   |

| t <sub>PID</sub>                                                                          |                  | See figure 3                                                                                                                                             |                      | 03             |     | 302  | 7    |

| t <sub>PID</sub><br>+ t <sub>OPS</sub> + 10(t <sub>ITO</sub> )<br>+ 10(t <sub>QLO</sub> ) | }                |                                                                                                                                                          |                      | 04             |     | 217  | 7    |

| WEO.                                                                                      | 1                | 1                                                                                                                                                        |                      | 05             |     | 172  | 1    |

| Tested on all CLBs                                                                        | t <sub>84</sub>  | See figure 3                                                                                                                                             | 9,10,11              | 02             |     | 85   | ns   |

| with t <sub>ICK</sub> +<br>interconnect +                                                 | "                |                                                                                                                                                          |                      | 03             |     | 62   | 1    |

| torn                                                                                      |                  |                                                                                                                                                          |                      | 04             |     | 42   | 7    |

| <sup>t</sup> çко<br>+ <sup>2t</sup> ILO                                                   | ļ                |                                                                                                                                                          |                      | 05             |     | 33   | 7    |

| Tested on all CLBs                                                                        | t <sub>B5</sub>  | 1                                                                                                                                                        | 9,10,11              | 02             |     | 66   | ns   |

| with t <sub>ICI</sub> +<br>interconnect +                                                 |                  |                                                                                                                                                          |                      | 03             |     | 49   |      |

| t <sub>CIO</sub>                                                                          |                  |                                                                                                                                                          |                      | 04             |     | 38   | 7    |

| <sup>‡¹t</sup> ILO                                                                        |                  |                                                                                                                                                          |                      | 05             |     | 26.5 | 1    |

| Tested on all CLBs                                                                        | t <sub>B6</sub>  | 1                                                                                                                                                        | 9,10,11              | 02             |     | 90   | ns   |

| with t <sub>ICC</sub> +<br>interconnect +                                                 | 50               |                                                                                                                                                          |                      | 03             |     | 67   | 1    |

| too                                                                                       |                  |                                                                                                                                                          |                      | 04             |     | 41   |      |

| t <sub>CCO</sub><br>+ 2(t <sub>ILO</sub> )                                                |                  |                                                                                                                                                          |                      | 05             |     | 31   | 1    |

| Interconnect +                                                                            | t <sub>B7</sub>  | Measured on 10 rows.                                                                                                                                     | 9,10,11              | 02             |     | 318  | ns   |

| <sup>t</sup> cko                                                                          | "                | See figure 3                                                                                                                                             |                      | 03             |     | 269  | 1    |

| tcko<br>+ tiHCK + tCKIH                                                                   |                  |                                                                                                                                                          |                      | 04             |     | 183  | 1    |

|                                                                                           |                  |                                                                                                                                                          |                      | 05             |     | 128  | 1    |

| 3tnin +                                                                                   | t <sub>B8</sub>  | Tested on all IOBs                                                                                                                                       | 9,10,11              | 02             |     | 274  | ns   |

| 3t <sub>PID</sub> + interconnect + t <sub>PL</sub>                                        | B0               | See figure 3                                                                                                                                             |                      | 03             |     | 204  | 1    |

| + t <sub>LI</sub> + 4(t <sub>OPS</sub> )                                                  |                  |                                                                                                                                                          |                      | 04             |     | 141  | 1    |

| t <sub>pL</sub> + t <sub>LI</sub> + t <sub>OPS</sub> + interconnect                       | t <sub>B</sub> 9 |                                                                                                                                                          | 9,10,11              | 05             |     | 32.5 | ns   |

| Logic input to                                                                            | t <sub>ILO</sub> | See figure 3                                                                                                                                             | 1/                   | 02             |     | 20   | ns   |

| output                                                                                    | 110              |                                                                                                                                                          | =                    | 03             |     | 15   | 1    |

| (combinatorial)                                                                           |                  |                                                                                                                                                          |                      | 04             |     | 10   | 1    |

|                                                                                           |                  |                                                                                                                                                          |                      | 05             |     | 7.5  | 1    |

| Logic input to                                                                            | t <sub>ITO</sub> |                                                                                                                                                          | 1/                   | 02             |     | 25   | ns   |

| output                                                                                    | 1 110            |                                                                                                                                                          | _                    | 03             |     | 20   | 1    |

| (transparent-<br>latch)                                                                   |                  |                                                                                                                                                          |                      | 04             |     | 14   | 1    |

| ,                                                                                         |                  |                                                                                                                                                          |                      | 05             |     | 10   | 1    |

| Logic input to                                                                            | t <sub>QLO</sub> | 1                                                                                                                                                        | 1/                   | 02             |     | 13   | ns   |

| output (additional                                                                        | W.L.U            |                                                                                                                                                          | _                    | 03             |     | 8    | 1    |

| for Q through F)                                                                          |                  |                                                                                                                                                          |                      | 04,05          |     | 6    | ┪    |

| K clock to output                                                                         | <sup>t</sup> cкo |                                                                                                                                                          | 1/                   | 02             |     | 20   | ns   |

| stoom to output                                                                           | -CKO             | 1                                                                                                                                                        | <u>.,</u>            | 03             |     | 15   | - I  |

|                                                                                           |                  |                                                                                                                                                          |                      | 04             |     | 10.5 | ┨    |

|                                                                                           | I                | ĺ                                                                                                                                                        | 1                    | j 🕶 ]          |     | 10.7 | 1    |

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                     | 5962-88638        |

|------------------------------------------------------|------------------|---------------------|-------------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>B | SHEET<br><b>5</b> |

DESC FORM 193A JUL 94

9004708 0014062 316

TABLE I. <u>Electrical performance characteristics</u> - Continued. Test Symbol Conditions Group A Device Limits Unit  $4.5 \text{ V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V}$  $-55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +125^{\circ}\text{C}$ unless otherwise specified subgroups type Min Max K clock logictICK 1/ 02 12 ns input setup 03 8 04 7 05 6 K clock logictcki 1/ ALL 2 ns input hold C clock to output tcco 1/ 02 25 ns 03 19 04 13 05 9 C clock logicticc 1/ 02 12 input setup ns 03 9 04 6 05 5 C clock logic-133<sup>‡</sup> 1/ 02 6 ns input hold 03,04 2 05 Logic input to G tcio 1/ 02 37 clock to output ns 03 27 04 20 05 13 Logic input to G tici 1/ 02 clock logic-input ns setup 03 4 04 3 05 2 Logic input to G tcII 1/ 02 9 clock logic-input ns hold 03 5 04 4 3

See footnotes at end of table.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

SIZE

A

FREVISION LEVEL

B

SHEET

6

DESC FORM 193A

**JUL 94**

**--** 9004708 0014063 252 **--**

TABLE I. <u>Electrical performance characteristics</u> - Continued.

| Test                                  | Symbol           | Conditions<br>$4.5 \text{ V} \leq \text{V}_{CC} \leq 5.5 \text{ V}$                                                                                      | Group A<br>subgroups | Device<br>type | Li  | mits | Unit |

|---------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----|------|------|

|                                       |                  | $4.5 \text{ V} \leq \text{V}_{CC} \leq 5.5 \text{ V}$<br>$-55^{\circ}\text{C} \leq \text{T}_{C} \leq +125^{\circ}\text{C}$<br>unless otherwise specified |                      |                | Min | Max  |      |

| Set/reset direct                      | t <sub>RIO</sub> |                                                                                                                                                          | 1/                   | 02             |     | 25   | ns   |

| input A or D to out                   | İ                |                                                                                                                                                          |                      | 03             |     | 22   | 7    |

|                                       |                  |                                                                                                                                                          |                      | 04             |     | 16   | 1    |

|                                       |                  |                                                                                                                                                          |                      | 05             |     | 10   | 7    |

| Set/reset direct<br>through F or G to | t <sub>RLO</sub> |                                                                                                                                                          | 1/                   | 02             |     | 37   | ns   |

| out                                   | ŀ                |                                                                                                                                                          |                      | 03             |     | 28   |      |

|                                       |                  |                                                                                                                                                          |                      | 04             |     | 21   |      |

|                                       |                  |                                                                                                                                                          |                      | 05             |     | 14   | ] ]  |

| Set/reset direct<br>master reset pin  | t <sub>MRQ</sub> |                                                                                                                                                          | 1/                   | 02             |     | 55   | ns   |

| to out                                |                  |                                                                                                                                                          |                      | 03             |     | 45   |      |

|                                       |                  |                                                                                                                                                          |                      | 04             |     | 40   |      |

|                                       |                  |                                                                                                                                                          |                      | 05             |     | 17   |      |

| Set/reset direct seperation of        |                  |                                                                                                                                                          | υ                    | 02             | 17  |      |      |

| set/reset                             | t <sub>RS</sub>  |                                                                                                                                                          | ע                    | 03             | 9   |      | ns   |

|                                       |                  |                                                                                                                                                          |                      | 04             | 7   |      |      |

|                                       |                  |                                                                                                                                                          |                      | 05             | 6   |      |      |

| Set/reset direct<br>set/reset pulse-  | t <sub>RPW</sub> |                                                                                                                                                          | 1/                   | 02             | 12  |      | ns   |

| width                                 |                  |                                                                                                                                                          |                      | 03             | 9   |      |      |

|                                       |                  |                                                                                                                                                          |                      | 04             | 7   |      |      |

| -                                     |                  |                                                                                                                                                          |                      | 05             | 6   |      |      |

| Flip-flop toggle<br>rate Q through F  | F <sub>CLK</sub> |                                                                                                                                                          | 1/                   | 02             | 33  |      | MHz  |

| to flip-flop                          |                  |                                                                                                                                                          |                      | 03             | 50  |      |      |

|                                       |                  |                                                                                                                                                          | [                    | 04             | 70  |      |      |

|                                       |                  |                                                                                                                                                          |                      | 05             | 100 |      |      |

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                     | 5962-88638     |

|------------------|---------------------|----------------|

|                  | REVISION LEVEL<br>B | SHEET <b>7</b> |

DESC FORM 193A

JUL 94

9004708 0014064 199 📟

TABLE I. <u>Electrical performance characteristics</u> - Continued.

| Test                                 | Symbol           | Conditions<br>4.5 V $\leq$ V <sub>CC</sub> $\leq$ 5.5 V                                                                                                  | Group A<br>subgroups | Device<br>type | L   | imits | Unit |

|--------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----|-------|------|

|                                      |                  | $4.5 \text{ V} \leq \text{V}_{CC} \leq 5.5 \text{ V}$<br>$-55^{\circ}\text{C} \leq \text{T}_{C} \leq +125^{\circ}\text{C}$<br>unless otherwise specified |                      |                | Min | Max   | 7    |

| Clock high                           | t <sub>CH</sub>  |                                                                                                                                                          | 1/                   | 02             | 12  |       | ns   |

|                                      |                  |                                                                                                                                                          |                      | 03             | 8   |       |      |

|                                      |                  |                                                                                                                                                          |                      | 04             | 7   |       |      |

|                                      |                  |                                                                                                                                                          |                      | 05             | 5   |       | 7    |

| Clock low                            | t <sub>CL</sub>  |                                                                                                                                                          | 1/                   | 02             | 12  |       | ns   |

|                                      |                  |                                                                                                                                                          |                      | 03             | 8   |       | 7    |

|                                      |                  |                                                                                                                                                          |                      | 04             | 7   |       | 7    |

|                                      |                  |                                                                                                                                                          |                      | 05             | 5   |       |      |

| Pad (package pin)<br>to input direct | t <sub>PID</sub> |                                                                                                                                                          | 1/                   | 02             |     | 12    | ns   |

| to input direct                      |                  |                                                                                                                                                          |                      | 03             |     | 8     |      |

|                                      |                  |                                                                                                                                                          |                      | 04             |     | 6     |      |

|                                      |                  |                                                                                                                                                          |                      | 05             |     | 4     |      |

| I/O clock to input (storage)         | t <sub>LI</sub>  |                                                                                                                                                          | 1/                   | 02             |     | 20    | ns   |

| (515) 430,                           |                  |                                                                                                                                                          |                      | 03             |     | 15    |      |

|                                      |                  |                                                                                                                                                          |                      | 04             |     | 11    |      |

|                                      |                  |                                                                                                                                                          |                      | 05             |     | 8     | 1    |

| I/O clock to pad-<br>input setup     | t <sub>PL</sub>  |                                                                                                                                                          | 1/                   | 02             | 12  |       | ns   |

| mpac secup                           |                  |                                                                                                                                                          |                      | 03             | 8   |       | ]    |

|                                      |                  |                                                                                                                                                          |                      | 04             | 6   |       | ]    |

|                                      |                  |                                                                                                                                                          |                      | 05             | 4   |       | 1    |

| I/O clock to pad-<br>input hold      | t <sub>LP</sub>  |                                                                                                                                                          | 1/                   | All            | 0   |       | ns   |

| I/O clock pulse<br>width             | tLW              |                                                                                                                                                          | 1/                   | 02             | 12  |       | ns   |

| RIGUI                                |                  |                                                                                                                                                          | Ī                    | 03             | 9   |       |      |

|                                      |                  | j                                                                                                                                                        |                      | 04             | 7   |       |      |

|                                      |                  |                                                                                                                                                          |                      | 05             | 5   |       | 1    |

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                     | 5962-88638 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>B | SHEET 8    |

DESC FORM 193A JUL 94

9004708 0014065 025

TABLE I. <u>Electrical performance characteristics</u> - Continued.

| Test                             | Symbol           | Conditions<br>$4.5 \text{ V} \leq \text{V}_{CC} \leq 5.5 \text{ V}$                                                                                      | Group A<br>subgroups | Device<br>type | Li  | mīts | Unit |

|----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----|------|------|

|                                  |                  | $4.5 \text{ V} \leq \text{V}_{CC} \leq 5.5 \text{ V}$<br>$-55^{\circ}\text{C} \leq \text{T}_{C} \leq +125^{\circ}\text{C}$<br>unless otherwise specified |                      | ''             | Min | Max  |      |

| Output (enabled)<br>to pad       | t <sub>OP</sub>  |                                                                                                                                                          | 1/                   | 02             |     | 15   | ns   |

| to pau                           |                  |                                                                                                                                                          |                      | 03             |     | 12   | 1    |

|                                  |                  |                                                                                                                                                          |                      | 04             |     | 9    | 7    |

|                                  |                  |                                                                                                                                                          |                      | 05             |     | 7    | 7    |

| Three-state to pad<br>begin hi-z | t <sub>THZ</sub> |                                                                                                                                                          | У                    | 02             |     | 25   | ns   |

| begin in 2                       |                  | ,                                                                                                                                                        |                      | 03             |     | 20   | 1    |

|                                  |                  |                                                                                                                                                          |                      | 04             |     | 15   |      |

|                                  |                  |                                                                                                                                                          |                      | 05             |     | 11   |      |

| Three-state to pad end hi-z      | <sup>t</sup> TON |                                                                                                                                                          | 1/                   | 02             |     | 25   | ns   |

|                                  |                  |                                                                                                                                                          |                      | 03             |     | 20   | 1    |

|                                  |                  |                                                                                                                                                          |                      | 04             |     | 16   | 1    |

|                                  |                  |                                                                                                                                                          |                      | 05             |     | 13   | 1    |

| RESET to input                   | t <sub>RI</sub>  |                                                                                                                                                          | У                    | 02             |     | 40   | ns   |

| (storage)                        |                  |                                                                                                                                                          |                      | 03             |     | 30   | 1    |

|                                  |                  |                                                                                                                                                          | ĺ                    | 04             |     | 26   | ]    |

|                                  | _                |                                                                                                                                                          |                      | 05             |     | 17   | ]    |

| RESET to input                   | <sup>t</sup> RC  |                                                                                                                                                          | Ŋ                    | 02             | 35  |      | ns   |

| clock                            |                  |                                                                                                                                                          |                      | 03             | 25  |      | 1    |

|                                  |                  |                                                                                                                                                          |                      | 04             | 20  |      | 1    |

|                                  |                  |                                                                                                                                                          | Ī                    | 05             | 14  |      | 1    |

$<sup>\</sup>underline{\mathcal{U}}$  Parameter is not directly tested. Devices are first 100 percent functionally tested. Benchmark patterns (t<sub>B1-8</sub>) are then used to determine the compliance of this parameter. Characterization data are taken at initial device testing, prior to the introduction of significant changes, and at least twice yearly to monitor correlation between benchmark patterns and this parameter.

2/ Minimum CLOCK widths for the auxillary buffer are 1.25 times the t<sub>CH</sub>, t<sub>CL</sub>.

SIZE **STANDARD** Α 5962-88638 MICROCIRCUIT DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444

9

DESC FORM 193A JUL 94

9004708 0014066 761

Case X

| Device<br>type                                                                                                                                                                  | ALL                                                                                                                                                                                           | Device<br>type                                                                                                                                                                  | All                                                        | i<br>i | Device<br>type                                                                                                          | ALL                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Terminal<br>number                                                                                                                                                              | Terminal<br>symbol                                                                                                                                                                            | Terminal<br>number                                                                                                                                                              | Terminat<br>symbol                                         |        | Terminal<br>number                                                                                                      | Terminal<br>symbol                                                                                                           |

| A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>B8<br>B9<br>B10<br>B11<br>C1<br>C2<br>C3<br>C5<br>C6<br>C7<br>C10 | A9-I/O A8-I/O A-11I/O A-12I/O I/O A-13I/O I/O A-3I/O A-3I/O A-2I/O CCLK I/O PWRDWN A10-I/O A7-I/O I/O A14-I/O I/O A15-I/O A1-I/O DIN-DO-I/O I/O INDEX PIN A6-I/O GND A5-I/O DOUT-I/O RCLK I/O | D1<br>D2<br>D10<br>D11<br>E1<br>E2<br>E3<br>E9<br>E10<br>E11<br>F2<br>F3<br>F9<br>F10<br>G1<br>G2<br>G3<br>G9<br>G10<br>G11<br>H1<br>H2<br>H10<br>H11<br>J1<br>J1<br>J10<br>J11 | I/O I/O I/O WRT-D1-I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O |        | K1<br>K2<br>K3<br>K4<br>K5<br>K6<br>K7<br>K8<br>K9<br>K10<br>K11<br>L2<br>L3<br>L4<br>L5<br>L6<br>L7<br>L8<br>L9<br>L10 | I/O M2-I/O HDC-I/O I/O I/O I/O I/O I/O I/O OB-I/O RESET XTL1 or I/O MO-RTRIG I/O LDC-I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O |

NC = NO CONNECT

FIGURE 1. <u>Terminal connections</u>

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                     | 5962-88638  |

|------------------------------------------------------|------------------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>B | SHEET<br>10 |

DESC FORM 193A JUL 94

9004708 0014067 9T8 **=**

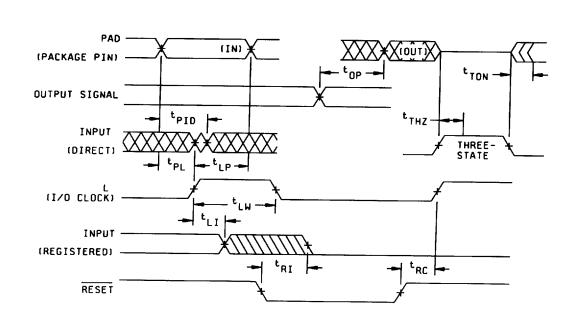

PWRDWN V<sub>CC</sub>(VALID) General logic cell array (LCA) switching characteristics. FIGURE 3. Timing diagrams and switching characteristics. SIZE STANDARD Α 5962-88638 MICROCIRCUIT DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444 12 DESC FORM 193A JUL 94 **9004708 0014069 770**

### NOTES:

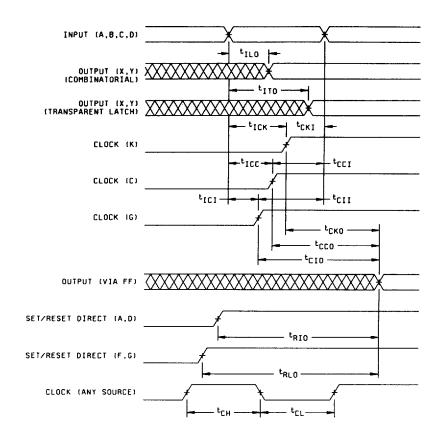

1. Configurable logic block (CLB) switching characteristics.

2. Timing is measured at 0.5 Vcc levels with 50 pF minimum output load. Input signal conditioning: Rise and fall times  $\le$  6 ns; Amplitude = 0 and 3 V.

FIGURE 3. <u>Timing diagrams and switching characteristics</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                     | 5962-88638  |

|------------------------------------------------------|------------------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>B | SHEET<br>13 |

DESC FORM 193A JUL 94

FIGURE 3. <u>Timing diagrams and switching characteristics</u> - Continued.

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br><b>A</b> |                     | 5962-88638      |

|------------------------------------------------------|------------------|---------------------|-----------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>B | SHEET <b>14</b> |

DESC FORM 193A

JUL 94

**-** 9004708 0014071 329 **-**

#### 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, D or E using the circuit submitted with the certificate of compliance (see 3.6 herein). The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 <u>Quality conformance inspection</u>. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

#### 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 ( $C_{IN}$  and  $C_{OUT}$  measurements) shall be measured only for the initial test and after process or design changes which may affect capacitance. Sample size is 5 devices with no failures, and all input and output terminals tested.

- d. Subgroups 7 and 8 shall consist of verifying functionality of the device. These tests form a part of the vendors test tape and shall be maintained and available from the approved sources of supply.

#### 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- Test condition A, B, C, D, or E using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

# 4.4 Device programming.

4.4.1 <u>Programming procedures and characteristics</u>. Programming procedures and characteristics shall be as specified by the individual device manufacturer and shall be made available upon request.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                     | 5962-88638      |

|------------------------------------------------------|------------------|---------------------|-----------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>B | SHEET <b>15</b> |

DESC FORM 193A JUL 94

9004708 0014072 265

TABLE IIA. Electrical test requirements. 1/2/3/4/5/

| Line<br>no. | Test Requirements                          | Subgroups (in accordance with MIL-<br>STD-883, method<br>5005, table I) |

|-------------|--------------------------------------------|-------------------------------------------------------------------------|

| 1           | Interim electrical parameters (see 4.2)    |                                                                         |

| 2           | Staic burn-in<br>(method 1015)             | Required                                                                |

| 3           | Same as line 1                             |                                                                         |

| 4           | Dynamic burn-in<br>(method 1015)           | Not<br>Required                                                         |

| 5           | Final electrical<br>paramters              | 1*,2,3,7*,<br>8A,8B,9,10,<br>11                                         |

| 6           | Group A test<br>requirements               | 1,2,3,4**,7,<br>8A,8B,9,10,<br>11                                       |

| 7           | Group C end-point<br>electrical parameters | 2,3,7,<br>8A,8B                                                         |

| 8           | Group D end-point<br>electrical parameters | 2,3,8A,8B,                                                              |

| 9           | Group E end-point<br>electrical parameters | 1,7,9                                                                   |

- $\frac{1}{2}$  Blank spaces indicate tests are not applicable.

- $\frac{2}{3}$ . Any or all subgroups may be combined when using high-speed testers.

- Subgroups 7 and 8 functional tests shall verify the functionality of the device.

- 4/ \* indicates PDA applies to subgroup 1 and 7.

- 5/ \*\* see 4.4.1e.

#### 5. PACKAGING

5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-STD-883 (see 3.1 herein).

#### 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes..

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DDForm 1692, Engineering Change Proposal MIL-STD-481 using DD form 1693, Engineering Change Proposal (Short Form).

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DESC-EC, telephone (513) 296-6047.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br><b>A</b> |                     | 5962-88638  |

|-----------------------------------------------------------------|------------------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |                  | REVISION LEVEL<br>B | SHEET<br>16 |

DESC FORM 193A JUL 94

💶 9004708 0014073 1T1 🖿

6.5 <u>Comments</u>. Comments on this drawing should be directed to DESC-EC, Dayton, Ohio 45444, or telephone (513) 296-5377.

# 6.6 Pin descriptions.

| PIN name<br>(number) | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRDWN<br>(B2)       | POWER-DOWN. An active low power-down input stops all internal activity to minimize $V_{CC}$ power and puts all output buffers in a high-impedance state. Configuration is retained, however, internal storage elements are Reset. When the PWRDWN pin returns HIGH, the <u>device</u> returns to operation with the same sequence of reset, <u>buffer</u> enable and DONE/PROGRAM as at the completion of configuration. If not used PWRDWN must be tied to $V_{CC}$ .                                                                                                                                                                                                                                                                                                               |

| MO<br>(L1)           | MODE 0. This input and M1, M2 are sampled before the start of configuration to establish the configuration mode to be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |