This Preliminary data sheet provides detailed functional capabilities for product currently in prototype production. These specifications are being provided to allow for electrical design, layout and operation.

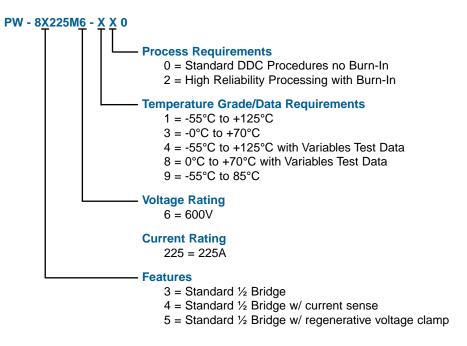

# PW-8X225M6 225A, 600V MAGNUM MOTOR DRIVE

# DESCRIPTION

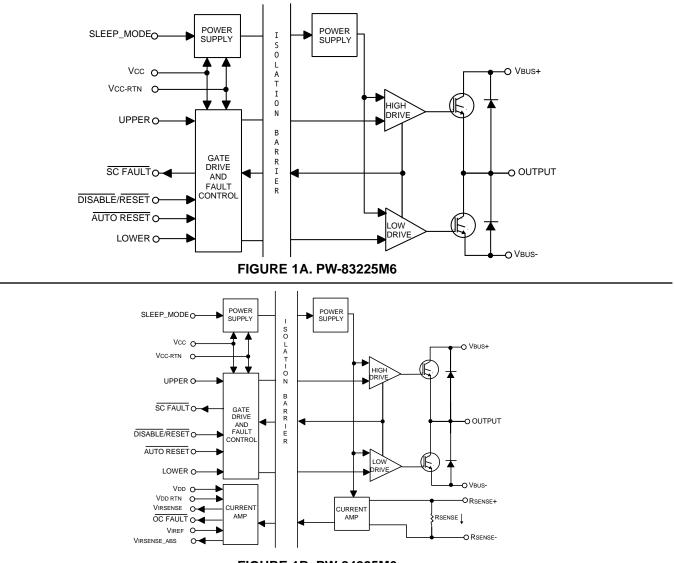

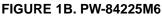

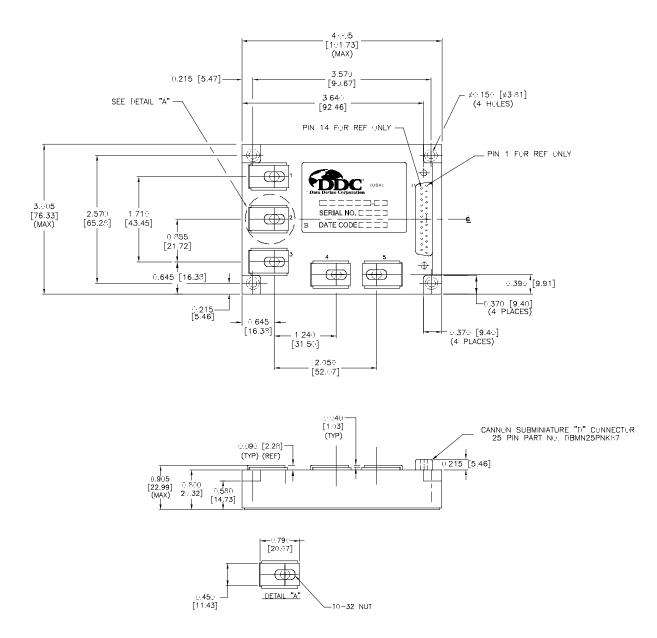

The PW-83225M6, PW-84225M6 and PW-85225M6 are half-bridge drive modules containing isolated switch drivers, an upper and lower solid-state switch, and an isolated power supply. In addition, the PW-84225M6 contains isolated current sensing feedback circuitry and the PW-85225M6 contains a regenerative clamp protection circuit.

The three modules can be used in any combination to create drives for brush, brushless DC, or AC induction motors. The current sense output signal and logic inputs are compatible with DSP/ microprocessors and/or FPGA/ASIC circuits used to control the motor drives. These modular drives are capable of operating from either a  $\pm 135$ Vdc or 270Vdc power source that is electrically isolated from the logic input signals. The modules are fault tolerant from output shorts, loss of any or all power supplies, and power supply sequencing.

# **APPLICATIONS**

The high reliability and flexibility of these drives make them suitable for Military and Aerospace applications. Among the many applications are: actuator systems for primary and secondary flight controls on aircraft, fan and compressor motor drives for environment conditioning, pump motors for fuel and hydraulic fluid, antenna and radar positioning, and thrust vector position control of missiles, drones, and RPV's.

# **FEATURES**

- 600 Vdc Drive for 270 Vdc Motors

- 215 Amps @85°C

- Operates with Brushless, Brush, and Induction Motors

- Input to Output Ground Isolation with Floating Output Stage

- Short Circuit Protection

- Trapezoidal or Sinusoidal Compatible

- DSP/Microprocessor Compatible

- PW-83225M6 Half-Bridge Drive

- PW-84225M6 Half-Bridge Drive with Current Sense

- PW-85225M6 Half-Bridge Drive with Regenerative Clamp

FOR MORE INFORMATION CONTACT:

"Data Device Corporation

Data Device Corporation 105 Wilbur Place Bohemia, New York 11716 631-567-5600 Fax: 631-567-7358 www.ddc-web.com Technical Support: 1-800-DDC-5757 ext. 7677

© 2001 Data Device Corporation

FIGURE 1C. PW-85225M6

| TABLE 1. PW-8X225M6 ABSOLUTE MAXIMUM RATINGS TC = 25°C |                                                        |               |       |  |  |  |  |

|--------------------------------------------------------|--------------------------------------------------------|---------------|-------|--|--|--|--|

| PARAMETER                                              | SYMBOL                                                 | VALUE         | UNITS |  |  |  |  |

| Drive Supply Voltage                                   | VBUS+ to VBUS-                                         | 600           | Vdc   |  |  |  |  |

| Logic Power-In Supply Voltage                          | Vcc                                                    | 5.5           | Vdc   |  |  |  |  |

| Input Logic Voltage                                    | UPPER, LOWER, DISABLE/RESET,<br>SLEEP_MODE, AUTO RESET | 5.5           | Vdc   |  |  |  |  |

| Reference Input Voltage                                | VIREF                                                  | VDD + 0.5 Vdc | Vdc   |  |  |  |  |

| Continuous Output Current                              | lo                                                     | 225           | А     |  |  |  |  |

| Peak Output Current (<10mS)                            | IPEAK                                                  | 400           | А     |  |  |  |  |

| Storage Temperature Range                              | TCS                                                    | -65 to +125   | °C    |  |  |  |  |

| Intermittent Case Operating Temperature                | Тсі                                                    | -55 to +125   | °C    |  |  |  |  |

| Continuous Case Operating Temperature                  | ТС                                                     | -55 to +100   | °C    |  |  |  |  |

| Junction Temperature, Power Devices                    | Tj                                                     | +150          | °C    |  |  |  |  |

| Junction Temperature, Other Components                 | Tj                                                     | +125          | °C    |  |  |  |  |

| Isolation Voltage (Note 2)                             | VISO                                                   | 2500          | Vdc   |  |  |  |  |

Note 1: In all tables TC refers to the temperature of the Magnum heat sink surface. Note 2: From VCC-RTN to VBUS+, VBUS-, OUTPUT, REGEN\_CLAMP, RSENSE+, RSENSE-.

#### TABLE 2. PW-8X225M6 SPECIFICATIONS Vcc = Vdd = 5V UNLESS OTHERWISE NOTED, Tc = -55°C TO 100°C FOR MIN, AND MAX VALUES, Tc = 25°C FOR TYP VALUES (SEE NOTE 1).

| TC = -55 C TO TOU C FOR MIN. AND MAX VALUES, $TC = 25$ C FOR TTF VALUES (SEE NOTE T). |                |                                                                       |     |      |      |       |  |

|---------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------|-----|------|------|-------|--|

| PARAMETER                                                                             | SYMBOL         | TEST CONDITIONS                                                       | MIN | TYP  | MAX  | UNITS |  |

| OUTPUT STAGE                                                                          |                |                                                                       |     |      |      |       |  |

| Drive Supply Voltage (motor) Output Switch<br>Transistors (each)                      | VBUS+ to VBUS- | Unipolar/Bipolar                                                      |     | 270  | 600  | Vdc   |  |

| Output Current Continuous Drive (DC)                                                  | ю              | TC = $25^{\circ}$ C, non switching DC                                 |     |      | 215  | A     |  |

|                                                                                       | IO             | TC = $85^{\circ}$ C, non switching DC                                 |     |      | 150  | A     |  |

| Output Current Commutating Drive                                                      | IO             | TC = +25 to +85°C, 3 phase drive,<br>50% duty cycle, 20 KHz switching |     |      | 215  | A     |  |

| Turn-on energy per pulse                                                              | EON            | VCE = 270V, I = 50A Tj = +125°C                                       |     | 1.8  |      | mJ    |  |

| Turn-off energy per pulse                                                             | EOFF           | VCE = 270V, I = 50A Tj = +125°C                                       |     | 14.4 |      | mJ    |  |

| Peak Current                                                                          | IPEAK          | TC = +25°C, ≤ 15 ms                                                   |     |      | 360  | A     |  |

| Short Circuit Trip Current (Note 2)                                                   | ISC            | <5 µs                                                                 | 600 | 900  | 1200 | A     |  |

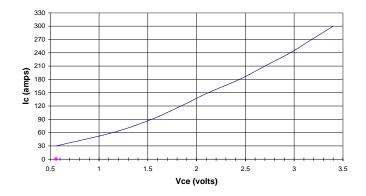

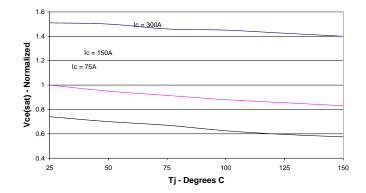

| Output Voltage Drop (IGBT)                                                            | VCE(SAT)       | IO = 145A                                                             |     | 2.2  | 2.6  | Vdc   |  |

| FLYBACK VOLTAGE                                                                       |                |                                                                       |     |      |      |       |  |

| Forward Voltage                                                                       | VF             | IO = 145A                                                             |     | 1.45 | 1.65 | Vdc   |  |

| Reverse Recovery Time @ T j = +125° C                                                 | trr            | IO = 145A                                                             |     | 180  |      | ns    |  |

| Reverse recovery Peak Current                                                         | Irr            | di/dt = 480A/µs, IF = 150 A (90°C)                                    |     | 60   | 80   | A     |  |

| Reverse Leakage Current @ T j = +25° C                                                | lr             | VBUS = 480Vdc                                                         |     |      | 1100 | μA    |  |

| Reverse Leakage Current @T j = +125° C                                                | lr             | VBUS = 480Vdc                                                         |     |      | 6.0  | mA    |  |

| OUTPUT SWITCHING CHARACTERISTICS                                                      |                |                                                                       |     |      |      |       |  |

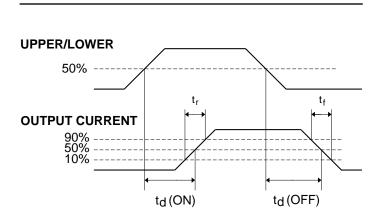

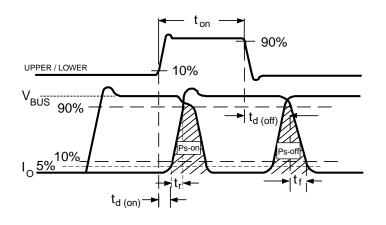

| (SEE FIGURE 5)                                                                        |                |                                                                       |     |      |      |       |  |

| Turn-on Propagation Delay                                                             | td (on)        | Vbus = 350Vdc, Resistive load                                         | 390 |      | 1000 | ns    |  |

| Turn-off Propagation Delay                                                            | td (off)       | Vbus = 350Vdc, Resistive load                                         | 740 |      | 1200 | ns    |  |

| Disable Propagation Delay                                                             | tsd            |                                                                       |     | 100  |      | μs    |  |

| Turn-on Rise Time                                                                     | tr             |                                                                       | 50  |      | 200  | ns    |  |

| Turn-off Fall Time                                                                    | tf             |                                                                       | 100 |      | 200  | ns    |  |

| Sleep_Mode Delay                                                                      | tsleep         |                                                                       | 0.7 | 0.5  | 1.5  | ms    |  |

| Output Switching Frequency                                                            | fPWM           |                                                                       | 0   | 25   |      | KHz   |  |

Note 1: In all tables TC refers to the temperature of the Magnum heat sink surface.

Note 2: VBUS+ to VBUS- must be ≥10V (during short circuit) for short circuit protection to operate.

| Vc                                                                                                                                                                                                                                                             | c = V D D = 5 V U                                                         | 25M6 SPECIFICATIONS (CONT.)<br>UNLESS OTHERWISE NOTED,<br>K VALUES, Tc = 25°C FOR TYP V |                    |                               | TE 1)                            |                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|-------------------------------|----------------------------------|------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                      | SYMBOL                                                                    | TEST CONDITIONS                                                                         |                    |                               | MAX                              | UNITS                                    |

| CONTROL INPUTS<br>AUTO RESET                                                                                                                                                                                                                                   |                                                                           |                                                                                         |                    |                               |                                  |                                          |

| High Level Input Voltage<br>Low Level Input Voltage<br>Hysteresis Voltage<br>High Level Input Current<br>Low Level Input Current<br>UPPER, LOWER                                                                                                               | VIH<br>VIL<br>VHYST<br>IIH<br>IIL                                         | VCC = 4.5V<br>VCC = 4.5V<br>Vin = VCC<br>Vin = 0V                                       | 1.55<br>0.9<br>0.4 | 2.5<br>1.6<br>0.9<br>0<br>1.5 | 3.15<br>2.45<br>2.1<br>1.5       | Vdc<br>Vdc<br>Vdc<br>μA<br>mA            |

| High Level Input Current<br>Low Level Input Current<br>DISABLE/RESET                                                                                                                                                                                           | liH<br>li∟                                                                | Vin = VCC<br>Vin = 0V                                                                   | 0                  | 20<br>0.1                     | 21<br>100                        | μA<br>nA                                 |

| High Level Input Current<br>Low Level Input Current<br>SLEEP_MODE                                                                                                                                                                                              | liH<br>li∟                                                                | Vin = VCC<br>Vin = 0V                                                                   |                    | 3                             | 1.5                              | μA<br>μA                                 |

| High Level Input Voltage<br>Low Level Input Voltage<br>High Level Input Current<br>Low Level Input Current<br><u>UPPER-LOWER DEADTIME</u><br><u>AUTO RESET</u> Delay to output off<br>AUTO RESET Delay to output enabled<br>RESET pulsewidth to clear SC FAULT | VIH<br>VIL<br>IIH<br>IIL<br>tDEAD<br>tdoff.auto<br>tdon.auto<br>tpw.reset | VCC = 4.5V<br>VCC = 4.5V<br>Vin = VCC<br>Vin = 0V                                       | 2.4<br>0.6<br>300  | 0.1<br>23<br>1<br>202<br>3    | 0.8                              | Vdc<br>Vdc<br>μA<br>μs<br>ms<br>ms<br>ns |

| Cycle time between AUTO RESET retries                                                                                                                                                                                                                          | tcycle.auto                                                               | AUTO RESET tied to SC FAULT                                                             | 40                 | 100                           |                                  | ms                                       |

| CONTROL OUTPUTS<br>SC FAULT<br>High Level Output Current<br>Low Level Output Current                                                                                                                                                                           | ISCFLTH<br>ISCFLTL                                                        | Vo = VCC<br>Vo = 0.4V                                                                   | -80                | 5                             | 6                                | μA<br>mA                                 |

| <b>THERMAL</b><br>Maximum Thermal Resistance - IGBT<br>Maximum Thermal Resistance - Diode<br>Junction Temperature Range<br>Case Operating Temperature<br>Case Storage Temperature                                                                              | θjc<br>θjc<br>Tj<br>Tc<br>Tcs                                             | Each UPPER or LOWER                                                                     | -55<br>-55<br>-65  | 0.13<br>0.36                  | 0.2<br>0.75<br>150<br>100<br>125 | W.3°<br>W,3°<br>S<br>S<br>S              |

| MECHANICAL<br>Mounting Torque<br>Hold down<br>Power Terminals<br>D-Connector Screws<br>Weight                                                                                                                                                                  |                                                                           |                                                                                         | 10<br>34<br>5      | 17 (482)                      | 12<br>42<br>65                   | in-lbs<br>in-lbs<br>in-lbs<br>oz (gm)    |

Note 1: In all tables TC refers to the temperature of the Magnum heat sink surface.

Note 2: VBUS+ to VBUS- must be ≥10V (during short circuit) for short circuit protection to operate.

| TABLE 3. PW-83225M6 SPECIFICATIONS<br>Vcc = Vdd = 5V UNLESS OTHERWISE NOTED,<br>Tc = -55°C TO 100°C FOR MIN. AND MAX VALUES, Tc = 25°C FOR TYP VALUES (SEE NOTE 1). |                                                    |              |  |     |     |    |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|--|-----|-----|----|--|--|--|--|

| PARAMETER                                                                                                                                                           | PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS |              |  |     |     |    |  |  |  |  |

| POWER AND LOGIC SUPPLY                                                                                                                                              | POWER AND LOGIC SUPPLY                             |              |  |     |     |    |  |  |  |  |

| Voltage VCC, VDD 4.5 5 5.5 Vdc                                                                                                                                      |                                                    |              |  |     |     |    |  |  |  |  |

| ogic Supply Current (see Note 2) ICC SLEEP_MODE 50 mA                                                                                                               |                                                    |              |  |     |     |    |  |  |  |  |

|                                                                                                                                                                     | ICC                                                | fpwm = 25KHz |  | 260 | 350 | mA |  |  |  |  |

Note 1: In all tables TC refers to the temperature of the Magnum heat sink surface.

Note 2: During initial power-on @ Vcc~3.5VDC, a transient current pulse up to 100 mA above lcc may be observed.

| TABLE 4. PW-84225M6 SPECIFICATIONS, Vcc = Vdd = 5V UNLESS OTHERWISE NOTED,<br>Tc = -55°C TO 100°C FOR MIN. AND MAX VALUES, Tc = 25°C FOR TYP VALUES (SEE NOTE 1). |                |                                  |        |       |        |                 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|--------|-------|--------|-----------------|--|--|

| PARAMETER                                                                                                                                                         | SYMBOL         | TEST CONDITIONS                  | MIN    | ТҮР   | MAX    | UNITS           |  |  |

| POWER AND LOGIC SUPPLY                                                                                                                                            |                |                                  |        |       |        |                 |  |  |

| Voltage                                                                                                                                                           | VCC, VDD       |                                  | 4.5    | 5     | 5.5    | Vdc             |  |  |

| Logic Supply Current (see Note 2)                                                                                                                                 | ICC            | SLEEP_MODE                       | 15     | 25    | 50     | mA              |  |  |

|                                                                                                                                                                   | ICC            | fpwm = 25Khz                     | 150    | 260   | 350    | mA              |  |  |

| Current Amplifier Supply Current                                                                                                                                  | IDD            |                                  |        | 10    | 20     | mA              |  |  |

| CURRENT AMPLIFIER                                                                                                                                                 |                |                                  |        |       |        |                 |  |  |

| VIRSENSE Gain %                                                                                                                                                   | GVOUT%         | 0A = VIREF/2                     |        | 0.185 |        | %VIREF/A        |  |  |

| VIRSENSE Gain                                                                                                                                                     | GVOUT          | VIREF = 5.0V                     |        | 9.27  |        | mV/A            |  |  |

| VIRSENSE Gain ERROR                                                                                                                                               | EVOUT          | 0A = VIREF/2                     | -7     |       | 7      | %               |  |  |

| VIRSENSE Offset %                                                                                                                                                 | VOS%VIREF      | 0A = VIREF/2                     | -0.64  |       | 0.64   | %VIREF          |  |  |

| VIRSENSE Offset                                                                                                                                                   | Vos            | VIREF = 5.0V                     | -32    |       | 32     | mV              |  |  |

| VIRSENSE Offset % Drift                                                                                                                                           | TCVOS%         | 0A = VIREF/2                     | -18    |       | 22     | ppm of VIREF/°C |  |  |

| VIRSENSE Offset Drift                                                                                                                                             | TCVOS          | VIREF = 5.0V                     | -90    |       | 130    | μV/°C           |  |  |

| VIRSENSE_ABS Gain %                                                                                                                                               | GVOUT%         | 0A = 0V                          |        | 0.372 |        | %VIREF/A        |  |  |

| VIRSENSE_ABS Gain                                                                                                                                                 | GVABS          | 0A = 0V                          |        | 18.6  | _      | mV/A            |  |  |

| VIRSENSE_ABS Gain ERROR                                                                                                                                           | EVABS          |                                  | -9     |       | 9      | %               |  |  |

| VIRSENSE_ABS Offset %                                                                                                                                             | VOSABS % VIREF |                                  | -2.66  |       | 2.66   | %VIREF          |  |  |

| VIRSENSE_ABS Offset                                                                                                                                               | VOSABS         | VIREF = 5.0V                     | -133   |       | 133    | mV              |  |  |

| VIRSENSE_ABS Offset % DRIFT                                                                                                                                       | TCVOSABS%      |                                  | -18    |       | 22     | ppm of VIREF/°C |  |  |

| VIRSENSE_ABS Offset DRIFT                                                                                                                                         | TCVOSABS       | VIREF = 5.0V                     | -90    |       | 110    | μV/°C           |  |  |

| Delay Time                                                                                                                                                        | tdelay         | 50A to 215A step                 |        | 9     | 20     | μs              |  |  |

| Bandwidth                                                                                                                                                         | fBW            | -3 db                            | 20     | 30    |        | kHz             |  |  |

| Linear Range                                                                                                                                                      | Irange         |                                  |        | ±215  |        | A               |  |  |

| OC FAULT Trip Level                                                                                                                                               | loc            | VIREF = 5.0V                     | ±246.2 | ±274  | ±299.7 | A               |  |  |

| Trip Delay Time                                                                                                                                                   | tIOC           | 50A to 215A step, VIREF = $5.0V$ |        | 3     | 6<br>1 | μs              |  |  |

| Reference Voltage Current Input                                                                                                                                   | IVIREF         |                                  |        | 0.26  |        | mA              |  |  |

| Reference Voltage Input                                                                                                                                           | VIREF          |                                  | 4      |       | VDD    | Vdc             |  |  |

| OC FAULT (-55° TO 100°C)                                                                                                                                          |                |                                  |        |       |        |                 |  |  |

| High Level Output Current                                                                                                                                         | IOCFLTH        | VO = VDD                         |        | 0.2   | 15     | μA              |  |  |

| Low Level Output Current                                                                                                                                          | IOCFLTL        | VO = 0.8V max                    |        |       | 4      | mA              |  |  |

Note 1: In all tables TC refers to the temperature of the Magnum heat sink surface. Note 2: During initial power-on @ Vcc~3.5VDC, a transient current pulse up to 100 mA above Icc may be observed.

| TABLE 5. PW-85225M6 SPECIFICATIONS, $Vcc = Vdd = 5V$ UNLESS OTHERWISE NOTED,<br>Tc = -55°C TO 100°C FOR MIN. AND MAX VALUES, Tc = 25°C FOR TYP VALUES (SEE NOTE 1).               |                                                                  |                                                                            |             |                               |                                    |                              |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------|-------------|-------------------------------|------------------------------------|------------------------------|--|--|

| PARAMETER                                                                                                                                                                         | SYMBOL                                                           | TEST CONDITIONS                                                            | MIN         | TYP                           | MAX                                | UNITS                        |  |  |

| POWER AND LOGIC SUPPLY<br>Voltage<br>Current (see Note 2)                                                                                                                         | Vcc<br>Icc<br>Icc                                                | SLEEP_MODE<br>fpwm = 25Khz                                                 | 4.5         | 5<br>25<br>260                | 5.5<br>50<br>350                   | Vdc<br>mA<br>mA              |  |  |

| OVERVOLTAGE TRANSISTOR (REGEN_CLAMP)<br>Continuous Current Drive<br>Peak Current<br>Output Voltage Drop (IGBT)<br>Reverse Leakage @ T J = +25°C<br>Reverse Leakage @ T J = +125°C | lo<br>Io<br>IPEAK<br>VCE(SAT)<br>Ir<br>Ir                        | TC = +25°C<br>TC = +85°C<br>TC = +85°C, 15 ms<br>50A<br>480 Vdc<br>480 Vdc |             | 2.5                           | 75<br>50<br>100<br>3<br>200<br>1.0 | Α<br>Α<br>Vdc<br>μΑ<br>mA    |  |  |

| OVERVOLTAGE FLYBACK DIODE<br>Reverse Leakage @ Tc = +25°C<br>Reverse Leakage @ Tc = +125°C<br>OVERVOLTAGE TRIP<br>Trip Level Hysteresis                                           | lr<br>Ir<br>Vtrip<br>Vhyst                                       | 480 Vdc<br>480 Vdc<br>without external adjustment                          | 358<br>35   | 400<br>40                     | 750<br>20<br>440<br>45             | μA<br>mA<br>Vdc<br>Vdc       |  |  |

| REGEN STATUS (REF. TO VBUS-)<br>High Level Output Voltage<br>Low Level Output Voltage<br>Output resistance<br>Vtrip rise to status ON Delay<br>Vtrip fall status OFF Delay        | VOHstatus<br>VOLstatus<br>Rstatus<br>tdon.status<br>tdoff.status | No Load<br>No Load                                                         | 11.4<br>4.5 | 12<br>0.2<br>4.75<br>36<br>48 | 12.6<br>0.4<br>5                   | Vdc<br>Vdc<br>KΩ<br>µs<br>µs |  |  |

| THERMAL<br>Maximum Thermal Resistance                                                                                                                                             |                                                                  |                                                                            |             | 0.5                           | 0.75                               | °C/W                         |  |  |

Note 1: In all tables TC refers to the temperature of the Magnum heat sink surface. Note 2: During initial power-on @ Vcc~3.5VDC, a transient current pulse up to 100 mA above Icc may be observed.

# INTRODUCTION

The PW-8X225M6 Magnum family is a series of universal modular half-bridge motor drives intended for use with brush, brushless, DC and AC induction motors in aerospace applications.

The PW-8X225M6 contains an isolation barrier between the power and control stages, that attenuates ground noise generated from the high speed, high power switching. All signals from the control to the power sections are isolated from power and ground of the other section. This eliminates false triggering of the input signals and the need for creative grounding schemes. The isolation barrier also allows the user to operate the output stage from either unipolar or bipolar power supplies without level shifting the input signals. A built in power supply located in the control stage provides power to all electronics in the power stage. This eliminates the need for refresh cycles or external power supplies for the gate drive circuitry and allows switching duty cycles from 0 - 100%. (Reference FIGURES 1A, 1B, and 1C)

The output power transistors on all modules are protected from a short circuit applied to the output pin. When a short circuit condition is detected, the output transistors are shut down and a flag SC FAULT is made active [logic low (L)] indicating a short has occurred. The PW-84225M6 contains additional current sensing circuitry that can monitor either motor current or DC bus current. The output voltage of the current sensing circuit can be used as a feedback signal in a servo drive to create a torque loop. (Reference FIGURE 1B)

All output power transistors can be protected from regenerative bus overvoltage when utilizing dynamic braking with the addition of one PW-85225M6 module. This module contains an overvoltage switch that is enabled when an overvoltage condition is detected. This switch is normally wired to an external (user supplied, application specific) load dump resistor to provide a load across the high voltage bus when overvoltage is detected. During an overvoltage condition, the status flag REGEN\_STA-TUS is active (logic high (H)) indicating an overvoltage condition is occurring. (Reference FIGURE 1C)

# **MODULE AND I/O OPERATION**

#### UPPER, LOWER (INPUTS)

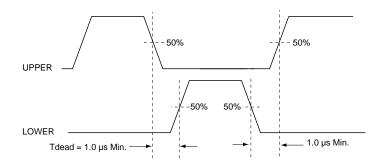

UPPER and LOWER are active high CMOS Schmitt-trigger inputs that control the gate drives of the output transistors. (TTL compatibility requires external 10K $\Omega$  pull-up resistors) Each input is electrically isolated from the output. A dead band, as shown in FIGURE 2, between UPPER and LOWER inputs is necessary to prevent output cross conduction.

#### SC FAULT (OUTPUT)

SC FAULT is an active low open collector output signal that indicates when the output of the module has experienced a short circuit condition. SC FAULT will remain active until DISABLE/RESET is made active (L). The signal is inactive at a logic high (H) during normal operation.

See SHORT CIRCUIT PROTECTION for more detail.

#### DISABLE/RESET (INPUT)

DISABLE/RESET is an active low CMOS Schmitt-trigger input. When DISABLE/RESET is held active it does two things:

- 1.) Resets the SC FAULT (if it was active), and

- 2.) Disables the output (makes the output high impedance)

If this line is used solely to clear SC FAULT then it only needs to be pulsed active. The width of the active pulse must be at least the width of the trip reset pulse (100ns) to ensure that SC FAULT is cleared properly. When this line is inactive, the OUTPUT is allowed to respond to the other control lines of the module (UPPER, LOWER, SLEEP\_MODE).

Note: TTL compatibility requires an external pull-up resistor.

#### AUTO RESET (INPUT)

AUTO RESET is an active low (L) input. When AUTO RESET is tied to SC FAULT the protection circuit will reset automatically after the short circuit fault has occurred. This automatic reset enables the output to respond to the input commands.

See SHORT CIRCUIT PROTECTION for more detail.

#### SHORT CIRCUIT PROTECTION

The PW-8X225M6 modules have provisions for complete short circuit protection from either a hard or soft short to the VBUS+ or VBUS- lines.

Each output transistor on all PW-8X225M6 modules is protected from a hard (direct, low impedance) short to the VBUS+ or VBUS-

#### FIGURE 2. PW-8X225M6 DEAD BAND REQUIREMENT

lines by circuitry that detects the de-saturation voltage for that transistor during a short condition. Once a hard short circuit condition is detected, the active output transistors are shut down and SC FAULT output is set active [logic low (L)]. The SC FAULT signal can be used by a controller as a signal to initiate a fault routine to reset or shut down the system. The DISABLE/RESET input can be used to shut down the gate drivers if a short persists. If the AUTO RESET is tied to SC FAULT, the circuit will automatically reset when a fault occurs. This inactivates SC FAULT and reactivates the output transistor within 40 to 100ms. If the short is still present, the circuit will repeat the shut down and automatically reset until the short is clear.

Protecting against a soft short requires the addition of PW-84225M6 modules for current sensing and external circuitry. When a soft short occurs, the external circuit can set DISABLE/RESET low (L) to shut down the gate drivers.

#### SLEEP\_MODE (INPUT)

SLEEP\_MODE is an active high input that turns the internal power supply off. A logic low (L) enables the power supply and allows the motor drive to operate normally.

A logic high (H) on the SLEEP\_MODE input disables the internal power supply, disabling the motor drive output. No damage will occur to the motor drive during turn on or turn off of the power supply. Additionally, no special power up sequence is required.

The UPPER and LOWER logic gate driver inputs should not be active while transitioning in and out of sleep mode. If the UPPER and LOWER logic inputs must be active while entering sleep mode then DISABLE/RESET must be held active while coming out of sleep mode.

**Note:** SLEEP\_MODE has an internal pull-up resistor. If the input is not connected, it will default to logic high, turning the power supply and the motor drive off.

## FIGURE 3. PW-8X225M6 INPUT/OUTPUT TIMING RELATIONSHIP

# VCC, VCC-RTN (INPUTS)

The VCC and VCC-RTN are power connections that supply input power to the internal power supply, the gate drive and fault control circuits.

#### VBUS+, VBUS- (INPUTS)

VBUS+ and VBUS- are the high voltage power connections to the output stage. The high voltage can be either unipolar (+V and ground) or bipolar (+/- V). Care must be taken to ensure that the transient bus voltage VBUS at the module terminals never exceeds the absolute maximum supply ratings during switching excursions. External capacitor filtering will be required (See DDC applications note AN/H-7).

#### OUTPUT (OUTPUT)

Output is the power switch output that is connected to one input of the motor and applies VBUS+, VBUS-, or high impedance to the motor based on the state of the control inputs. FIGURE 3 illustrates the timing relationship between the output and the UPPER/LOWER inputs. The output is capable of sourcing or sinking up to 215 Amps, and can withstand a short circuit to VBUS+ or VBUS- without any damage by automatically turning itself off (Zstate).

#### VDD, VDD- RTN (APPLIES TO THE PW-84225M6 ONLY)

VDD and VDD-RTN supplies input power to the current amplifier.

## VIRSENSE (OUTPUT) (APPLIES TO PW-84225M6 ONLY)

VIRSENSE is an output that provides a voltage proportional to the current passing through RSENSE. The voltage is scaled by a reference voltage VREF and is equal to VREF/2 to represent zero current. A voltage greater than VIREF/2 indicates a positive current flow (positive voltage from RSENSE + to RSENSE -) through RSENSE. See FIGURE 1B.

This  $\mathsf{V}\mathsf{IRSENSE}$  voltage is scaled by the input voltage at  $\mathsf{V}\mathsf{IREF},$  where

VIRSENSE = (VIREF/2) + (VIREF/540) \* (IRSENSE)

Note: IRSENSE is current through RSENSE =  $108m\Omega$ . Zero amps in RSENSE is indicated when VIRSENSE = VIREF/2. A voltage greater (less) than VIREF/2 indicates a positive (negative) current flow through RSENSE with a value defined by the VIRSENSE equation. VIRSENSE is electrically isolated from the output stage. A Positive (negative) current flow from RSENSE + to RSENSE - produces a positive (negative) voltage measurement (See FIGURE 1B). When the power supply is shut down (SLEEP\_MODE input high), the voltage at VIRSENSE will indicate 0V.

## VIREF (INPUT) (APPLIES TO PW-84225M6 ONLY)

A precision voltage reference from an external source is connected to the VIREF pin to set the output voltage scale for VIRSENSE and VIRSENSE\_ABS. Note: The accuracy of the VIRSENSE and VIRSENSE\_ABS outputs are subject to the accuracy and tem-

perature coefficient of VIREF. These must be taken into account in calculating the overall accuracy of VIRSENSE.

# RSENSE+, RSENSE- (INPUTS) (APPLIES TO PW-84225M6 ONLY)

The RSENSE+ and RSENSE- pins are connected to an internal shunt resistor and monitoring circuitry. These pins can be connected anywhere within the isolation restrictions on the pins (600V to power pins, 2500V to logic pins). These pins are typically connected in series with the output, VBUS+ or VBUS-, to measure motor drive current.

#### VIRSENSE\_ABS (OUTPUT) (APPLIES TO PW-84225M6 ONLY)

VIRSENSE\_ABS output voltage is the absolute value of the VIRSENSE voltage signal. VIRSENSE\_ABS is zero volts when there is no current flowing through the RSENSE resistor. It will increase towards the value of VIREF as the current in RSENSE approaches either -274 or +274 amps (measurement limits of VIRSENSE). VIRSENSE\_ABS is an open source output and is "wire-OR-able". When two or more VIRSENSE\_ABS outputs are "wire-OR-ed", the highest voltage will appear on the common signal. A typical use for combining these outputs is for determining when an overload condition has occurred. The VIRSENSE\_ABS voltage is scaled by the input voltage VIRSENSE where:

#### VIRSENSE\_ABS = 2 x [VIRSENSE- VIREF/2]

# OC FAULT (OUTPUT) (APPLIES TO PW-84225M6 ONLY)

$\overrightarrow{OC}$  FAULT is an active low open drain output that goes active when the current flowing through RSENSE has exceeded the  $\overrightarrow{OC}$ FAULT trip level. This signal is not latched like  $\overrightarrow{SC}$  FAULT, and goes inactive as soon as the over current condition stops.

## REGEN\_STATUS (OUTPUT) (APPLIES TO PW-85225M6 ONLY)

The REGEN\_STATUS pin is referenced to VBUS-. It indicates the state of the regen clamp switch (H = on, L = off). An external opto-isolator input can be connected between REGEN\_STATUS and VBUS- to translate this status to logic circuits if desired. The REGEN\_STATUS output is connected to the 0V amp through a 5K resistor. When the regen clamp switch is active (inactive), the 0V amp sources +15V (0V) through the 5K resistor. (see FIG-URE 1C)

## REGEN\_CLAMP (OUTPUT) (APPLIES TO PW-85225M6 ONLY) (REF. R20 ON FIGURES 13 AND 14)

An external load dump resistor is connected between REGEN\_CLAMP and VBUS+. When VBUS+ reaches the overvoltage trip level set by the OV\_ADJ, the internal clamp circuit will apply the load dump resistor from VBUS+ to the VBUS-, thereby dissipating the regenerative energy in the external resistor.

|       | TABLE 6. PW-8X225 TRUTH TABLE |         |         |         |            |               |            |          |        |

|-------|-------------------------------|---------|---------|---------|------------|---------------|------------|----------|--------|

| UPPER | LOWER                         | TEST A* | TEST B* | TEST C* | AUTO RESET | DISABLE/RESET | SLEEP_MODE | SC FAULT | OUTPUT |

| 1     | 0                             | 1       | 0       | 0       | 1          | 1             | 0          | 1        | VBUS+  |

| 0     | 1                             | 1       | 0       | 0       | 1          | 1             | 0          | 1        | VBUS-  |

| 1     | 0                             | 0       | 1       | 0       | 1          | 1             | 0          | 1        | VBUS+  |

| 0     | 1                             | 0       | 1       | 0       | 1          | 1             | 0          | 1        | VBUS-  |

| 1     | 0                             | 0       | 0       | 1       | 1          | 1             | 0          | 1        | VBUS+  |

| 0     | 1                             | 0       | 0       | 1       | 1          | 1             | 0          | 1        | VBUS-  |

| 1     | 0                             | 1       | 1       | 1       | 1          | 1             | 0          | 1        | VBUS+  |

| 0     | 1                             | 1       | 1       | 1       | 1          | 1             | 0          | 1        | VBUS-  |

| 0     | 0                             | 1       | 1       | 1       | 1          | 1             | 0          | 0        | Z      |

| 1     | 0                             | 1       | 1       | 1       | 1          | 1             | 0          | 0        | Z      |

| 0     | 1                             | 1       | 1       | 1       | 1          | 1             | 0          | 0        | Z      |

| Х     | Х                             | 0       | 0       | 0       | Х          | 1             | 0          | Х        | Z      |

| Х     | Х                             | Х       | Х       | Х       | Х          | 0             | 0          | Х        | Z      |

| Х     | Х                             | Х       | Х       | Х       | Х          | Х             | 1          | 1        | Z      |

X = Indicates this input is irrelevant

Z = High Impedance state (off)

Z (VBUSx) = SC FAULT will not inhibit a gate drive that did not generate the fault. The opposite gate drive may still activate the output (VBUSx state). Only the gate drive (upper or lower) that faulted is inhibited and the output stays high impedance (Zstate) when faulted driver is commanded active.

\* Optional feature of PW-8X225M6-600 only.

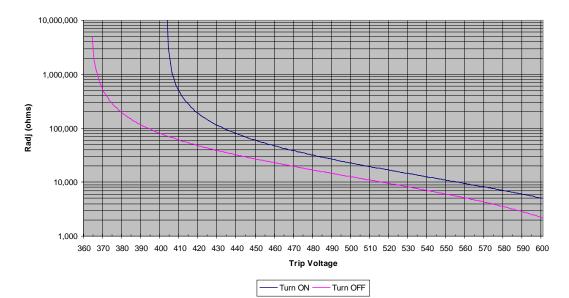

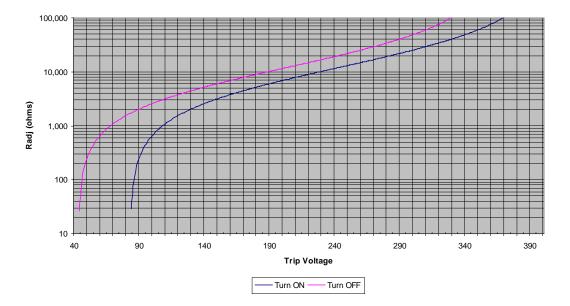

#### OV\_ADJ (INPUT) (APPLIES TO PW-85225M6 ONLY) The PW-85225M6 is internally set for a trip voltage of 400V.

The trip point can be adjusted to a higher or lower voltage by

connecting an external overvoltage adjust resistor Rov\_ADJ (Ref. R21 on FIGURES 13 and 14).

To set the OV trip point to a voltage above 400 volts connect Rov\_ADJ between the OV\_ADJ and OV\_ADJ\_HIGH pins. To set the OV trip point to a voltage above 400 volts connect Rov\_ADJ between the OV\_ADJ and OV\_ADJ\_LOW pins. The value of

$\ensuremath{\mathsf{Rov}_\mathsf{ADJ}}$  for voltages above (below) 400 volts should be selected based upon FIGURES 4 and 5.

#### TEST A, TEST B, TEST C (PW-8X225M6-600 ONLY)

These logic inputs are used to test individual pairs (UPPER and LOWER) of output transistors within the module per TABLE 6. The intent is to provide the user with the capability to detect an open transistor within the parallel combination of output devices.

**Note:** When Test A, Test B, Test C are exercised individually, the device is not capable of delivering the rated current.

FIGURE 4. PW-8X225M6 OVERVOLTAGE TRIP VOLTAGE VS. RESISTANCE OF EXTERNAL RESISTOR CONNECTED BETWEEN OV\_ADJ AND OV\_ADJ\_HIGH

FIGURE 5. PW-8X225M6 TYPICAL OVERVOLTAGE TRIP VOLTAGE VS. RESISTANCE (IN OHMS) OF EXTERNAL RESISTOR ROV\_ADJ CONNECTED BETWEEN OV\_ADJ AND OV\_ADJ\_LOW

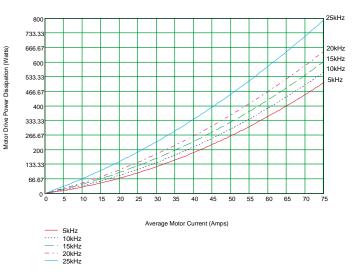

#### POWER DISSIPATION (SEE FIGURES 6 AND 7)

There are three major contributors to power dissipation in the motor driver: conduction losses, switching losses, and flyback diode losses. Consider the following operating conditions:

TCASE = 85 °C

VBUS = +270V

Io = 40A

ton =  $50\mu s$ ; T =  $100\mu s$  (period)

$V_{CE(SAT)} = 2.2V$  (see TABLE 2 and FIGURES 6 and 7)

tr = 200ns ) tf = 200ns

fPWM = 10kHz (switching frequency)

VF is the diode forward voltage, (TABLE 2), IO = 50A, TC = +25°C

VF(avg) = 1.35V

T<sub>J MAX</sub> = 150 °C (TABLE 2, T<sub>J</sub>)  $\Theta_{JC} = 0.55$  °C/<sub>W</sub> (TABLE 2)

#### 1. Conduction Losses (Pc)

$\label{eq:pc} \begin{array}{l} \mathsf{Pc} = \mathsf{IO} \; x \; \mathsf{VCE}(\mathsf{SAT}) \; x \; (\mathsf{ton} \; / \; \mathsf{T}) \\ \mathsf{Pc} = 40 \mathsf{A} \; x \; 2.2 \mathsf{V} \; x \; (50 \mu \mathsf{s} \; / \; 100 \mu \mathsf{s}) \\ \mathsf{Pc} = 44 \mathsf{W} \end{array}$

#### 2. Switching Losses (PS-TOTAL)

PS-TOTAL = (PS-ON + PS-OFF) x fpwm PS-ON = (EON x (VBUS / 270) x (IO/50A)) PS-ON = (4.0 x (270 / 270) x (40 / 50)) PS-ON = 3.2 mJ PS-OFF = (EOFF x (VBUS/270) x (IO/50)) PS-OFF = (2.4 mJ x (270/270) x (40/50)) PS-OFF = 1.92 mJ PS-TOTAL = 10000 x (.0032 + .00192) PS-TOTAL = 51.2W

3. Flyback diode Losses (Pdf)

Pdf = Io x VF(avg) x (1- (ton / T)) Pdf = 40A x 1.35V x [1 - (50µs / 100µs)] Pdf = 33.8W

#### 4. Transistor Power Dissipation (PT)

PT = PC + PS = 95.2W

#### 5. Maximum Module Power Dissipation (PMAX)

To calculate the maximum power dissipation of the output transistor / diode pair as a function of the case temperature, use the following equation:

PMAX = ((T<sub>J</sub>MAX - TCASE) / ΘJC) 118W = ((150 °C - 85 °C) / 0.55°C/W)

**FIGURE 6. OUTPUT CHARACTERISTICS**

#### FIGURE 7. PW-8X2255 AVERAGE MOTOR CURRENT VS. MOTOR DRIVE POWER DISSIPATION

# **APPLICATIONS**

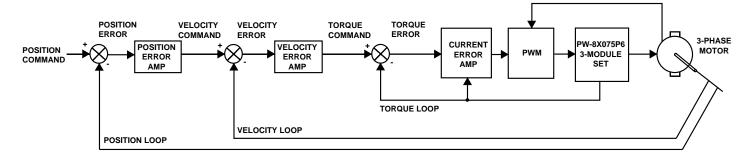

The PW-8X225 3-module set can be easily used in a variety of applications, including motor position, velocity or torque control (see FIGURE 10). Examples of these applications are described below.

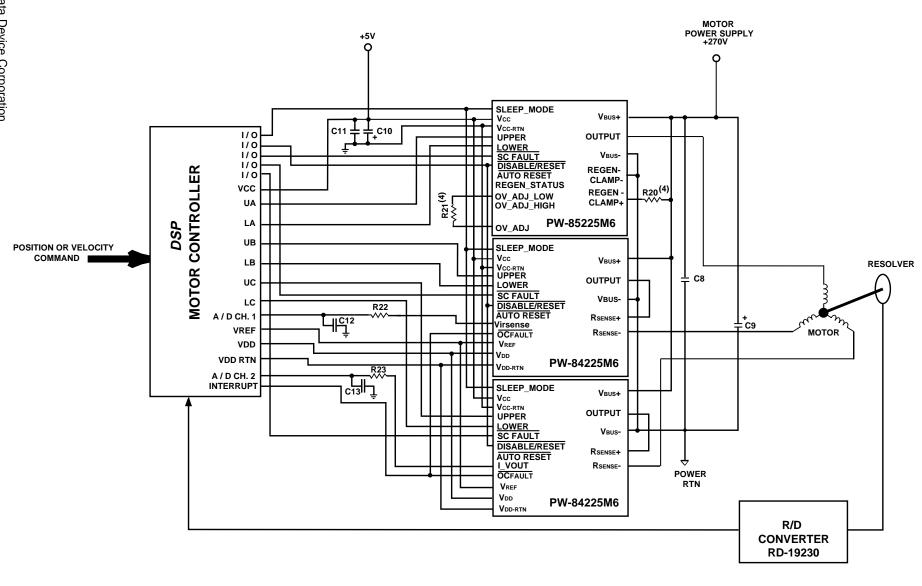

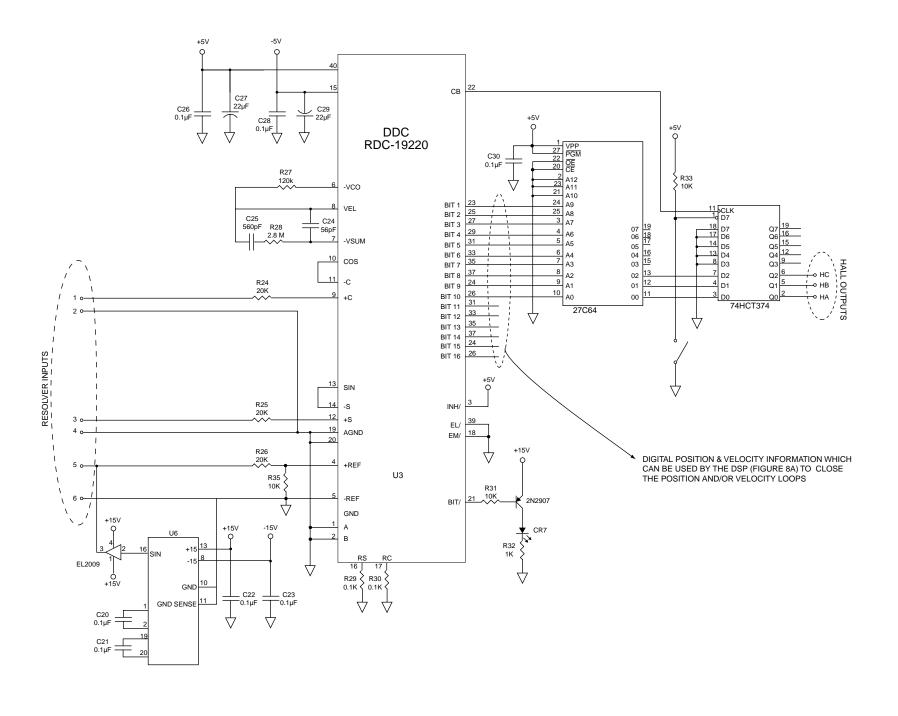

#### POSITION OR VELOCITY CONTROL USING DSP

FIGURE 13 shows an example of position and/or velocity control hook-up with inner torque loop using the Digital Signal Processor (DSP) for motor control. Using software, the DSP can be implemented with one of several motor control algorithms such as FOC (Field Oriented Control) with SVM (Space Vector modulation).

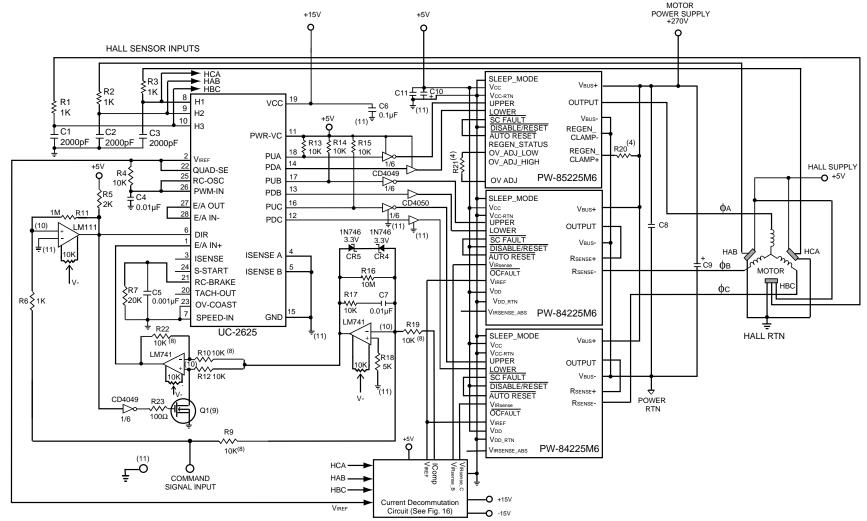

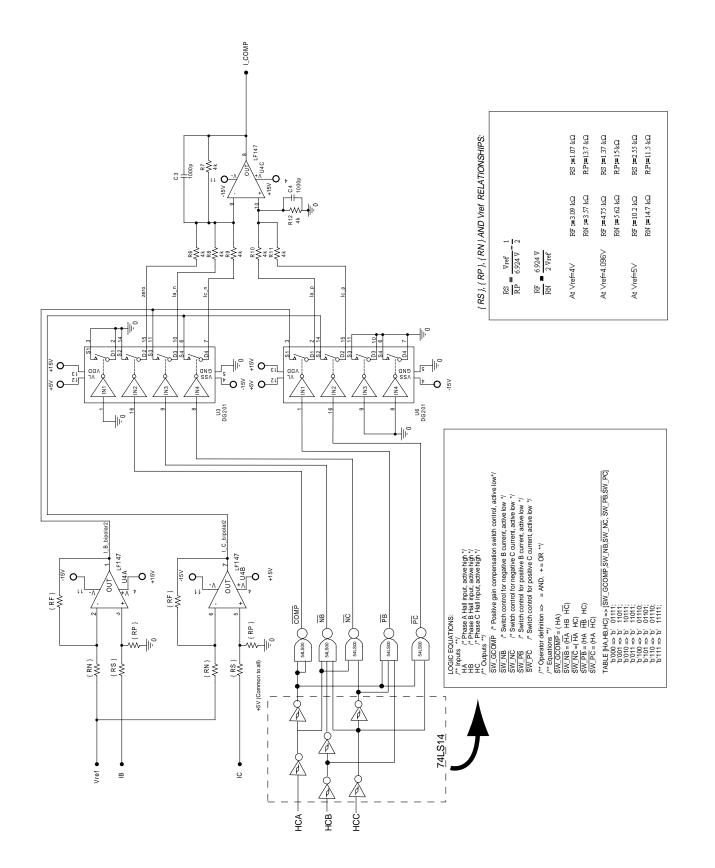

## TORQUE HOOK-UP USING UC-2625 MOTOR CON-TROLLER

FIGURE 14 shows an example of torque control loop with regenerative clamp protection using UC-2625, two PW-84225M6, and one PW-85225M6. Two PW-84225M6 (½ bridge with current sense) sense the current in motor phase B and C. VIRSENSE\_ABS pins on each of the PW-84225M6 can be tied together to generate a single composite analog output which is compared to the torque commanded input to produce an error signal. UC2625 uses this error signal to regulate the output current (or torque) by controlling the duty cycle of the output transistors.

For the case when a resolver is available instead of Hall-effect devices, the circuit shown in FIGURE 15 converts the resolver (sin and cos) signals to Hall signals which can be used to commutate the output transistors.

#### HALL SIGNAL COMMUTATION

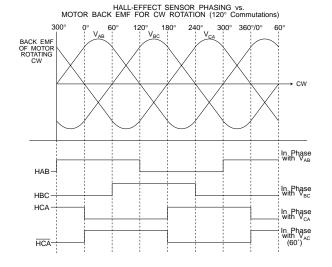

The hall signals HAB, HBC, HCA are logic signals from the motor Hall-effect sensors. The UC-2625 uses a phasing convention referred to as 120 degree spacing; that is, the output of HAB is in phase with motor back EMF voltage VAB, the output of HBC is in phase with motor back EMF voltage VBC, and the output of HCA is in phase with motor back EMF voltage VCA. Logic "1" (or HIGH ) is defined by an input greater than 2.4Vdc or an open circuit to the controller; Logic "0"(or LOW) is defined as any Hall voltage input less than 0.8Vdc.

The UC-2625 will operate with Hall phasing of 60° or 120° electrical spacing. If 60° commutation is used, then the output of HCA must be inverted as shown in FIGURES 11 and 12. In FIG-URE 11 the Hall sensor outputs are shown with the corresponding back EMF voltage they are in phase with.

#### FIGURE 8. - SATURATION VOLTAGE CHARACTERISTICS

# FIGURE 9. - TEMPERATURE DEPENDENCE OF VCE(SAT)

# FIGURE 11. HALL PHASING

#### FIGURE 12. HALL SENSOR SPACING

REMOTE POSITION SENSOR (HALL) SPACING FOR 60 DEGREE COMMUTATION

REMOTE POSITION SENSOR (HALL) SPACING FOR 120 DEGREE COMMUTATION

# FIGURE 10. TYPICAL POSITION, VELOCITY AND TORQUE CONTROL LOOP

MOTOR ANGLE / POSITION INFORMATION (HALL / RESOLVER / ENCODER)

NOTES:

FIGURE 13. PW- 8X225M6 POSITION OR VELOCITY HOOK- UP USING DSP MOTOR CONTROLLER

1. C8 is a ceramic capacitor and should be selected per DDC Application Note AN/ H- 7, MAGNUM Motor Drive Power Supply Capacitor Selection. 2. C9 is an electrolytic capacitor and should be selected per DDC Application Note AN/ H- 7, MAGNUM Motor Drive Power Supply Capacitor Selection.

4. Resistance and power of R20 (Load dump resistor), and R21 (OV Adjust resistor) is application specific. (See OV\_ADJ and REGEN\_CLAMP descriptions for details)

3. C10 is 22  $\mu\text{F},$  15 V electrolytic capacitor. C11 is 0.1  $\mu\text{F},$  50 V ceramic capacitor.

1ω

#### NOTES:

- 1. C8 is a ceramic capacitor and should be selected per DDC Application Note AN/ H- 7, MAGNUM Motor Drive Power Supply Capacitor Selection.

- 2. C9 is an electrolytic capacitor and should be selected per DDC Application Note AN/ H-7, MAGNUM Motor Drive Power Supply Capacitor Selection.

- 3. C10 is 22  $\mu\text{F},$  15 V electrolytic capacitor. C11 is 0.1  $\mu\text{F},$  50 V ceramic capacitor.

- 4. Resistance and power of R20 and R21 is application specific.

- 5. All resistors have a tolerance of ±10%, unless otherwise specified.

- 6. The CD4050 converts the +15V logic output of the UC- 2625 to +5V logic signals.

- 7. The CD4049 (or equivalent) inverts the upper signal from the UC- 2625.

- 8. 1% or better, depending on required accuracy.

- 9. Q 1 can be either IRML2402 or IRMU014 or IRLD014.

- 10. These high impedance inputs and summing junctions of the operational amplifiers are highly sensitive to noise.

- 11. These grounds should be closely tied together to reduce ground noise effect.

- 12. Connect Hall sensor inputs to motor shaft position sensors that are 120 electrical degrees apart. Motors with 60 electrical degree position sensor coding can be used if one or two of the position sensor signals are inverted.

14

PW-8X225 PRELIMINARY A-8/30/02-0

FIGURE 15. RESOLVER TO HALL SIGNAL CONVERSION CIRCUIT

<del>1</del>5

# FIGURE 16. PW-8X225M6 CURRENT DECOMMUTATION CIRCUIT

| TABLE 7. PIN ASSIGNMENTS |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PW-83225M6               | PW-84225M6                                                                                                    | PW-85225M6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| CONTROL PINS             |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| SLEEP_MODE               | SLEEP_MODE                                                                                                    | SLEEP_MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| TEST B *                 | TEST B *                                                                                                      | TEST B *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| TEST A *                 | TEST A *                                                                                                      | TEST A *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| VCC                      | VCC                                                                                                           | VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| VCC-RTN                  | VCC-RTN                                                                                                       | VCC-RTN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| N/C                      | N/C                                                                                                           | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| SC FAULT                 | SC FAULT                                                                                                      | SC FAULT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| N/C                      | N/C                                                                                                           | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| N/C                      | N/C                                                                                                           | REGEN_STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| N/C                      | N/C                                                                                                           | 0V_ADJ_HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| N/C                      | N/C                                                                                                           | 0V_ADJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| N/C                      | N/C                                                                                                           | 0V_ADJ_LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| N/C                      | VIREF                                                                                                         | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| TEST C *                 | TEST C *                                                                                                      | TEST C *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| AUTO RESET               | AUTO RESET                                                                                                    | AUTO RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| VCC                      | VCC                                                                                                           | VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| VCC-RTN                  | VCC-RTN                                                                                                       | VCC-RTN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| DISABLE/RESET            | DISABLE/RESET                                                                                                 | DISABLE/RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| LOWER                    | LOWER                                                                                                         | LOWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| UPPER                    | UPPER                                                                                                         | UPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| N/C                      | VCC-RTN                                                                                                       | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| N/C                      | Vdd                                                                                                           | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| N/C                      | VIRSENSE                                                                                                      | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| N/C                      | VIRSENSE_ABS                                                                                                  | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| N/C                      | OC FAULT                                                                                                      | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |