Data Sheet, DS1, June 2002

THE REAL PROPERTY

# GREEN 24+2G Ethernet Switch on Chip PLB 2224 Version 1.3

Wired Communications

Never stop thinking.

#### **Data Sheet**

| <b>Revision History:</b>        |                                                                                                   | 2002-06-03                         | DS1 |

|---------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------|-----|

| Previous Ve                     | ersion:                                                                                           | 01.01                              |     |

| Page                            | Subjects (n                                                                                       | najor changes since last revision) |     |

| Page 23<br>Page 202<br>Page 141 | Updated Package & Ball Pin Assignment,<br>Added AC characteristics,<br>Added Register Definitions |                                    |     |

| Page 106<br>Page 218            |                                                                                                   |                                    |     |

| Page 202<br>Page 196            |                                                                                                   |                                    |     |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com.

Edition 2002-06-03 Published by Infineon Technologies AG,

St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2002. All Rights Reserved.

#### **Attention please!**

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Table of Contents**

| <b>1</b><br>1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4<br>1.3<br>1.4<br>1.5                           | Overview<br>Introduction<br>Features<br>Ports & Network Interfaces<br>Switch Engine<br>Management<br>Benefits<br>Logic Symbol                                                                                                                                                                                                                                              | 12<br>13<br>13<br>13<br>13<br>14<br>14<br>14<br>15<br>16             |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.1.1                                                                                  | Typical Configurations       Pin Descriptions         Pin Definitions and Functions       Signal List                                                                                                                                                                                                                                                                      | . 20<br>. 23                                                         |

| <b>3</b><br>3.1<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.1.3<br>3.2.2<br>3.2.3<br>3.3<br>3.3<br>3.3.1 | Functional Description         Introduction         Functional Block Description         10/100/1000 Mbit/s Media Access Control (GMAC/MAC)         10/100 Ethernet Ports         Gigabit Ethernet Ports         MDIO Interface         Receive Module (RX)         Port Configuration, Status and Event Registers         Switch Controller         Packet Data Buffering | 29<br>31<br>31<br>31<br>31<br>31<br>32<br>33<br>33<br>34<br>36<br>36 |

| 3.3.2<br>3.3.3<br>3.3.3.1<br>3.3.3.2<br>3.3.3.3<br>3.3.3.4<br>3.3.3.5                                     | Address Resolution Logic (ARL)         Address Learning and Updating         PLB 2224 is not Configured for Auto Learning         Global Updating         Address Resolution         Address Aging         Configuring MA Table Using CPU                                                                                                                                  | 38<br>39<br>39<br>39<br>39<br>41                                     |

| 3.3.4<br>3.3.4.1<br>3.3.4.2<br>3.3.5<br>3.3.6                                                             | Port Tx and MAC Tx<br>Packet Queuing and Port Queues<br>Packet Scheduling<br>Packet & Queue Manager (PQC)<br>Transmit Module (TX)                                                                                                                                                                                                                                          | 41<br>42<br>42<br>42<br>42<br>43                                     |

| 3.3.6.1<br>3.3.6.2<br>3.3.6.3<br>3.3.7<br>3.3.7.1                                                         | Receiving and Sending Packets from the CPU Port                                                                                                                                                                                                                                                                                                                            | 44<br>45<br>45                                                       |

| Table of                                                                                                                           | Contents F                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 3.3.8<br>3.3.9<br>3.3.9.1<br>3.3.9.2<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.3<br>3.4.4<br>3.5                                    | LED Interface                                                                                                                                                                                                                                                                                                                                                                                    | . 49<br>. 49<br>. 50<br>. 52<br>. 52<br>. 52<br>. 52<br>. 52<br>. 52                                 |

| <b>4</b><br>4.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.2<br>4.2.1<br>4.2.2<br>4.2.2.1<br>4.3                                              | Data Structure         Internal Memory         VLAN Memories         PBL (Packet Buffer Link List) – 1 K x 2 Bytes         BCASTQ (BroadCAST Queue) – 256 x 2 Bytes x 32 = 16 KBytes         MA (MAC Address) - 64 KByte for up to 8 K Addresses         Indirect Access to the Memories         Access to EDRAM         Access to MIB Counters         VLAN Memories         Network Management | . 57<br>. 57<br>. 58<br>. 58<br>. 58<br>. 58<br>. 62<br>. 64<br>. 65<br>. 68                         |

| <b>5</b><br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.1.1<br>5.4.1.2 | Operational DescriptionData FlowFrame ReceptionIngress FilteringFrame ForwardingEgress FilteringEgress FilteringFrame TransmissionTerminating or Originating FramesCPU TransmissionFlow ControlStatistics RegistersPacket ClassificationExamplesDesired Filters and ActionsPattern Register Setup                                                                                                | . 72<br>. 72<br>. 72<br>. 72<br>. 72<br>. 73<br>. 73<br>. 73<br>. 73<br>. 73<br>. 73<br>. 73<br>. 73 |

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                                                                    | Packet Monitoring       Packet Prioritization         Packet Prioritization       Packet Prioritization         Trunking       Packet Prioritization         Address Learning       Packet Prioritization         MAC Address Table and Filtering Table       Packet Prioritization                                                                                                              | . 84<br>. 85<br>. 87                                                                                 |

#### **Table of Contents**

| 5.9.1                                                                                                                                                           | Accessing the Address Table                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 5.9.2                                                                                                                                                           | MAC Table Entry Formats                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| 5.9.3                                                                                                                                                           | Storage of the MAC Tables                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

| 5.9.4<br>5.9.4.1                                                                                                                                                | Forwarding Frames                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| 5.9.4.1                                                                                                                                                         | Frame Forwarding Example with SNMP                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| 5.9.4.2                                                                                                                                                         | Using the CPU                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| 5.10.1                                                                                                                                                          | VLAN Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| 5.10.1                                                                                                                                                          | VLAN Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| 5.10.2                                                                                                                                                          | VLAN Operation                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 5.10.3.1                                                                                                                                                        | VLAN Memories                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| 5.10.4                                                                                                                                                          | VLAN Ingress Filter                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 5.10.5                                                                                                                                                          | VLAN Tag Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 5.10.6                                                                                                                                                          | VLAN Security                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| 5.10.6.1                                                                                                                                                        | VLAN Membership/Port List Determination                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| 5.11                                                                                                                                                            | Spanning Tree                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| 5.11.1                                                                                                                                                          | Description of Spanning Tree Support                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| 5.11.1.1                                                                                                                                                        | Spanning Tree Topologies                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

| 5.11.2                                                                                                                                                          | Spanning Tree Protocol Support                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 5.12                                                                                                                                                            | SNMP and RMON MIBs                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| 5.13                                                                                                                                                            | LED                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

|                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

| 6                                                                                                                                                               | Interface Description                                                                                                                                                                                                                                                                                                                                                                                                                                 | 105                                                                                                                        |

| <b>6</b>                                                                                                                                                        | Interface Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

| 6.1                                                                                                                                                             | External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105                                                                                                                        |

| 6.1<br>6.1.1                                                                                                                                                    | External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105<br>105                                                                                                                 |

| 6.1<br>6.1.1<br>6.1.2                                                                                                                                           | External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105<br>105<br>105                                                                                                          |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3                                                                                                                                  | External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105<br>105<br>105<br>105                                                                                                   |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                                                                                         | External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105<br>105<br>105<br>105<br>105                                                                                            |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                                                                                | External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105<br>105<br>105<br>105<br>105<br>105                                                                                     |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                                                                                         | External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105<br>105<br>105<br>105<br>105                                                                                            |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                                                                                       | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface                                                                                                                                                                                                                                                                                                                    | 105<br>105<br>105<br>105<br>105<br>105<br>105                                                                              |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2                                                                                                | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface                                                                                                                                                                                                                                                                                        | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106                                                                       |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1                                                                                       | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface                                                                                                                                                                                                                                                                       | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106                                                                       |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1<br>6.2.2                                                                              | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface<br>I2C Interface                                                                                                                                                                                                                                                      | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106<br>106                                                                |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1<br>6.2.2<br>6.2.2.1                                                                   | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface<br>I2C Interface<br>The PCI Local Bus Interface                                                                                                                                                                                                                       | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106<br>106<br>106<br>106                                                  |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1<br>6.2.2<br>6.2.2.1<br>6.2.2.1<br>6.2.2.2                                             | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface<br>I2C Interface<br>The PCI Local Bus Interface<br>The Generic Interface                                                                                                                                                                                              | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106<br>106<br>106<br>106                                                  |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1<br>6.2.2<br>6.2.2.1<br>6.2.2.2<br>6.2.2.3                                             | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface<br>I2C Interface<br>The PCI Local Bus Interface<br>The Generic Interface<br>PCI Interface Details                                                                                                                                                                     | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106<br>106<br>106<br>106<br>107<br>109<br>111                             |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1<br>6.2.2<br>6.2.2.1<br>6.2.2.2<br>6.2.2.1<br>6.2.2.2<br>6.2.2.3<br>6.2.2.4            | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface<br>I2C Interface<br>The PCI Local Bus Interface<br>The Generic Interface<br>PCI Interface Details<br>Generic Interface Signals Description                                                                                                                            | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106<br>106<br>106<br>106<br>107<br>109<br>111                             |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1<br>6.2.2<br>6.2.2.1<br>6.2.2.2<br>6.2.2.3<br>6.2.2.3<br>6.2.2.4<br>6.2.2.5            | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface<br>I2C Interface<br>The PCI Local Bus Interface<br>The Generic Interface<br>PCI Interface Details<br>Generic Interface Signals Description<br>IIC Interface Signals                                                                                                   | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106<br>106<br>106<br>106<br>107<br>109<br>111<br>112                      |

| 6.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1<br>6.2.2<br>6.2.2.1<br>6.2.2.2<br>6.2.2.3<br>6.2.2.4<br>6.2.2.5<br>6.2.3<br>6.2.3.1<br>6.2.3.2 | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface<br>I2C Interface<br>The PCI Local Bus Interface<br>The Generic Interface<br>PCI Interface Details<br>Generic Interface Signals Description<br>IIC Interface Signals<br>I2C Bus Concept<br>Start and Stop Conditions<br>Application Note for IIC Interface of PLB 2224 | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106<br>106<br>106<br>106<br>106<br>107<br>109<br>111<br>112<br>113<br>114 |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.2<br>6.2.1<br>6.2.2.1<br>6.2.2.1<br>6.2.2.2<br>6.2.2.3<br>6.2.2.4<br>6.2.2.5<br>6.2.3<br>6.2.3.1 | External Interfaces<br>10/100 PHYs<br>Gigabit PHYs<br>MDIO Interface<br>LED Interface<br>JTAG Interface<br>Clock / Reset Interface<br>CPU and EEPROM Interface<br>CPU Interface<br>I2C Interface<br>The PCI Local Bus Interface<br>The Generic Interface<br>PCI Interface Details<br>Generic Interface Signals Description<br>IIC Interface Signals<br>I2C Bus Concept<br>Start and Stop Conditions                                                   | 105<br>105<br>105<br>105<br>105<br>105<br>105<br>106<br>106<br>106<br>106<br>106<br>107<br>109<br>111<br>112<br>113<br>114 |

#### **Table of Contents**

| 7      | Register Description                                      | 121 |

|--------|-----------------------------------------------------------|-----|

| 7.1    | PCI Configuration Phase                                   | 122 |

| 7.2    | Switch Configuration Phase                                | 123 |

| 7.2.1  | Chip Level Configuration                                  | 123 |

| 7.2.2  | Port Level Configuration and Monitoring                   | 124 |

| 7.2.3  | Switch Level Configuration                                | 126 |

| 7.2.4  | VLAN and Bridge Configuration                             | 128 |

| 7.2.5  | BPDU Transmission and Receiving                           | 130 |

| 7.3    | PLB 2224 PCI Configuration Registers                      | 131 |

| 7.3.1  | Register 0x00, PCI Configuration Space ID                 | 132 |

| 7.3.2  | Register 0x04, PCI Configuration Space Status and Command | 133 |

| 7.3.3  | Register 0x08, PCI Configuration Class                    | 137 |

| 7.3.4  | Register 0x0C, PCI Configuration Miscellaneous 0          | 138 |

| 7.3.5  | Register 0x3C, PCI Configuration Miscellaneous 1          | 140 |

| 7.4    |                                                           | 141 |

| 7.4.1  | Chip Configuration Register                               | 141 |

| 7.4.2  | Chip Type Register                                        | 144 |

| 7.4.3  | Switch Configuration Register                             | 145 |

| 7.4.4  | Switch Status and Mask Register                           | 151 |

| 7.4.5  | Port Status Register                                      | 154 |

| 7.4.6  | Port Event Register                                       | 155 |

| 7.4.7  | Port Underrun/Overrun Register                            | 155 |

| 7.4.8  | Port MII Register                                         | 156 |

| 7.4.9  | Port Monitor Register                                     | 157 |

| 7.4.10 | Port Priority Register                                    | 158 |

| 7.4.11 | Port Trunk Register                                       | 158 |

| 7.4.12 | Port Bridge State Register                                | 159 |

| 7.4.13 | Portlist_1023 Register                                    | 160 |

| 7.4.14 | Port Index Register_20_0                                  | 161 |

| 7.4.15 | DA Index Register                                         |     |

| 7.4.16 | Memory Upper Address Register                             | 163 |

| 7.4.17 | Memory Access Register                                    | 165 |

| 7.4.18 | CMAC Data Register                                        | 167 |

| 7.4.19 | CMAC RX Register                                          | 167 |

| 7.4.20 | CMAC TX Register                                          | 169 |

| 7.4.21 | —                                                         | 169 |

| 7.4.22 | ARL Register                                              | 170 |

| 7.4.23 | FREEQ Register                                            | 172 |

| 7.4.24 | FREEQ_CNT                                                 | 173 |

| 7.4.25 | CPU_TXQ26 Count Register                                  | 173 |

| 7.4.26 | CPU_TXQ27                                                 | 174 |

| 7.4.27 | CPU Water Mark Register                                   | 174 |

#### **Table of Contents**

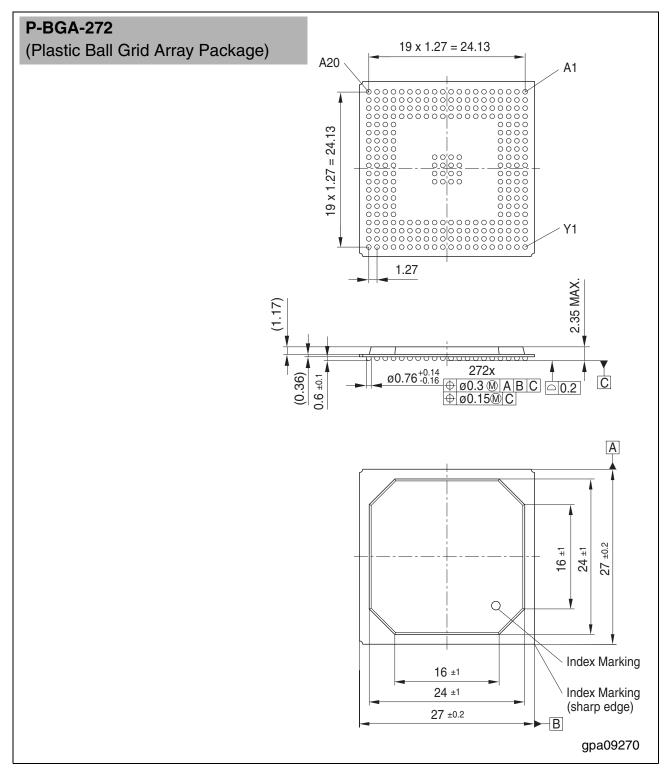

| 9                                                                       | Package Details (P-BGA-272)                                                                                                                                                                                                                                                                               | 218                                    |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

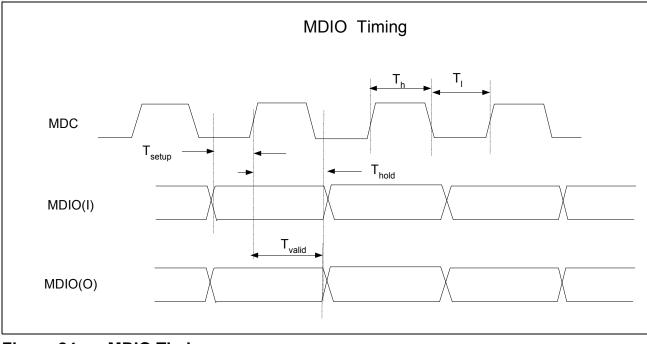

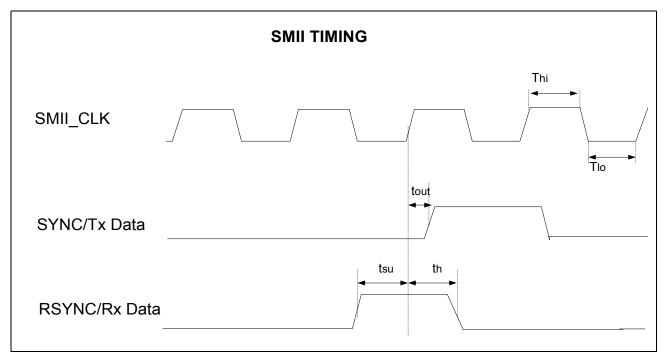

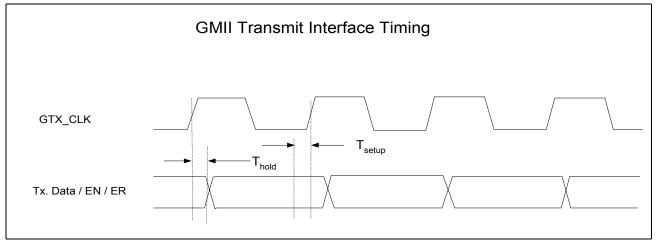

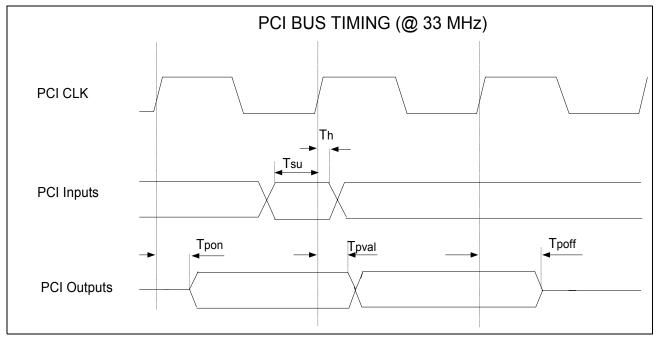

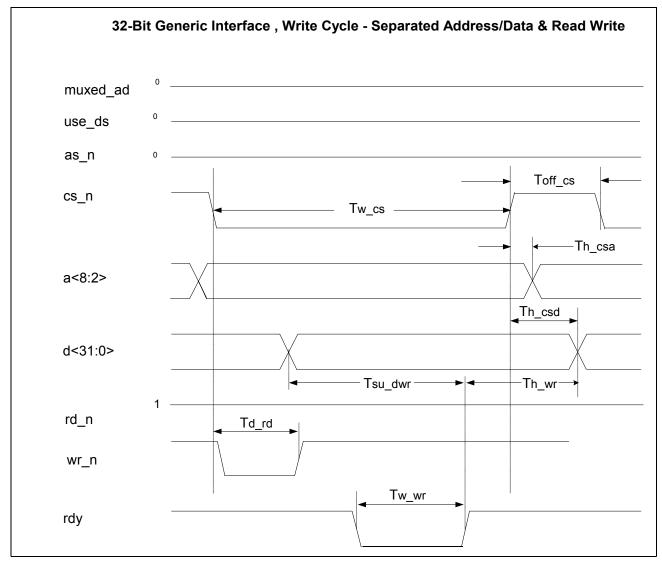

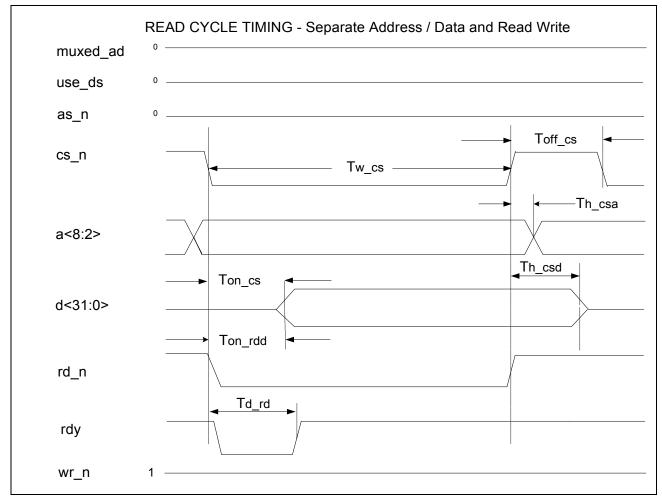

| 8<br>8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7 | Electrical Characteristics<br>AC Characteristics .<br>MDIO Interface Timing Details .<br>SMII Interface Timing Details .<br>GMII/TBI Interface Timing .<br>PCI Interface / Generic Interface Timing .<br>Timing Parameters ( Figure 29 to Figure 36 ) .<br>Serial LED Interface Timing .<br>IIC Timings . | 202<br>203<br>204<br>205<br>213<br>214 |

| -                                                                       |                                                                                                                                                                                                                                                                                                           |                                        |

| 7.4.49                                                                  | G_PCS_2 Register                                                                                                                                                                                                                                                                                          |                                        |

| 7.4.48                                                                  | G PCS 1 Register                                                                                                                                                                                                                                                                                          | 197                                    |

| 7.4.40                                                                  | G_PCS0 Register / Gport Link Status Register                                                                                                                                                                                                                                                              | 195                                    |

| 7.4.45                                                                  | G Mode Register                                                                                                                                                                                                                                                                                           | 192                                    |

| 7.4.44                                                                  | GMAC Registers                                                                                                                                                                                                                                                                                            |                                        |

| 7.4.43                                                                  | Enable Filtering Register                                                                                                                                                                                                                                                                                 |                                        |

| 7.4.42                                                                  | Action_Table Registers                                                                                                                                                                                                                                                                                    | 189                                    |

| 7.4.41                                                                  | Offset Group Register                                                                                                                                                                                                                                                                                     | 188                                    |

| 7.4.40                                                                  | OFFSET Registers                                                                                                                                                                                                                                                                                          |                                        |

| 7.4.39                                                                  |                                                                                                                                                                                                                                                                                                           |                                        |

| 7.4.38<br>7.4.39                                                        |                                                                                                                                                                                                                                                                                                           |                                        |

| 7.4.37                                                                  | Port Index Register 26_21                                                                                                                                                                                                                                                                                 |                                        |

| 7.4.36                                                                  | VLAN Ingress Filter                                                                                                                                                                                                                                                                                       |                                        |

| 7.4.35                                                                  | 5 5                                                                                                                                                                                                                                                                                                       | 182                                    |

| 7.4.34                                                                  | Port Cfi Register                                                                                                                                                                                                                                                                                         | 182                                    |

| 7.4.33                                                                  | Egress Priority Table                                                                                                                                                                                                                                                                                     | 181                                    |

| 7.4.32                                                                  |                                                                                                                                                                                                                                                                                                           |                                        |

| 7.4.31                                                                  | Gport Watermark Control (RX)                                                                                                                                                                                                                                                                              |                                        |

| 7.4.30                                                                  | Gport Watermark Control (TX)                                                                                                                                                                                                                                                                              |                                        |

| 7.4.29                                                                  | FE Watermark Control (RX)                                                                                                                                                                                                                                                                                 |                                        |

| 7.4.28                                                                  | FE Watermark Control (TX)                                                                                                                                                                                                                                                                                 |                                        |

|                                                                         |                                                                                                                                                                                                                                                                                                           | •                                      |

#### List of Figures

| List of Figure | es F                                                                | Page |

|----------------|---------------------------------------------------------------------|------|

| Figure 1       | Logic Symbol                                                        | . 15 |

| Figure 2       | General System Integration                                          |      |

| Figure 3       | 48 x 10/100 Mbit/s Port Managed Solution                            | . 17 |

| Figure 4       | MDU/MTU Application                                                 | . 18 |

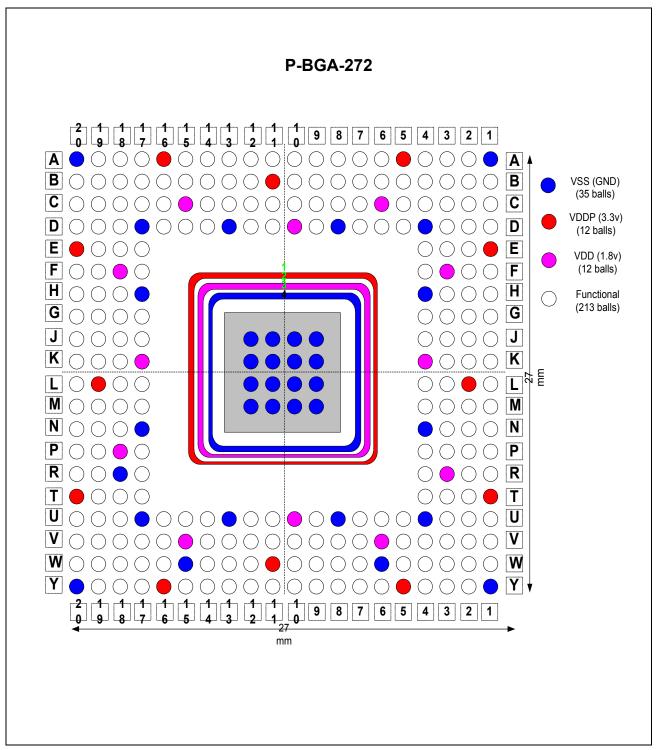

| Figure 5       | Pin Configuration (Bottom View: Power & Ground Pins)                | . 20 |

| Figure 6       | Pin Configuration (Top View: Functional Part 1).                    | . 21 |

| Figure 7       | Pin Configuration (Top View: Functional Part 2)                     | . 21 |

| Figure 8       | Pin Configuration (Top View: Functional Part 3)                     | . 22 |

| Figure 9       | Pin Configuration (Top View: Functional Part 3)                     | . 22 |

| Figure 10      | Functional Block Diagram                                            | . 28 |

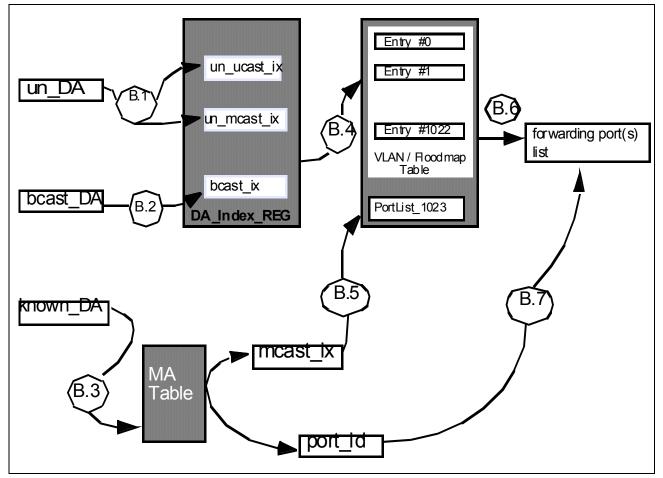

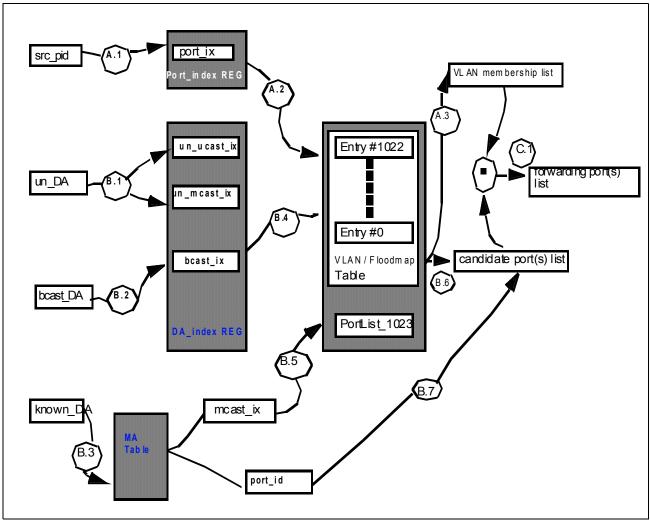

| Figure 11      | Destination Port List Creation (VLAN's Disabled)                    | . 40 |

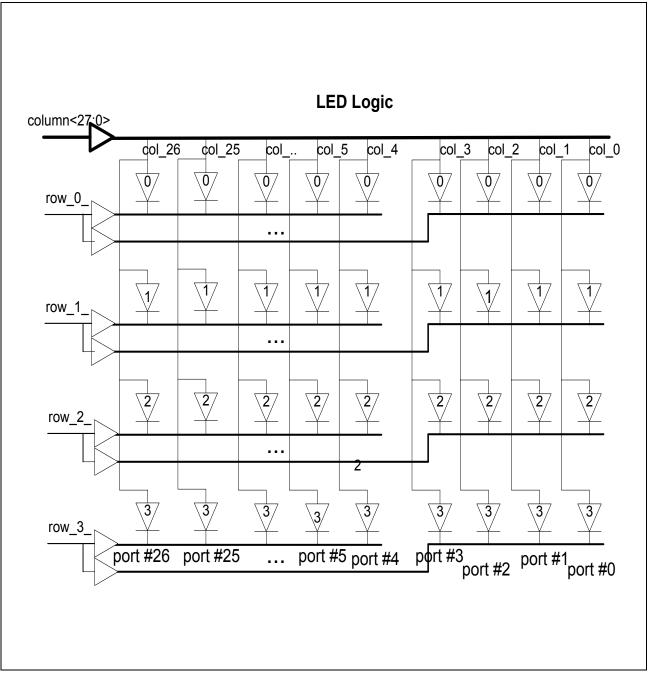

| Figure 12      | Matrix Mode LED Connection                                          |      |

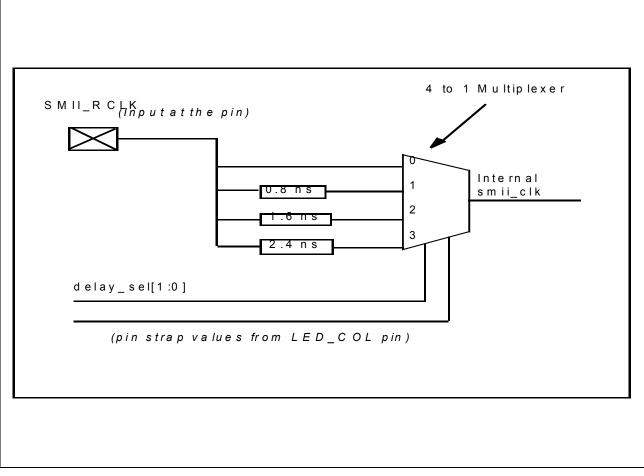

| Figure 13      | Delay Control for SMII Clock Internally                             | . 51 |

| Figure 14      | Flow Control Mechanism                                              |      |

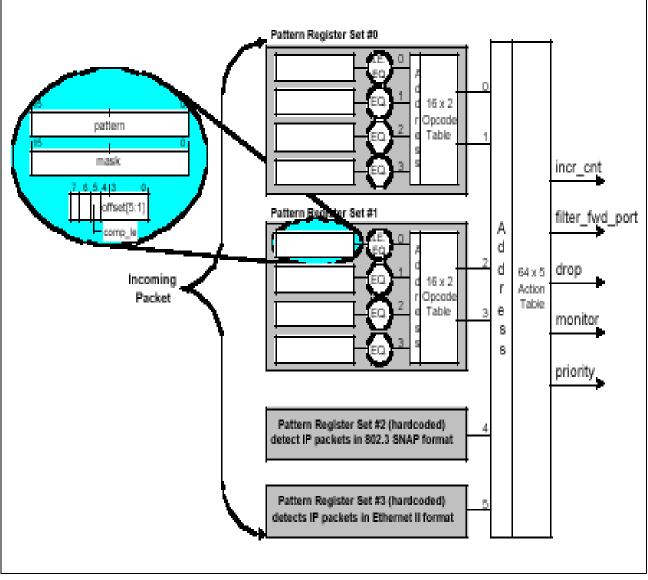

| Figure 15      | Packet Classification                                               |      |

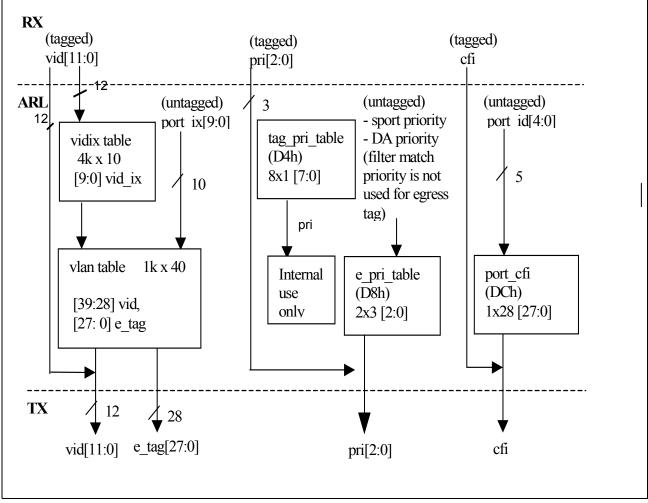

| Figure 16      | VLAN Tag Conversion                                                 |      |

| Figure 17      | Address Resolution/Destination Port List Creation (VLAN Enabled).   |      |

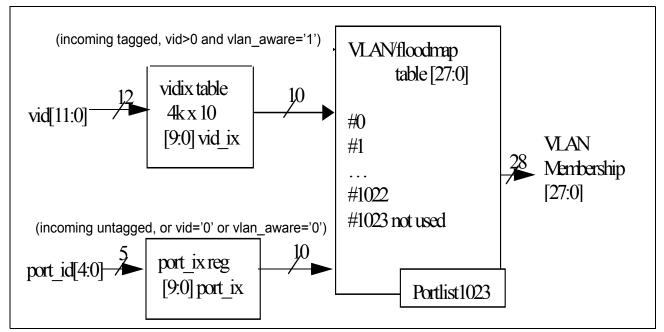

| Figure 18      | VLAN Membership Determination                                       |      |

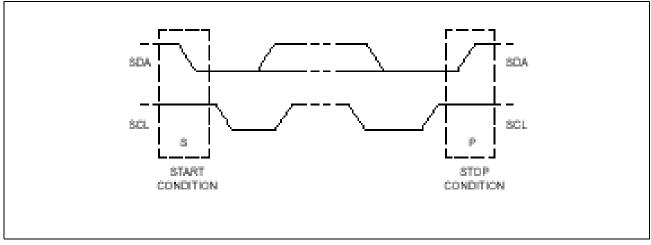

| Figure 19      | Start & Stop Condition                                              |      |

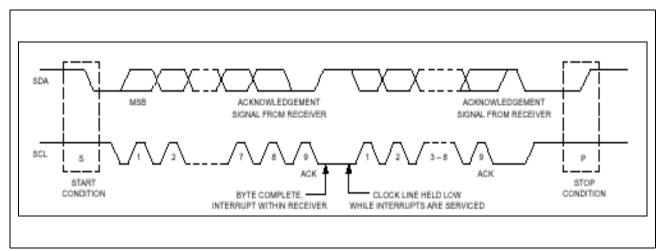

| Figure 20      | Data Transfer on the IIC Bus                                        |      |

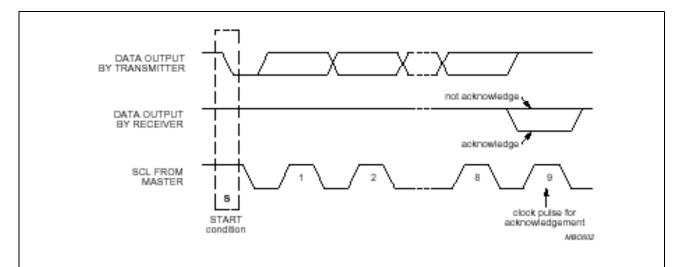

| Figure 21      | Acknowledge on the I2C Bus                                          |      |

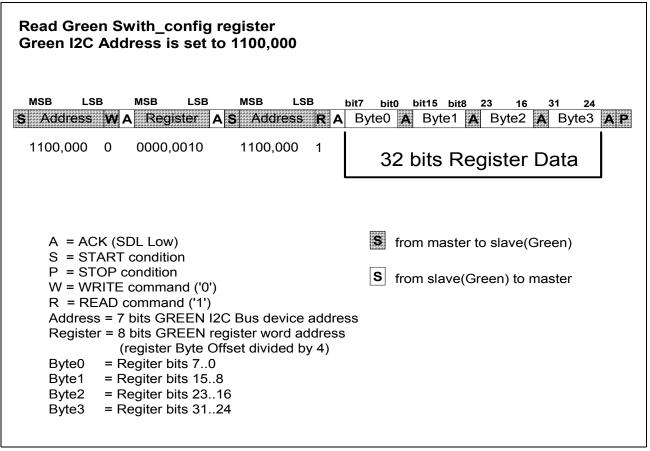

| Figure 22      | Read Protocol for IIC Bus                                           |      |

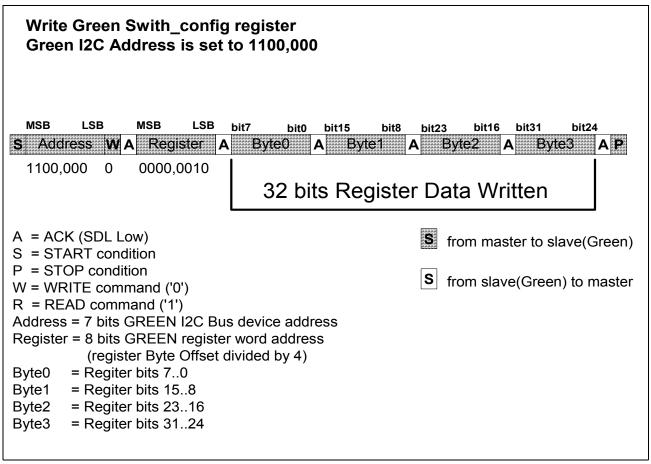

| Figure 23      | Write Protocol for IIC Interface.                                   |      |

| Figure 24      | MDIO Timing                                                         |      |

| Figure 25      | SMII Interface Timing.                                              |      |

| Figure 26      | GMII/TBI Tx. Interface Timing                                       |      |

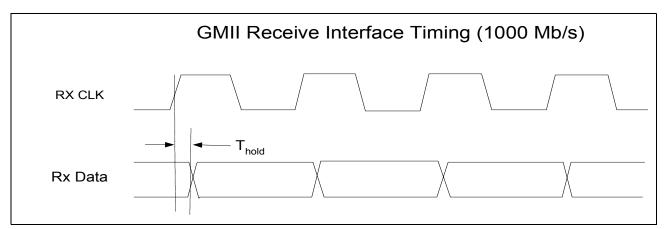

| Figure 27      | GMII/TBI Rx. Interface Timing                                       |      |

| Figure 28      | PCI / Generic Interface Timing.                                     |      |

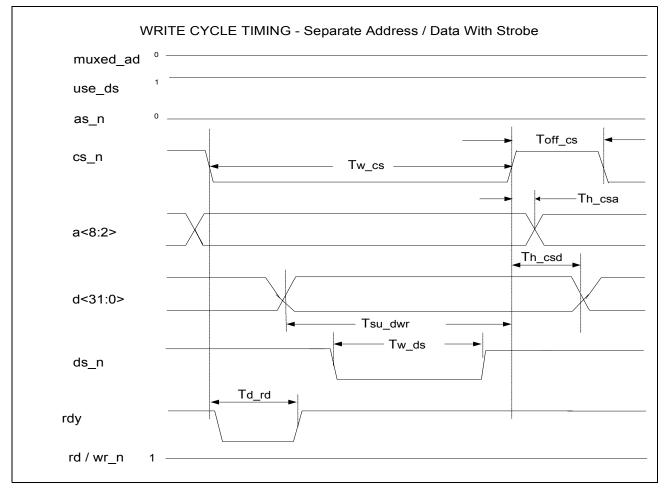

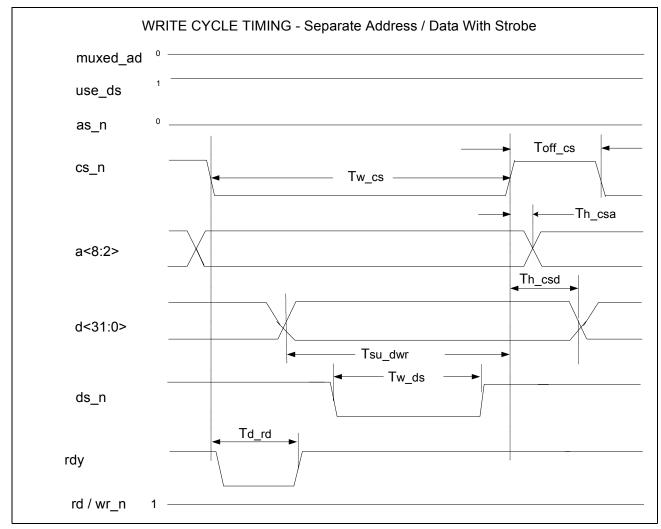

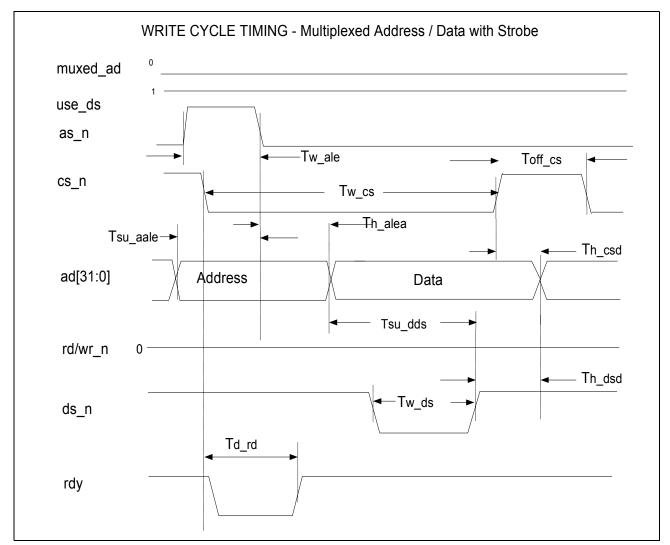

| Figure 29      | 32-Bit Generic Interface Write Cycle - Separate Addr/Data / R / W.  |      |

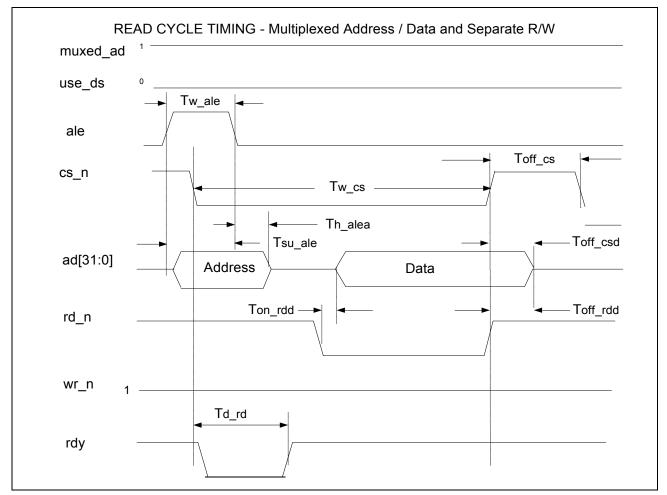

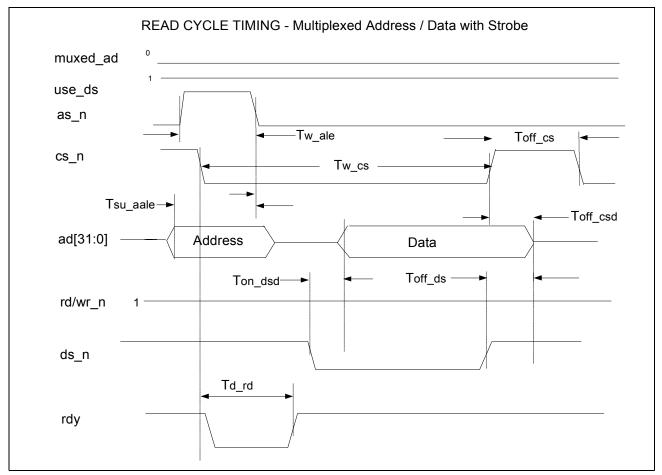

| Figure 30      | 32-Bit Generic Interface Read Cycle - Separate Addr / Data / R / W. | 207  |

| Figure 31      | 32-Bit Generic Interface Write Cycle - Separate Addr / Data with    | 000  |

| <b>-</b> : 00  | Strobe                                                              | 208  |

| Figure 32      | 32-Bit Generic Interface Write Cycle - Separate Addr / Data with    | 000  |

|                |                                                                     | .209 |

| Figure 33      | 32-Bit Generic Interface Read - Muxed Addr / Data & Separate R/W    |      |

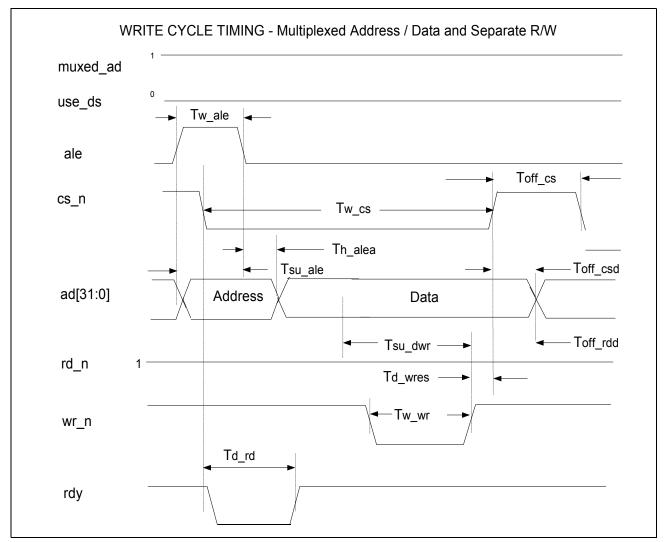

| Figure 34      | 32-Bit Generic Interface Write - Muxed Addr / Data & Separate R/W   | 211  |

| Figure 35      | 32-Bit Generic Interface Write Cycle - Muxed Addr / Data with       | 040  |

| Figure 20      | Strobe                                                              | 212  |

| Figure 36      | 32 Bit Generic Interface Read Cycle - Muxed Addr/Data with Strobe   |      |

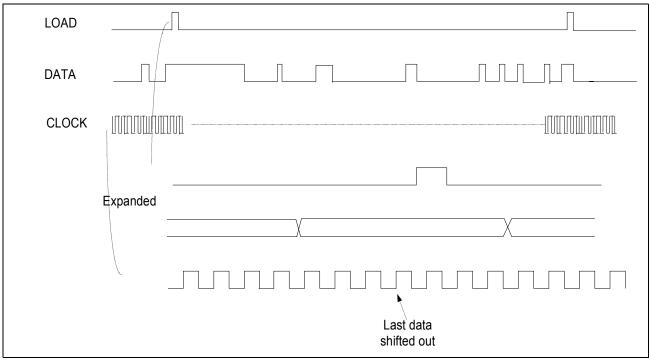

| Figure 37      |                                                                     | 214  |

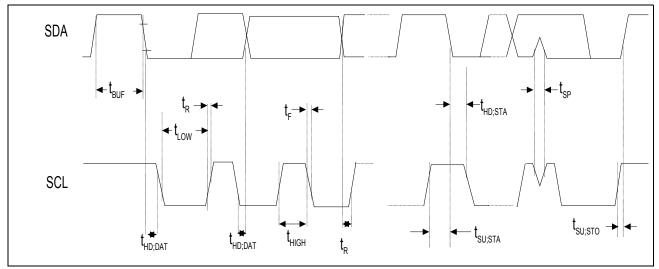

| Figure 38      | IIC Interface Timing                                                | 215  |

#### List of Tables

|          |                                                            | -    |

|----------|------------------------------------------------------------|------|

| Table 1  | Typical Configurations Using PLB 2224                      | . 19 |

| Table 2  | Pin Descriptions                                           |      |

| Table 3  | PBH Header Format                                          |      |

| Table 4  | Packet Buffer Header                                       |      |

| Table 5  | MA Entry Formats for Unicast and Multicast Addresses       |      |

| Table 6  | MA Table Entry Types                                       |      |

| Table 7  | PBH Packet Length for Different crc_gen & pkt_padding Bits |      |

| Table 8  | Matrix LED Modes (per port)                                |      |

| Table 9  | Power Strapping Table                                      |      |

| Table 10 | Spanning Tree States and Actions                           |      |

| Table 11 | Register Table                                             |      |

| Table 12 | EDRAM Details                                              | . 56 |

| Table 13 | SRAM Details                                               |      |

| Table 14 | Internal Memories                                          |      |

| Table 15 | VLAN Memories                                              | . 57 |

| Table 16 | PBL Format                                                 | . 58 |

| Table 17 | Broadcast Queue Entry Format                               | . 59 |

| Table 18 | Packet Buffer Header                                       | . 59 |

| Table 19 | MA Format for Unicast Entry                                | . 60 |

| Table 20 | MA Format for Multicast Entry                              | . 60 |

| Table 21 | Memory Upper Address Register.                             | . 62 |

| Table 22 | Memory Access Register                                     | . 63 |

| Table 23 | VLAN Memories.                                             | . 68 |

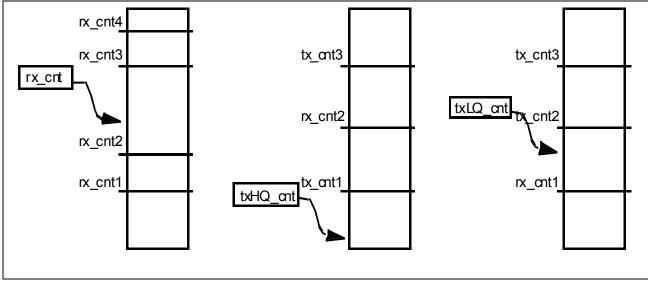

| Table 24 | Rx Counters                                                | . 76 |

| Table 25 | Tx Counters                                                | . 77 |

| Table 26 | VLAN Rx Counters (per VLAN)                                | . 77 |

| Table 27 | VLAN Tx Counters (per VLAN)                                | . 77 |

| Table 28 | Group[3] Set to Detect IP in Ethernet II Format            | . 81 |

| Table 29 | Group[2] Set to Detect IP in 802.3 SNAP                    | . 81 |

| Table 30 | Group[1] Used for IP Packets in Ethernet II Format         | . 82 |

| Table 31 | Group[0] -Used for IP packets in 802.3 SNAP Format         | . 82 |

| Table 32 | Group[3] -Op Code                                          | . 82 |

| Table 33 | Action Code Table                                          | . 83 |

| Table 34 | Trunk Combination.                                         | . 85 |

| Table 35 | MA Entry Formats for Unicast and Multicast Addresses       | . 88 |

| Table 36 | VLAN Table Entry Format                                    | . 90 |

| Table 37 | VLAN Memories                                              | . 91 |

| Table 38 | VLAN Ingress Filter                                        | . 92 |

| Table 39 | Qualification of Packets                                   | . 96 |

| Table 40 | Spanning Tree States and Actions                           | . 99 |

| Table 41 | SNMP Receiving Counters                                    | 101  |

| Table 42 | SNMP Transmitting Counters                                 | 101  |

#### List of Tables

| Table 43 | LED Configurations                                   | 103 |

|----------|------------------------------------------------------|-----|

| Table 44 | Correspondence between PCI/Generic and IIC Interface | 108 |

| Table 45 | PCI Interface Signals                                | 109 |

| Table 46 | Generic Interface Signals.                           | 111 |

| Table 47 | I2C Interface Signals                                | 112 |

| Table 48 | Definition of IIC Bus Terminology                    | 113 |

| Table 49 | PCI Command Definition                               | 119 |

| Table 50 | PCI Configuration Register Address Space             | 120 |

| Table 51 |                                                      | 123 |

| Table 52 | Port Level Configuration and Monitoring              | 124 |

| Table 53 |                                                      | 126 |

| Table 54 | VLAN and Bridge Configuration                        | 128 |

| Table 55 | Filtering Configuration                              |     |

| Table 56 |                                                      | 129 |

| Table 57 | BPDU Transmission and Reception                      | 130 |

| Table 58 | PCI Configuration Registers                          | 131 |

| Table 59 |                                                      | 132 |

| Table 60 | •                                                    | 137 |

| Table 61 | Register 0x0C PCI Config Miscellaneous0              | 138 |

| Table 62 |                                                      | 139 |

| Table 63 | • •                                                  | 140 |

| Table 64 | • •                                                  | 141 |

| Table 65 | Chip_type Register                                   | 144 |

| Table 66 |                                                      | 145 |

| Table 67 |                                                      | 152 |

| Table 68 | Port Status Register                                 | 154 |

| Table 69 | -                                                    | 155 |

| Table 70 |                                                      | 156 |

| Table 71 | Port MII Register                                    | 157 |

| Table 72 | Port Monitor Register                                | 158 |

| Table 73 | Port Priority Register                               |     |

| Table 74 |                                                      | 159 |

| Table 75 | -                                                    | 160 |

| Table 76 | Portlist_1023 Register                               | 161 |

| Table 77 | Port Index Register_20_0                             | 161 |

| Table 78 | DA Index Register                                    | 163 |

| Table 79 |                                                      | 163 |

| Table 80 | Memory Access Register                               | 165 |

| Table 81 | CMAC Data Register                                   | 167 |

| Table 82 | CMAC RX Register                                     | 167 |

| Table 83 | CMAC TX Register                                     | 169 |

| Table 84 | CMAC_TX1 Register                                    | 170 |

## List of Tables

| Table 85  | ARL Register                               | 170 |

|-----------|--------------------------------------------|-----|

| Table 86  | FREEQ Register 1                           | 172 |

| Table 87  | FREEQ_CNT                                  | 173 |

| Table 88  | CPU TXQ26 Count Register 1                 | 173 |

| Table 89  | CPU_TXQ27 Register 1                       | 174 |

| Table 90  | CPU Water Mark Register 1                  | 175 |

| Table 91  | FE TX Watermark Control Register           | 176 |

| Table 92  | FE Rx Watermark Control Register 1         | 177 |

| Table 93  | Gport TX Watermark Control Register 1      | 178 |

| Table 94  | Gport RX Watermark Control Register 1      | 179 |

| Table 95  | Tag Priority Table Register    1           | 181 |

| Table 96  | Egress Priority Table 1                    | 182 |

| Table 97  | Port Cfi Register                          | 182 |

| Table 98  | VLAN Aware/inTag Control Register 1        | 183 |

| Table 99  | VLAN Ingress Filter 1                      | 184 |

| Table 100 | Port Index Register 26_21 1                | 184 |

| Table 101 |                                            | 185 |

| Table 102 |                                            | 186 |

| Table 103 | OFFSET Group0 Registers 1                  | 187 |

| Table 104 |                                            | 188 |

| Table 105 |                                            | 189 |

| Table 106 | Action_Table Registers 1                   | 190 |

| Table 107 |                                            | 192 |

| Table 108 |                                            | 192 |

| Table 109 | G_Mode Register 1                          | 193 |

| Table 110 |                                            | 196 |

| Table 111 |                                            | 198 |

| Table 112 | G_PCS_2 Register 1                         | 199 |

| Table 113 |                                            | 200 |

| Table 114 | Operating Range                            | 200 |

| Table 115 | DC Characteristic                          | 201 |

| Table 116 | AC Characteristics MDIO                    | 202 |

| Table 117 | AC Characteristics - SMII                  | 203 |

| Table 118 | AC Characteristics GMII Tx. Interface      | 204 |

| Table 119 | AC Characteristics GMII Rx. Interface      | 205 |

| Table 120 | AC Characteristics PCI                     | 205 |

| Table 121 | 32-Bit Generic Interface Timing Parameters | 213 |

| Table 122 | Serial LED Interface Timing                |     |

| Table 123 | IIC Bus Timing Parameters                  | 215 |

| Table 124 | Capacitances                               |     |

|           |                                            |     |

## 1.1 Introduction

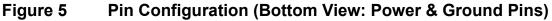

PLB 2224 is a single chip Multiport Ethernet switch, with embedded Frame Buffer & Address Table memory. PLB 2224 is a single-chip solution for building high-port count workgroups and wiring closet Fast Ethernet switches. The architecture allows the device to implement standalone and stackable Fast Ethernet switches, which are low-cost, low part-count and have low power implementations.

PLB 2224 provides a high level of integration, It provides 24 Fast Ethernet and 2 Gigabit Ethernet ports. It is capable of supporting wire-speed, full-duplex packet traffic on all ports under worst-case traffic conditions. PLB 2224 Provides 32-bit PCI or generic CPU interface as well as a 2-wire master/slave serial interface for connecting an external Micro-controller for Managed Switch Implementation.

The device is based on Infineon 0.18  $\mu$  Embedded DRAM process & integrates all the necessary Memory required to implement Full duplex wire speed switch for 24 Fast ethernet ports with 2 Gigabit uplink ports. Hence the device can be targeted for both high performance ethernet core switches or high density ethernet edge switches. The on chip Frame Buffer is organized as 2 banks of 256-bit wide embedded DRAM, operating at 100 MHz, providing up to 16 Gbit/s memory bandwidth. PLB 2224 can achieve packet forwarding/switching speed of up to 8 Million packets per second. It provides 2 priority queues per port to enable time sensitive data have access to the network with minimal delay. SMII support on 10/100 Mbit/s interfaces & GMII/MII/TBI on Gigabit interface is provided. Matrix & serial interface for port status LEDs is provided. Embedded Packet buffer & address table allows low pin count packaging in a P-BGA-272 pin package. This "system on chip" solution enables system designers to develop cost effective unmanaged/managed/intelligent switches. The core logic operates at 1.8 V & I/Os operate at 3.3 V.

## 24+2G Ethernet Switch on Chip GREEN

## Version 1.3

# 1.2 Features

## 1.2.1 Ports & Network Interfaces

- High performance Gigabit Fast Ethernet switch controller, wire-speed operation on every port.

- Single chip with twentyfour x 10/100 Mbit/s and two x Gbit/s Ports (10/100/1000 Mbit/s ports)

- SMII Interface on 10/100 Mbit/s ports supports autonegotiation for speed and duplex setting.

- GMII and PMA Interface on Gigabit ports (full-duplex only) and optional MII interface support on Gigabit ports, Half duplex is supported in 10/100 Mbit/s mode only.

- Full-duplex IEEE 802.3x flow control and collision-based congestion control in halfduplex

- Provide packet switching functions between 1000/100/10 Mbit/s & fast Ethernet ports

- Support 802.3ad based port trunking for high-bandwidth inter-switch links.

- 2/4/8 10/100 Ports or 2 Gigabit ports can be combined to form trunks multiple trunks per device

# 1.2.2 Switch Engine

- Support wire-speed switching with low latency using store-and-forward switching. Fast latency time for both unicast and broadcast. Best broadcast throughput performance

- Address learning and resolution up to 8 K entries, auto-learning and auto-aging.

- Two priority levels per port for CoS support WFQ scheduling.

- Supports both port-based and tagged 802.1Q VLAN scheme for up to 1 K Active VLANs

- Port monitoring and forwarding of packets to the CPU port

| Туре     | Package   |

|----------|-----------|

| PLB 2224 | P-BGA-272 |

## 1.2.3 Management

- Allow network administrators to create Layer 2 MAC-address based filters to constrain users to particular destinations, implement basic Layer 2 security, and simulate a multicast environment using static filters.

- Support extensive traffic/network management through SNMP, four critical groups of RMON (statistics, history, alarms, events) and MIBs.

- Supports IEEE 802.1D Spanning Tree for network loop detection and disabling (particularly useful in larger networks) and for fault-tolerant connectivity supports Secure Mode Traffic filtering on a per port basis

- PCI compliant 32-bit, 33 MHz CPU interface. Can also be used as a generic interface with multiplexed or separate address/data. Glueless Interface to many 32-bit processors.

- 2-wire serial interface for configuration I<sup>2</sup>C E2PROM or CPU connection for unmanaged, minimally managed or stackable switches.

- Supports local console and Telnet interface for operation, administration, and maintenance. Simple to use and troubleshoot, with minimum reconfigurations required. New software releases can be downloaded either locally or over the network

- Glue less LED interfaces four status LEDs per port for displaying buffer utilization at each port (Optional Serial interface for LEDs for customer specific glue logic)

## 1.2.4 Benefits

• Embedded Packet Buffer & Address Table enables low cost system design.Support for up to 1 K Port/Tag based VLAN (IEEE 802.1Q) with up to 3 MIBs per VLAN, enables application in MDU/MTU markets.

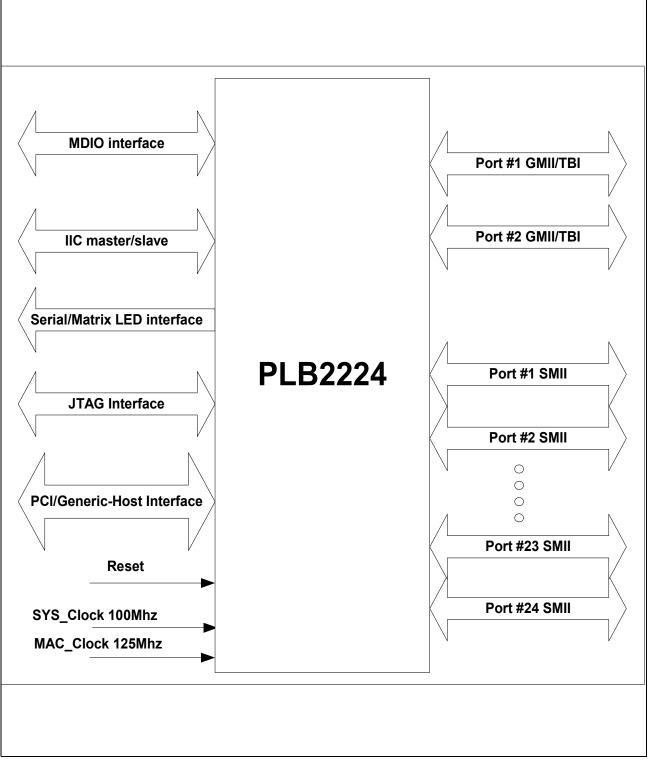

# 1.3 Logic Symbol

• The valous interfaces that are available on PLB 2224 is shown in the figure below.

Figure 1 Logic Symbol

# 1.4 Typical Applications

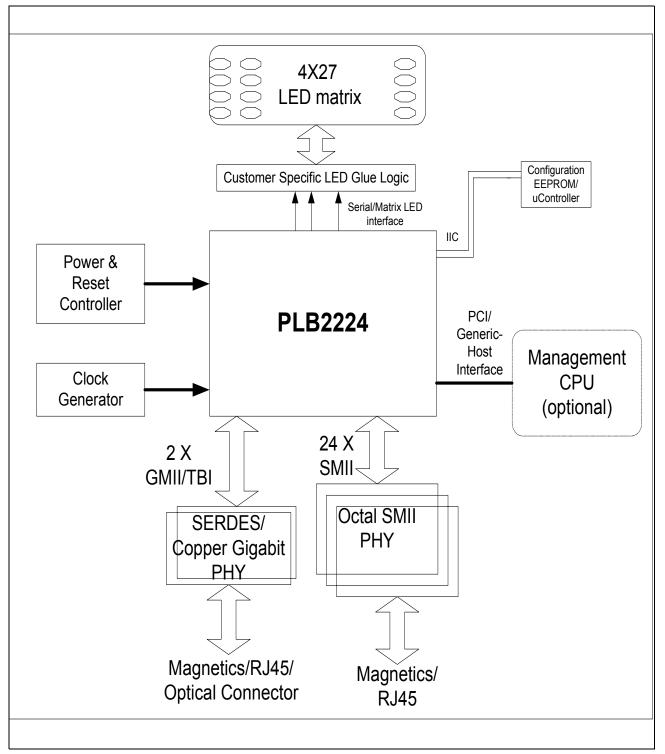

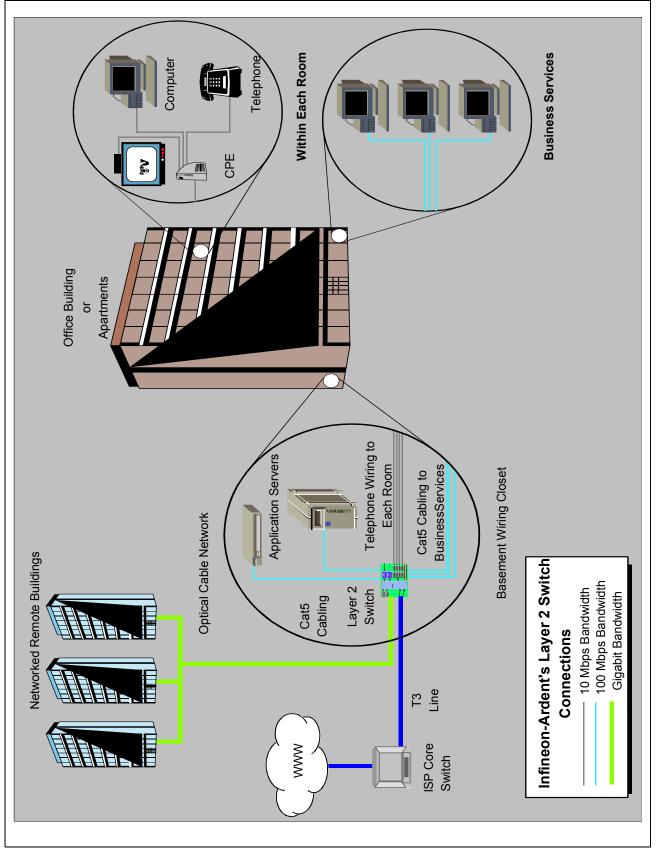

Figure 2 to Figure 4 gives a general overview of system integration of the PLB 2224

Figure 2 General System Integration

#### Overview

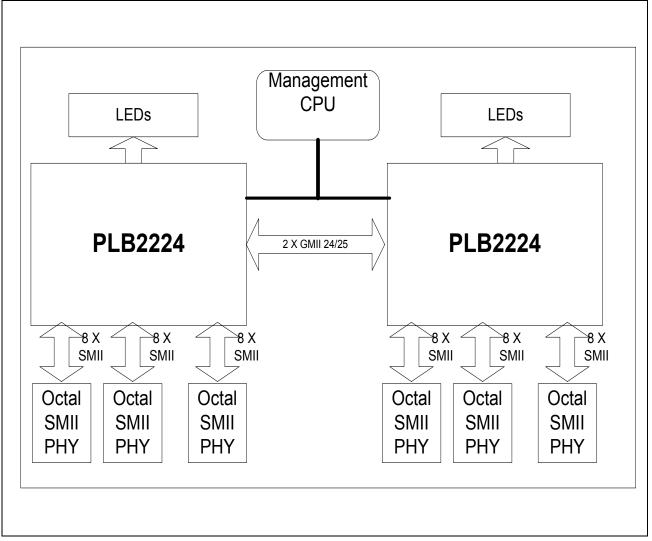

Figure 3 48 x 10/100 Mbit/s Port Managed Solution

#### Overview

Figure 4 MDU/MTU Application

# **1.5** Typical Configurations

Switches in a variety of different configurations can be designed using PLB 2224. The table below shows a few configurations that can be built and the major components that are needed to build them.

## Table 1 Typical Configurations Using PLB 2224

|                                                | PLB 2224 | 10 /100<br>Octal<br>Phy | GBit<br>Phy | CPU<br>Subsys                                           | Comments                                                                                                                                                                                      |

|------------------------------------------------|----------|-------------------------|-------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24 10/100 +<br>2GE fully<br>managed            | 1        | 3                       | 2           | 32-bit<br>Generic or<br>PCI                             |                                                                                                                                                                                               |

| 24 10/100 +<br>2GE minimally<br>managed        | 1        | 3                       | 2           | 8-bit with 2<br>wire Serial<br>Interface                | Spanning Tree Protocol only                                                                                                                                                                   |

| 24 10/100 + 2<br>GE SOHO<br>with WAN<br>Router | 2        | 3                       | 2           | 32-bit<br>Generic or<br>PCI                             |                                                                                                                                                                                               |

| 48 10/100<br>standalone,<br>managed            | 2        | 6                       | 0           | 32-bit<br>Generic or<br>PCI                             |                                                                                                                                                                                               |

| 48 10/100<br>Low-cost<br>unmanaged             | 2        | 6                       | 0           | None                                                    | Uses EEPROM for initial configuration                                                                                                                                                         |

| 24 x 10/100<br>Stackable<br>managed            | 1        | 3                       | 2           | 32-bit<br>Generic<br>with 2-wire<br>Serial<br>interface | GE Ports used to connect<br>stack elements, 2-wire<br>Serial interface is used to<br>communicate between stack<br>elements                                                                    |