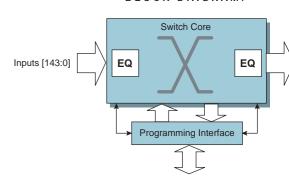

# BLOCK DIAGRAM:

| FEATURES:                                                                                                                          | BENEFITS:                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| <ul> <li>6.5 Gbps 144 × 144 strictly nonblocking switch matrix with multicast and<br/>output striping programming modes</li> </ul> | 936 Gbps aggregate bandwidth in a single chip for h<br>switching and video systems               |

| Input signal equalization (ISE) with programmable control globally or on<br>a per-channel basis                                    | Addresses system-level and board-level signal integ<br>intersymbol interface (ISI) jitter issues |

| ▶ Adjustable output pre-emphasis EQ                                                                                                | ▶ EQ and drive flexibility for driving boards, cables, ar                                        |

| ▶ Differential current mode logic (CML) data output driver                                                                         | ► Convenient I/O flexibility for interfacing with multiple                                       |

| ▶ Protocol-independent switching and data transmission                                                                             | Can be used with latest storage, Ethernet, and netw                                              |

| ▶ 16 W typical power dissipation                                                                                                   | ▶ Low per-channel power                                                                          |

| ▶ 45 mm × 45 mm, 1.27 mm pin pitch, 1072-pin BGA package                                                                           | Layout-friendly package and pinout for easier PCB or page 2.                                     |

| ▶ Parallel and serial programming modes for configuration and monitoring                                                           | ▶ Programming and control convenience                                                            |

| ▶ Software control to optimize power dissipation                                                                                   | ▶ Control and lower overall power when ports are not                                             |

## APPLICATIONS:

- ▶ Core and metro transport

- ▶ Enterprise

- ▶ High-speed automated test equipment

- ▶ Broadcast video systems

- ▶ Storage, Ethernet, and networking equipment

VSC3144

programmed to connect to any of its inputs. The signal path through the device uses no registers and

is fully asynchronous. This means there are no restrictions on the phase, frequency, or signal pattern of any input.

A high degree of signal integrity is maintained throughout the VSC3144 device because each high-speed output is a fully differential, switched-current driver with on-die terminations. Data inputs are

Core programming for the VSC3144 device port-by-port basis, or multiple program assignn issued simultaneously using the CONFIG bit. initialized for straight-through, multicast, or oth channels can be powered down to allow effic applications that require only a subset of the Power-down is enabled in the software by progroutputs with a power-down code.

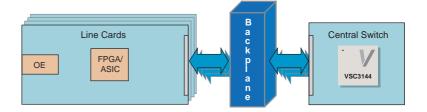

#### **BACKPLANE APPLICATION:**

#### SPECIFICATIONS:

- ▶ 6.5 Gbps NRZ per-channel data rate

- ▶ 2.5 V power supply (2.5 V or 3.3 V program port power supply)

- ▶ 2.5 V or 3.3 V CMOS TTL-compatible I/O

- ▶ Differential CML I/O with integrated termination impedance

- ▶ 0 °C to 85 °C operating temperature range

#### Γrademarks <sup>™</sup>

Vitesse, ASIC-Friendly, FibreTimer, TimeStream, Snoop Loop, Super FEC, FOCUSConnect, Meigs-II, Meigs-IIe, Lansing, Campbell-I, Barrington, PaceMaker, HOVCAT48, HOVCAT48e, HOVCAT192, HOVCAT192e, Micro PHY, FOCUS32, FOCUS16, IQ2200, NexSAS, VersaCAT, GigaStream, HawX, SparX, StaX, VstaX, SimpliPHY, VeriPHY, ActiPHY, XFP PRO, SFP PRO, Smart-LINK, OctalMAC, EQ Technology are trademarks in the United States and/or other jurisdictions of Vitesse Semiconductor Corporation. All other trademarks or registered trademarks mentioned herein are the property of their respective holders.

### Copyright © 2006

Vitesse Semiconductor Corporation ("Vitesse") retains the right to make changes to its products or specifications to improve performance, reliability or manufacturability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will be assumed by Vitesse for its use. Furthermore, the information contained herein does not convey to the purchaser of microelectronic devices any license under the patent right of any manufacturer.

Cam Tel: Fax:

741

sale