# **IMSG170**

# High Performance CMOS Color look-up table

Preliminary

#### **FEATURES**

- Compatible with the RS 170A video standard

- Pixel rates up to 50 MHz

- 256K possible colors

- Single monolithic, high performance CMOS

- · Pixel address mask

- RGB analog output, 6 bit DAC per gun, composite blank + sync

- Low DAC glitch energy

- Video signal output into 75 ohms

- TTL compatible inputs

- Micropocessor compatible write interface

- Single +5V ± 10% power supply

- Low power dissipation, 750mW max at maximum pixel rate

- Standard 600 mil 28 pin DIP package

### **DESCRIPTION**

4802688 0002430

DΕ

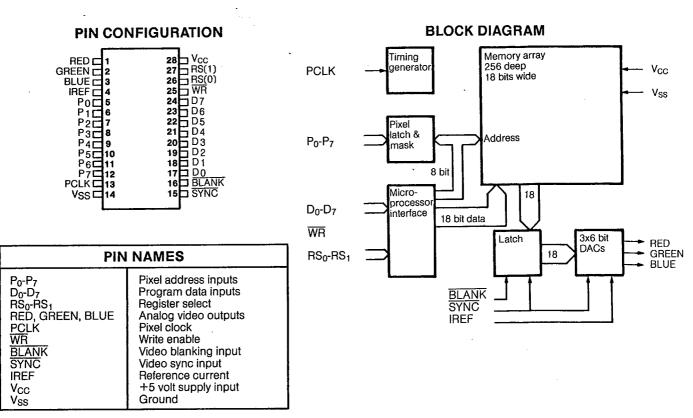

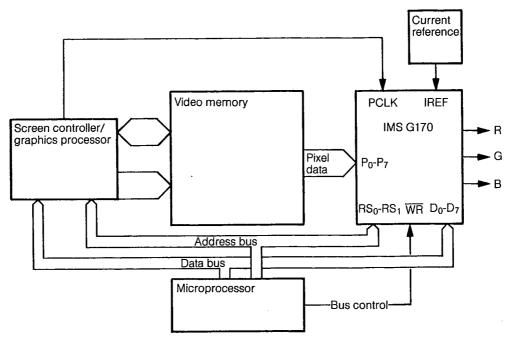

The IMSG170 integrates the function of a color lookup table (or color palette), digital-analog convertors (with  $75\Omega$  outputs) and microprocessor interface into a single 28 pin package.

At any time, a set of up to 256 colors may be selected for display from a palette of 256K. The IMSG170 significantly reduces component cost, board area, and power consumption.

The pixel word mask allows displayed colors to be changed in a single write cycle rather than by modifying the look-up table.

INMOS CORP 95 DE 4802688 0002431 9

# **FUNCTIONAL DESCRIPTION**

4802688 INMOS CORP

95D 02431 D 7-52-33-09

### PIXEL INTERFACE

| SIGNAL                         | PIN  | INPUT/<br>OUTPUT | SIGNAL<br>NAME   | DESCRIPTION                                                                                                                                                                                                                                                             |

|--------------------------------|------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK                           | 13   | Input            | Pixel Clock      | The rising edge of the Pixel Clock signal controls the sampling of values on the Pixel Address, Blanking and Sync inputs. The Pixel Clock also controls the progress of these values through the three stage pipeline of the Color Look-Up Table to the analog outputs. |

| P <sub>0</sub> -P <sub>7</sub> | 5-12 | Input            | Pixel<br>Address | The byte wide value sampled on these inputs is masked<br>by the Pixel Mask Register and then used as the address<br>into the Color Look-Up Table. This causes an internal 18<br>bit wide color value to be produced.                                                    |

| BLANK                          | 16   | Input            | Blanking         | A low value on this input, when sampled, will cause a color value of zero to be applied to the inputs of the DACs regardless of the color value of the current pixel.                                                                                                   |

| SYNC                           | 15   | Input            | Sync             | The value on this input, when sampled, controls an offset on the analog outputs, the offset being 30% of the full scale analog output. If SYNC is low there is no offset, if SYNC is high the offset is active.                                                         |

## **ANALOG INTERFACE**

| SIGNAL                 | PIN         | INPUT/<br>OUTPUT           | SIGNAL<br>NAME          | DESCRIPTION                                                                                                                                                                                                                                   |

|------------------------|-------------|----------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RED,<br>GREEN,<br>BLUE | 1<br>2<br>3 | Output<br>Output<br>Output | Red,<br>Green,<br>Blue, | These three signals are the outputs of three 6 bit DACs. Each DAC is composed of 90 current sources whose outputs are summed. 63 of the current sources are controlled by the binary input to the DACs, 27 are controlled by the SYNC signal. |

| IREF                   | 4           | Input                      | Reference<br>Current    | The Reference Current drawn from V <sub>CC</sub> via the IREF pin determines the current sourced by each of the current sources in the DACs. Each current source producing 1/30 of IREF when turned on.                                       |

## **MICROPROCESSOR INTERFACE**

| SIGNAL                           | PIN   | INPUT/<br>OUTPUT | SIGNAL<br>NAME     | DESCRIPTION                                                                                                                                                                                                                                          |

|----------------------------------|-------|------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WR                               | 25    | Input            | Write Enable       | The Write Enable signal controls the timing of write operations to the microprocessor interface. A minimum high period for the Write Enable signal is specified in terms of the Pixel Clock period allowing the two signals to be asynchronous.      |

| RS <sub>0</sub> -RS <sub>1</sub> | 26-27 | Input            | Register<br>Select | The values on these inputs are sampled on the falling edge of the Write Enable signal, they specify which one of the three internal registers is to be written to next. See internal Register description for the function of these three registers. |

| D <sub>0</sub> -D <sub>7</sub>   | 17-24 | Input            | Program<br>Data    | On the rising edge of Write Enable the byte value on the Program Data inputs is written to the specified register.                                                                                                                                   |

| RS <sub>1</sub> | RS <sub>0</sub> | SIZE<br>(BITS) | REGISTER<br>NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|-----------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | 0               | 8              | Pixel<br>Address | The Pixel Address register is written with an 8 bit value to address a location within the Color Look-Up Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0               | 1               | 18             | Color Value      | The Color Value register is internally an 18 bit wide register. The 18 bit value is formed by the concatenation of the least significant 6 bits from each of 3 bytes written to the Color Value register. The first value written will be applied to the red DAC, the second to the green DAC and the third to the blue DAC. After the third byte is written to the Color Value register the 18 bit word will be written to the location in the Color Look-Up Table specified by the current contents of the Pixel Address register. The Pixel Address register is then incremented. |

| 1               | Don't Care      | 8              | Pixel Mask       | The Pixel Mask register can be used to mask selected bits of the Pixel Address value applied to the Pixel Address inputs (P <sub>0</sub> -P <sub>7</sub> ). A one in a position in the mask register leaves the corresponding bit in the Pixel Address unaltered, a zero setting that bit to zero. The Pixel Mask register does not affect the Pixel Address generated by the Microprocessor Interface when the look-up table is being modified.                                                                                                                                     |

#### **DEVICE DESCRIPTION**

The IMSG170 is intended for use as the output stage of raster scan video systems. It contains a high speed random access store of 256 x 18 bit words, three 6 bit high speed DAC's, a microprocessor interface and a pixel word mask.

An 8 bit value read in on the Pixel Address input is used as a read address for the store and results in an 18 bit data word. This data is partitioned as three fields of 6 bits, with each field being applied to the inputs of a 6 bit DAC.

Pixel rates of up to 50 MHz are achieved by pipelining the memory access over two clock periods.

Externally generated sync and blanking signals can be input to the IMSG170, these signals act on all three of

the analog outputs. The SYNC and BLANK signals are delayed internally by pipelining so that they appear at the analog outputs with the correct relationship to the pixel address stream.

The contents of the look up table can be modified via an 8 bit wide microprocessor interface. The use of an internal synchronizing circuit allows operations on the interface to be totally asynchronous to the video path.

A pixel word mask is included to allow the incoming pixel address to be masked. This permits rapid changes of the effective contents of the Color Look-Up Table to facilitate such operations as animation and flashing objects.

# **IMSG170**

#### VIDEO PATH

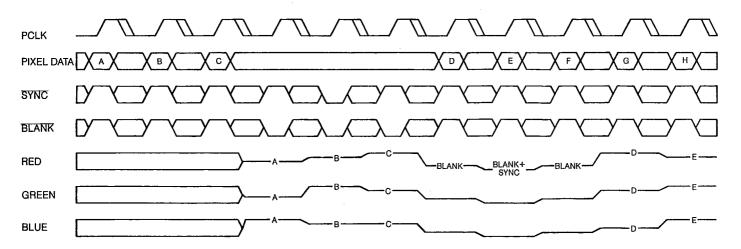

Pixel Address, SYNC and BLANK inputs are sampled on the rising edge of Pixel Clock and appear at the analog outputs after two further rising edges of Pixel Clock.

INMOS CORP 95

#### **ANALOG OUTPUTS**

The outputs of the DACs are intended to produce 1 volt peak white amplitude (i.e., 0.7 volts swing and 0.3 volts sync as specified by RS170A) when driving a 75 ohm load and when a 4.44 mA IREF is supplied.

The BLANK and SYNC inputs to the IMSG170 act on all three of the analog outputs. When the BLANK input is low a binary zero is applied to the inputs of the DACs. When the SYNC input is low an offset on the analog outputs of 30% of the full scale output current is removed. The BLANK and SYNC inputs can be operated independently of each other.

The expressions for peak white voltage/output loading combinations are given below:

1) Composite sync (SYNC going low to generate sync pulses on the analog outputs)

|                | IHEF X 90 X HIOAO |

|----------------|-------------------|

| V peak white=  | 30                |

|                | IREF x 27 x Rload |

| V black level= | 30                |

2) Separate sync (SYNC continuously low)

V peak white=

$$\frac{IREF \times 63 \times Rload}{30}$$

Vblack level = 0

### **MICROPROCESSOR INTERFACE**

There are three internal registers in the IMSG170. These are:

| RS1 | RS0 | Register      |

|-----|-----|---------------|

| 0   | 0   | Pixel Address |

| 0   | 1   | Color Value   |

| 1   | 0   | Pixel Mask    |

The Pixel Address register is used to specify the location in the look-up table to be written with a color value. The Color Value register contains the data used to update the contents of the location specified by the Pixel Address register. The Pixel Mask register is an 8 bit register. The value in the mask register is bitwise ANDed with the incoming pixel address to give a masked pixel address.

The microprocessor interface is asynchronous with the video path, the timing of operations on the interface registers being controlled by the Write Enable signal (WR). On the falling edge of this signal the register select lines are sampled, and on the rising edge the values on the data bus are sampled. To allow for the internal synchronization of the written data with the video path, Write Enable must be high for at least three Pixel Clock cycles between write operations. Each time a new color value is written to the Look-Up Table to modify its contents the write cycle will replace the color value read cycle for one pixel.

To write a new color value to the table a pixel address must be specified and then an 18 bit data word written to that location in the Table.

Locations in the Look-Up Table can be specified in two ways. The first is to write a pixel address and then perform a color value write sequence. The second method is to write an initial pixel address and then (as the Pixel Address register increments after every color value write sequence) write a succession of new color values for the range of pixel addresses to be written.

A color value write sequence is three successive byte writes to the Color Value register. The least significant 6 bits are taken from each byte written and concatenated into an 18 bit word. The first byte written will define the red intensity, the second the green and the last the blue.

The pixel address used to access the Color Look-Up Table is the result of the bitwise ANDing of the incoming pixel address and contents of the Pixel Mask register. This pixel masking process can be used to alter the displayed colors without altering the video memory or the look-up table contents. Thus, by partitioning the color definitions by one or more bits in the pixel address rapid animation and flashing objects can be produced.

In the event that the Pixel Address register is modified during a color value write sequence the Color Value register is initialized, aborting any unfinished write sequence.

The Pixel Mask register is independent of the Pixel Address and Color Value registers.

## **ABSOLUTE MAXIMUM RATINGS**<sup>a</sup>

| Voltage on V <sub>CC</sub>                              |

|---------------------------------------------------------|

| Voltage on Other Pin $V_{SS} = 0.5V$ to $V_{CC} = 0.5V$ |

| Temperature Under Bias40°C to 85°C                      |

| Storage Temperature (Ambient)65°C to 150°C              |

| Power Dissipation1V                                     |

| Reference Current15m/                                   |

| Analog Output Current (Per Output) 45m/                 |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### DC OPERATING CONDITIONS<sup>a</sup>

| SYMBOL          | PARAMETER                     | MIN  | TYP | MAX                  | UNITS | NOTES                               |

|-----------------|-------------------------------|------|-----|----------------------|-------|-------------------------------------|

| V <sub>CC</sub> | Positive Supply Voltage       | 4.5  | 5.0 | 5.5                  | Volts |                                     |

| V <sub>SS</sub> | Ground                        |      | 0   |                      | Volts |                                     |

| V <sub>IH</sub> | Input Logic "1" Voltage       | 2.0  |     | V <sub>CC</sub> +0.5 | Volts |                                     |

| V <sub>IL</sub> | Input Logic "0" Voltage       | -0.5 |     | 0.8                  | Volts | -2.0 V Min for<br>20 ns pulse width |

| T <sub>A</sub>  | Ambient Operating Temperature | 0    |     | 70                   | °C    |                                     |

# DC ELECTRICAL CHARACTERISTICS a, b (0°C $\leq$ T<sub>A</sub> $\leq$ +70°C) (V<sub>CC</sub> = 5.0V $\pm$ 10%)

| SYMBOL             | PARAMETER                    | MIN  | MAX        | UNITS | NOTES                    |

|--------------------|------------------------------|------|------------|-------|--------------------------|

| Icc                | Average Power Supply Current |      | 150        | mΑ    | С                        |

| IREF               | Reference Current            | -1.5 | <b>-</b> 7 | mΑ    | d                        |

| VO max             | Maximum Output Voltage       | 2    |            | ٧     | e, l <sub>O</sub> ≤ 10mA |

| l <sub>o</sub> max | Maximum Output Current       | 21   |            | mA    | $e, V_0 \le 1V$          |

|                    | Full Scale Accuracy          | ±5   |            | %     | е                        |

|                    | Sync Accuracy                | 29   | 31         | %     | g                        |

|                    | Differential Accuracy        | ±1   |            | %     | h                        |

|                    | Linearity                    | ±0.5 |            | LSB   | i                        |

#### **AC TEST CONDITIONS**

| Input Pulse Levels | V <sub>SS</sub> to 3V<br>2.5ns<br>1.5V |

|--------------------|----------------------------------------|

|--------------------|----------------------------------------|

# AC ELECTRICAL CHARACTERISTICS<sup>a</sup>

$(0^{\circ}C \le T_A \le 70^{\circ}C) (V_{CC} = 5.0V \pm 10\%)$

| PARAMETER                | MIN | MAX | UNITS | NOTES |

|--------------------------|-----|-----|-------|-------|

| Rise Time (10% to 90%)   |     | 8   | ns    | j     |

| Full Scale Settling Time |     | 20  | ns    | j,k,f |

| Glitch Energy            |     | 400 | pVsec | f     |

Note a: All voltages in this data sheet are with respect to  $V_{SS}$  unless specified otherwise.

Note b: The Pixel Clock frequency must be stable for a period of at least 20μS after power-up (or after a change in Pixel Clock frequency) before proper device operation is achieved.

Note c: Pixel Clock frequency = 50 MHz (lo = lo max)

Note d: Reference currents below the minimum specified may cause the applied outputs to become invalid.

the analog outputs to become invalid.

Note e: SYNC ≥ V<sub>IH</sub> (min). Note f: This parameter is sampled, not 100% tested. Note g: Sync current is nominally 30% of peak white current. Note h: Between different analog outputs on the same device.

Note i: Monotonicity guaranteed. Note i: Load =  $75 \Omega + 30 pF$ .

Note k: To within 1% of full scale voltage.

#### 4802688 IN **IMSG170**

# **VIDEO OPERATION**

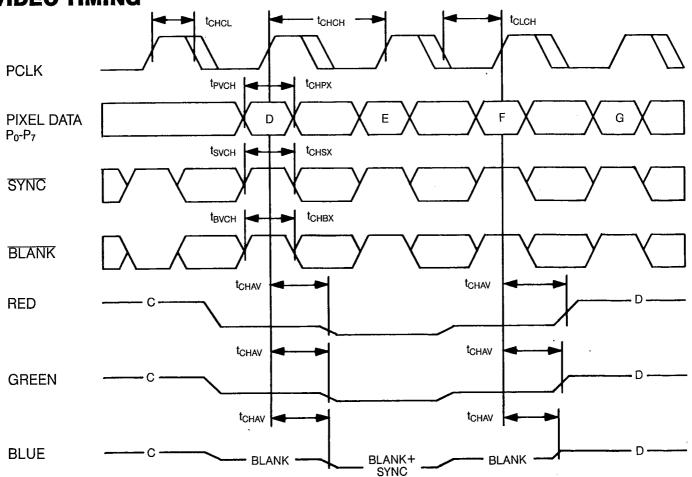

AC OPERATING CONDITIONS:  $V_{CC} = +5.0V \pm 10\%$ ,  $0^{\circ}C \le T_A \le 70^{\circ}C^{b}$

| OVIADOL            | DADAMETED                   |     | 170-50 |     | 170-35 | UNITS  | NOTES |

|--------------------|-----------------------------|-----|--------|-----|--------|--------|-------|

| SYMBOL             | PARAMETER                   | MIN | MAX    | MIN | MAX    | 014113 | NOTES |

| tchch              | PCLK Period                 | 20  | 10000  | 28  | 10000  | ns     |       |

| Δt <sub>CHCH</sub> | PCLK Jitter                 |     | ±2.5   |     | ±2.5   | %      | n     |

| tсьсн              | PCLK Width Low              | 6   | 10000  | 9   | 10000  | ns     |       |

| tchcL              | PCLK Width High             | 6   | 10000  | 9   | 10000  | ns     |       |

| t <sub>PVCH</sub>  | Pixel Word Setup Time       | 3   |        | 4   |        | ns     |       |

| t <sub>CHPX</sub>  | Pixel Word Hold Time        | 3   |        | 4   |        | ns     |       |

| tsvcн              | SYNC Setup Time             | 3   |        | 4   |        | ns     |       |

| t <sub>BVCH</sub>  | BLANK Setup Time            | 3   |        | 4   |        | ns     |       |

| t <sub>CHSX</sub>  | SYNC Hold Time              | 3   |        | 4   |        | ns     |       |

| t <sub>СНВХ</sub>  | BLANK Hold Time             | 3   |        | 4   |        | ns     |       |

| t <sub>CHAV</sub>  | PCLK to Valid DAC Output    | 15  | 30     | 15  | 45     | ns     | 0     |

| ∆t <sub>CHAV</sub> | Differential Output Delay   |     | 1      |     | 1      | ns     | р     |

|                    | Pixel Clock Transition Time |     | 50     |     | 50     | ns     |       |

Note n: This parameter for allowed variation in the Pixel Clock frequency does not permit the Pixel Clock period to vary outside the minimum and maximum values for Pixel Clock (t<sub>CHCH</sub>) period specified above.

Note o: A valid analog output is defined as when the changing analog signal is half way between its successive values.

Note p: Between different analog outputs on the same device.

## **VIDEO TIMING**

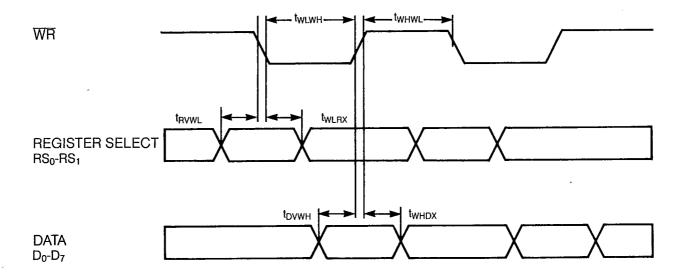

# MICROPROCESSOR INTERFACE: WRITE CYCLE TIMING

AC OPERATING CONDITIONS:  $V_{CC} = +5.0V \pm 10\%$ ,  $0^{\circ}C \le T_A \le 70^{\circ}C$

| SYMBOL            | PARAMETER                    | IMSG170-50          |     | IMSG170-35          |     | UNITS | NOTES |

|-------------------|------------------------------|---------------------|-----|---------------------|-----|-------|-------|

|                   |                              | MIN                 | MAX | MIN                 | MAX | UNITS | NOTES |

| t <sub>WLWH</sub> | WR Pulse Width Low           | 50                  |     | 50                  |     | ns    |       |

| twhwL             | WR Pulse Width High          | 3*t <sub>снсн</sub> |     | 3*t <sub>снсн</sub> |     | ns    | m     |

| t <sub>RVWL</sub> | Register Select Setup Time   | 10                  |     | 15                  |     | ns    |       |

| t <sub>WLRX</sub> | Register Select Hold Time    | 10                  |     | 15                  |     | ns    |       |

| t <sub>DVWH</sub> | Data Setup Time              | 10                  |     | 15                  |     | ns    |       |

| t <sub>WHDX</sub> | Data Hold Time               | 10                  |     | 15                  |     | ns    |       |

|                   | Write Enable Transition Time |                     | 50  |                     | 50  | ns    |       |

Note m: The parameter twhwL allows for the write data to be synchronized with the pixel clock, hence this parameter is expressed in terms of the pixel clock period t<sub>CHCH</sub>.

# WRITE CYCLE TIMING

4802688 INMO!

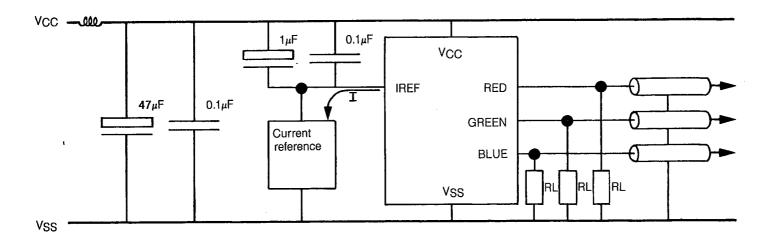

**APPLICATION**

The IMSG170 has no on chip power supply rejection

to analog outputs. To ensure proper operation in a system environment it is recommended that the following quidelines are followed.

#### POWER DISTRIBUTION

Transient currents are required by high speed CMOS circuitry such as the IMSG170. These transient current spikes can cause significant power supply and ground noise unless adequate power distribution and decoupling is used. The recommended power distribution scheme combines proper layout and placement of decoupling capacitors. A ground plane and locally isolated VCC supply, as shown below, will help to minimize VCC noise generated by eternal circuitry. A high frequency

decoupling capacitor with value of  $0.1\mu F$  and a larger tantalum capacitor with a value of  $47\mu$ F should be placed in parallel between V<sub>CC</sub> and V<sub>SS</sub> as close as possible to the device.

#### **CURRENT REFERENCE**

The current reference (IREF) input to the IMSG170 provides an onboard voltage reference by sourcing a current from the V<sub>CC</sub> supply. To prevent noise modulating the analog outputs the current reference should be as stable as possible and decoupled to V<sub>CC</sub>. To minimize cross-talk onto IREF the current source should be sited as close as possible to the IMSG170 and a ground plane should be used.

**Inmos Corporation**

P.O. Box 16000 • Colorado Springs, Colorado 80935 • (303) 630-4000 • TWX 910-920-4904 11205 Alpharetta Highway • Roswell, Georgia 30076 • (404) 475-1936 • TWX 810-751-0015 Suite 3001, Westborough Business Park • Westborough, Massachusetts 01581 • (617) 273-5150 • TWX 710-332-8777 9841 Broken Land Parkway, Suite 113 • Columbia, Maryland 21045 • (301) 995-0813 • TWX 710-862-2872 8300 Norman Center Drive • Minneapolis, Minnesota 55437 • (612) 831-5626 • TWX 910-576-2740 800 East Campbell Road, Suite 199 • Richardson, Texas 75081 • (214) 669-9001 • TWX 910-997-0822 1735 N. First Street, Suite 303 • San Jose, California 95112 • (408) 298-1786 • TWX 910-338-2151 23505 S. Crenshaw Blvd., Suite 201 • Torrance, California 90505 • (213) 530-7764 • TWX 910-347-7334 **Inmos Limited**

Whitefriars • Lewins Mead • Bristol BSI 2NP • England • Tel 0272-290-861 • TLX 851-444723 Inmos SARL

Immeuble Monaco • 7 rue le Corbusier SILIC 219 • 94518 Rungis Cedex • Tel (1) 887-22-01 • TLX 201222 Inmos GmbH

Danziger Strasse 2 • 8057 Eching • Tel (089) 319-1028 • TLX 522645

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents, trademarks, or other rights of INMOS.