Advance information

T-52-33-13

# High-Reliability, Radiation-Hardened CMOS/SOS Interrupt Controller

Aerospace Class S Screening

#### Features:

- Provides interrupt controller functions

- Meets the interrupt structure of Mil-Std-1750A

- Includes two timers and a Trigger Go counter

- Concatenable in multiples of eight bits

Full military-temperature-range operation

- 40-mil-center hermetic leadless package for high packing density

The RCA-GP517/1RZ, a CMOS/SOS, radiation-hardened, LSI, microprogrammable interrupt controller, is part of the EPIC (emulation programmable IC) family. The EPIC family contains a number of microprogrammable and bit-slice ICs for space computers and other high-performance emulating computer applications. The GP517 works well with EPIC family microprogram sequencers like the GP501 and GP502 (2910 type).

The GP517 incorporates the functions required of interrupt controllers, but, in addition, has features tailored to meet the interrupt structure of MIL-STD-1750A. The MIL-STD-1750A defines a 16-bit microprocessor instruction set that is finding increased use in military and space applications.

The GP517/1RZ interrupt controller is available in a 48-contact leadless-chip-carrier package (J suffix) and in a 64-lead ceramic flatpack (K suffix).

#### Radiation Features:

- Radiation hardened to 100 krads (Si)

- Latch-up free under transient radiation

- Resistance to upset under transient radiation rate of up to 1 x 10<sup>10</sup> rads (Si)/sec

OPERATING CONDITIONS at  $T_A = -55^{\circ}$  C to +125° C. For maximum reliability, operating conditions should be selected so that operation is always with the following ranges:

| CHARACTERISTIC             | LIM  | UNITS |       |

|----------------------------|------|-------|-------|

| CHARACTERISTIC             | Min. | Max.  | UNITS |

| DC Operating Voltage Range | 4.5  | 10.5  | V     |

MAXIMUM RATINGS, Absolute-Maximum Values:

DC SUPPLY-VOLTAGE RANGE, (V<sub>DD</sub>):

(All voltage values referenced to V<sub>SS</sub> terminal)

INPUT VOLTAGE RANGE, ALL INPUTS

DC INPUT CURRENT, ANY ONE INPUT

POWER DISSIPATION PER PACKAGE (P<sub>D</sub>):

For T<sub>A</sub> = -55 to +100° C

For T<sub>A</sub> = -55 to +100° C

For T<sub>A</sub> = FULL PACKAGE-TEMPERATURE RANGE

FOR T<sub>A</sub> = FULL PACKAGE-TEMPERATURE RANGE

STORAGE-TEMPERATURE RANGE (T<sub>A</sub>)

STORAGE-TEMPERATURE RANGE (T<sub>SD</sub>)

At distance 1/16 ± 1/32 in. (1.59 ± 0.79 mm) from case for 10 s max.

-0.5 to +11 V

-0.5 to +10 M

-0.5

2072

A-09

\_9-197

## HARRIS SEMICOND SECTOR T-52-33-13

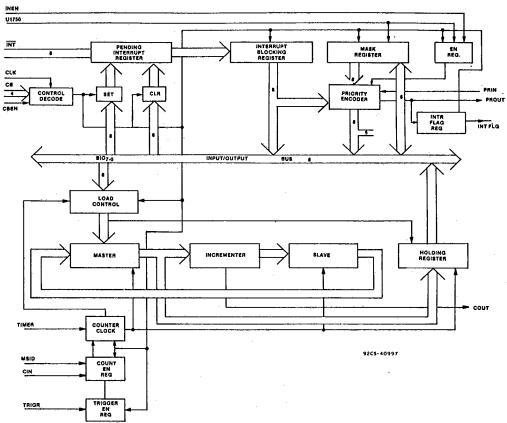

Fig. 1(a) - Functional diagram of the GP517 as an 8-bit slice.

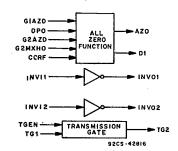

Fig. 1(b) - Random on-chip logic of GP517.

9-198— 2073 A-10 —

\_Radiation-Hardened High-Reliability ICs

HARRIS SEMICOND SECTOR

**GP517/1RZ**

STATIC ELECTRICAL CHARACTERISTICS,  $V_{DD}$  = 5 V  $\pm$  5%

T-52-33-13

|                                   | <u> </u> |                                           |            |          | LIM        | ITS      |            |               |          |

|-----------------------------------|----------|-------------------------------------------|------------|----------|------------|----------|------------|---------------|----------|

| CHARACTERISTIC                    |          | CONDITIONS                                | -55<br>+25 | °C       | +12        |          | +25        | ation<br>i° C | UNITS    |

|                                   |          |                                           |            |          |            | Max.     | Min.       | Max.          |          |

| Quiescent Device Current          | loo      | V <sub>IN</sub> =0 V or V <sub>DD</sub>   | <u> </u>   | 0.5      |            | 1.5      |            | 1.5           |          |

|                                   | Іоря     | Open Circuit Outputs Cycle Time=200 ns    | –          | 5        | _          | 7.5      | 1          | 7.5           | mA       |

| Operating Device Current          | Note 3   | Open Circuit Outputs Cycle Time=1000 ns   | _          | 2.5      | _          | 3.5      | _          | 3.5           |          |

| Input Leakage Current,<br>Low     | lı.      | V <sub>IN</sub> =0, Note 1                |            | 20       |            | 30       | <u>-</u> . | 30            |          |

| Input Leakage Current,<br>High    | Н        | V <sub>IN</sub> =V <sub>DD</sub> , Note 1 | _          | 20       | · <u> </u> | 30       |            | 30            | μΑ       |

| 3-State Output Leakage<br>Current | lozu     | Applied Voltage=0 V, Note 1               |            | 20       | _          | 30       |            | 30            |          |

| 3-State Output Leakage<br>Current | lozH     | Applied Voltage=V <sub>DD</sub> , Note 1  | _          | 20       | _          | 30       |            | 30            |          |

| Output (Sink) Current             | loL      | V <sub>OUT</sub> =0.4 V                   | 0.3        |          | 0.2        |          | 0.2        |               |          |

| Output (Source) Current           | Іон      | V <sub>OUT</sub> =V <sub>DD</sub> -0.4 V  | 0.3        |          | 0.2        |          | 0.2        | <u> </u>      | mA.      |

| Output (Sink) Current-Bus         | lor Bus  | Vout=0.4 V                                | 2.5        | _        | 1,8        | <u> </u> | 1.8        | 上二            | ] ''''   |

| Output (Source) Current-Bus       | loн Bus  | V <sub>OUT</sub> =V <sub>DD</sub> -0.4 V  | 2,5        |          | 1.8        |          | 1.8        | <u> </u>      | <u> </u> |

| Output Voltage Low Level          | Vol      | Note 2                                    |            | 0.5      | <u> </u>   | 0.5      | _          | 0.5           | 1 .      |

| Output Voltage High Level         | Voн      | Note 2                                    | 4.5        | _        | 4.5        | <u> </u> | 4.5        | <u> </u>      | v        |

| Input Low Voltage                 | VIL      | V <sub>ουτ</sub> =0.5 V or 4.5 V          |            | 0.75     | _          | 0.75     | <u> </u>   | 0.75          | ]        |

| Input High Voltage                | ViH      | Vout=0.5 V or 4.5 V                       | 4.25       | <u> </u> | 4.25       |          | 4.25       | <u></u>       |          |

$\dagger$ The limits shown are for tests performed within one hour of radiating to 100 krads (Si). NOTES:

1. All other inputs (non-measured) are held at opposite logic level. 2. Input levels shall be  $V_{DD}$  and  $V_{SS}$ . Outputs open. 3. Measured while running the vector set.

ZAH ₩ 3 0P24500 1550E#

Radiation-Hardened High-Reliability ICs **GP517/1RZ**

HARRIS SEMICOND SECTOR : T-52-33-13.

STATIC ELECTRICAL CHARACTERISTICS,  $V_{\mbox{\scriptsize DD}}$  = 10 V  $\pm$  5%

|                                   |                     |                                           |          |      | LIM  | IITS     |                     | -            |        |

|-----------------------------------|---------------------|-------------------------------------------|----------|------|------|----------|---------------------|--------------|--------|

|                                   |                     |                                           |          |      |      |          |                     | st†          | LINUTO |

| CHARACTERISTIC                    |                     | CONDITIONS                                | +25      | °C,  | +12  | 5°C      | Radiation<br>+25° C |              | ONIIS  |

|                                   |                     |                                           |          | Max. | Min. | Max.     | _                   |              |        |

| Quiescent Device Current          | lpp                 | Vin=0 V or Vpp                            |          | 1    | _    | 3        | _                   | 3            |        |

|                                   | lope                | Open Circuit Outputs Cycle Time=200 ns    | <u> </u> | 10   | _    | 15       | _                   | 15           | mA.    |

| Operating Device Current          | Note 3              | Open Circuit Outputs Cycle Time=1000 ns   | _        | 5    | _    | 7.5      | _                   | 7.5          | "      |

| Input Leakage Current,<br>Low     | Ιμ                  | V <sub>IN</sub> =0, Note 1                |          | 30   |      | 40       | <b>-</b>            | 40           |        |

| Input Leakage Current,<br>High    | lін                 | V <sub>IN</sub> =V <sub>DD</sub> , Note 1 | -        | 30   | _    | 40       |                     | 40           | μA     |

| 3-State Output Leakage<br>Current | lozL                | Applied Voltage=0 V, Note 1               |          | 30   | _    | 40       | _                   | 40           |        |

| 3-State Output Leakage<br>Current | lozн                | Applied Voltage=Von, Note 1               | -        | 30   | _    | 40       | -                   | 40           |        |

| Output (Sink) Current             | loL                 | V <sub>ουτ</sub> =0.5 V                   | 0.6      | 匚    | 0.4  |          | 0.4                 |              |        |

| Output (Source) Current           | Юн                  | V <sub>OUT</sub> =V <sub>DD</sub> -0.5 V  | 0.6      |      | 0.4  | -        | 0.4                 |              | mA.    |

| Output (Sink) Current-Bus         | lo <sub>L</sub> Bus | V <sub>ouт</sub> =0.5 V                   | 6        | Ī-   | 4.3  | <b>—</b> | 4.3                 | <del>-</del> | ] ""A  |

| Output (Source) Current-Bus       | loн Bus             | V <sub>OUT</sub> =V <sub>DD</sub> -0.5 V  | 6        | L=_  | 4,3  | -        | 4.3                 | -            | l      |

| Output Voltage Low Level          | Vol                 | Note 2                                    |          | 0.5  |      | 0.5      | _                   | 0.5          | ]      |

| Output Voltage High Level         | V <sub>он</sub>     | Note 2                                    | 9.5      |      | 9.5  |          | 9.5                 | _            | l v    |

| Input Low Voltage                 | VIL                 | Vou₁=1 V or 9 V                           |          | 1.5  |      | 1.5      |                     | 1.5          | _  "   |

| Input High Voltage                | ViH                 | Vout=1 V or 9 V                           | 8.5      |      | 8.5  |          | 8.5                 | l —.         | -      |

$<sup>^{\</sup>dagger}\text{The limits}$  shown are for tests performed within one hour of radiating to 100 krads (Si).

9-200\_\_\_ 2075

All other inputs (non-measured) are held at opposite logic level.

Input levels shall be Vop and Vss. Outputs open.

Measured while running the vector set.

HARRIS SEMICOND SECTOR

\_Radiation-Hardened High-Reliability ICs

**GP517/1RZ**

DYNAMIC ELECTRICAL CHARACTERISTICS,  $V_{\mbox{DD}}$  = 5 V  $\pm$  5%

T-52-33-13

| •                                      |                                   | M               | AXIMUM LIM | TS                           |       |      |

|----------------------------------------|-----------------------------------|-----------------|------------|------------------------------|-------|------|

| CHARACTERISTIC                         | PROP.<br>DELAY<br>t <sub>PD</sub> | -55°C,<br>+25°C | +125° C    | Post†<br>Radiation<br>+25° C | UNITS | FIG. |

| INTO→PROUT                             | HL                                | 110             | 150        | 150                          |       | 6    |

| CB <sub>0,2,3</sub> →PROUT             | LH                                | 125             | 168        | 168                          |       | 7    |

| CLOCK→PROUT                            | HL                                | 125             | 168        | 168                          |       | 8    |

| CLOCK→PROUT                            | LH                                | 125             | 168        | 168                          |       | 8    |

| PRIN→PROUT                             | HL                                | 65              | 87         | 87                           |       | 9    |

| CLOCK→COUT                             | LH                                | 160             | 216        | 216                          |       | 10   |

| TIMER-COUT                             | HL                                | 100             | 135        | 135                          | 1     | 11   |

| CBEN→BIO₃                              | ZH                                | 100             | 135        | 135                          |       | 12   |

| CLOCK→INTFLG                           | LH                                | 60              | 80         | 80                           |       | 13   |

| CLOCK-INTFLG                           | HL                                | 65              | 87         | 87                           |       | 14   |

| PRIN→PROUT                             | LH                                | 100             | 135        | 135                          | l ns  | 9    |

| G1AZDD1                                | HL                                | 35              | 47         | 47                           | "     | 15   |

| G2AZD→AZO                              | HL                                | 35              | 47         | 47                           |       | 16   |

| G2MXH0→D1                              | LH                                | 65              | 87         | 87                           |       | 17   |

| CBEN→BIO <sub>2-0</sub>                | ZL                                | 105             | 141        | 141                          |       | 12   |

| CB₀,₃PROUT                             | HL                                | 105             | 141        | 141                          |       | 18   |

| CB <sub>0,1,2</sub> BIO <sub>7-0</sub> | ZH                                | 80              | 108        | 108                          | 1     | 19   |

| INVI1→INVIO1                           | LH                                | 45              | 60         | 60                           |       | 20   |

| INVI2-INVIO2                           | LH                                | 45              | 60         | 60                           |       | 21   |

| INVI1→INVIO1                           | HL                                | 45              | 60         | 60                           |       | 20   |

| INVI2→INVIO2                           | HL                                | 45              | 60         | 60                           |       | 21   |

<sup>†</sup>Radiation measurements are made on two samples/wafer. The limits shown are for tests performed within one hour of radiating to 100 krads (Si).

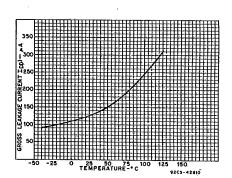

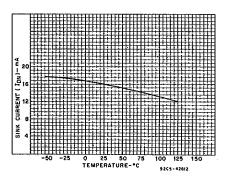

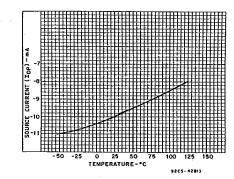

Fig. 2 - Typical gross leakage as a function of temperature.

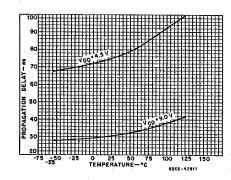

Fig. 3 - Typical propagation delay as a function of temperature.

2076

A - 13

9-20

Radiation-Hardened High-Reliability ICs.

T-52-33-13

### **GP517/1RZ**

DYNAMIC ELECTRICAL CHARACTERISTICS,  $V_{\mbox{\scriptsize DD}}$  = 10 V  $\pm$  5%

|                                         | T              | М                 | AXIMUM LIM | TS                           | · ·   |      |

|-----------------------------------------|----------------|-------------------|------------|------------------------------|-------|------|

| CHARACTERISTIC                          | PROP.<br>DELAY | -55° C,<br>+25° C | +125°C     | Post†<br>Radiation<br>+25° C | UNITS | FIG. |

| INTO-PROUT                              | HL             | 55                | 75         | 75                           |       | 6    |

| CB <sub>0,2,3</sub> PROUT               | LH             | 65                | 87         | 87                           |       | 7    |

| CLOCKPROUT                              | HL             | 65                | 87         | 87                           |       | 8    |

| CLOCK-PROUT                             | - LH           | 65                | 87         | 87                           |       | 8    |

| PRIN→PROUT                              | HL             | 35                | 47         | 47                           | 1     | 9    |

| CLOCK-COUT                              | LH             | 85                | 114        | 114                          |       | 10   |

| TIMER-COUT                              | HL             | 55                | 75         | 75                           |       | 11   |

| CBENBIO₃                                | ZH             | 55                | 75         | 75                           | ŀ     | 12   |

| CLOCK-INTFLG                            | LH             | 35                | 47         | 47                           |       | 13   |

| CLOCK⊶INTFLG                            | HL             | 35                | 47         | 47                           |       | 14   |

| PRINPROUT                               | LH             | 50                | 75         | 75                           | ns    | 9    |

| G1AZDD1                                 | HL             | 20                | 27         | 27                           |       | 15   |

| G2AZD→AZO                               | HL             | 20                | 27         | 27                           | 1     | 16   |

| G2MXH0→D1                               | LH             | 35                | 47         | 47                           |       | 17   |

| CBEN-BIO2-0                             | ZL             | 55                | 75         | 75                           | :     | 12   |

| CB <sub>0,3</sub> →PROUT                | HL             | 55                | 75         | 75                           | ĺ     | 18   |

| CB <sub>0,1,2</sub> →BIO <sub>7-0</sub> | ZH             | 40                | 54         | 54                           |       | 19   |

| INVI1→INVIO1                            | LH             | 25                | 33         | 33                           |       | 20   |

| INVI2→INVIO2                            | LH             | 25                | 33         | 33                           |       | 21   |

| INVI1→INVIO1                            | HL             | 25                | 33         | 33                           | 1     | 20   |

| INVI2-INVIO2                            | HL             | 25                | 33         | 33                           | 1     | 21   |

<sup>†</sup>Radiation measurements are made on two samples/wafer. The limits shown are for tests performed within one hour of radiating to 100 krads (Si).

Fig. 4 - Typical sink current as a function of temperature.

Fig. 5 - Typical source current as a function of temperature,

9-202 2077

A - 14

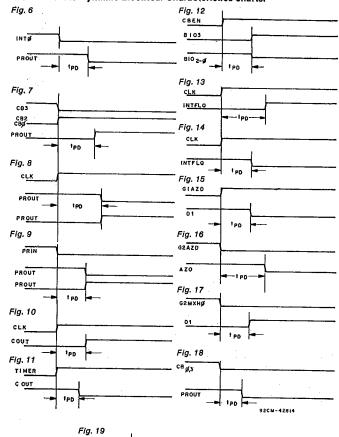

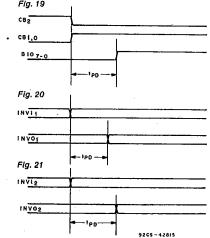

Timing Diagrams for Measuring Propagation Delays

Figure numbers are referred to in the Dynamic Electrical Characteristics charts.

T-52-33-13

2078

B-01

9-203

#### ARCHITECTURE AND MICROPROGRAMMING

The GP517 has three functions: interrupt handling, timer handling, and random logic operation. A functional block diagram of the interrupt controller, designed as an 8-bit slice, is shown in Fig. 1(a). The random logic is shown in Flg. 1(b).

The GP517 meets all the requirements of the 1750A interrupt structure. The IC has on-chip timer handling. For 16 interrupt lines, two units can be concatenated. If the device address pin (MSID) is wired high, the IC represents the most significant slice; if grounded, the IC is the least significant slice.

The interrupt handler responds to negative-going interrupt pulses. Of the 8 inputs on each slice, input 0 has the highest priority and input 7 the lowest. Each register on the chip is loaded from or read to the bidirectional bus BIO7-0. BIO0 is connected to the highest priority interrupt, BIO, to the

Arriving interrupts are stored in the PI register, then loaded into the interrupt blocking register, the output of which is used by the priority encoder, provided the mask bits are set (high) and the output of the enable register is high. Note that the blocking register cannot be loaded when the PI register is being read or when it is being used to encode a vector output to the bus. If the signal U1750 is high, interrupt 0.1 and 5 do not the three the results and the signal U1750 is high. interrupts 0, 1, and 5 do not use the enable register, and 0 and 5 do not use their mask bits. Hence, the interrupt definitions for 0, 1, and 5 in Table I are satisfied.

The priority output (PROUT) is low if an interrupt has been stored in the interrupt blocking register or if the priority input (PRIN) is low. A low PRIN indicates an interrupt in a unit of higher priority.

The highest priority interrupt in the PI register is encoded as one-of-eight, and the 3-bit value is output on BIO2-0. Input 0 (highest priority) will output a code of 111. The inverted value of MSID is output on BIO3, and zeroes are output to  $BIO_{7-4}$ . If no interrupts are pending, the  $BIO_{7-0}$  is 0.

The GP517 is under microcontrol by a 4-bit instruction field, CB<sub>3-0</sub>, and an enable signal, CBEN. If CBEN is low, no operation is done. If CBEN is high, the four-bit field is decoded to determine which of 16 functions is to be executed.

The timer is an 8-bit counter that can be concatenated (Fig. 1(a)). The counter consists of a master section, an incrementer, a slave section, and a holding register. The

Table I - Definition of Interrupts For Mil-Std-1750A

| Interrupt<br>Number | Definitions                    |

|---------------------|--------------------------------|

| 0 (Highest          | Power Down                     |

| Priority)           | (cannot be masked or disabled) |

| 1                   | Machine Error                  |

| •                   | (cannot be disabled)           |

| 2                   | Spare                          |

| 3                   | Floating Point Overflow        |

| 2<br>3<br>4<br>5    | Fixed Point Overflow           |

| 5                   | Executive Call                 |

|                     | (cannot be masked or disabled) |

| 6                   | Floating Point Underflow       |

| 7                   | Timer A                        |

|                     | (if implemented)               |

| 8                   | Spare                          |

| 9                   | Timer B                        |

|                     | (if implemented)               |

| 10                  | Spare                          |

| 11                  | Spare                          |

| 12                  | input/Output Level 1           |

|                     | (if implemented)               |

| 13                  | Spare                          |

| 14                  | Input/Output Level 2           |

|                     | (if implemented)               |

| 15                  | Spare                          |

|                     |                                |

master section accepts data from the slave when the counter clock is high.

The slave accepts data from the master through the incrementer when the counter clock is low. The holding register accepts data from the master when the clock is high. The design prevents the holding register from changing while the counter is being read to the bus.

Loading of the various sections is controlled by the clock and the count enable register. The latter is set by the start count instruction and is cleared by the stop count or load counter instructions. The count enable register can also be set if the trigger enable register is set by a negative edge transition at the external trigger input.

The interrupt handler performs eleven microcoded functions and the timer five. These functions are summarized in Table

Table II - Functions of the Interrupt Handler

| Instruction<br>Field | Action                                                                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0 or 1               | No operation                                                                                                                            |

| 2                    | Load 1-bit interrupt-enable register from INEN                                                                                          |

| 3                    | Load interrupt mask register with value of bus: BIO <sub>7-0</sub>                                                                      |

| 4                    | Reset pending interrupt for each bit set of corresponding bit in BiO7-0                                                                 |

| 5.                   | Set pending interrupt for each corresponding bit set of BIO7-0                                                                          |

| 6                    | Clear interrupt flag - INTFLG goes low - PROUT goes high                                                                                |

| 7                    | Strobe interrupt flag - Load interrupt flag register with PROUT                                                                         |

| 8                    | Output vector, and clear pending interrupt - 3-bit encoded value is output on BIO₂-o - MSID is output on BIO₃                           |

| 9                    | Read pending interrupt - Output of blocking register goes to BIO7-0                                                                     |

| Ан                   | Read interrupt mask register - Contents go to BIO <sub>7-0</sub>                                                                        |

| Вн                   | Read counter - Output goes to BIO7-0                                                                                                    |

| Сн                   | Load counter - Loads from BIO <sub>7-0</sub> into master, slave and holding register - Clears count enable and trigger enable registers |

| DH                   | Stop counter - Clears count enable and trigger enable registers                                                                         |

| Eн                   | Start counter - Sets count enable register                                                                                              |

| Fн                   | Arm trigger Go - Sets trigger enable register                                                                                           |

9-204 2079

B-02

The following list elaborates on Table II.

Details of Micro-operations

a: The Interrupt handler performs the following microcoded functions:

#### CB<sub>3-0</sub> Effect

#### 0, 1 No operation

2 Load Interrupt enable register - When the CPU clock is high, loads the one-bit register from the INTEN input. If this input is high, all eight interrupts are enabled. If INTEN is low, all interrupts are disabled. If U1750 is high, interrupts 0, 1 and 5 are not affected by the interrupt enable register.

not affected by the interrupt enable register.

Load Interrupt mask register - When the CPU clock is high, loads the register with the value of BIO<sub>7-0</sub>. An interrupt may pass on to the interrupt blocking register if its mask register bit is set. Note that interrupt 0 connects to the mask bit loaded from BIO<sub>7</sub>. If the input U1750 is high, interrupts 0 and 5 are not affected by the mask.

Reset pending interrupt - When the CPU clock is

Heset pending interrupt - When the CPU clock is high, each bit in the register is reset for which the corresponding bit of BIO<sub>7-0</sub> is set. If a bit of the PIR is being reset, and its interrupt input goes low, that bit of the PIR will not be set.

Set pending interrupt - When the CPU clock is high, each bit in the register is set for which the corresponding bit of BIO<sub>7-0</sub> is set.

Clear interrupt flag - When the CPU clock is high,

6 Clear interrupt flag - When the CPU clock is high, clears the interrupt flag register. This will force INTFLG low. Also, when the CPU clock is high, this sets PROUT.

7 Strobe interrupt flag - When the CPU clock is high, loads the interrupt flag register with PROUT inverted. The interrupt flag output (INTFLG) will always output the value of this register. A high level indicates that an interrupt has been loaded into the interrupt blocking register of either this ICT or in an ICT of higher priority.

8 Output vector and clear pending interrupt - The highest priority interrupt in the pending interrupt register is encoded as one of eight, and the three-bit encoded value is output on BIO<sub>2-0</sub>. Input 0 (the highest priority) would output a code of 111. The inverted value of MSID is output on BIO<sub>3</sub>. Zeros are output to BIO<sub>7-0</sub>. When the CPU clock is high, the encoded interrupt is cleared in the PIR, and PROUT is forced high. The interrupt blocking register will not change during this instruction in order to prevent a late arriving interrupt from affecting the priority encoder. If the interrupt input for the encoded interrupt goes low during this instruction, it will not set the PIR.

Read pending Interrupt - The contents of the interrupt blocking register are output on BIO<sub>7-0</sub>. If the PIR changes during this instruction (i.e., an interrupt is received), neither the blocking register nor BIO<sub>7-0</sub> will change. (NOTE: Executing this instruction on consecutive microcycles may not give the correct value of the PIR on the second microcycle).

A Read Interrupt mask register - The contents of the register are output on BIO<sub>7-0</sub>.

b: The following microcoded instructions are performed by the timer:

#### CB<sub>3-0</sub> Effect

T-52-33 -/3

- B Read counter Outputs the contents of the counter holding register to BIO<sub>7-0</sub>.

- C Load counter When the CPU clock is high, loads the value of BIO<sub>7-0</sub> into the master, slave, and holding register sections of the counter. Clears the count enable register and clears the trigger enable register.

- D Stop counter When the CPU clock is high, clears the count enable register and clears the trigger enable register.

- E Start counter When the CPU clock is high, sets the count enable register.

- F Arm trigger Go When the CPU clock is high, sets the trigger enable register. This will allow the next 1 0 transition of the external trigger input to set the count enable register.

#### Timer

The timer is an 8-bit concatenated counter. The counter consists of a master section, an incrementer, a slave section, and a holding register. The count enable register and counter clock control loading of the various sections. The count enable register is set by the start count instruction and is cleared by the stop count or load counter instructions. It may be set by a 1  $\rightarrow$  0 transition of the external trigger input if the trigger enable register is set.

The counter clock will be high if CIN is low (MS IC only), if the TIMER input is high or if the counter is being loaded. (Note that CIN is not used by the LS IC.) If none of these three conditions is met, the counter clock will be low if the count enable register is set. Once the counter clock is low, it cannot go high again until TIMER is high, the counter is loaded, or CIN is low. (Note that loading a count will stop the current count and load a new value; however, stopping a count will allow the current count to complete.)

The master section accepts data from the slave when the counter clock is high. The slave accepts data from the master through the incrementer when the counter clock is low. The holding register accepts data from the master when the counter clock is high, if the IC is not reading the counter, and if the counter clock was high when the CPU clock was last high. This keeps the holding register from changing while the counter is read to BIO. When the counter is loaded, the master, slave, and holding registers are all loaded.

### Random Logic

The random logic consists of five functions. The first function is a transmission gate. If TGEN is high, the bus pins TG1 and TG2 are connected by the transmission gate. If TGEN is low, TG1 and TG2 are isolated. Two functions are simple inverters. The output INVOT is the complement of the input INVI1. The output INVO2 is the complement of the input INVI2. The other two functions derive the outputs AZO and D1. The logical equations for each are:

#### AZO = G2AZD (G1AZD + DPO) D1 = AZO + G2MXHO

The random logic was designed to be used in architectures using the GP001.

D1 is a 3-state output which is enabled when the CCRF (condition code register flag) input is high. D1 is a function of AZO.

2080

8-03

\_9-205

I 4302271 0026596 7° ■ HAS

### **GP517/1RZ**

T-52-33-13.

Pin Functions for the GP517 48-Contact Leadless Chip Carrier

Radiation-Hardened High-Reliability ICs\_

| Pin<br>No. | Signal Name                    | Mnemonic         | 1/0 | Pin<br>No. | Signal Name                          | Mnemonic                | 1/0   |

|------------|--------------------------------|------------------|-----|------------|--------------------------------------|-------------------------|-------|

| 4          | Interrupt Enable Input         | INTEN            | ŧ   | 25         | Double Precision Operation Input     | DPO                     | - 1   |

| 2          | Bidirectional Data Bus 6       | BIO              | 1/0 | 26         | Data 1 Output                        | D1                      | 0     |

| 2          | Counter Carry Input            | CIN              | ï.  | 27         | All Zero Detect Output               | ÁZO                     | 0     |

| 4          | Timer Input                    | TIMER            | i   | 28         | GPU2 Multiplexer High 0 Input        | G2MXH0                  | ł.    |

| 5          | Most Significant IC Identifier | MSID             | i   | 29         | Condition Code Register Flag Input   | CCRF                    | ı     |

| 6          | External Trigger Input         | TRIGR            | ì   | 30         | GPU2 All Zero Detect Input           | G2AZD                   | í     |

| 7          | Control Bit Enable Input       | CBEN             | i   | 31         | Interrupt Input 7                    | INT7                    | ı     |

| (          | Control Bit Input 3            | CB3              | i i | 32         | Interrupt Input 6                    | INT6                    | - 1   |

| 8          | Control Bit Input 2            | CB2              | i   | 33         | Interrupt Input 5                    | INT5                    | - 1   |

| 9          | CPU Clock                      | CLK              | ŀ   | 34         | Interrupt Flag Output                | INTFLG                  | 0     |

| 10         |                                | CB0              | - 1 | 35         | Bidirectional Data Bus 3             | BIO₃                    | 1/0   |

| 11         | Control Bit Input 0            | BIO₄             | 1/0 | 36         | Interrupt Input 4                    | INT4                    | i     |

| 12         | Bidirectional Data Bus 4       | CB1              | ",  | 37         | Interrupt Input 3                    | INT3                    | ĺ     |

| 13         | Control Bit Input 1            | BIO <sub>2</sub> | 1/0 | 38         | Interrupt Input 2                    | INT2                    | 1     |

| 14         | Bidirectional Data Bus 2       |                  | 0   | 39         | Bidirectional Data Bus 5             | BIO₅                    | 1/0   |

| 15         | Priority Output                | PROUT<br>COUT    | ŏ   | 40         | Interrupt Input 1                    | INT1                    | ï.    |

| 16         | Counter Carry Output           |                  | Ÿ   | 41         | Upper IC for 1750 Architecture input |                         | i     |

| 17         | Inverter Input 2               | INVI2            | 6   | 42         | Interrupt Input 0                    | INTO                    | i.    |

| 18         | Inverter Output 2              | INVO2            | Ÿ   |            |                                      | PRIN                    | i     |

| 19         | GPU1 All Zero Detect Input     | G1AZD            | !   |            |                                      | TGEN                    | _ i _ |

| 20         | Inverter Input 1               | INVI1            | Ţ   | 44         |                                      | TG2                     | 1/0   |

| 21         | Inverter Output 1              | INVO1            | 0   | 45         | Transmission Gate Bus 2              | TG1                     | 1/0   |

| 22         | Bidirectional Data Bus 0       | BIO₀             | 1/0 | 46         | Transmission Gate Bus 1              |                         | 1/0   |

| 23         | Bidirectional Data Bus 1       | BIO <sub>1</sub> | 1/0 | 47         | Bidirectional Data Bus 7             | BłO <sub>7</sub><br>Van | 1/0   |

| 24         | Ground                         | Vss              | _   | 48         | Power                                | V 0.0                   |       |

Pin Functions for the GP517 64-Lead Flat Pack

| 04-F6 | au Flat Fack                   |                  |          |     |                                     |                  |     |  |

|-------|--------------------------------|------------------|----------|-----|-------------------------------------|------------------|-----|--|

| Pin   |                                |                  |          | Pin |                                     |                  | WO. |  |

| No.   | Signal Name                    | Mnemonic         | 1/0      | No. | Signal Name                         | Mnemonic         | 1/0 |  |

| 1     | No Connection                  | NC               |          | 33  | No Connection                       | NC               | -   |  |

| ż     | No Connection                  | NC               | _        | 34  | No Connection                       | NC               | _   |  |

| 3     | Priority Input                 | PRIN             | 1        | 35  | GPU1 All Zero Detect Input          | G1AZD            | - ! |  |

| 4     | Transmission Gate Enable Input | TGEN             | 1        | 36  | Inverter Input 1                    | INVI1            | l l |  |

| 5     | Transmission Gate Bus 2        | TG2              | 1/0      | 37  | Inverter Output 1                   | INVO             | 0   |  |

| 6     | Transmission Gate Bus 1        | TG1              | 1/0      | 38  | Bidirectional Data Bus 0            | BIO <sub>0</sub> | 1/0 |  |

| 7     | Bidirectional Data Bus 7       | BIO <sub>7</sub> | 1/0      | 39  | Bidirectional Data Bus 1            | BIO <sub>1</sub> | 1/0 |  |

| 8     | Power                          | Vop              |          | 40  | Ground                              | Vss              | _   |  |

| 9     | Interrupt Enable Input         | INTEN            | i        | 41  | Double Precision Operation Input    | DPO              | Ī   |  |

| 10    | Bidirectional Data Bus 6       | BIO <sub>6</sub> | 1/0      | 42  | Data 1 Output                       | D1               | 0   |  |

| 11    | Counter Carry Input            | CIN              | ı        | 43  | All Zero Detect Output              | AZO              | Ó   |  |

| 12    | Timer Input                    | TIMER            | - 1      | 44  | GPU2 Multiplexer High 0 Input       | G2MXH0           | ļ   |  |

| 13    | Most Significant IC Identifier | MSID             | - 1      | 45  | Condition Code Register Flag Input  |                  | . 1 |  |

| 14    | External Trigger Input         | TRIGR            | - 1      |     | GPU2 All Zero Detect Input          | G2AZD            |     |  |

| 15    | No Connection                  | NC               |          | 47  | No Connection                       | NC               | _   |  |

| 16    | No Connection                  | NC               | _        | 48  | No Connection                       | NC               | -   |  |

| 17    | No Connection                  | NC               | _        | 49  | No Connection                       | NC               | _   |  |

| 18    | No Connection                  | NC               |          | 50  | No Connection_                      | NC               | -   |  |

| 19    | Control Bit Enable Input       | CBEN             | l        | 51  | Interrupt Input 7                   | <u>INT7</u>      | ļ.  |  |

| 20    | Control Bit Input 3            | CB3              | ŀ        | 52  |                                     | INT6             | . ! |  |

| 21    | Control Bit Input 2            | CB2              | . 1      | 53  | Interrupt Input 5                   | INT5             | Ļ   |  |

| 22    | CPU Clock                      | CLK              | ı        | 54  | Interrupt Flag Output               | INTFLG           | .0  |  |

| 23    | Control Bit Input 0            | CB0              | ı        | 55  |                                     | BIO <sub>3</sub> | 1/0 |  |

| 24    | Bidirectional Data Bus 4       | BIO₄             | I/O      | 56  |                                     | INT4             | I - |  |

| 25    | Control Bit Input 1            | CB1              |          | 57  | Interrupt Input 3                   | INT3             | - ! |  |

| 26    | Bidirectional Data Bus 2       | BIO₂             | 1/0      | 58  | Interrupt Input 2                   | INT2             |     |  |

| 27    | Priority Output                | PROUT            | Q        | 59  | Bidirectional Data Bus 5            | BIO <sub>5</sub> | 1/0 |  |

| 28    | Counter Carry Output           | COUT             | 0        | 60  |                                     | INT1             | - 1 |  |

| 29    | Inverter Input 2               | INVI2            | <u>l</u> | 61  | Upper IC for 1750 Architecture Inpu |                  | 1   |  |

| 30    |                                | INVO2            | 0        | 62  |                                     | INTO             | '   |  |

| 31    | No Connection                  | NC               | _        | 63  |                                     | NC               | _   |  |

| 32    | No Connection                  | NC               | _        | 64  | No Connection                       | NC               | _   |  |

|       |                                |                  |          |     |                                     |                  |     |  |

9-206\_ 2081

B-04

Radiation-Hardened High-Reliability ICs

### **GP517/1RZ**

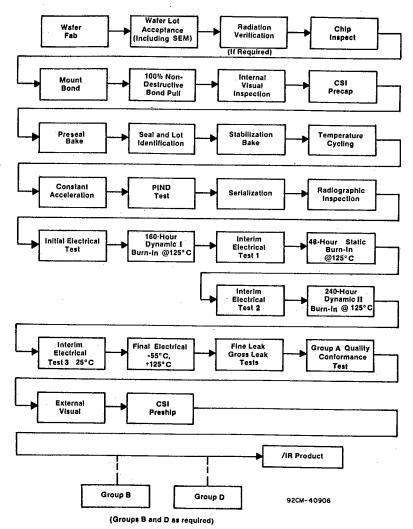

Flowchart for Modified Class S Screening per Mil-Std-883 Method 5004 T- 52 - 33-13

2082 B-05 \_\_\_\_\_\_\_9-207

T-52-33-13

**GP517/1RZ**

Modified Class S Screening for GP517/1RZ Per Mil-Std-883 Method 5004

| SCREEN                            | METHOD                     | REQMT.    | NOTES         |

|-----------------------------------|----------------------------|-----------|---------------|

| Wafer Lot Acceptance Incl. SEM    | 5007                       | 100%      |               |

| Radiation Verification (If Req'd) | 1019                       | Sample    |               |

| Nondestructive Bond Pull          | 1019                       | 100%      |               |

| Internal Visual                   | 2010                       | 100%      | See           |

|                                   | Cond. A                    |           | "Visual       |

|                                   | (Modified)                 |           | Inspection"   |

| Pre-Seal Bake                     | <u> </u>                   | 100%      |               |

| Stabilization Bake                | 1008                       | 100%      |               |

|                                   | Cond. C                    |           |               |

|                                   | 24 Hours Min, 150° C Min   |           |               |

| Temperature Cycling               | 1010                       | 100%      | 1             |

| . <u> </u>                        | Cond. C (-65° C to 150° C) |           |               |

| Constant Acceleration             | 2001                       | 100%      | ļ             |

|                                   | Cond. E                    |           | 1             |

|                                   | Y1 Dir., 30,000 g          |           | <u> </u>      |

| Particle Impact                   | 2020                       | 100%      | 1             |

| Noise Detection                   | Cond. A                    |           |               |

| (PIND)                            | 20g peak at 60 Hz          |           |               |

| Serialization                     | <del>-</del>               | 100%      |               |

| Radiographic, 1-View              | 2012                       | 100%      | 11            |

| Initial (Pre Burn-In)             | Per Applicable             | 100%      | See Table IV  |

| Electrical Parameters at 25° C    | Device Spec.               |           | V             |

| Burn-In Test (Dynamic I)          | 1015                       | 100%      | See Table V   |

| 160 Hours at 125° C               |                            |           | 5 7 11 17     |

| Interim Electrical Test 1         | -                          | 100%      | See Table IV  |

| % Defective Allowable (10%)       |                            | All Tests |               |

| 48-Hour Static Burn-In at 125° C  | _                          | 100%      |               |

| (With Delta Requirements)         | <u> </u>                   | 1000/     |               |

| Interim Electrical Test 2         |                            | 100%      |               |

| % Defective Allowable (5%)        |                            | All Tests | 1             |

| Functional (3%)                   |                            | 1000      | See Tables V. |

| 240-Hour Dynamic Burn-In          | 1015                       | 100%      | VI and VII    |

| (Dynamic II)                      | •                          |           | VI and VII    |

| (With Delta Requirements)         |                            | 100%      | See Table IV  |

| Interim Electrical Test 3         | Per Applicable             | 100%      | See Table IV  |

| Electrical Parameters at 25° C    | Device Spec.               | All Tests |               |

| % Defective Allowable (5%)        | 1                          | All Tests | ļ             |

| Functional (3%)                   | <del></del>                | 100%      | See Table IV  |

| Final Elect. Test @ -55/+125° C   | 1014                       | 100%      | See Table IV  |

| Seal                              | Cond. A or B               | 100%      | 1             |

| A) Fine                           | •                          | 100%      | -             |

| B) Gross                          | Cond. C<br>5005 - Class S  | 100%      | See Table IV  |

| Group A Quality Conformance       | 2009                       | 100%      | JOG TADIO IV  |

| External Visual                   | 5005 - Class S             | Optional  | See Table IV  |

| Group B Quality Conformance       | 5005 - Class S             | Optional  | See Table IV  |

| Group D Quality Conformance       | 5005 - Class 5             | Optional  | 000 14010 14  |

| CSI and/or GSI (Optional)         |                            |           |               |

9-208 \_\_\_ 2083

B-06

Group B .....

Group D .....

### **GP517/1RZ**

T-52-33-13

#### Table IV - Electrical Tests

For Individual tests, refer to the Static and Dynamic Characteristics charts.

| The state of the s | no Onaracteristics citarits.                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Interim Electrical Tests III Final Electrical Tests Quality Conformance:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Same as above 25° C<br>Same as above 25° C<br>Same as above 25° C |

| Group R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Same as above -55°C, 25°C, 125°C                                  |

#### Table V-Burn-In and Life-Test Circuits and **Timing Waveforms**

| Test       | Temperature | Duration<br>Min. | V <sub>DD</sub><br>Min. |

|------------|-------------|------------------|-------------------------|

| Dynamic I  | 125° C      | 160 hrs.         | 11 V                    |

| Static     | 125° C      | 48 hrs.          | 11 V                    |

| Dynamic II | 125° C      | 240 hrs.         | 11 V                    |

| Life Test  | 125° C      | 1000 hrs.        | 10.5 V                  |

#### Table VI-Delta Limits

| Test                     | Symbol | Delta*<br>Limits |

|--------------------------|--------|------------------|

| Quiescent Device Current | loo    | ±100 μA          |

| Output Low Current       | lou    | ±25%†            |

| Output High Current      | Іон    | ±25%†            |

Vpo = 10 V ± 5%.

†Measured from initial value.

#### Table VII-Delta Calculations

| Delta<br>Calculation | initial<br>Reading            | Final<br>Reading              |

|----------------------|-------------------------------|-------------------------------|

| I I                  | Interim Electrical<br>Tests 1 | Interim Electrical<br>Tests 2 |

| II .                 | Interim Electrical<br>Tests 1 | Interim Electrical<br>Tests 3 |

See Screening Flowchart, page 12.

#### **VISUAL INSPECTION**

Visual Inspection for Class S is performed to MIL-STD-883, Method 2010, Condition A except as follows:

3.2.1.1 - Metallization Scratches 3.2.1.2 - Metallization Voids

Same as above 25° C

Same as above 25°C

3.2.1.2 - Metallization Bridging

3.2.1.7 - Metallization Alignment

3.2.3 - Scribing and Die Defects. In addition, semicircular cracks that point away from the active circuit area are acceptable.

3.2.3c - A crack that exceeds 5 mils in length must also point towards or cross a scribe grid line.

3.1.7b - Lifting or Peeling of Glassivation, add NOTE of 3.2.7b to 3.1.7b.

#### Notes:

- High magnification inspection is performed at 200X to 300X and applies to the high current areas of the chip. The remainder of the chip is inspected at 75X to 150X where high magnification is required.

- Criteria 3.2.1.1a Metallization Scratches, and 3.2.1.2a Metallization Volds shall also apply to metallization over a passivation step (3.2.1.1d, 3.2.1.2b). Underlying

- oxide must also be exposed.

Criteria 3.2.1.7 Metallization Alignment and 3.1.2

Diffusion and Passivation(s) Faults are applied to the center and two opposite corners of the chip. Areas of sufficient complexity are viewed to assure general alignment and contact coverage and shall consist only of the area exposed to the immediate field of view.

- SOS Technology Devices

- 1. Diffusion faults 3.1.2.1 are not applicable. SOS devices are inspected for complete islands, bridging between islands and missing adjacent contacts from a row in a contact chain.

- The 1-mil wire clearance criteria is not applicable. Passivation faults are not applicable when a second

- free-flow oxide is used prior to metallization. Oxide gate bridge inspection is not applicable. Semicircular cracks not in an active area which

- start and end at the pellet edge are acceptable.

<sup>\*</sup>Limits apply at +25° C.