### **Features**

- 12 bit resolution

- Preadjusted Full Scale: ±1LSB max Gain Error

- Low Gain Tempco: 2ppm/°C

- · Fast TTL Data Latches

- Single +5V to 15V Operation

- · Small 20-pin 0.3" Wide DIP

- Low Cost

## Description

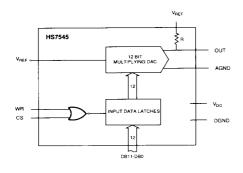

The HS 7545 is a precision, monolithic 12-Bit, CMOS, 4-quadrant multiplying DAC with an on-board latch. The latch is loaded by a single 12-Bit wide word and directly interfaces to most 12-and 16-bit bus systems. Data is loaded into the input latch under the control of CS and WR inputs. These control inputs are active low. Tying these inputs low makes the input latch transparent allowing direct unbuffered operation of the DAC.

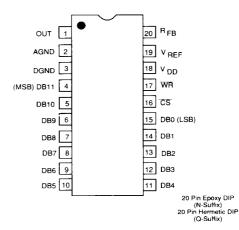

The HS 7545 is offered in a 20-pin plastic or hermetically-sealed CERDIP dual-in-line package. Processing to MIL-STD-883C is available.

## **Applications**

- · Digital Gain / Attenuation Control

- . Digital Control Of Circuit Functions

- X-Y Graphics

- Robotics

- Digital / Synchro Conversion

- Battery Operated Equipment

### Functional Diagram

#### Pin Connections

183

# HS-7545

12-Bit Buffered Monolithic CMOS MDAC

## **Absolute Maximum Ratings:**

| (T <sub>A</sub> = 25°C unless otherwise noted.)                                                                                      | 90.                                            | HS-7545 TQ/GUQ<br>HS-7545 BQ/GCQ<br>HS-7545 KN/GLN                                            | -55°C to 125°C<br>-25°C to 85°C<br>0°C to 70° |  |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| Voo to DGND Digital Input Voltage to DGND AGND to DGND VRFB, VREF to DGND                                                            | -03V, +17V<br>-0.3V, Vpb<br>-0.3V, Vpb<br>±25V | Dice Junction Temperature<br>Storage Temperature<br>Lead Temperature (Soldering, 60sec)       | +150°C<br>-65°C to +150°C<br>+300°C           |  |

| V <sub>PIN</sub> 1 to DGND -0.3V, V <sub>DD</sub><br>Power Dissipation (Any Package) to +75°C 450mW<br>Derates Above +75°C by 6mW/°C |                                                | Do not apply voltages higher than VDD or less than GND potential on any terminal except VREF. |                                               |  |

| Operating Temperature (T <sub>A</sub> = Full)                                                                                        | •                                              | Use proper ESD handling procedures.                                                           |                                               |  |

## **Electrical Characteristics:**

$V_{DD} = +5V$  or  $\pm 15V$  unless otherwise noted.  $V_{REF} = +10V$ , Out = 0V, AGND = DGND = 0V,  $T_{A}$ = Full unless otherwise noted.

| Parameters                                            | Symbol            | Conditions                                                                                  | Min | Тур | Max              | Units                    |

|-------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------|-----|-----|------------------|--------------------------|

| Static Accuracy                                       |                   |                                                                                             |     |     |                  |                          |

| Resolution                                            | N                 |                                                                                             | 12  |     |                  | Bits                     |

| Relative Accuracy                                     | INL               |                                                                                             |     |     | ±1/2             | LSB                      |

| Differential<br>Nonlinearity                          | DNL               |                                                                                             |     |     | ±1               | LSB                      |

| Gain Error                                            | G <sub>FSE</sub>  | Using internal $R_{\text{FB}}$ DAC latches =1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1           |     |     | 3<br>4<br>1<br>2 | LSB<br>LSB<br>LSB<br>LSB |

| Gain Temperature<br>Coefficient                       | TCG <sub>FS</sub> |                                                                                             |     | ±2  | ±5               | ppm/°C                   |

| Power Supply<br>Rejection<br>(ΔGain/ΔV <sub>DD)</sub> | PSS               | $T_A = 25^{\circ}C$ , $\Delta V_{DD} = \pm 5\%$<br>$T_A = Full$ , $\Delta V_{DD} = \pm 5\%$ |     |     | 0.002<br>0.004   | %/%<br>%/%               |

| Output Leakage<br>Current                             | I <sub>LKG</sub>  | WR = CS = 0V<br>All digital inputs = 0V                                                     |     |     |                  |                          |

|                                                       |                   | HS-7545 KN/BQ/GLN/GCQ<br>T <sub>A</sub> = 25°C<br>T <sub>A</sub> = Full                     |     |     | 10<br>50         | nA<br>nA                 |

|                                                       |                   | HS-7545 TQ/GUQ $T_A = 25^{\circ}C$ $T_A = Full$                                             |     |     | 10<br>200        | nA<br>nA                 |

|                                                       |                   |                                                                                             |     |     |                  |                          |

## **Electrical Characteristics:**

$\overline{V_{DD}}$  = +5V or ±15V unless otherwise noted.  $V_{REF}$  = +10V, Out = 0V, AGND = DGND = 0V,  $T_A$ = Full unless otherwise noted.

| Parameters                                      | Symbol           | Conditions                                                                                                                                                                                                                                                             | Min                      | Тур                      | Max        | Units                |

|-------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------------|----------------------|

| Dynamic Performance<br>Propagation Delay        | t <sub>PD</sub>  | From digital input change to 90% of final analog output, $I_{\text{Out}} \text{Load} = 100\Omega$ , $C_{\text{EXT}} = 13\text{pF}$ $T_{\text{A}} = 25^{\circ}\text{C}$                                                                                                 |                          |                          | 300        | nS                   |

| Current Settling Time                           | t <sub>s</sub>   | to 1/2 LSB $I_{\text{OUT}}$ LOAD = 100 $\Omega$                                                                                                                                                                                                                        |                          |                          | 1          | μS                   |

| Digital Charge Injection                        | a                | $V_{REF} = AGND$ ; $T_A = 25^{\circ}C$<br>$V_{REF} = AGND$ ; $T_A = Full$                                                                                                                                                                                              |                          |                          | 300<br>400 | nVS<br>nVS           |

| A.C Feedthrough $(V_{REF} \text{ to } I_{OUT})$ | FT               | $V_{REF} = \pm 10V                                  $                                                                                                                                                                                                                  |                          | 5                        |            | mV <sub>P-P</sub>    |

| Reference Input                                 |                  |                                                                                                                                                                                                                                                                        |                          |                          |            |                      |

| Input Resistance                                | R <sub>REF</sub> |                                                                                                                                                                                                                                                                        | 7                        | 11                       | 15         | kΩ                   |

| Analog Outputs                                  |                  |                                                                                                                                                                                                                                                                        |                          |                          |            |                      |

| Output Capacitance                              | Соит             | DB0-DB11= 0V, WR = CS = 0V<br>DB0-DB11 = V <sub>DD</sub> , WR = CS = 0V                                                                                                                                                                                                |                          |                          | 70<br>150  | pF<br>pF             |

| Digital Inputs                                  |                  |                                                                                                                                                                                                                                                                        |                          |                          |            |                      |

| Input High Voltage                              | V <sub>INH</sub> | $V_{DD} = +5V$ $V_{DD} = +15V$                                                                                                                                                                                                                                         | 2.4<br>13.5              |                          |            | V                    |

| Input Low Voltage                               | V <sub>INL</sub> | $\begin{vmatrix} V_{DD} = +5V \\ V_{DD-} + 15V \end{vmatrix}$                                                                                                                                                                                                          |                          |                          | 0.8<br>1.5 | V<br>V               |

| Input Current                                   | l <sub>iN</sub>  | $T_A = 25^{\circ}C$ $T_A = Full$                                                                                                                                                                                                                                       |                          |                          | 1<br>10    | μA<br>μA             |

| Input Capacitance<br>(DB0-DB11, WR, CS)         | C <sub>IN</sub>  | V <sub>IN</sub> = 0V                                                                                                                                                                                                                                                   |                          |                          | 8          | pF                   |

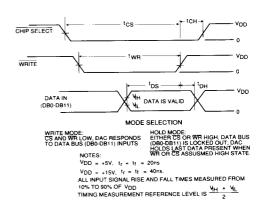

| Switching<br>Characteristics                    |                  | $(t_{CS} \ge t_{WR}, t_{CH} \ge 0)$                                                                                                                                                                                                                                    |                          |                          |            |                      |

| Chip Select to<br>Write Set-up Time             | t <sub>cs</sub>  | $ \begin{aligned} &V_{DD} = +5V, \ T_A = 25^{\circ}C \\ &V_{DD} = +5V, \ T_A = Full \\ &V_{DD} = +15V, \ T_A = 25^{\circ}C \\ &V_{DD} = +15V, \ T_A = Full \end{aligned} $                                                                                             | 280<br>380<br>180<br>200 | 200<br>270<br>120<br>150 |            | nS<br>nS<br>nS<br>nS |

| Chip Select to<br>Write Hold Time               | t <sub>ch</sub>  |                                                                                                                                                                                                                                                                        | 0                        |                          |            | nS                   |

| Write Pulse Width                               | t <sub>wn</sub>  | $ \begin{aligned} &V_{\text{DD}} = +5V, \ T_{\text{A}} = 25^{\circ}\text{C} \\ &V_{\text{DD}} = +5V, \ T_{\text{A}} = \text{Full} \\ &V_{\text{DD}} = +15V, \ T_{\text{A}} = 25^{\circ}\text{C} \\ &V_{\text{DD}} = +15V, \ T_{\text{A}} = \text{Full} \end{aligned} $ | 250<br>380<br>160<br>240 | 175<br>270<br>100<br>170 |            | nS<br>nS<br>nS<br>nS |

| Data Set-up Time                                | t <sub>os</sub>  | $\begin{array}{l} V_{DD} = +5V, \ T_A = 25^{\circ}C \\ V_{DD} = +5V, \ T_A = Full \\ V_{DD} = +5V, \ T_A = 25^{\circ}C \\ V_{DD} = +15V, \ T_A = 25^{\circ}C \end{array}$                                                                                              | 140<br>210<br>90<br>120  | 100<br>150<br>60<br>80   |            | nS<br>nS<br>nS<br>nS |

| Data Hold Time                                  | t <sub>DH</sub>  |                                                                                                                                                                                                                                                                        | 10                       |                          |            | nS                   |

# HS-7545

12-Bit Buffered Monolithic CMOS MDAC

## **Electrical Characteristics:**

$V_{DD} = +5V$  or  $\pm 15V$  unless otherwise noted.  $V_{REF} = +10V$ , Out = 0V, AGND = DGND = 0V,  $T_A = Full$  unless otherwise noted.

| Parameters     | Symbol          | Conditions                                                                                                                  | Min | Тур    | Max             | Units          |

|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|-----|--------|-----------------|----------------|

| Power Supply   |                 |                                                                                                                             |     |        |                 |                |

| Supply Current | l <sub>DD</sub> | All digital inputs = $V_{INL}$ or $V_{INH}$<br>All digital inputs = $0V$ or $V_{DD}$<br>$T_A = 25^{\circ}C$<br>$T_A = Full$ | į   | 2<br>5 | 2<br>100<br>100 | mA<br>μA<br>μA |

## **Circuit Operation**

#### General

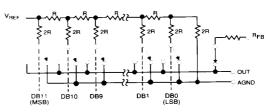

Figure 1 shows a simplified circuit of the D/A Converter section and Figure 2 gives an approximate equivalent switch circuit. R is typically  $11k\Omega$ .

The binary-weighted currents are switched between OUT and AGND by N-channel switches, thus maintaining a constant current in each ladder leg independent of the switch state.

The capacitance at the OUT terminal, C<sub>OUT</sub>, is code dependent and varies from 70pF (all switches to AGND) to 150pF (all switches to OUT).

The input resistance at  $V_{REF}$  (Figure 1) is always equal to  $R_{LDR}$  ( $R_{LDR}$  is the R/2R ladder characteristics resistance and is equal to value "R"). Since the input resistance at the  $V_{REF}$  pin is constant, the reference terminal can be driven by a reference voltage or a reference current, ac or dc, of positive or negative polarity. (If a current source is used, a low-temperature-coefficient external  $R_{FB}$  is recommended to define scale factor.)

#### **Digital Section**

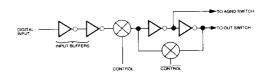

Figure 2 shows the digital structure for one bit. The digital signals CONTROL and CONTROL are generated from CS and WR.

The input buffers are simple CMOS inverters designed such that when the PM-7545 is operated with  $V_{\rm DD}=5V$ , the buffers convert TTL input levels (2.4V and 0.8V) into CMOS logic levels. When the digital input is in the region of 1.0 volts to 6.0 volts, the input buffers operate in their linear region and draw current from the power supply. To minimize power supply currents, it is recommended that the digital input voltages be as close to the supply rails ( $V_{\rm DD}$  and DGND) as is practically possible. The PM-7545 may be operated with any supply voltage in the ranage  $5 \le V_{\rm DD} \le 15$  volts. With  $V_{\rm DD} = +15V$ , the input logic livels are CMOS compatible only, i.e., 1.5V and 13.5V.

FIGURE 1: Simplified Schematic Of The HS7545

FIGURE 2: Digital Input Structure Of The HS7545

FIGURE 3: Write Cycle Timing Diagram

#### **Parameter Definitions**

#### **Relative Accuracy**

Sometimes referred to as endpoint nonlinearity, and is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. Relative Accuracy is measured after the zero and full-scale points have been adjusted, and is normally expressed in LSB or as a percentage of full scale.

#### **Differential Nonlinearity**

This is the difference between the measured change and the ideal change between any two adjacent codes. A differential nonlinearity of  $\pm 1$  LSB maximum over the full operating temperature range will ensure that a device is monotonic (the output will increase for an increase in digital code applied).

#### Gain Error

Gain or full scale error is the amount of output error between the ideal output and the actual output. The ideal output is  $V_{\text{REF}}$  minus 1 LSB. The gain error is adjustable to zero using external resistance.

#### **Output Capacitance**

The capacitance from OUT to AGND.

#### **Propagation Delay**

This is measured from the digital input change to the analog output current reaching 90% of its final value. It is a measure of the DAC's internal circuitry

#### **Digital Charge Injection**

This is a measure of the amount of charge injected to the analog output from the digital inputs, when the digital inputs change states. It is the area of the glitch and is specified in nVsec; it is measured with  $V_{\text{REF}} = AGND$ .

#### **Applications**

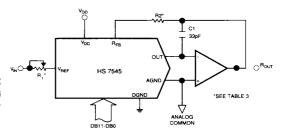

#### **Unipolar Operation**

Figure 4 shows a simple unipolar circuit. Resistor  $R_1$  is used to trim for full scale. The HS 7545 GLN, HS 7545 GCQ and HS 7545 GUD have a guaranteed maximum gain error of  $\pm 1$  LSB at 25°C and  $V_{DD} = \pm 5V$ , and in many applications the gain trim resistors are not required. Capacitor C1 provides phase compensation and helps prevent overshoot and ringing when using high speed op amps. The circuit of Figure 4 has constant input impedance at the  $V_{REF}$  terminal.

The circuit of Figure 4 can either be used as a fixed reference D/A converter so that it provides an analog output voltage in the range 0 to- $V_{IN}$  (the inversion is introduced by the op amp); or  $V_{IN}$  can be an ac signal in which case the circuit behaves as an attenuator (2-Quadrant Multiplier).  $V_{IN}$  can be any voltage in the range  $-20 \le V_{IN} \le +20$  volts (provided the op amp can handle such voltages) since  $V_{REF}$  is permitted to exceed  $V_{DD}$ . Table1 shows the code relationship for the circuit of Figure 4.

FIGURE 4: Unipolar Circuit Operation

| BINARY NUMBER IN<br>DAC REGISTER |      |      | ANALOG OUTPUT                                             |

|----------------------------------|------|------|-----------------------------------------------------------|

| 1111                             | 1111 | 1111 | -V <sub>IN</sub> { 4095 }                                 |

| 1000                             | 0000 | 0000 | $-V_{IN} \left\{ \frac{2048}{4096} \right\} = -1/2V_{IN}$ |

| 0000                             | 0000 | 0001 | -V <sub>IN</sub> { $\frac{1}{4096}$ }                     |

| 0000                             | 0000 | 0000 | 0 Volts                                                   |

**TABLE 1:** Unipolar Operation Binary Code Table

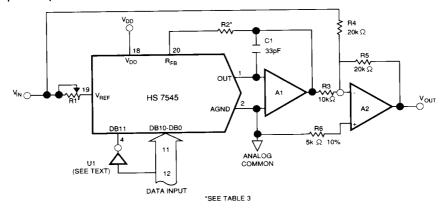

#### Bipolar Operation (2's Complement Code)

FIGURE 5: Bipolar Circuit Operation

Figure 5 shows a simple bipolar circuit configuration. Resistor  $R_{1}$  is used to trim for full scale. The HS-7545 GLN, HS-7545 GCQ and HS-7545 GUD have a guaranteed maximum gain error of  $\pm 1$  LSB at +25°C and  $V_{\rm DD}$  = +5V, and in many applications, the gain trim resistors are not required. Capacitor  $C_{1}$  provides phase compensation and helps prevent overshoot and ringing when using high speed opamps. The circuit of Figure 5 has constant input impedance at the  $V_{\rm REF}$  terminal.

Figure 5 and Table 2 illustrate the recommended circuit and code relationship for bipolar operation. The D/A function itself uses offset binary code. The inverter  $U_{\rm 1}$  on the MSB line, converts 2's-complement input code to offset binary code. The inverter  $U_{\rm 1}$  may be omitted if the inversion is done in software.

R3, R4 and R5 must match within 0.01% and should be the same type of resistors (preferably wire-wound or metal foil), so that their temperature coefficients match. Mismatch of R3 value to R4 causes both offset and full scale error. Mismatch of R5 to R4 and R3 causes full scale error.

|      | RY NUME<br>C REGIS |      | ANALOG OUTPUT                                         |

|------|--------------------|------|-------------------------------------------------------|

| 0111 | 1111               | 1111 | +V <sub>IN</sub> $\left\{ \frac{2047}{2048} \right\}$ |

| 0000 | 0000               | 0001 | $+V_{IN}\left\{\frac{1}{2048}\right\}$                |

| 0000 | 0000               | 0000 | 0 Volts                                               |

| 1111 | 1111               | 1111 | -V <sub>IN</sub> { $\frac{1}{2048}$ }                 |

| 1000 | 0000               | 0000 | $-V_{IN} \left\{ \frac{2048}{2048} \right\}$          |

**TABLE 2:** Bipolar Operation Code Table (2's Complement Code)

#### **Trim Resistor Values**

Table 3 shows the recommended trim resistor values for  $R_1$  and  $R_2$  in the circuits of Figure 4 & 5.

| Trim     | HS-7545                | HS-7545     |

|----------|------------------------|-------------|

| Resitor  | KN/BQ/TQ               | GLN/GCQ/GUQ |

| R₁<br>R₂ | $100\Omega$ $33\Omega$ | 20Ω<br>6.8Ω |

Table 3: Recommended Trim Resistor Value

# **Ordering Information**

| PART #      | PACKAGE                | TEMP<br>RANGE (°C) | RELATIVE<br>ACCURACY | GAIN<br>ERROR |

|-------------|------------------------|--------------------|----------------------|---------------|

| HS 7545 KN  | 20 Pin Epoxy Dip       | 0 to 70            | ± 1/2 LSB            | ± 3 LSB       |

| HS 7545 GLN | 20 Pin Epoxy Dip       | 0 to 70            | ± 1/2 LSB            | ± 1 LSB       |

| HS 7528 BQ  | 20 Pin Hermetic CERDIP | -25 to 85          | ± 1/2 LSB            | ± 3 LSB       |

| HS 7545 GCQ | 20 Pin Hermetic CERDIP | -25 to 85          | ± 1/2 LSB            | ± 1 LSB       |

| HS 7528 TQ  | 20 Pin Hermetic CERDIP | -55 to 125         | ± 1/2 LSB            | ± 3 LSB       |

| HS 7545 GUQ | 20 Pin Hermetic CERDIP | -55 to 125         | ± 1/2 LSB            | ± 1 LSB       |

<sup>•</sup> For devices processed in total compliance with MIL-STD-883, add /883 after the part number. Consult factory for 883 data sheet.

#### **CROSS REFERENCE INFORMATION**

| ADI Part No. | DataLinear Part No. |

|--------------|---------------------|

| AD 7545 JN   | HS 7545 KN          |

| AD 7545 KN   | HS 7545 KN          |

| AD 7545 LN   | HS 7545 GLN         |

| AD 7545 GLN  | HS 7545 GLN         |

| AD 7545 AQ   | HS 7545 BQ          |

| AD 7545 BQ   | HS 7545 BQ          |

| AD 7545 CQ   | HS 7545 GCQ         |

| AD 7545 GCQ  | HS 7545 GCQ         |

| AD 7545 SD   | HS 7545 TQ          |

| AD 7545 TD   | HS 7545 TQ          |

| AD 7545 UD   | HS 7545 GUD         |

| AD 7545 GUD  | HS 7545 GUD         |

The information in this document is subject to change without notice. SIPEX Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose, SIPEX Corporation assumes no responsibility for any errors that may appear in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of SIPEX Corporation.

<sup>•</sup> Package Designations: Suffix N Plastic DIP, Suffix Q Hermetic DIP. For package mechanical dimensions, call DataLinear at (408) 945-9080.