# 89151 T-LINK COMMUNICATIONS CONTROLLER

- Complete Implementation of the T-Link Rate Adaption Protocol in a Single Device

- Adapts Synchronous or Asynchronous Terminals to 64 Kbit/s Clear or Restricted Channels

- Rate Adaption of Asynchronous Data at Rates of 300 Bit/s to 19.2 Kbit/s

- Rate Adaption of Synchronous Data at Rates of 1200 Bit/s to 64 Kbit/s

- Implements CCITT I.515 Protocol Identification for use in Multiple Rate Adaption Environments

- Provides Interworking Capability to the ISDN

- Supports Exchange of Terminal Status Indicators

- Provides Error Correction for Data Rates of 9600 Bit/s or Less

- Supports Parallel and Serial DTE Data

- Serial Terminal Interface Including EIA or CCITT Handshake Leads

- General Purpose Parallel Microprocessor Interface

- Stand-Alone Mode of Operation

- Synchronous Serial Network Interface

- **SLD Compatible**

- **IDL Compatible**

- **Low Power, High Density CHMOS**

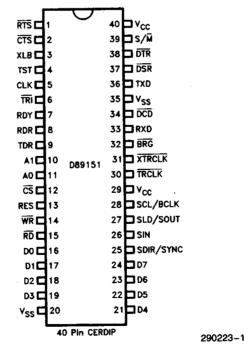

- Available in 40-Pin CERDIP Package (See Packaging Spec. Order # 231369)

The Intel 89151 T-Link Communications Controller (TCC) is a highly integrated communications controller which provides a complete implementation of the T-Link rate adaption protocol. The 89151 is used to adapt synchronous or asynchronous terminals to the public switched digital network, or an ISDN, providing transparent, digital end to end communications. The 89151 includes a serial terminal interface which supports synchronous or asynchronous terminals, a synchronous serial network interface, and a general purpose parallel microprocessor interface. The 89151 can operate as a peripheral to a wide variety of microprocessors.

DataShe

Figure 1. 89151 Pin Configuration

September 1989 Order Number: 290223-001

Table 1. 89151 Pin Description

| Symbol          | Pin No. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>CC</sub> | 29, 40  |      | POWER: +5V Power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| V <sub>SS</sub> | 20, 35  |      | GROUND: 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

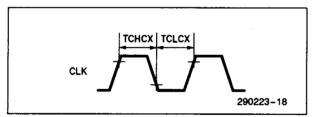

| CLK             | 5       | ı    | SYSTEM CLOCK: The 12 MHz internal system clock is input on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| RES             | 13      |      | <b>RESET:</b> (Active high input.) A high pulse on this pin instruct the 89151 to perform a self test of its internal functions and initializes the registers to the default settings. A high pulse lasting 100 ms after power-up or a 10 μs pulse while power up will reset the 89151. Operation begins after the high lever removed.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| S/M             | 39      |      | SLAVE/MASTER SELECT: A high level on this pin selects the 89151 to operate in the slave mode. In the slave mode local microprocessor is required to control the state transitions of the 89151. A low level on this pin selects the 89151 to operate in the master or stand-alone mode. In the stand-alone mode the 89151 functions without a local microprocessor and the state transitions are controlled internally.  THREE-STATE: (Active low input.) When both this pin and                                                                                                                                                                                                 |  |  |  |

| TRI             | 6       | 1    | THREE-STATE: (Active low input.) When both this pin and the S/M pin are low, all output pins and the SLD/SOUT pin are three-stated, and D0-D7 become input pins. For normal operation of the 89151 the TRI pin must be high.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| TST             | 4       | 1    | TEST PIN: This test pin should be connected to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| XLB             | 3       | D    | INVERT SLD/IDL DATA: A high level on this pin accomplements the transmit and receive data on the serial network interface independent of which interface, SLD or IDL, the 89151 has been configured to support. For normal SLD/IDL data this pin should be low.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| SLD/SOUT        | 27      | 1/0  | SUBSCRIBER LINE DATALINK/IDL TRANSMIT DATA: The function of this pin is dependent upon which serial network interface the 89151 has been configured to support. If the SLD interface is supported, this pin is a ping-pong data I/O used to transfer serial data between the 89151 and an SLD master device (e.g., 29C53AA). Receive SLD data is clocked into the SLD pin on the falling edge of SCL; transmit SLD data is clocked out of the SLD pin on the rising edge of SCL. If the IDL interface is supported, this pin is a data output used to transmit serial data to an IDL master device. Transmit IDL data is clocked out of the SOUT pin on the rising edge of BCLK. |  |  |  |

| SIN             | 26      |      | IDL RECEIVE DATA: If the 89151 has been configured to support the IDL interface, serial data is received on this pin from an IDL master device. Receive IDL data is clocked into the SIN pin on the falling edge of BCLK. If the 89151 is configured to support the SLD interface, this pin has no function and should be connected to either VSS or VCC.                                                                                                                                                                                                                                                                                                                        |  |  |  |

et4U.com

Table 1. 89151 Pin Description (Continued)

| Symbol                                 | Pin No.                                      | Туре                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------|----------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL/BCLK                               | 28                                           | I                                             | SUBSCRIBER CLOCK/IDL CLOCK: The serial network interface data clock is input on this pin. The frequency of the signal applied to this pin is dependent upon which serial network interface the 89151 is configured to support. If the SLD interface is supported, a 512 KHz signal should be applied to the SCL pin to clock data into and out of the SLD pin. If the IDL interface is supported and the 89151 is using the B1 channel, a 64 KHz to 2.56 MHz signal can be applied to the BCLK pin to clock data into and out of the SIN and SOUT pins. When the 89151 is using the B2 channel of the IDL interface, a 160 KHz to 2.56 MHz signal can be applied to the BCLK pin. |

| SDIR/SYNC                              | 25                                           | 1                                             | SUBSCRIBER DIRECTION/IDL SYNC: The function of the 8 KHz signal applied to this pin is dependent upon which serial network interface the 89151 has been configured to support. If the SLD interface is supported, the 8 KHz signal applied to the SDIR pin indicates SLD data direction and provides SLD data framing. A high level indicates that the 89151 is receiving data on the SLD pin; a low level indicates that the 89151 is transmitting data on the SLD pin. If the IDL interface is supported, the 8 KHz signal applied to the SYNC pin provides IDL data framing, with the falling edge of this signal indicating the beginning of a frame.                         |

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6 | 16<br>17<br>18<br>19<br>21<br>22<br>23<br>24 | 1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0 | DATA PINS: These data pins interface with the system data bus and allow the transfer of data to and from the 89151. Do is the least significant bit and D7 is the most significant bit of the data bus. When the 89151 is selected to operate in the astand-alone mode, pins D0–D7 become an input port which defines the operational parameters of the 89151. Refer to Table 2.                                                                                                                                                                                                                                                                                                  |

| A0<br>A1                               | 11<br>10                                     | l                                             | ADDRESS PINS: These address pins are used to select one of the directly addressable internal registers of the 89151. Refer to Table 3. When the 89151 is selected to operate in the stand-alone mode, the A1 pin selects which serial network interface the 89151 is going to support. A high level on A1 selects the SLD interface; a low level on A1 selects the IDL interface.                                                                                                                                                                                                                                                                                                 |

| CS                                     | 12                                           | l l                                           | CHIP SELECT: (Active low input.) A low level on this pin selects the 89151 and allows read or write operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WR                                     | 14                                           | l                                             | WRITE: (Active low input.) When the 89151 is selected and WR changes from a low to a high, data on pins D0-D7 is latched into the selected register of the 89151.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RD                                     | 15                                           | 1                                             | <b>READ:</b> (Active low input.) When the 89151 is selected and RD is low, data is transferred from the selected register of the 89151 to the data pins D0-D7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 1. 89151 Pin Description (Continued)

| Symbol Pin No. Type Function |         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|------------------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                       | Pin No. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| RDY                          | 7       | 0    | READY: (Active high output.) A high level on this pin indicates to the local microprocessor that the address register (ADR) can be written, or that the bus interface register (BIR) can be written or read. Writing to ADR causes the RDY pin to go low. See Figure 9 for details on accessing the indirect registers of the 89151. When the 89151 is selected to operate in the stand-alone mode, RDY, RDR, and TDR indicate the status of the 89151. Refer to Table 2. |  |  |  |  |

| RDR                          | 8       | 0    | RECEIVE DATA READY: (Active high output.) A high level on this pin indicates to the local microprocessor or DMA controller that data is available to be read from the DTE data register (DTED). When the 89151 is selected to operate in the stand-alone mode, RDY, RDR, and TDR indicate the status of the 89151. Refer to Table 2.                                                                                                                                      |  |  |  |  |

| TDR                          | 9       | 0    | TRANSMIT DATA READY: (Active high output.) A high level on this pin indicates to the local microprocessor or DMA controller that data can be written to the DTE data register (DTED). When the 89151 is selected to operate in the standalone mode, RDY, RDR, and TDR indicate the status of the 89151. Refer to Table 2.                                                                                                                                                 |  |  |  |  |

| DTR                          | 38      | l    | DATA TERMINAL READY: (Active low input.) A low level on this pin indicates to the 89151 that the DTE is ready to operate. Data terminal ready can alternatively be asserted by the local microprocessor through configuration register 1 (CFR1).                                                                                                                                                                                                                          |  |  |  |  |

| DSR                          | 37      | 0    | DATA SET READY: (Active low output.) A low level on this pin indicates to the DTE that the 89151 is ready to exchange further control signals to initiate the transfer of data.                                                                                                                                                                                                                                                                                           |  |  |  |  |

| RTS                          | 1       | 1    | REQUEST TO SEND: (Active low input.) A low level on this pin indicates to the 89151 that the DTE is requesting the 89151 to assume the network transmit mode. Request to send can alternatively be asserted by the local microprocessor through configuration register 1 (CFR1).                                                                                                                                                                                          |  |  |  |  |

| CTS                          | 2       | 0    | CLEAR TO SEND: (Active low output.) A low level on this pin indicates to the DTE that the 89151 is prepared to accept data for transmission to the network.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| DCD                          | 34      | 0    | DATA CARRIER DETECT: (Active low output.) This pin reflects the complement of the RTS T-Link signaling bit sent by the far-end TE. When the DCD pin goes low, the 89151 then sends a clear to send indicator back to the far-end TE through the CTS T-Link signaling bit.                                                                                                                                                                                                 |  |  |  |  |

| TXD                          | 36      | 1    | TRANSMIT DATA: Serial data transmitted by the DTE is input on this pin. When the 89151 is configured for synchronous serial DTE data, the serial data input on the TXD pin is sampled on the rising edge of TRCLK or XTRCLK, depending on the source of the serial terminal interface clock.                                                                                                                                                                              |  |  |  |  |

Table 1. 89151 Pin Description (Continued)

| Symbol | Pin No. | Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD    | 33      | 0    | RECEIVE DATA: Serial data received by the DTE is output on this pin. When the 89151 is configured for synchronous serial DTE data, the serial data is shifted out of the RXD pin on the falling edge of TRCLK or XTRCLK, depending on the source of the serial terminal interface clock.                                                                                                                                                                                         |

| TRCLK  | 30      | 0    | TRANSMIT/RECEIVE CLOCK: This clock output provides the timing for the synchronous serial data exchange between the DTE and the 89151 when the 89151 is configured to provide the serial terminal interface clock. If the 89151 is configured to use the serial terminal interface clock provided by the DTE on the XTRCLK pin, then TRCLK = XTRCLK. The TRCLK pin is clamped high during asynchronous operation.                                                                 |

| XTRCLK | 31      | ı    | external transmit/receive clock: The clock input on this pin provides the timing for the synchronous serial data exchange between the DTE and the 89151 when the 89151 is configured to use the serial terminal interface clock provided by the DTE. If the 89151 is configured for asynchronous operation or configured to provide the serial terminal interface clock on the TRCLK pin, the XTRCLK pin should be connected to V <sub>CC</sub> through a weak pull up resistor. |

| BRG    | 32      | 0    | BAUD RATE GENERATOR CLOCK: This clock output provides the 1X baud rate clock during synchronous operation and the 16X baud rate clock during asynchronous operation.                                                                                                                                                                                                                                                                                                             |

DataSheet4U.com

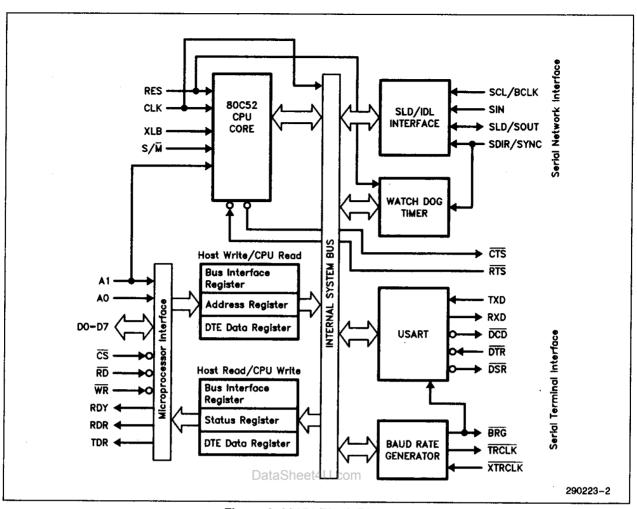

Figure 2. 89151 Block Diagram

et4U.com

# INTRODUCTION

The 89151 T-Link Communications Controller provides a T-Link building block for implementing a Terminal Adaption Device (TAD) that may be used for an ISDN Terminal Adaptor (TA) or other TAD application. The complete T-Link rate adaption protocol is built into the 89151. The 89151 rate adapts both synchronous and asynchronous Data Terminal Equipment (DTE) to a full duplex 64 Kbit/s channel.

In ISDN TA applications the rate adaption protocol to be supported is left up to the Customer Premises Equipment (CPE) manufacturers. The protocol identifier (PID) as defined in appendix A of CCITT I.515 is used to coordinate the rate adaption protocol used in a TA. The 89151 implements the CCITT I.515 protocol identification to assist CPE manufacturers who are implementing multiple rate adaption protocols in their TAs.

# T-LINK RATE ADAPTION PROTOCOL

T-Link is a full duplex byte oriented rate adaption protocol designed to transfer either synchronous or asynchronous data over a switched digital circuit at data rates from 300 bit/s to 64 Kbit/s. The T-Link protocol can be used over a 64 Kbit/s clear channel, or over a 64 Kbit/s restricted channel that permits

the use of the full 64 Kbit/s capacity, but with a 1's density requirement. T-Link can also be used over a 64 Kbit/s channel with capacity restricted to 56 Kbit/s due to the use of inband signaling or a 1's density requirement of today's T1 networks. The T-Link rate adaption protocol provides:

- End to end synchronization.

- Support of terminals with synchronous data rates from 1200 bit/s to 64 Kbit/s.

- Support of terminals with asynchronous data rates from 300 bit/s to 19.2 Kbit/s.

- Exchange of EIA or CCITT terminal status indicators

- Error correction for data rates of 9600 bit/s or less.

- Optional capability of requesting the restart of the rate adaption procedure.

- Optional capability of adapting to the requested parameters from the originating Terminal Equipment (TE).

- Far-end loopback requests.

Networks providing circuit switched 64 Kbit/s data transmission are ideal for providing high speed, wide area data transfer. T-Link provides a rate adaption protocol which can be used by a TAD to connect present DTEs to such networks. The T-Link protocol can be used over existing networks as well as over the ISDN. See Figure 3.

DataSheet4U. Com ISDN. See Figure 3.

TAD

TRUNK NON-ISDN DIGITAL NETWORK

NETWORK

15DN T-LINK

290223-3

Figure 3. Rate Adaption for the Switched Digital Network

et4U.com

# 89151 ARCHITECTURAL OVERVIEW

There are three separate interfaces to the 89151 which facilitate its use in Data Communication Equipment (DCE) applications supporting the T-Link rate adaption protocol. The general purpose parallel microprocessor interface which allows the 89151 to operate as a peripheral to a wide variety of microprocessors. The serial terminal interface which supports both synchronous and asynchronous terminals. The serial network interface which supports both the Intel Subscriber Line Datalink (SLD) and the Northern Telecom Interchip Digital Link (IDL) interfaces. See Figure 2.

# **MICROPROCESSOR INTERFACE**

The general purpose parallel microprocessor interface allows the 89151 to operate with a wide variety of microprocessors and microcontrollers. This interface is used to support both the slave and standalone modes of operation as selected by the level on the  $S/\overline{M}$  pin.

In the slave mode, S/M=1, a local microprocessor is required to control the state transitions of the 89151 in order to establish and maintain a T-Link connection with the far-end TE. The local microprocessor must also configure the operating parameters of the 89151 when in the slave mode. The RDY, RDR, and TDR output pins are available toet4 facilitate the process of transferring commands, status, or data between the 89151 and a local microprocessor or DMA controller. Alternatively, the complement of these output pins are available by reading the status register (SR) of the 89151.

In the stand-alone mode,  $S/\overline{M}=0$ , the 89151 functions without a local microprocessor, and the state transitions required to establish and maintain a T-Link connection are done internally by the 89151. The operating parameters to be used by the 89151 are configured by the levels on the D7-D0 and A1 pins. The status of the 89151 is indicated by the levels on the RDY, RDR, and TDR output pins. Refer to Table 2.

#### SERIAL TERMINAL INTERFACE

The serial terminal interface supports synchronous terminals with data rates from 1200 bit/s to 64 Kbit/s, and asynchronous terminals with data rates from 300 bit/s to 19.2 Kbit/s. Since the T-Link protocol carries the terminal status indicators across the connection through the T-Link Sd bytes (EIA/CCITT signaling), the standard EIA/CCITT handshake leads are provided. The complement of the output EIA/CCITT handshake leads are available by reading the status register (SR) of the 89151. The input EIA/CCITT handshake signals can be asserted by the local microprocessor through configuration register 1 (CFR1).

The translation of the terminal status indicators as they are carried across the connection through the T-Link Sd bytes (EIA/CCITT signaling) to the far-end TE is as follows:

DATA TERMINAL READY (DTR) — DATA SET READY (DSR)

REQUEST TO SEND (RTS) — DATA CARRIER DETECT (DCD)

CLEAR TO SEND (CTS) 4

290223-20

DataShe

The function of the EIA/CCITT handshake signals differs slightly depending on the configuration of the 89151 when in the data mode state.

For asynchronous operation:

If DCD or DSR is off, no data is sent to the DTE on the RXD pin.

If RTS is off or if a break has been received from the far-end TE through the break bit in the T-Link Sd bytes, no data is sent to the far-end TE. The EIA/CCITT handshake signal information is still sent to the far-end TE through the T-Link Sd bytes.

For synchronous operation below 48 Kbit/s:

If DCD is off, all 1's are sent to the DTE on the RXD pin.

If RTS if off, all 1's are sent to the serial network interface.

If DSR is off, the data being transmitted or received by the DTE is unaffected.

For 48, 56, and 64 Kbit/s synchronous operation:

If DTR is off, the local RTS and DCD get turned off. All 1's are sent to the DTE on the RXD pin, and all 1's are sent to the serial network interface.

In all cases, CTS is logically "ANDed" with the local RTS to allow CTS to turn off quickly when RTS if off.

The clock which provides the timing for the synchronous serial data exchange between the DTE and the 89151 can either be supplied by the 89151 on the TRCLK pin, or the 89151 can accept an external clock from the DTE on the XTRCLK pin. Only one end of a T-Link connection should be accepting an external clock from the DTE. If both ends are accepting an external clock from the DTE, the T-Link parameter exchange will not be successfully

completed. When the 89151 is configured for synchronous serial DTE data, the data input on the TXD pin is sampled on the rising edge of TRCLK or XTRCLK, depending on the source of the serial terminal interface clock. The falling edge of TRCLK or XTRCLK, depending on the source of the serial terminal interface clock, shifts data out of the 89151 on the RXD pin when the 89151 is configured for synchronous serial DTE data.

The 89151 provides a baud rate generator clock on the BRG pin which can be used for external timing purposes. The 1X baud rate clock is provided on the BRG pin during synchronous operation, and the 16X baud rate clock is provided during asynchronous operation.

# SERIAL NETWORK INTERFACE

The serial network interface is designed to transfer serial data between the 89151 and the network side of the TAD. The serial data is coded according to the T-Link protocol and transferred at a rate of 64 Kbit/s. The serial network interface supports both the Intel Subscriber Line Datalink (SLD) and the Northern Telecom Interchip Digital Link (IDL) interfaces.

# **SLD Interface**

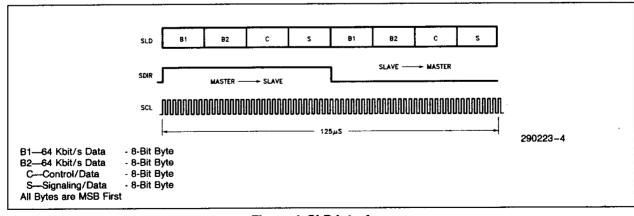

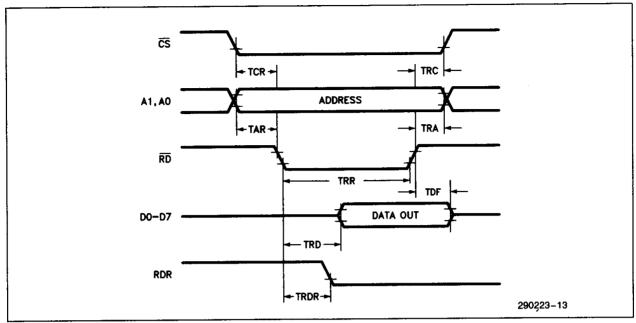

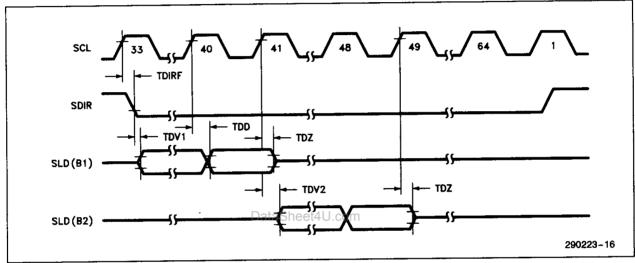

When the 89151 is configured to support the SLD interface, serial data is transferred bidirectionally on the SLD pin between the 89151 and a SLD master device (e.g., 29C53AA). A 512 KHz data clock should be input on the SCL pin, and a 8 KHz signal should be input on the SDIR pin to indicate SLD data direction and provide SLD data framing. The SIN pin has no function when the SLD interface is supported, so this input pin should be connected to VSS or VCC. Receive SLD data is clocked into the SLD pin on the falling edge of SCL when SDIR is high. Transmit SLD data is clocked out of the SLD pin on the rising edge of SCL when SDIR is low. See Figure 4.

Figure 4. SLD Interface

5-54

et4U.com

The 89151 can operate over either the B1 or B2 channel, but only transmits data on the SLD pin during the assigned channel. This allows the 89151 to share the SLD interface with another SLD slave device, such as the 29C48 programmable CODEC/Filter. The 89151 places the SLD pin in a high impedance state during the transmit control and signaling bytes of the SLD interface.

# **IDL** Interface

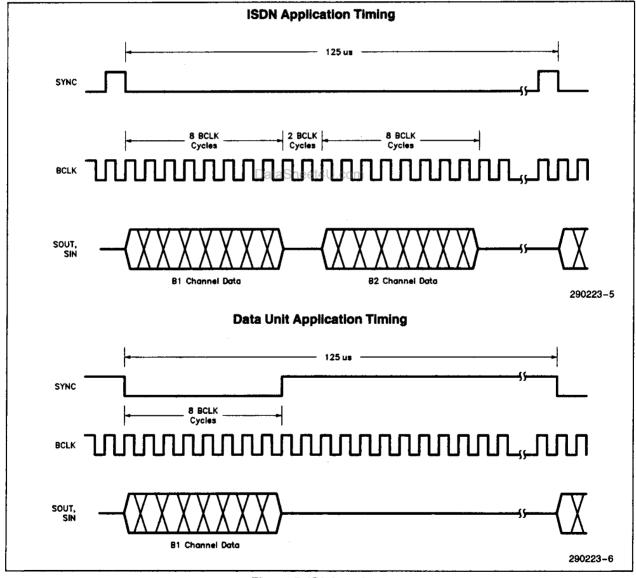

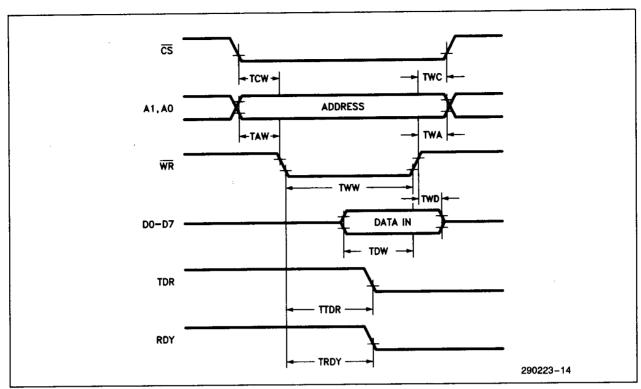

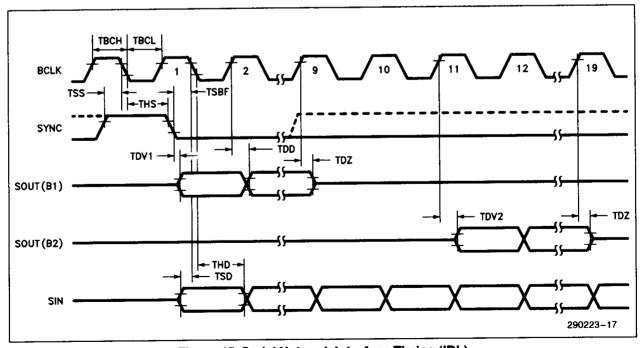

When the 89151 is configured to support the IDL interface, serial data is transferred in both directions simultaneously on the SIN and SOUT pins between the 89151 and a IDL master device. The 89151 can operate over either the B1 or B2 channel, but only the B1 channel of the IDL interface should be used in Data Unit applications, as shown in Figure 5. If the

89151 is using the B1 channel, a 64 KHz to 2.56 MHz data clock can be input on the BCLK pin. Whereas a 160 KHz to 2.56 MHz data clock can be input on the BCLK pin if the 89151 is using the B2 channel. A 8 KHz synchronization signal should be input on the SYNC pin to provide IDL data framing, with the falling edge of this signal indicating the beginning of a frame. Receive IDL data is clocked into the SIN pin on the falling edge of BCLK. Transmit IDL data is clocked out of the SOUT pin on the rising edge of BCLK. See Figure 5.

The 89151 only transmits data on the SOUT pin during the assigned B1 or B2 channel. The 89151 does not transmit during the D channel, auxiliary, or maintenance time slots of the IDL interface. The 89151 places the SOUT pin in a high impedance state during these time slots.

Figure 5. IDL Interface

5-55

www.DataSheet4U.com

DataShe

DataSheet4U.com

The 89151 can complement the transmit and receive data on the serial network interface independent of which interface, SLD or IDL, is supported. If the XLB pin is high, the serial network interface data will be complemented. For normal serial network interface data the XLB pin should be low. The 89151 reads the XLB pin during execution of a self test to determine if the serial network interface data should be complemented.

The SLD/SOUT pin is three-stated after the 89151 enters the self test state, and it can be three-stated at any time by setting the NIT bit in configuration register 0 (CFR0) to 1. The 89151 constantly monitors the NIT bit, and as soon as this bit is set to 1 the SLD/SOUT pin is three-stated. If the SLD/SOUT pin has been three-stated by setting the NIT bit to 1, the SLD/SOUT pin can be enabled by setting the NIT bit to 0 and instructing the 89151 to enter the setup state. This is useful for TAs which support multiple rate adaption protocols. The 89151 can be used to perform the PID exchange, and then if necessary the SLD/SOUT pin can be three-stated and another rate adaption device enabled onto the serial network interface.

# INTERNAL STATES

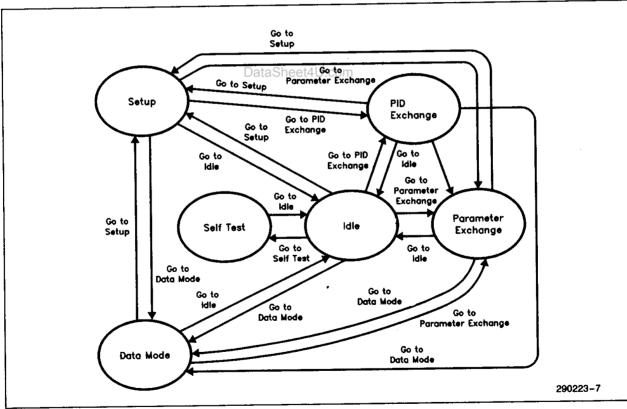

The 89151 functions as a state machine with each internal state of the 89151 performing a distinct part of the T-Link protocol. When the 89151 is in the slave mode, a local microprocessor controls the state transitions of the 89151 to establish and maintain a T-Link connection with the far-end TE. In the stand-alone mode the 89151 performs the required state transitions internally. Figure 6 shows the allowed state transitions of the 89151, and the corresponding command codes that need to be written to the general command status register (GCSR) in order for these state transitions to occur when the 89151 is in the slave mode.

# **Self Test**

The 89151 performs internal self test routines during this state. During the self test the internal ROM, internal RAM, USART, baud rate generator, and the serial network interface are tested. The registers of the 89151 are initialized to the default settings during the self test state. The self test state can only be entered from the idle state.

Figure 6. 89151 State Transitions

et4U.com

5-56

www.DataSheet4U.com

#### Idle

During this state the 89151 is inactive and T-Link Sgidle bytes (channel idle) are being transmitted on the serial network interface.

# Setup

The operating parameters of the 89151 that have been programmed by the local microprocessor in the configuration registers (CFR0-CFR3) and the loopback control register (LCR) are checked for correctness during this state. If the operating parameters are correct, the 89151 then configures itself for communication using these parameters. During the setup state the 89151 transmits T-Link Sgidle bytes (channel idle) on the serial network interface.

# PID Exchange

During this state the 89151 performs the protocol identifier (PID) exchange with the far-end TA. This PID exchange supports the protocol identification as defined in appendix A of CCITT 1.515. The PID exchange is used to coordinate which rate adaption protocol is used in a TA that supports multiple rate adaption protocols.

# **Parameter Exchange**

During this state the 89151 performs a T-Link hand-shake, called a parameter exchange, with the farend TE. If the parameter exchange state was not entered from the PID exchange state, then both ends of the T-Link connection acquire T-Link synchronization to each other, exchange T-Link protocol version identifiers (T-Link PID), and exchange their desired operating parameters to be used for communication. Upon successful completion of the T-Link parameter exchange, both ends of the T-Link connection agree on the version of the T-Link protocol to be used as well as the operating parameters to be used for communication.

When the parameter exchange state is entered from the PID exchange state, both ends of the T-Link connection are already synchronized to each other and the version of the T-Link protocol to be used is already agreed upon. Both ends of the T-Link connection then exchange their desired operating parameters and agree upon which parameters are going to be used for communication. The only time that the parameter exchange state is entered from the PID exchange state is when the local microprocessor has instructed the 89151 to go to the PID

exchange state and upon completion of the PID exchange the protocol agreed upon is T-Link. The 89151 then automatically enters the parameter exchange state.

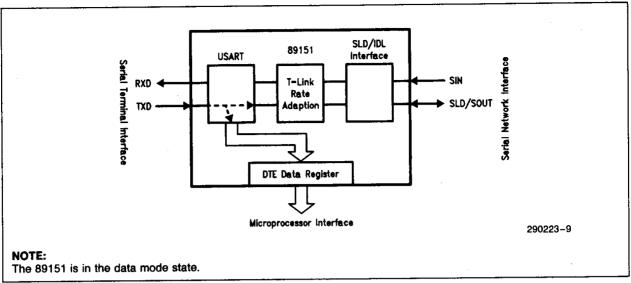

#### **Data Mode**

During this state the 89151 passes data between the serial network interface and either the serial terminal interface or the DTE data register (DTED), while rate adapting this data according to the T-Link protocol.

When the 89151 is operating in the slave mode, the local microprocessor should instruct the 89151 to enter the data mode state after a successful parameter exchange. If the data mode state is entered directly from the setup state, the 89151 automatically uses version 2 of the T-Link protocol. Then the operating parameters that will be used by the 89151 are those that the local microprocessor programmed in the configuration registers (CFR0-CFR3) and the loopback control register (LCR) prior to the 89151 entering the setup state. This method of going directly to the data mode state from the setup set allows the local microprocessor to configure the 89151 for transparent operation.

When transparent operation is required, the local microprocessor should write the desired operating parameters into the configuration registers (CFR0-CFR3) and the loopback control register (LCR) making sure that the 89151 is configured for 64 Kbit/s synchronous operation. The local microprocessor should instruct the 89151 to go to the setup state, and then directly to the data mode state. Once in the data mode state, the 89151 will pass 64 Kbit/s synchronous data transparently between the serial network interface and either the serial terminal interface or the DTE data register (DTED).

The 89151 can be configured for similar transparent operation when the 64 Kbit/s network channel is restricted to 56 Kbit/s due to the use of inband signaling or a 1's density requirement. In this case the local microprocessor should configure the 89151 for 56 Kbit/s synchronous operation before instructing the 89151 to go to the setup state, and then directly to the data mode state. Once in the data mode state, the 89151 will pass 56 Kbit/s synchronous data transparently between the serial network interface and either the serial terminal interface or the DTE data register (DTED). For 56 Kbit/s transparent operation the least significant bit of the B1 or B2 channel on the serial network interface is set to 1 for transmission and ignored on reception.

DataShe

# **SLAVE MODE**

When the  $S/\overline{M}$  pin is high, the 89151 is selected to operate in the slave mode. This mode is intended to be the normal operating mode of the 89151. A local microprocessor, communicating with the 89151 over the parallel microprocessor interface, is responsible for controlling the state transitions of the 89151.

The following illustrates the sequence of actions that a local microprocessor would perform to establish and maintain a T-Link connection:

#### 1. Reset

After being reset the 89151 enters the self test state. During the self test the RDY pin is low, and once the self test is complete the RDY pin goes high. The results of the self test can then be read from the bus interface register (BIR) as shown below. These self test results are no longer available from BIR once the local microprocessor has accessed an indirect register of the 89151.

| 7 | 6 | 5 | 4             | 3             | 2                            | 1           | 0           |

|---|---|---|---------------|---------------|------------------------------|-------------|-------------|

| x | x | x | USART<br>Test | Clock<br>Test | Network<br>Interface<br>Test | RAM<br>Test | ROM<br>Test |

0 = test passed; 1 = test failed

Alternatively, the local microprocessor could read the general command status register (GCSR) for the self test status, once the RDY pin is high, to deteret mine if the self test passed or failed. This is the only way for the local microprocessor to determine the status of the self test when the 89151 has been instructed to enter the self test state by a command written to GCSR. The self test results read from BIR are only available after completion of a self test that was initiated by the 89151 having been reset. If the self test passed, the 89151 should then be instructed to enter the idle state.

# NOTE:

In order for the network interface test to pass valid SCL/BCLK and SDIR/SYNC signals must be applied to the 89151.

# 2. Configuration of Operating Parameters

Once the 89151 is idle, the desired operating parameters should be configured. The operating parameters of the 89151 are configured through the configuration registers (CFR0-CFR3) and the loopback control register (LCR). Although these registers may be written at any time, it is recommended that they be written when the 89151 is in the idle state. Once the local microprocessor has configured the operating parameters, it should then instruct the 89151 to enter the setup state.

# NOTE:

If the 89151 is not instructed to go to the setup state, it will continue to use the parameters that were in use during the last T-Link connection, or the default operating parameters. The default operating parameters are defined by the default settings of the 89151 registers which are initialized during the self test state.

Once in the setup state, the 89151 checks the correctness of operating parameters that have been previously received in CFR0-CFR3 and LCR. If there is an error in these operating parameters received from the local microprocessor, the status message of "bad setup" will be returned in the general command status register (GCSR). New and correct operating parameters should then be sent and the 89151 should be instructed to reenter the setup state.

# 3. Establishment of the Link

This function is not performed by the 89151. Call setup and take down must be handled by the local microprocessor.

#### 4. Establishment of a T-Link Connection

To start a T-Link parameter exchange with the farend TE the local microprocessor must send the 89151 the command to go to the parameter exchange state. Two forms of this command are available, one for the originating TE and one for the answering TE. It is important that these distinctions be observed and these commands be used correctly. The local microprocessor is responsible for determining when the parameter exchange is complete by periodically reading the general command status register (GCSR) to determine the status of the 89151. If the parameter exchange is not completed after a reasonable period of time, the local microprocessor is responsible for initiating corrective action.

Alternatively, the 89151 could be instructed to perform a PID exchange with the far-end TA. To start the PID exchange the local microprocessor must send the 89151 the command to go to the PID exchange state. Two forms of this command are available, one for the originating TA and one for the answering TA. The same distinctions that need to be observed when using the two parameter exchange commands also need to be observed when using the two PID exchange commands. Once the PID exchange is complete and the protocol agreed upon is

DataShe

T-Link, the 89151 automatically enters the parameter exchange state. If the PID exchange is complete and the protocol agreed upon is not T-Link, the 89151 will indicate this status in GCSR. The local microprocessor should then read the PID from the protocol identifier register (PIR) and take the necessary actions to activate the appropriate rate adaption method.

# 5. Transition to and Maintaining Data Mode

Once the T-Link parameter exchange has been successfully completed, the 89151 should be instructed to go to the data mode state. When in the data mode state, the 89151 is passing data between the serial network interface and either the serial terminal interface or the DTE data register (DTED), while rate adapting this data according to the T-Link protocol. The local microprocessor is responsible for periodically reading the status of the 89151 from the general command status register (GCSR) and taking any necessary actions.

# 6. Completion of a Call

Actual take down of the call is the responsibility of the local microprocessor. When a call has been completed, the 89151 should be sent to the idle state.

# **Serial DTE Data**

When the 89151 is in the slave mode, DTE data can be sent and received through the serial terminal interface. The 89151 is configured for serial DTE data when the PDTE bit in configuration register 0 (CFR0) is set to 0. The following data rates are supported by the 89151 when configured for serial DTE data.

Asynchronous: 300, 1200, 2400, 4800, 9600, 19200 bit/s

Synchronous: 1200, 2400, 4800, 9600, 19200, 48000, 56000, 64000 bit/s

The 89151 provides some special features when configured for asynchronous serial DTE data. Once the 89151 has been configured and is currently in the idle state or data mode idle state, data written to the DTE data register (DTED) is sent out the serial terminal interface on the RXD pin. Likewise, data input on the TXD pin can be read from DTED. When the RDR pin is high or the RDR bit in the status register (SR) is 0, data is available to be read from DTED. When the TDR pin is high or the TDR bit in SR is 0, data can be written to DTED. This feature allows the local microprocessor to directly communicate with the DTE connected to the serial terminal interface of the 89151. See Figure 7.

If the local microprocessor wants to communicate with the DTE connected to the serial terminal interface while the 89151 is in the idle state, the local microprocessor needs to first configure the appropriate operating parameters of the 89151. The 89151 needs to be configured for asynchronous serial DTE data (SYNC=0 and PDTE=0 in CFR0), and the SLD/SOUT pin should be three-stated (NIT=1 in CFR0). The various asynchronous operating parameters should be configured in CFR2, and the appropriate data rate should be configured in CFR3. The DataSheet4U local microprocessor should instruct the 89151 to go to the setup state, and then directly to the data mode state. The 89151 should then be instructed to enter the idle state. Once the 89151 is in the idle state, the local microprocessor can communicate with the DTE connected to the serial terminal interface of the 89151.

NOTE:

The 89151 is in the idle state or data mode idle state.

Figure 7. Microprocessor to DTE Communication in the Idle or Data Mode Idle State

DataShe

Figure 8. Microprocessor to DTE Communication in the Data Mode State

When the 89151 is configured for asynchronous serial DTE data and is currently in the data mode state, data input on the TXD pin can be read from DTED, but data written to DTED will not get sent out the serial terminal interface on the RXD pin. When the RDR pin is high or the RDR bit in SR is 0, data is available to be read from DTED. This allows the local microprocessor to monitor the data transmitted by the DTE connected to the serial terminal interface of the 89151. See Figure 8.

If the local microprocessor wants to regain control of sending data to the DTE when the 89151 is configured for asynchronous serial DTE data and is currently in the data mode state, the 89151 should be instructed to enter the data mode idle state. The 89151 will maintain the T-Link connection by sending T-Link Sd bytes (EIA/CCITT signaling) to the farend TE while scanning for Sgr bytes (T-Link restart request) received from the far-end TE. When the local microprocessor is done communicating with the DTE, the 89151 should be instructed to enter the data mode state.

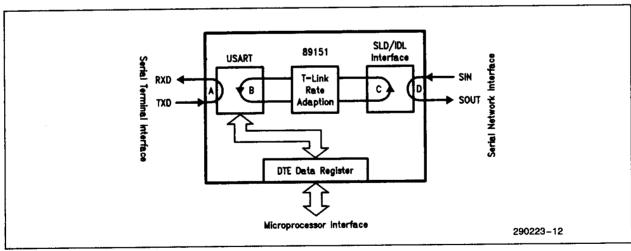

# **Parallel DTE Data**

When the 89151 is in the slave mode, DTE data can be sent and received through the parallel microprocessor interface instead of the serial terminal interface. The 89151 is configured for parallel DTE data when the PDTE bit in configuration register 0 (CFR0) is set to 1.

The DTE data register (DTED) and the RDR and TDR pins are used to implement this parallel mode of operation. The input EIA/CCITT handshake leads at the serial terminal interface are ignored during the parallel mode of operation, but these handshake signals can be controlled by the local microprocessor

through configuration register 1 (CFR1). The output EIA/CCITT handshake leads are maintained at the serial terminal interface during the parallel mode of operation, and the complement of these handshake leads can be read from the status register (SR). When the 89151 is configured for parallel DTE data, the TXD pin is internally connected to the RXD pin once the data mode state has been entered. This ensures that any data received on the serial terminal interface is looped back and does not interfere with the parallel mode of operation. The following data rates are supported by the 89151 when configured for parallel DTE data.

Asynchronous: 300, 1200, 2400, 4800, 9600, 19200 bit/s

Synchronous: 48000, 56000, 64000 bit/s

For asynchronous data up to 8 bits can be sent and received. For synchronous data 6 bits are supported for 48 Kbit/s, 7 bits for 56 Kbit/s, and 8 bits for 64 Kbit/s. Data less than 8 bits is always justified to the least significant bit of the DTE data register (DTED). The 89151 accepts parallel DTE data at the effective rate which was negotiated during the T-Link parameter exchange. For example, if after the T-Link parameter exchange the 89151 is configured for 7-bit asynchronous data, 1 start bit, even parity, 1 stop bit, at 9600 bit/s, the 89151 will expect new data to be written to DTED no faster than once every 1.04 ms.

To maintain a high data transfer rate the RDR and TDR pins can be used for interrupts or DMA requests. The complement of these pins can be read from the status register (SR) if polling is used. When the RDR pin is high or the RDR bit in SR is set to 0, this indicates that data should be read from DTED. If

DataShe

5-60

this data is not read from DTED before new decoded data arrives from the serial network interface, the old data will be overwritten. When the TDR pin is high or the TDR bit in SR is set to 0, this indicates that data should be written to DTED. If new data is not written to DTED when the 89151 is configured for synchronous operation, all ones will be sent to the serial network interface. The RDR and TDR pins are self clearing after DTED is read or written respectively.

# STAND-ALONE MODE

When the  $S/\overline{M}$  pin is low, the 89151 is selected to operate in the stand-alone mode. This mode allows the 89151 to function without a local microprocessor. In the stand-alone mode the 89151 actively reads the microprocessor interface to establish the operating parameters. The 89151 then automatically executes the state transitions required to establish a T-Link connection with the far-end TE.

The 89151 reads the  $S/\overline{M}$  pin after being reset and periodically thereafter to determine if the A1 pin should be read. When the 89151 is selected to operate in the stand-alone mode, the A1 pin selects which serial network interface the 89151 is going to support. A high level on A1 selects the SLD interface; a low level on A1 selects the IDL interface. The operating parameters are configured by the levels on the D7-D0 pins. Refer to Table 2. The 89151 continuously polls these pins checking for changes et al. in the operating parameters. When the 89151 is polling the D7-D0 pins it is actually reading this data from the address register (ADR). Therefore, the other pins of the microprocessor interface should be set for an ADR write as follows: A0 = 1,  $\overline{CS} = 0$ ,  $\overline{WR} = 0$ , and  $\overline{RD} = 1$ . This allows the operating parameters of the 89151 to be configured by a set of dip switches. When in the stand-alone mode, the status of the 89151 is indicated by the levels on the RDY, RDR. and TDR pins. Refer to Table 2.

When the 89151 is in the stand-alone mode, an alternate method of configuring the operating parameters of the 89151 requires a local microprocessor to write the configuration information, as shown in Table 2, to the address register (ADR). This is a simplified method of the slave mode since the local microprocessor only needs to perform one write to configure the operating parameters of the 89151. The local microprocessor can read the bus interface register (BIR) to obtain the current status of the 89151. The status messages read from BIR are the same as those read from the general command status register (GCSR) when the 89151 is in the slave mode. Refer to Table 6. The EIA/CCITT signaling bits and the break bit received in the T-Link Sd bytes (EIA/CCITT signaling), as well as the ready flags, can be read by the local microprocessor from the status register (SR).

In the stand-alone mode the 89151 is configurable for a subset of its full capabilities. The 89151 is non-adaptive or fixed when in the stand-alone mode. Therefore, the 89151 will not adapt to any of the operating parameters received from the far-end TE during the T-Link parameter exchange. This is because there is no way to determine the adapted configuration of the 89151 even if it was able to adapt to the received operating parameters. In the stand-alone mode the 89151 always uses the B1 channel of the serial network interface.

The 89151 supports both version 1 and 2 of the T-Link protocol when in the stand-alone mode. The 89151 does not have the capability to perform the originate function of the CCITT I.515 PID exchange in the stand-alone mode, since there is no way to pass the results of a PID exchange to a local microprocessor. When in the stand-alone mode, the 89151 can be the originating or answering end of a T-Link connection. The 89151 performs the T-Link protocol version exchange, which in the answering mode does follow the answering function of the CCITT I.515 PID exchange.

The following illustrates the sequence of actions that is repeated by the 89151 while operating in the stand-alone mode:

# 1. Self Test (RDY = 0, RDR = 0, TDR = 0)

The self test is automatically executed after the 89151 has been reset. If the 89151 passes the self test, it proceeds to step 2. RDY=0, RDR=1, and TDR=1 indicate that the self test failed. If the self test failed, the 89151 will continue to indicate the self test failed status until it is reset.

# 2. Setup (RDY = 1, RDR = 0, TDR = 0)

The 89151 will read the address register (ADR) and decode the D7-D0 pins according to Table 2, and enter the setup state. The 89151 then configures itself for communication using the parameters read from ADR and proceeds to step 3.

# 3. Parameter Exchange (RDY = 1, RDR = 0, TDR = 1)

The 89151 will enter the parameter exchange state. The 89151 will remain in this state until the T-Link parameter exchange is successfully completed. Once a successful T-Link parameter exchange has been completed the 89151 proceeds to step 4.

DataShe

5-61

www.DataSheet4U.com

# 4. Data Mode (RDY = 1, RDR = 1, TDR = 0)

The 89151 will enter the data mode state and begin passing data between the serial terminal interface and the serial network interface, while rate adapting this data according to the T-Link protocol. The 89151 responds to restart received and inband sync lost conditions by repeating steps 2 through 4.

The operating parameters of the 89151 may be changed at any time by altering the logic levels on the D7-D0 pins. When the 89151 detects that the D7-D0 pins have changed, it will go to the idle state and proceed with steps 2 through 4 of the above sequence.

**Table 2. Stand-Alone Mode Interface**

| ſ           |             |             |        |        | 8915°  | l Pins |        |                   |        |        |          |                                       |                                       |

|-------------|-------------|-------------|--------|--------|--------|--------|--------|-------------------|--------|--------|----------|---------------------------------------|---------------------------------------|

| R<br>D<br>Y | R<br>D<br>R | T<br>D<br>R | A<br>1 | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3            | D<br>2 | D<br>1 | 0        | Paramet                               | er/Status                             |

|             |             |             |        |        |        |        |        |                   |        |        |          | Async. (bit/s)                        | Sync. (bit/s)                         |

|             |             |             |        |        |        |        |        |                   | 0      | 0      | 0        | 1200                                  | 1200                                  |

|             |             |             |        |        |        |        |        |                   | 0      | 0      | 1        | 2400                                  | 2400                                  |

|             |             |             |        |        |        |        |        |                   | 0      | 1      | 0        | 4800                                  | 4800                                  |

| i           |             |             |        |        |        |        |        |                   | 0      | 1      | 1        | 9600                                  | 9600                                  |

|             |             |             |        |        |        |        |        |                   | 1      | 0      | 0        | 19200                                 | 19200                                 |

|             |             |             |        |        |        |        |        |                   | 1      | 0      | 1        | 300                                   | 48000                                 |

|             |             |             |        |        |        |        |        |                   | 1      | 1      | 0        | 300                                   | 56000                                 |

|             |             |             |        |        |        |        |        |                   | 1      | 1      | 1        | . 300                                 | 64000                                 |

|             |             |             |        |        |        |        |        | 0                 |        |        | <u> </u> | Asynchronous Data<br>Synchronous Data |                                       |

|             |             |             |        |        |        |        | 0      | ata Cla           | neet/I | 1 0000 |          | Originate Paramet                     |                                       |

|             |             |             |        |        |        |        |        | <del>ata Si</del> | 100141 | J.60H  |          | Async.                                | Sync.                                 |

| -           |             |             |        |        |        | 0      |        |                   |        |        |          | No Parity<br>Odd Parity               | External Clock<br>Internal Clock      |

|             |             |             |        |        | 0      |        |        |                   |        |        |          | 7-Bit Characters<br>8-Bit Characters  | Restarts Disabled<br>Restarts Enabled |

|             |             |             |        | 0      |        |        |        |                   | -      |        |          | 1 Stop Bit<br>2 Stop Bits             | Not Used<br>Not Used                  |

|             |             |             | 0      |        |        |        |        |                   |        |        |          | IDL Interface<br>SLD Interface        |                                       |

|             |             | 0           |        | •      |        |        |        |                   |        |        |          | Busy/Idle<br>In Parameter Exch        | nange                                 |

|             | 0           |             |        |        |        |        |        |                   |        |        |          | Not in Data Mode<br>In Data Mode      |                                       |

| 0           |             |             |        |        |        |        |        |                   |        |        |          | Under Test<br>Self Test Passed        |                                       |

et4U.com

# 89151 REGISTER DEFINITIONS

The following register definitions are applicable when the 89151, operating in the slave mode, is communicating with a local microprocessor over the parallel microprocessor interface.

# 89151 Directly Addressable Registers

The following registers are directly connected to the microprocessor interface. These registers are accessible and are available by a single microprocessor cycle access.

Table 3. 89151 Directly Addressable Registers

| <b>A1</b> | A0 | Access | Symbol | Function               |

|-----------|----|--------|--------|------------------------|

| 0         | 0  | RD, WR | BIR    | Bus Interface Register |

| 0         | 1  | RD     | SR     | Status Register        |

| 0         | 1  | WR     | ADR    | Address Register       |

| 1         | 0  | RD, WR | DTED   | DTE Data Register      |

| 1         | 1  | RD, WR | _      | Reserved               |

# Address Register (ADR)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

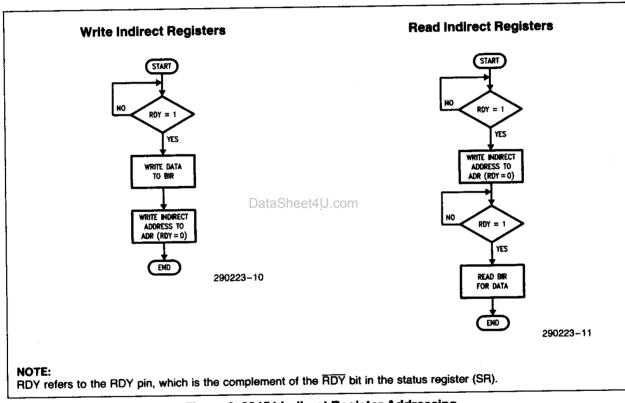

This register is used to intermediately store the address of registers during indirect addressing. Writing to ADR causes the RDY pin to go low and the  $\overline{\text{RDY}}$  bit in the status register (SR) to be set to 1.

# **Bus Interface Register (BIR)**

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |

|----|----|----|----|----|----|----|----|--|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |  |

This register is used to intermediately store data that is written or read from the indirectly addressable registers (GCSR, LCR, PIR, CFR0, CFR1, CFR2, and CFR3).

# **DTE Data Register (DTED)**

| 7 | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|---|---|---|-----|------|---|---|---|

|   |   | , | DTE | Data |   |   |   |

When the 89151 is configured for parallel DTE data (PDTE = 1 in CFR0), this register is used for passing

parallel DTE data to and from the 89151. This register is written with data to be sent to the serial network interface, and when read contains data received from the serial network interface. When the TDR pin is high or the  $\overline{\text{TDR}}$  bit in the status register (SR) is set to 0, this indicates that DTED should be written. When the RDR pin is high or the  $\overline{\text{RDR}}$  bit in SR is set to 0, this indicates that DTED should be read. Data less than 8 bits is justified to the least significant bit, bit 0, of DTED.

# Status Register (SR)

|   | 7 | 6   | 5   | 4   | 3   | 2   | . 1 | 0   |

|---|---|-----|-----|-----|-----|-----|-----|-----|

| 1 | X | BRK | DCD | DSR | CTS | RDR | TDR | RDY |

This register indicates the current status of the EIA/CCITT signaling bits and the break bit received in the T-Link Sd bytes (EIA/CCITT signaling) from the far-end TE, as well as the current status of the ready flags. This register may be read at any time. There is no ready handshake pin associated with reading SR.

BRK — Break received. When this bit is set to 1, the 89151 has received a break from the far-end TE through the break bit in the T-Link Sd bytes. When the 89151 is configured for asynchronous serial DTE data (SYNC=0 and PDTE=0 in CFR0) and a break has been received from the far-end TE, the 89151 will send a break on the serial terminal interface to the DTE.

DCD — Data carrier detect. This bit reflects the complement of the serial terminal interface  $\overline{DCD}$  handshake lead.

DSR — Data set ready. This bit reflects the complement of the serial terminal interface DSR handshake lead.

CTS — Clear to send. This bit reflects the complement of the serial terminal interface CTS handshake lead.

RDR — Receive data ready. When this bit is set to 0, data is available to be read from the DTE data register (DTED). This bit reflects the complement of the RDR output pin.

TDR — Transmit data ready. When this bit is set to 0, data can be written to the DTE data register (DTED). This bit reflects the complement of the TDR output pin.

DataShe

RDY — Ready. This bit along with the address register (ADR) and the bus interface register (BIR) are used to access the indirectly addressable registers of the 89151. Writing to ADR causes this bit to be set to 1 and the RDY pin to go low. This bit reflects the complement of the RDY output pin.

# 89151 Indirectly Addressable Registers

The following registers are not directly connected to the microprocessor interface and may be accessed through indirect addressing as detailed in Figure 9. Indirect addressing uses the contents of the address register (ADR) as a pointer to the indirect registers. Example: The following sequence illustrates how a local microprocessor would instruct the 89151 to go to the setup state by writing to the indirectly addressable general command status register (GCSR).

- Once the RDY pin is high or the RDY bit in the status register (SR) is 0, the local microprocessor writes the GSUP command code of 01H to the bus interface register (BIR). Refer to Table 5.

- The local microprocessor writes 00H to the address register (ADR), which is the address of GCSR for a write operation. Refer to Table 4. The 89151 then transfers the contents of BIR to GCSR.

Figure 9. 89151 Indirect Register Addressing

Table 4. 89151 Indirectly Addressable Registers

| ADR (A       | \7-A0)                    | Symbol | Register Name                   |  |  |

|--------------|---------------------------|--------|---------------------------------|--|--|

| Read Address | ead Address Write Address |        |                                 |  |  |

| X000XXX1     | X000XXX0                  | GCSR   | General Command Status Register |  |  |

| X001XXX1     | X001XXX0                  | LCR    | Loopback Control Register       |  |  |

| X010XXX1     | X010XXX0                  | PIR    | Protocol Identifier Register    |  |  |

| X100XXX1     | X100XXX0                  | CFR0   | Configuration Register 0        |  |  |

| X101XXX1     | X101XXX0                  | CFR1   | Configuration Register 1        |  |  |

| X110XXX1     | X110XXX0                  | CFR2   | Configuration Register 2        |  |  |

| X111XXX1     | X111XXX0                  | CFR3   | Configuration Register 3        |  |  |

et4U.com

Example: The following sequence illustrates how a local microprocessor would obtain the current status of the 89151 by reading the indirectly addressable general command status register (GCSR).

- 1. Once the RDY pin is high or the RDY bit in the status register (SR) is 0, the local microprocessor writes 01H to the address register (ADR), which is the address of GCSR for a read operation. Refer to Table 4. The RDY pin goes low and the RDY bit in SR is set to 1.

- 2. Once the RDY pin is high or the RDY bit in SR is 0, the local microprocessor can read the contents of GCSR from the bus interface register (BIR). If the local microprocessor read 19H from BIR, this status message means that the 89151 received a good setup. Refer to Table 6.

# **Configuration Register 0 (CFR0)**

| 7   | 6   | 5    | 4    | 3    | 2    | 1    | 0   |  |

|-----|-----|------|------|------|------|------|-----|--|

| NIS | NIT | ADPT | PDTE | B1B2 | ICLK | SYNC | RSE |  |

(default = 00001100)

This configuration register controls some of the various operating parameters of the 89151.

NIS — Network interface select. This bit selects which serial network interface the 89151 will support. When NIS=1, the 89151 is configured for SLD operation. When NIS=0, the 89151 is configured for IDL operation.

NIT — Network interface three-state. When NIT=1, the SLD/SOUT pin is three-stated. When NIT=0, the SLD/SOUT pin is enabled for normal operation. The 89151 constantly monitors the NIT bit, and as soon as this bit is set to 1 the SLD/SOUT pin is three-stated. If the SLD/SOUT pin has been three-stated by setting the NIT bit to 1, the SLD/SOUT pin can be enabled by setting the NIT bit to 0 and instructing the 89151 to enter the setup state.

#### NOTE:

The SLD/SOUT pin is three-stated after the 89151 enters the self test state. If CFR0 is read by the local microprocessor after completion of the self test, the NIT bit will be set to 1. If the local microprocessor does not write to the configuration registers (CFR0-CFR3) or the loopback control register (LCR) before instructing the 89151 to enter the setup state, the 89151 will use the default operating parameters which were initialized during the self test state. In this case, the NIT bit will be set to 0 and the SLD/SOUT pin enabled once the setup state has been entered.

ADPT - Adaptive. When ADPT = 1, the 89151 is adaptive. This means that the 89151 will use the operating parameters received from the far-end TE during the T-Link parameter exchange instead of those received from the local microprocessor. The operating parameters that the 89151 has adapted to can be determined by reading the appropriate configuration registers. These registers will reflect the operating parameters currently in use by the 89151 rather than those that were originally sent by the local microprocessor. When ADPT=0, the 89151 is fixed. This means that the 89151 will not adapt to the operating parameters received from the far-end TE during the T-Link parameter exchange, and only the operating parameters received from the local microprocessor will be used.

PDTE — Parallel DTE data. When PDTE=1, the 89151 is configured for parallel DTE data. In the parallel mode of operation the flow of data is between the serial network interface and the DTE data register (DTED). When PDTE=0, the 89151 is configured for serial DTE data. In the serial mode of operation the flow of data is between the serial network interface and serial terminal interface.

# NOTE:

When the 89151 is configured for parallel DTE data, the TXD pin is internally connected to the RXD pin, as shown by loopback A in Figure 10, once the data mode state has been entered. This ensures that any data received on the serial terminal interface is looped back and does not interfere with the parallel mode of operation.

B1B2 — B1/B2 channel select. This bit selects which B channel of the serial network interface will be used by the 89151. When B1B2=1, the 89151 will use the B1 channel. When B1B2=0, the 89151 will use the B2 channel.

ICLK — Internal clock. This bit determines the source of the clock that provides the timing for the synchronous serial data exchange between the DTE and the 89151. When ICLK=1, internal clock, the 89151 provides the clock on the TRCLK pin. When ICLK=0, external clock, the 89151 uses the clock that is input on the TRCLK pin.

DataShe

#### NOTE:

When the 89151 is configured for asynchronous DTE data (SYNC=0), the internal clock is used for a baud rate reference, and the TRCLK pin is clamped high. For asynchronous DTE data the ICLK bit returns a 0 when CFR0 is read.

#### NOTE:

When the 89151 is configured for synchronous parallel DTE data (SYNC=1 and PDTE=1), the internal clock is always used.

# NOTE:

Only one end of a T-Link connection can use an external clock source. If both ends are configured for an external clock source, the T-Link parameter exchange will not be successfully completed.

#### NOTE:

If the 89151 is going to use the serial terminal interface clock that is input on the XTRCLK pin for 48, 56, or 64 Kbit/s synchronous serial DTE data (SYNC=1 and PDTE=0), this clock must be phase locked to the network clock to avoid clock slippage. Therefore, it is recommended to have the 89151 provide the serial terminal interface clock on the TRCLK pin for 48, 56, or 64 Kbit/s synchronous serial DTE data.

SYNC — Synchronous data. This bit configures the 89151 for either synchronous or asynchronous DTE data. When SYNC=1, synchronous operation is selected. When SYNC=0, asynchronous operation is selected.