# μPD78238 Family (μPD78233/234/237/238/P238) 8-Bit, K-Series Microcontrollers With A/D and D/A Converters, Real-Time Output Ports

June 1993

#### Description

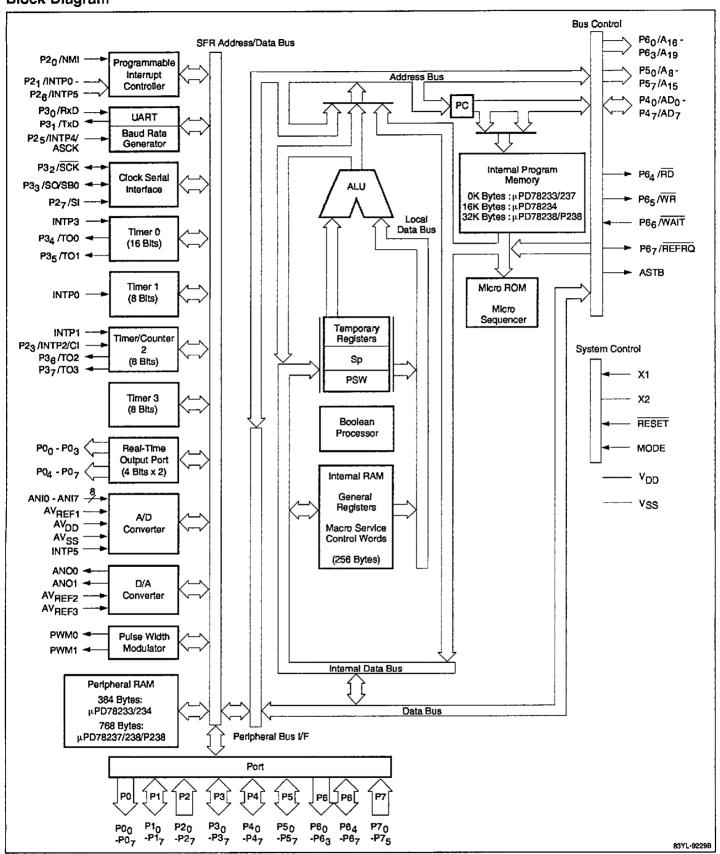

The  $\mu$ PD78233,  $\mu$ PD78234,  $\mu$ PD78237,  $\mu$ PD78238, and  $\mu$ PD78P238 are members of the K-Series® of microcontrollers and are designed for real-time embedded control applications. These 8-bit, single-chip microcontrollers have a minimum instruction time of 333 ns at 12 MHz (500 ns for the  $\mu$ PD78233/237). They feature 8-bit hardware multiply and divide instructions, four banks of main registers, an advanced interrupt handling facility, a powerful set of memory mapped on-chip peripherals, and the ability to address up to 1M bytes of external data memory. On board memory includes 640 or 1024 bytes of RAM, 16K or 32K bytes of mask ROM, or 32K bytes of UV EPROM or one-time programmable (OTP) ROM.

The advanced interrupt handling facility provides two levels of programmable hardware priority control and two separate methods of servicing interrupt requests: vectored and macro service. The macro service facility reduces the overhead involved in servicing peripheral interrupts by transferring data between the memory-mapped special function registers (SFRs) and memory without the use of time consuming interrupt service routines. In addition, the macro service facility can be initialized to automatically alter timer compare register values or to repeatedly output a prespecified pattern at a fixed or variable rate. By using macro service to control the real-time output ports, the  $\mu$ PD78238 family can easily and accurately drive two independent stepper motors.

The combination of the macro service facility, four banks of main registers, extended data memory address space, and powerful on-chip peripherals makes these devices ideal for applications in office automation, communication, HVAC, and industrial control.

# **Features**

- Complete single-chip microcontroller

- 8-bit ALU

- Program memory (ROM)

μPD78233/237: ROMless

μPD78234: 16K bytes

μPD78238/P238: 32K bytes

- Data memory (RAM)

μPD78233/234: 640 bytes

μPD78237/238/P238: 1024 bytes

K-series is a registered trademark of NEC Electronics, Inc

- Powerful instruction set

- 8-bit unsigned multiply and divide

- 16-bit arithmetic instructions

- 1-bit and 8-bit logic instructions

- Minimum instruction time

- 333 ns at 12 MHz (µPD78234/238/P238)

- -500 ns at 12 MHz ( $\mu$ PD78233/237)

- Memory expansion

- 8085 bus-compatible

- 64K program address space

- 1M data address space

- □ Large I/O capacity

- Up to 64 I/O port lines on μPD78234/238/P238

- Up to 46 I/O port lines on  $\mu$ PD78233/237

- --- Software programmable pullup resistors

- Memory-mapped on-chip peripherals (special function registers)

- □ Timer/counter unit

- -- 16-bit timer 0:

Two 16-bit compare registers

One 16-bit capture register

One external interrupt/capture line

-- 8-bit timer 1:

One 8-bit compare register

One 8-bit capture/compare register

One external interrupt/capture line

- 8-bit timer/counter 2:

Two 8-bit compare registers

One 8-bit capture register

One external interrupt/capture line

One external event counter line

--- 8-bit timer 3:

One 8-bit compare register

- □ Pulse-width modulated (PWM) outputs

- Two 12-bit precision hardware controlled

- Four 8-bit precision timer controlled

- □ Two 4-bit (or one 8-bit) real-time output ports

- Eight-channel 8-bit A/D converter

- □ Two-channel 8-bit D/A converter

- Programmable priority interrupt controller (two levels)

- ☐ Two methods of interrupt service

- Vectored interrupts

- Macro service mode with choice of three different types

# Features (cont)

- □ Two-channel serial communication interface

- Asynchronous serial interface (UART)

Dedicated baud rate generator

- Clock-synchronized interface

Full-duplex, three-wire mode

NEC serial bus interface (SBI) mode

- □ Refresh output for pseudostatic RAM

- □ STOP and HALT standby functions

- □ 5-volt CMOS technology

# **Ordering Information**

| Part Number    | ROM          | Package                        | Package Drawing |

|----------------|--------------|--------------------------------|-----------------|

| μPD78233GC     | ROMless      | 80-pin plastic QFP             | \$80GC-65-3B9-1 |

| μPD78234GC-xxx | 16K mask ROM | -                              |                 |

| μPD78237GC     | ROMless      | -                              |                 |

| μPD78238GC-xxx | 32K mask ROM | -                              |                 |

| μPD78P238GC    | 32K OTP ROM  | -                              |                 |

| μPD78233GJ     | ROMless      | 94-pin plastic QFP             | S94GJ-80-5BG-1  |

| μPD78234GJ-xxx | 16K mask ROM | -                              |                 |

| μPD78237GJ     | ROMless      | -                              |                 |

| μPD78238GJ-xxx | 32K mask ROM | -                              |                 |

| μPD78P238GJ    | 32K OTP ROM  | -                              |                 |

| μPD78233LQ     | ROMless      | 84-pin PLCC                    | P84L-50A3-1     |

| μPD78234LQ-xxx | 16K mask ROM | -                              |                 |

| μPD78237LQ     | ROMless      | -                              |                 |

| μPD78238LQ-xxx | 32K mask ROM | -                              |                 |

| μPD78P238LQ    | 32K OTP ROM  | -                              |                 |

| μPD78P238KF    | 32K UV EPROM | 94-pin ceramic LCC with window | X94KW-80A       |

Note: xxx indicates ROM code suffix.

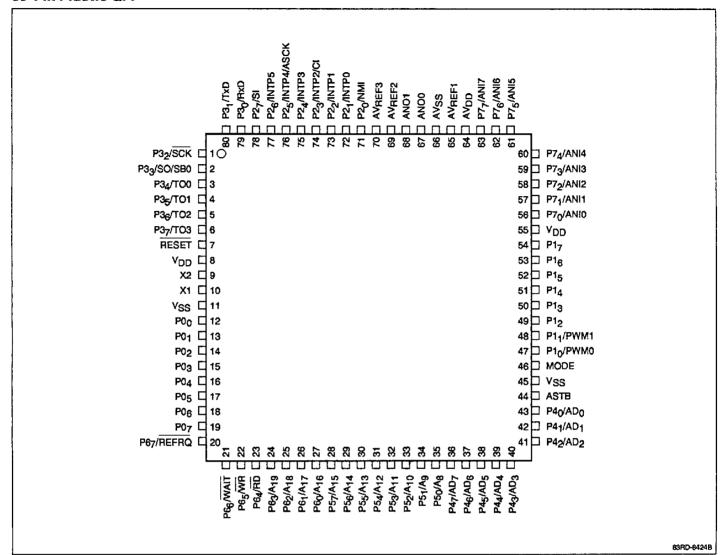

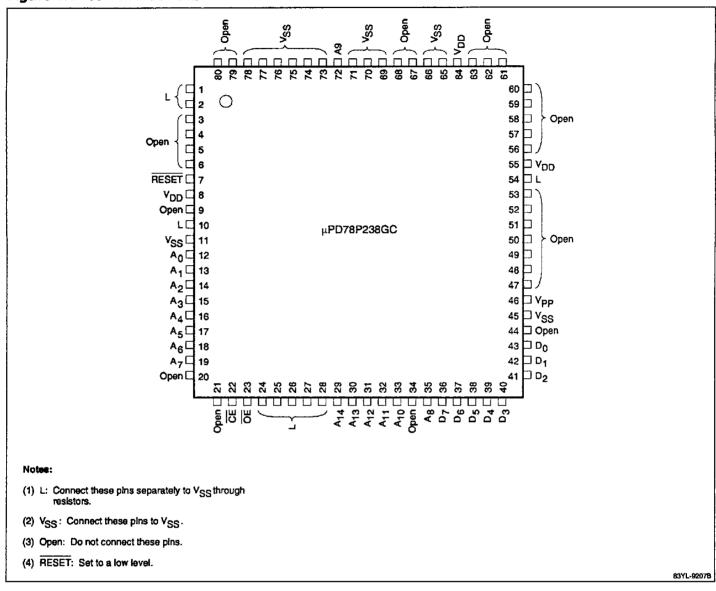

# Pin Configurations

### 80-Pin Plastic QFP

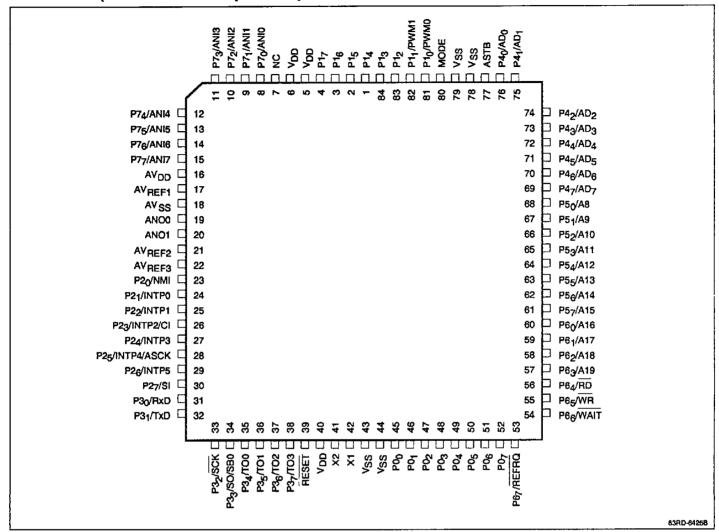

# Pin Configurations (cont)

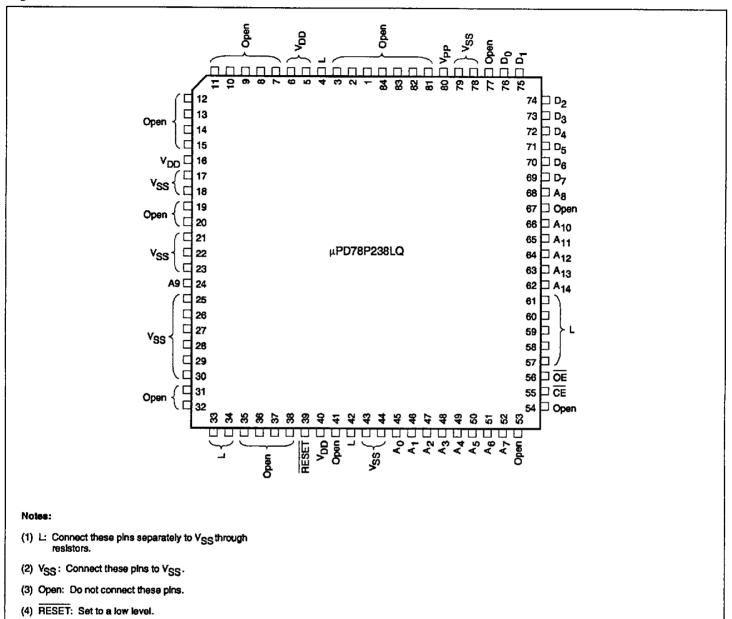

#### 84-Pin PLCC (Plastic Leaded Chip Carrier)

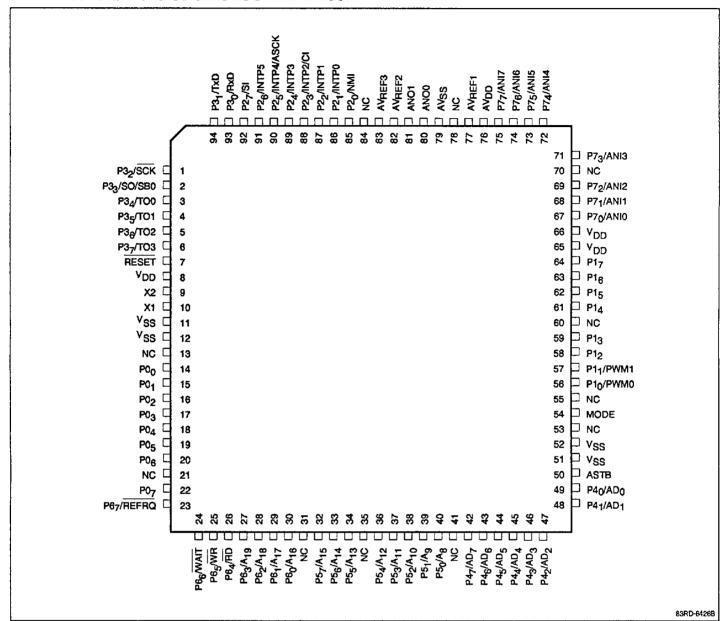

# Pin Configurations (cont)

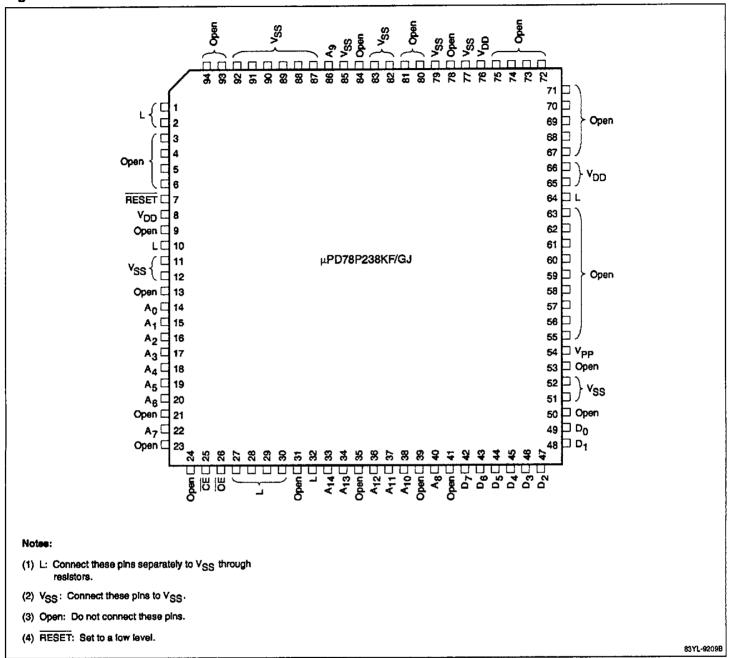

#### 94-Pin Plastic QFP and Ceramic LCC with Window

Pin Functions; Normal Operating Mode

| Symbol                             | First Function                                                                                                                                                                                                                                                                                                              | Symbol                            | Second Function                                                                              |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------|

| P0 <sub>0</sub> - P0 <sub>7</sub>  | Port 0; 8-bit tristate output port/real time output port                                                                                                                                                                                                                                                                    |                                   |                                                                                              |

| P1 <sub>0</sub><br>P1 <sub>1</sub> | Port 1; 8-bit, bit-selectable tristate input/output port                                                                                                                                                                                                                                                                    | PWM0<br>PWM1                      | Pulse-width modulated outputs                                                                |

| P1 <sub>2</sub> - P1 <sub>7</sub>  | -                                                                                                                                                                                                                                                                                                                           | _                                 |                                                                                              |

| P2 <sub>0</sub>                    | Port 2; 8-bit input port                                                                                                                                                                                                                                                                                                    | NMI                               | External nonmaskable interrupt                                                               |

| P2 <sub>1</sub> P2 <sub>2</sub>    | -                                                                                                                                                                                                                                                                                                                           | INTP0<br>INTP1                    | Maskable external interrupts                                                                 |

| P2 <sub>3</sub>                    | -                                                                                                                                                                                                                                                                                                                           | INTP2<br>CI                       | Maskable external interrupt External clock input to timer/counter 2                          |

| P2 <sub>4</sub>                    | -                                                                                                                                                                                                                                                                                                                           | INTP3                             | Maskable external interrupt                                                                  |

| P2 <sub>5</sub>                    | -                                                                                                                                                                                                                                                                                                                           | INTP4<br>ASCK                     | Maskable external interrupt Asynchronous serial clock input                                  |

| P2 <sub>6</sub>                    | -                                                                                                                                                                                                                                                                                                                           | INTP5                             | Maskable external interrupt                                                                  |

| P2 <sub>7</sub>                    | -                                                                                                                                                                                                                                                                                                                           | SI                                | Serial data input for three-wire serial I/O mode                                             |

| P3 <sub>0</sub>                    | Port 3; 8-bit, bit-selectable tristate input/output port                                                                                                                                                                                                                                                                    | RxD                               | Asynchronous serial receive data input                                                       |

| P3 <sub>1</sub>                    | -                                                                                                                                                                                                                                                                                                                           | TxD                               | Asynchronous serial transmit data input                                                      |

| P3 <sub>2</sub>                    | -                                                                                                                                                                                                                                                                                                                           | SCK                               | Serial shift clock input/output                                                              |

| P3 <sub>3</sub>                    | -                                                                                                                                                                                                                                                                                                                           | SO<br>SBO                         | Serial data output for three-wire serial I/O mode I/O bus for NEC serial bus interface (SBI) |

| P3 <sub>4</sub> - P3 <sub>7</sub>  | -                                                                                                                                                                                                                                                                                                                           | TO0 - TO3                         | Timers T0 to T3 outputs                                                                      |

| P40 - P47                          | Port 4; 8-bit tristate input/output port                                                                                                                                                                                                                                                                                    | AD <sub>0</sub> - AD <sub>7</sub> | Low-order 8-bit multiplexed address/data bus                                                 |

| P5 <sub>0</sub> - P5 <sub>7</sub>  | Port 5; 8-bit, bit-selectable tristate input/output port                                                                                                                                                                                                                                                                    | A <sub>8</sub> - A <sub>15</sub>  | High-order 8-bit address bus                                                                 |

| P6 <sub>0</sub> - P6 <sub>3</sub>  | Port 6; 4-bit output port                                                                                                                                                                                                                                                                                                   | A <sub>16</sub> - A <sub>19</sub> | Extended memory address bus                                                                  |

| P6 <sub>4</sub>                    | Port 6; 4-bit, bit-selectable tristate input/output port                                                                                                                                                                                                                                                                    | RD                                | External memory read strobe                                                                  |

| P6 <sub>5</sub>                    | •                                                                                                                                                                                                                                                                                                                           | WR                                | External memory write strobe                                                                 |

| P6 <sub>6</sub>                    | -                                                                                                                                                                                                                                                                                                                           | WAIT                              | External memory wait signal input                                                            |

| P6 <sub>7</sub>                    |                                                                                                                                                                                                                                                                                                                             | REFAQ                             | Refresh pulse output used by external pseudostatic memory                                    |

| P7 <sub>0</sub> - P7 <sub>7</sub>  | Port 7; 8-bit input port                                                                                                                                                                                                                                                                                                    | ANIO - ANI7                       | Analog voltage input to A/D converter                                                        |

| ANO0, ANO1                         | Analog voltage output from D/A converter                                                                                                                                                                                                                                                                                    |                                   |                                                                                              |

| ASTB                               | Address strobe output used to latch the low-order 8 address for external memory                                                                                                                                                                                                                                             | -                                 |                                                                                              |

| RESET                              | External system reset input                                                                                                                                                                                                                                                                                                 | <b>-</b>                          |                                                                                              |

| MODE                               | Internal ROM or external memory control signal input. A low-level input selects internal ROM. A high-level input selects external memory. The $\mu$ PD78234/238 can be used in ROMless mode by setting the MODE pin high. However, the $\mu$ PD78P238 cannot be used in ROMless mode and its MODE pin must only be set low. | -                                 |                                                                                              |

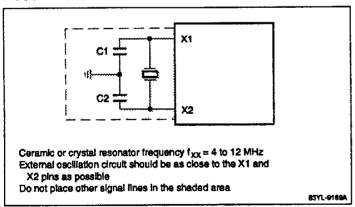

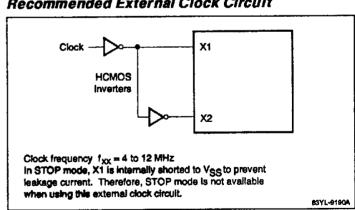

| X1                                 | Crystal/ceramic resonator connection or external clock input                                                                                                                                                                                                                                                                |                                   |                                                                                              |

| X2                                 | Crystal/ceramic resonator connection or inverse of external clock                                                                                                                                                                                                                                                           | -                                 |                                                                                              |

| AV <sub>REF1</sub>                 | A/D converter reference voltage                                                                                                                                                                                                                                                                                             | -                                 |                                                                                              |

# Pin Functions; Normal Operating Mode (cont)

| Symbol                                     | First Function                   | Symbol | Second Function |  |

|--------------------------------------------|----------------------------------|--------|-----------------|--|

| AV <sub>REF2</sub> ,<br>AV <sub>REF3</sub> | D/A converter reference voltages |        |                 |  |

| AV <sub>DD</sub>                           | A/D converter power supply       |        |                 |  |

| AVSS                                       | A/D converter ground             |        |                 |  |

| V <sub>DD</sub>                            | +5 volt power supply input       |        |                 |  |

| V <sub>SS</sub>                            | Power supply ground              | _      |                 |  |

| NC                                         | No connection                    |        |                 |  |

#### **FUNCTIONAL DESCRIPTION**

### Central Processing Unit (CPU)

The  $\mu$ PD78238 family CPU features 8- and 16-bit arithmetic including an 8 x 8-bit unsigned multiply and 16 x 8-bit unsigned divide (producing a 16-bit quotient and an 8-bit remainder). The multiply executes in 3.67  $\mu$ s and the divide in 12.36  $\mu$ s at 12 MHz (4.00 and 12.69  $\mu$ s respectively for  $\mu$ PD78233/237).

A CALLT vector table and a CALLF program area decrease the number of bytes in the call instructions for commonly used subroutines. A 1-byte call instruction (CALLT) can access up to 32 subroutines through the addresses contained in the CALLT vector table. A 2-byte call instruction (CALLF) can access any routine beginning at a specific address in the CALLF area.

The internal system clock ( $f_{CLK}$ ) is generated by dividing the oscillator frequency by two. Therefore, at the maximum oscillator frequency of 12 MHz, the internal system clock is 6 MHz. The minimum instruction execution time for an instruction fetched from internal ROM is 333 ns (500 ns when fetched from external memory).

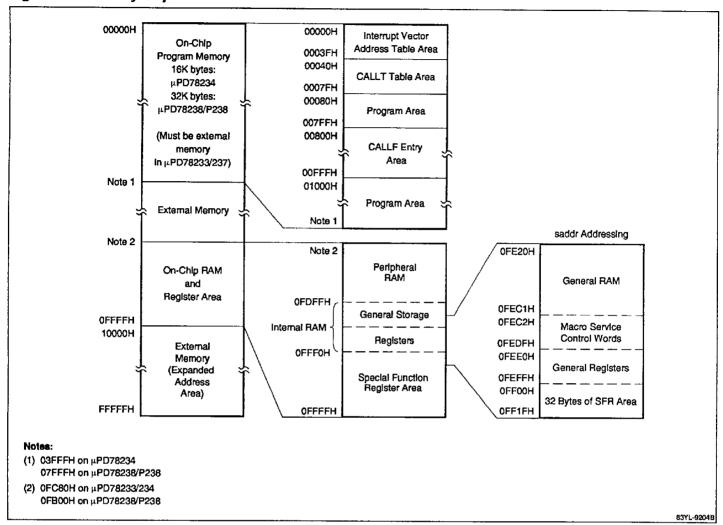

### **Memory Space**

The  $\mu$ PD78238 family has a 1M byte address space (see figure 1). The first 64K bytes of this address space (00000H-0FFFFH) can be used as both program and data memory. The remaining 960K bytes of this address space (10000H-FFFFFH) can only be used as data memory and is known as expanded memory.

# **Block Diagram**

Figure 1. Memory Map

#### **External Memory**

The  $\mu$ PD78238 family has an 8-bit wide external data bus and a 16-bit wide external address bus (20-bit wide if expanded memory is enabled). The low-order 8 bits of the address bus are multiplexed to provide the 8-bit data bus and are supplied by I/O port 4. The high-order address bits of the 16-bit address bus are taken from port 5. If expanded memory is enabled, the expanded address nibble is provided by P60 to P63. Address latch, read, and write strobes are also provided.

The memory expansion mode register (MM) is used to enable external memory, to specify up to two additional wait states or the use of the WAIT input pin for the first 64K bytes of memory, and to enable the high-speed internal ROM fetch. Ports 4, 5, and 6 are available as general purpose I/O ports when only internal ROM is used and no external program or data space is required.

## **Expanded Data Memory**

The MM register is also used to enable the external expanded data memory space, addresses 10000H to FFFFH. When the expanded data memory is enabled, the entire 1M byte address space is divided into 16 banks of 64K bytes each. The low-order 4-bits of the P6 or the PM6 registers are used as bank selection registers to supply the address information to A<sub>16</sub> to A<sub>19</sub>. Data can easily be transferred from one memory bank to another by using the appropriate instructions. Address lines A<sub>16</sub> to A<sub>19</sub> are only active when an instruction that uses expanded addressing is being executed. A programmable wait control register (PW) allows the programmer to specify up to two additional wait states or the use of the WAIT input pin for expanded data memory space.

### **On-Chip RAM**

The  $\mu$ PD78237/238 have a total of 1024 bytes of on-chip RAM (640 bytes in the  $\mu$ PD78233/234).

The  $\mu$ PD78P238 also contains 1024 bytes of on-chip RAM. By using the memory size select (IMS) register, the  $\mu$ PD78P238 can be programmed to emulate either a  $\mu$ PD78234 device with 640 bytes of on-chip RAM or a  $\mu$ PD78238 with 1024 bytes. The programming of this register is transparent to the ROM-based device, allowing easy transfer of code to a ROM-based device.

The upper 256-byte area (FE00H-FEFFH) features high-speed access and is known as "Internal RAM." The remainder (FB00H-FDFFH and FC80H-FDFFH in the  $\mu$ PD78233/234) is accessed at the same speed as external memory and is known as "Peripheral RAM." The general register banks and the macro service control words are stored in Internal RAM. The remainder of Internal RAM and any unused register bank locations are available for general storage.

## **On-Chip Program Memory**

The  $\mu$ PD78234/238 contain 16K and 32K bytes of internal ROM respectively. The  $\mu$ PD78P238 contains 32K bytes of UV EPROM or one-time programmable ROM. By using the IMS register, the  $\mu$ PD78P238 can be programmed to emulate a  $\mu$ PD78234 device with 16K bytes of internal PROM or a  $\mu$ PD78238 with 32K bytes. This programming is transparent to the ROM-based device, allowing easy transfer of code to a ROM-based device. Instructions from on-chip program memory can be fetched at high speed or at the same rate as from external memory. The  $\mu$ PD78233 and the  $\mu$ PD78237 do not have on-chip program memory.

## **CPU Control Registers**

**Program Counter.** The program counter is a 16-bit binary counter register that holds the address of the next instruction to be executed. During reset, the program counter is loaded with the address stored in locations 0000H and 0001H.

**Stack Pointer.** The stack pointer is a 16-bit register that holds the address of the last item pushed onto the stack. It is decremented before new data is pushed onto the stack and incremented after data is popped off the stack.

**Program Status Word.** The program status word (PSW) is an 8-bit register that contains flags that are set or reset depending on the results of an instruction.

This register can be written to or read from 8 bits at a time. The individual flags can also be manipulated on a bit-by-bit basis. The assignment of PSW bits follows.

| 7                                     |      |                         |                        | _                                               |         |      | 0  |

|---------------------------------------|------|-------------------------|------------------------|-------------------------------------------------|---------|------|----|

| ΙE                                    | Z    | RBS1                    | AC                     | RBS0                                            | 0       | ISP  | CY |

| CY<br>ISP<br>RBS0, I<br>AC<br>Z<br>IE | RBS1 | Regis<br>Auxili<br>Zero | upt proter basing care | riority st<br>ank seled<br>arry flag<br>quest e | ction 1 | lags |    |

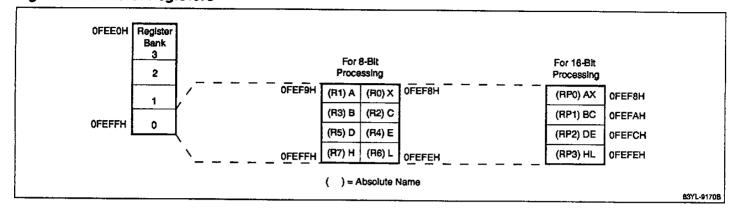

#### **General Registers**

The general-purpose registers (figure 2) consist of four banks of registers located at addresses FEE0H to FEFFH in Internal RAM. Each bank consists of eight 8-bit general registers that can also be used in pairs to function as four 16-bit registers. Two bits in the PSW (RBS0 and RBS1) specify which of the register banks is active. The bits are set under program control. Registers have both functional names (like A, X, B, C for 8-bit registers and AX, BC for 16-bit registers) and absolute names (like R1, R0, R3, R2 for 8-bit registers and RP0, RP1 for 16-bit registers). Each instruction determines whether a register is referred to by its functional or absolute name and whether it is 8 or 16 bits.

#### Addressing

The µPD78238 family features 1-byte addressing of both the special function registers and the portion of on-chip RAM from FE20H to FEFFH. The 1-byte sfr addressing accesses the entire SFR area, while the 1-byte saddr addressing accesses the first 32 bytes of the SFR area and 224 bytes of internal RAM. Sixteen-bit SFRs and words of memory in these areas can be addressed by 1-byte saddrp addressing, which is valid for even addresses only. Since many instructions use 1-byte addressing, access to these locations is almost as fast and versatile as access to the general registers. There are seven addressing modes for data in main memory: direct, register, register indirect with autoincrement and decrement, saddr, SFR, based, and indexed. There are also both 8-bit and 16-bit immediate operands.

Figure 2. General Registers

# **Special Function Registers**

The input/output ports, timers, capture and compare registers, and mode and control registers for both the peripherals and the CPU are collectively known as special function registers. They are all memory-mapped between FF00H and FFFFH and can be ac-

cessed either by main memory addressing or by 1-byte sfr addressing. They are either 8 or 16 bits as required, and many of the 8-bit registers are capable of single-bit access as well. Locations FFD0H through FFDFH are known as the external SFR area. Registers in external circuitry interfaced and mapped to these addresses can be addressed with SFR addressing. Table 1 is a list of the special function registers.

Table 1. Special Function Registers

| table 1. Spec | cial Function Registers                        |        |     | Access Units (Bits) | (Bits) |              |                   |

|---------------|------------------------------------------------|--------|-----|---------------------|--------|--------------|-------------------|

| Address       | Register (SFR)                                 | Symbol | R/W | 1                   | 8      | 16           | State After Reset |

| OFF00H        | Port 0                                         | P0     | R/W | х                   | х      | _            | Undefined         |

| OFF01H        | Port 1                                         | P1     | R/W | х                   | х      | _            | Undefined         |

| 0FF02H        | Port 2                                         | P2     | R   | х                   | х      |              | Undefined         |

| OFF03H        | Port 3                                         | P3     | R/W | х                   | ×      | _            | Undefined         |

| OFF04H        | Port 4                                         | P4     | R/W | x                   | ×      |              | Undefined         |

| OFF05H        | Port 5                                         | P5     | R/W | x                   | ×      |              | Undefined         |

| OFF06H        | Port 6                                         | P6     | R/W | x                   | ×      | _            | хон               |

| 0FF07H        | Port 7                                         | P7     | R   | х                   | ×      | _            | Undefined         |

| OF FOAH       | Port 0 buffer register (low)                   | POL    | R/W | х                   | ×      | _            | Undefined         |

| OFFOBH        | Port 0 buffer register (high)                  | POH    | R/W | x                   | ×      | _            | Undefined         |

| 0FF0CH        | Real-time output port control register         | RTPC   | R/W | х                   | ×      | <del>-</del> | 00Н               |

| OFF10H-0FF11H | 16-bit compare register 0 (16-bit timer 0)     | CR00   | R/W | _                   |        | x            | Undefined         |

| OFF12H-0FF13H | 16-bit compare register (16-bit timer 0)       | CR01   | R/W | _                   | _      | х            | Undefined         |

| OFF14H        | 8-bit compare register (8-bit timer 1)         | CR10   | R/W | _                   | х      | _            | Undefined         |

| OFF15H        | 8-bit compare register (8-bit timer/counter 2) | CR20   | R/W |                     | х      | _            | Undefined         |

| OFF16H        | 8-bit compare register (8-bit timer/counter 2) | CR21   | R/W | _                   | х      | _            | Undefined         |

| OFF17H        | 8-bit compare register (8-bit timer 3)         | CR30   | R/W |                     | х      |              | Undefined         |

| 0FF18H-0FF19H | 16-bit capture register (16-bit timer 0)       | CR02   | R   | _                   | _      | х            | Undefined         |

| 0FF1AH        | 8-bit capture register (8-bit timer/counter 2) | CR22   | R   |                     | Х      |              | Undefined         |

| 0FF1CH        | 8-bit capture/compare register (8-bit timer 1) | CR11   | R/W | _                   | ×      | _            | Undefined         |

| OFF20H        | Port 0 mode register                           | РМ0    | W   | _                   | х      |              | FFH               |

| 0FF21H        | Port 1 mode register                           | PM1    | w   | _                   | Х      | -            | FFH               |

| 0FF23H        | Port 3 mode register                           | РМЗ    | W   | _                   | x      |              | FFH               |

| 0FF25H        | Port 5 mode register                           | PM5    | W   | _                   | ×      |              | FFH               |

| 0FF26H        | Port 6 mode register                           | PM6    | R/W | х                   | ×      | _            | FxH               |

| off30H        | Capture/compare control register 0             | CRC0   | W   | _                   | x      |              | 10H               |

| 0FF31H        | Timer output control register                  | тос    | W   |                     | ×      |              | 00H               |

| 0FF32H        | Capture/compare control register 1             | CRC1   | w   | _                   | ×      |              | 00H               |

| OFF34H        | Capture/compare control register 2             | CRC2   | W   |                     | ×      |              | 00H               |

| OFF40H        | Pullup resistor option register                | PUO    | R/W | x                   | x      |              | 00H               |

| 0FF43H        | Port 3 mode control register                   | РМСЗ   | R/W | x                   | ×      |              | 00H               |

| off50H-0ff51H | 16-bit timer register 0                        | TMO    | R   |                     |        | х            | 0000H             |

| 0FF52H        | 8-bit timer register 1                         | TM1    | R   |                     | ×      |              | 00H               |

| 0FF54H        | 8-bit timer register 2                         | TM2    | R   |                     | Х      | _            | 00H               |

| 0FF56H        | 8-bit timer register 3                         | тмз    | R   |                     | ×      | _            | 00H               |

| 0FF5CH        | Prescaler mode register 0                      | PRMO   | w   |                     | x      | _            | 00H               |

| 0FF5DH        | Timer control register 0                       | TMC0   | R/W |                     | x      |              | 00H               |

| OFF5EH        | Prescaler mode register 1                      | PRM1   | w   |                     | x      |              | 00Н               |

| OFF5FH        | Timer control register 1                       | TMC1   | R/W |                     | ×      |              | 00H               |

| OFF60H        | D/A converter value setting register 0         | DACSO  | R/W |                     | x      | -            | 00H               |

|               |                                                |        |     |                     |        |              |                   |

Table 1. Special Function Registers (cont)

|               |                                                      |        |     | Acce | ess Units | (Bits)      |                                       |

|---------------|------------------------------------------------------|--------|-----|------|-----------|-------------|---------------------------------------|

| Address       | Register (SFR)                                       | Symbol | R/W | 1    | 8         | 16          | <ul> <li>State After Reset</li> </ul> |

| 0FF61H        | D/A converter value setting register 1               | DACS1  | R/W | _    | ×         |             | 00H                                   |

| 0FF68H        | A/D converter mode register                          | ADM    | R/W | х    | ×         | _           | 00H                                   |

| OFF6AH        | A/D conversion result register                       | ADCR   | R   | _    | х         | _           | Undefined                             |

| OFF70H        | PWM control register                                 | PWMC   | R/W | _    | ×         |             | 05H                                   |

| 0FF72H-0FF73H | PWM modulo register 0                                | PWM0   | W   | _    | _         | ×           | Undefined                             |

| 0FF74H-0FF75H | PWM modulo register 1                                | PWM1   | W   | _    | _         | ×           | Undefined                             |

| OFF7DH        | One-shot pulse output control register               | OSPC   | R/W | x    | ×         | _           | 00H                                   |

| OFF80H        | Clocked serial interface mode register               | CSIM   | R/W | ×    | ×         |             | 00H                                   |

| 0FF82H        | Serial bus interface control register                | SBIC   | R/W | ×    | ×         |             | 00H                                   |

| 0FF86H        | Serial shift register                                | SIO    | R/W |      | х         |             | Undefined                             |

| 0FF88H        | Asynchronous serial interface mode register          | ASIM   | R/W | х    | ×         |             | 80H                                   |

| OFF8AH        | Asynchronous serial interface status register        | ASIS   | R   | х    | x         | -           | 00Н                                   |

| OFF8CH        | Serial receive buffer UART                           | RxB    | R   |      | ×         | _           | Undefined                             |

| OFF8EH        | Serial transmit shift register: UART                 | TxS    | w   |      | ×         |             | Undefined                             |

| OFF90H        | Baud rate generator control register                 | BRGC   | W   |      | ×         | _           | 00H                                   |

| OFFC0H        | Standby control register                             | STBC   | R/W |      | ×         | _           | 0000x000B                             |

| 0FFC4H        | Memory expansion mode register                       | ММ     | R/W | ×    | ×         | _           | 20H                                   |

| 0FFC5H        | Programmable wait control register                   | PW     | R/W | ×    | ×         | _           | 80H                                   |

| 0FFC6H        | Refresh mode register                                | RFM    | R/W | х    | ×         | _           | 00H                                   |

| OFFCFH        | Memory size select register                          | IMS    | W   |      | ×         | _           | Undefined                             |

| OFFDOH-OFFDFH | External SFR area                                    | _      | R/W | х    | ×         |             | Undefined                             |

| OFFEOH        | Interrupt request flag register L                    | IFOL   | R/W | х    | x         | _           | 00Н                                   |

| OFFE1H        | Interrupt request flag register H                    | IFOH   | R/W | х    | ×         |             | 00Н                                   |

| OFFE0H-OFFE1H | Interrupt request flag register H                    | IFO    | R/W | _    | _         | x           | 0000Н                                 |

| OFFE4H        | Interrupt mask flag register L                       | MKOL   | R/W | x    | x         |             | FFH                                   |

| OFFE5H        | Interrupt mask flag register H                       | МКОН   | R/W | x    | ×         |             | FFH                                   |

| 0FFE4H-0FFE5H | Interrupt mask flag register H                       | МКОН   | R/W | _    | _         | х           | FFFH                                  |

| OFFE8H        | Priority specification flag register L               | PROL   | R/W | х    | ×         |             | FFH                                   |

| OFFE9H        | Priority specification flag register H               | PROH   | R/W | x    | ×         | <del></del> | FFH                                   |

| 0FFE8H-0FFE9H | Priority specification flag register H               | IF0    | R/W | _    |           | ×           | FFFH                                  |

| 0FFECH        | Interrupt service mode specification flag register L | ISMOL  | R/W | x    | ×         | _           | 00H                                   |

| OFFEDH        | Interrupt service mode specification flag register H | ISMOH  | R/W | х    | x         | _           | 00H                                   |

| OFFECH-OFFEDH | Interrupt service mode specification flag register   | ISM0   | R/W | _    | _         | х           | 00Н                                   |

| OFFF4H        | External interrupt mode register 0                   | INTMO  | R/W | ×    | х         |             | 00H                                   |

| OFFF5H        | External interrupt mode register 1                   | INTM1  | R/W | x    | х         | _           | 00Н                                   |

| OFFF8H        | interrupt status register                            | IST    | R/W | ×    | ×         |             | 00H                                   |

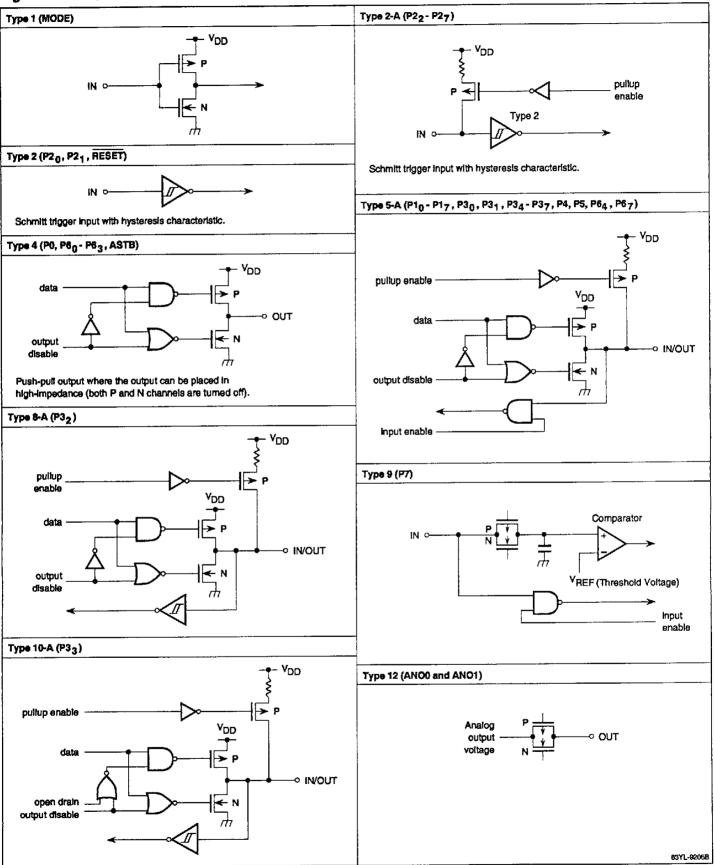

Figure 3. Pin I/O Circuits

### Input/Output Ports

There are up to 64 port lines on the  $\mu$ PD78234/238/P238 and up to 46 port lines on the  $\mu$ PD78233/37. (Ports 4, 5, and two bits of port 6 are not available on the  $\mu$ PD78233/237 since the  $\mu$ PD78233/237 must always

use external memory.) Table 2 lists the features of each port and figure 3 shows the structure of each port pin. The pin levels of all port 2, 3, and 7 pins can always be read or tested regardless of the dual pin function.

Table 2. Digital Port Functions

| Port   | Operational Features                                           | Configuration   | Direct Drive<br>Capability | Software Pullup<br>Resistor Connection            |

|--------|----------------------------------------------------------------|-----------------|----------------------------|---------------------------------------------------|

| Port 0 | 8-bit high impedance output                                    |                 | Transistor                 |                                                   |

| Port 1 | 8-bit input or output                                          | Bit selectable  | LED                        | Byte selectable, input bits only                  |

| Port 2 | 8-bit Schmitt trigger input                                    |                 |                            | In 6-bit unit (P2 <sub>2</sub> -P2 <sub>7</sub> ) |

| Port 3 | 8-bit input or output                                          | Bit selectable  |                            | Byte selectable, input bits only                  |

| Port 4 | 8-bit input or output                                          | Byte selectable | LED                        | Byte selectable                                   |

| Port 5 | 8-bit input or output                                          | Byte selectable | LED                        | Byte selectable, input bits only                  |

| Port 6 | 4-bit output (bits 0 to 3) 4-bit input or output (bits 4 to 7) | Bit selectable  |                            | In 4-bit unit, input bits only                    |

| Port 7 | 8-bit input                                                    |                 |                            |                                                   |

#### Note:

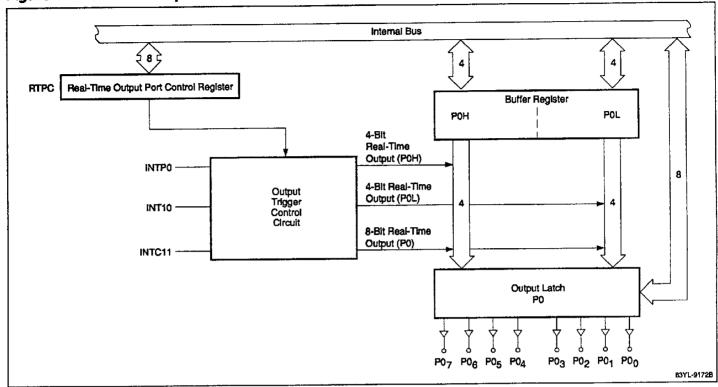

### Real-time Output Port

The real-time output port (RTPC) shares pins with port 0. It can be used as two independent 4-bit real-time output ports or one 8-bit real-time output port. In the real-time output mode, data stored beforehand in the buffer registers, P0H and P0L, is transferred immediately to the output latch of P0 on the occurrence of a timer 1 interrupt (INTC10 or INTC11) or external interrupt (INTP0) (see figure 4). By using the real-time output port with the macro service function, port 0 can be used to output preprogrammed patterns at preprogrammed variable time intervals. In this mode, two independent stepper motors can accurately be driven at a fixed or variable rate.

<sup>(1)</sup> Software pullup resistors can be internally connected only on a port-by-port bits to port bits set to input mode. Pullup resistors are not connected to port bits set to output mode.

Figure 4. Real-time Output Port

# Analog-to-Digital (A/D) Converter

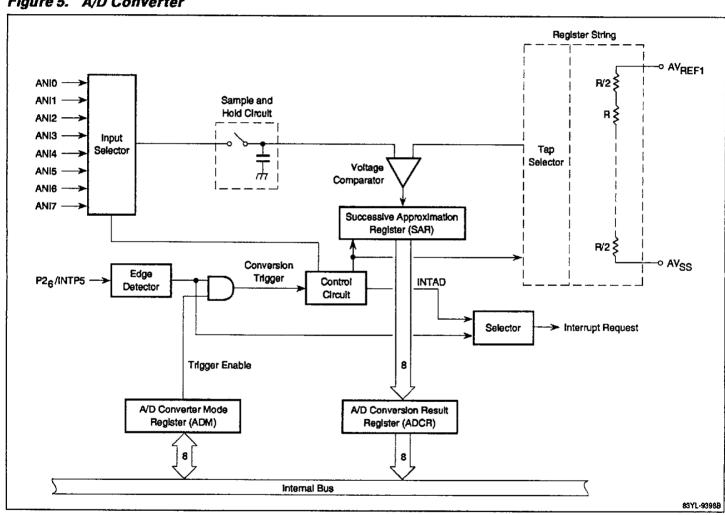

The µPD78238 family A/D converter (see figure 5) uses the successive-approximation method for converting up to eight multiplexed analog inputs into 8-bit digital data. The conversion time per input is 30 µs at 12 MHz operation. A/D conversion can be started by an external interrupt, INTP5, or under software control.

The A/D converter can operate in either scan mode or select mode. In scan mode, from one to eight sequential inputs can be programmed for conversion. The A/D converter selects each input in order, converts the

data, stores it in the A/D conversion result (ADCR) register, and generates an interrupt (INTAD). This converted data can be easily transferred to memory by using the macro service function.

In select mode, only one of the eight A/D inputs can be selected for conversion. The ADCR register is continually updated and can be read at any time. If the A/D converter is started by an external interrupt, an INTAD interrupt occurs at the completion of each conversion. If the A/D converter is started by software, no interrupts are generated.

Figure 5. A/D Converter

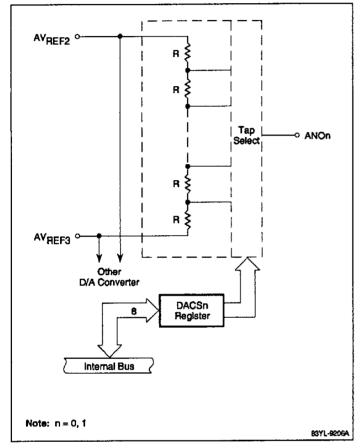

### Digital-to-Analog (D/A) Converter

The  $\mu$ PD78238 family has two D/A converters as shown in figure 6. The 8-bit digital data, written to the DACSn register (n=0, 1), selects one of the 256 taps on a resistor ladder between AV<sub>REF2</sub> and AV<sub>REF3</sub>. The selected voltage becomes the analog output at the ANOn pin. The ANOn is a high-impedance output and requires an external buffer to drive a low-impedance load.

Figure 6. D/A Converter

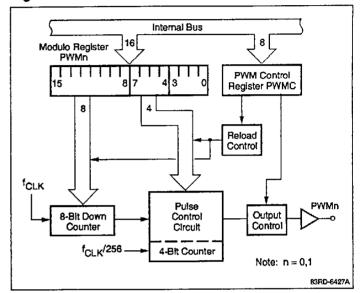

# Hardware Pulse-Width Modulated Outputs

The  $\mu$ PD78238 family has two 12-bit resolution pulsewidth modulated (PWM) outputs (see figure 7) with a repetition rate of 23.4 kHz at 12 MHz (f<sub>CLK</sub> = 6 MHz). The polarity of each output can be selected under program control. The two PWM outputs, PWM0 and PWM1, share pins with port 1, bits 0 and 1 respectively. These outputs are designed for controlling DC motors.

Figure 7. Hardware Pulse-Width Modulator

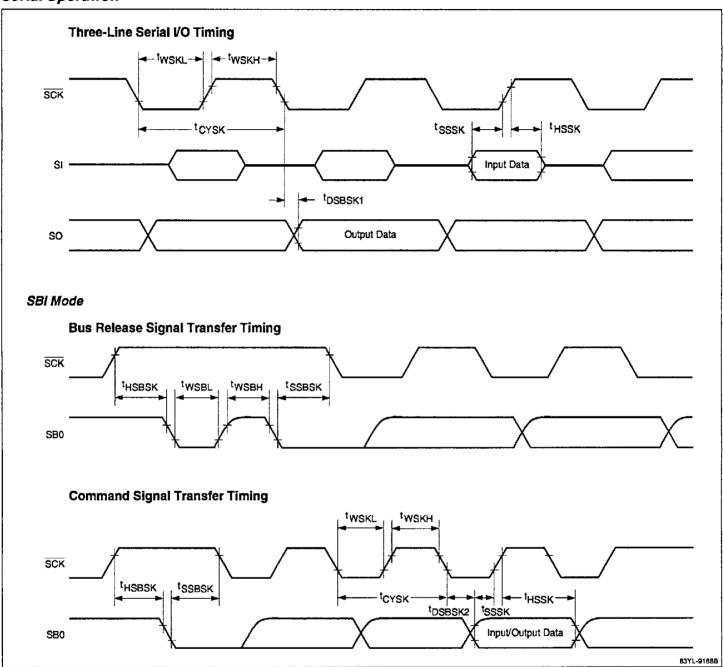

#### Serial Interface

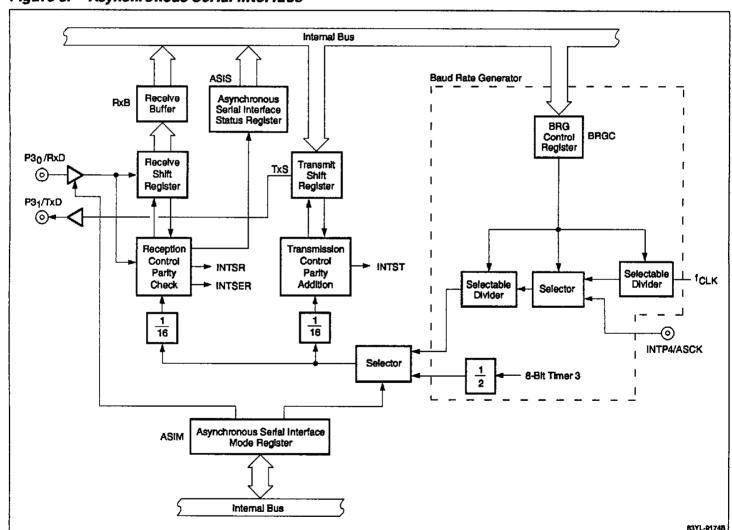

The µPD78238/P238 have two independent serial interfaces. The first is a standard UART. The UART (figure 8) permits full-duplex operation and can be programmed for 7- or 8-bits of data after the start bit, followed by one or two stop bits. Odd, even, zero or no parity can also be selected. The serial clock for the UART can be provided by an on-chip baud rate generator or timer 3. By using either the internal system clock or an external clock input into the ASCK pin, the baud rate generator is capable of generating all of the commonly used baud rates. The UART generates three interrupts: INTST (transmission complete), INTSR (reception complete), and INTSER (reception error).

Figure 8. Asynchronous Serial Interface

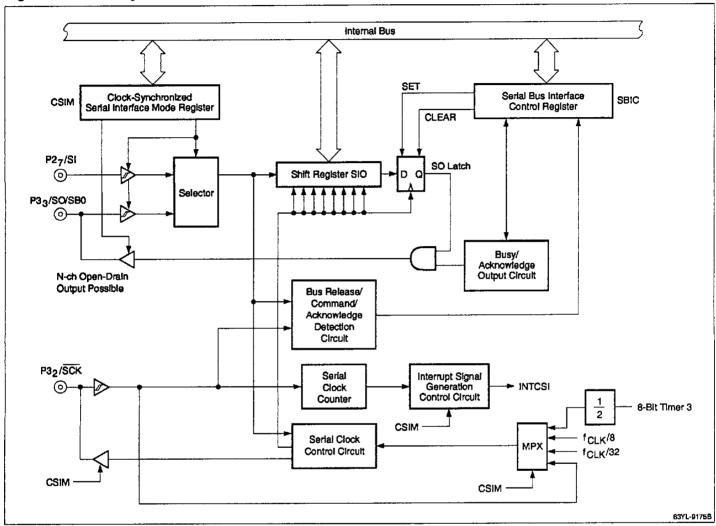

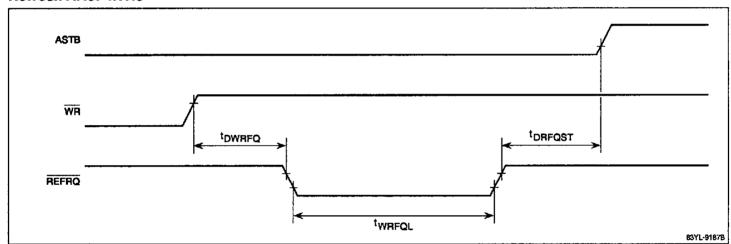

The second interface is an 8-bit clock-synchronized serial interface (figure 9). It can be operated in either a three-wire serial I/O mode or NEC serial bus interface (SBI) mode.

Figure 9. Clock-Synchronized Serial Interface

In the three-wire serial I/O mode, the 8-bit shift register (SIO) is loaded with a byte of data and eight clock pulses are generated. These eight pulses shift the byte of data out of the SO line (MSB first) and in from the SI line providing full-duplex operation. This interface can also be set to receive or to transmit data only. The INTCSI interrupt is generated after each 8-bit transfer. One of three internal clocks or an external clock clocks the data.

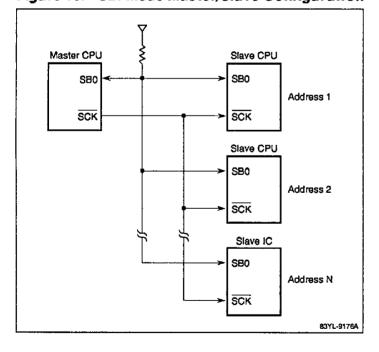

The NEC SBI mode is a two-wire high-speed proprietary serial interface available on most devices in the NEC  $\mu$ PD75xxx and  $\mu$ PD78xxx product lines. Devices are connected in a master/slave configuration (see figure 10). There is only one master device at a time; all others are slaves. The master sends addresses, commands, and data over the serial bus line (SB0) using a fixed hardware protocol synchronized with the SCK line. Each slave  $\mu$ PD78238 family device can be programmed in software to respond to any one of 256 addresses. There are also 256 commands and 256 data types. Since all commands are user definable, any software protocol, simple or complex, can be defined. It is even possible to develop commands to change a slave into a master and the previous master into a slave.

Figure 10. SBI Mode Master/Slave Configuration

#### **Timers**

The  $\mu$ PD78238 family has one 16-bit timer and three 8-bit timers. The 16-bit timer counts the internal system clock (f<sub>CLK</sub>/8) while the three 8-bit timers can be programmed to count a number of prescaled values of the internal system clock. One of the 8-bit timers can also count external events.

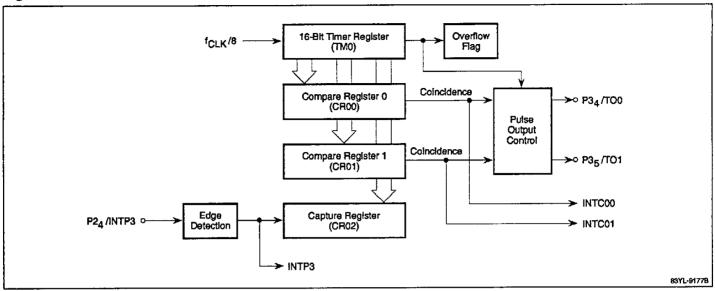

Timer 0 consists of a 16-bit timer (TM0), two 16-bit compare registers (CR00 and CR01), and a 16-bit capture register (CR02). Timer 0 can be used as two interval timers, to output a programmable square wave or two pulse-width modulated signals, to measure pulse widths, or to generate a software-triggered one-shot pulse. (see figure 11).

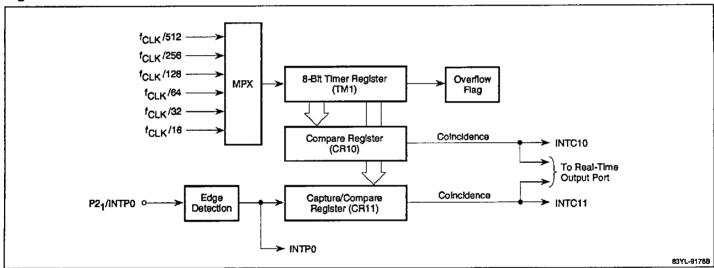

Timer 1 consists of an 8-bit timer (TM1), 8-bit compare register (CR10), and 8-bit capture/compare register (CR11). Timer 1 can be used as two interval timers or to measure pulse widths. In addition, it can be used to generate the output trigger for the real-time output port (see figure 12).

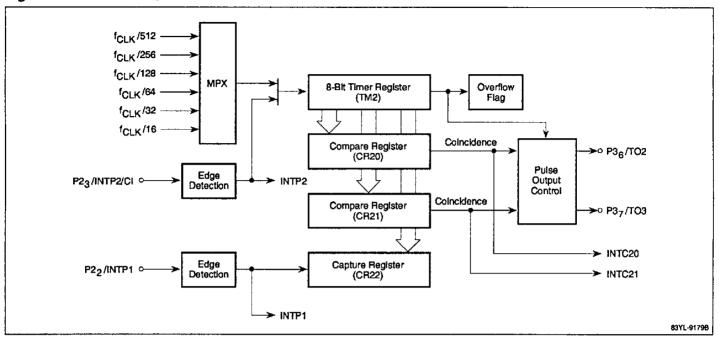

Timer/counter 2 consists of an 8-bit timer (TM2), two 8-bit compare registers (CR20 and CR21), and an 8-bit capture register (CR22). Timer/counter 2 can also be used as two interval timers, to output a programmable square wave or two pulse-width modulated signals, or to measure pulse widths. In addition, it can be used to count external events sensed on the CI line or as a one-shot timer (see figure 13).

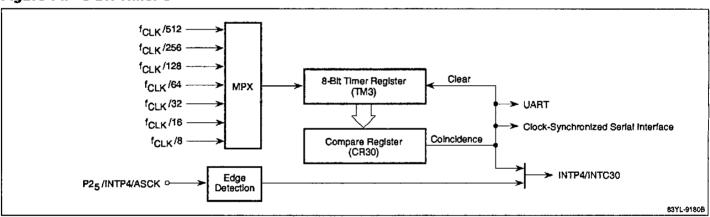

Timer 3 consists of an 8-bit timer (TM3) and an 8-bit compare register (CR30). Timer 3 can be used as an interval timer or as a clock for the clock-synchronized serial interface (see figure 14).

Figure 11. 16-Bit Timer 0

Figure 12. 8-Bit Timer 1

Figure 13. 8-Bit Timer/Counter 2

Figure 14. 8-Bit Timer 3

### Interrupts

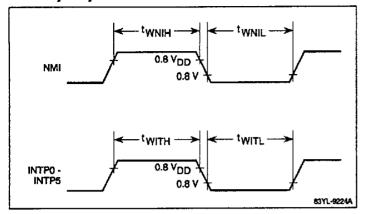

The  $\mu$ PD78238 family has 18 maskable hardware interrupt sources; 6 are external and 12 are internal. Since there are only 16 interrupt vectors and sets of control flags, 2 of the 6 external maskable interrupts, INTP4 and INTP5, share interrupt vectors and control flags with INTC30 and INTAD respectively. The active interrupt source for each shared vector must be chosen by the program. In addition, there is one nonmaskable interrupt and one software interrupt. The software interrupt, generated by the BRK instruction, is not maskable (see table 3).

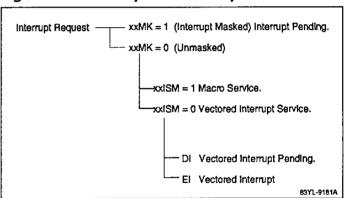

Interrupt Servicing. The  $\mu$ PD78238 family provides two levels of programmable hardware priority control and two different methods of handling maskable interrupt requests: standard vectoring and macro service. The programmer can choose the priority and mode of servicing each maskable interrupt by using the interrupt control registers.

Interrupt Control Registers. The  $\mu$ PD78238 family has four 16-bit interrupt control registers. Each bit in each register is dedicated to one of the 16 active maskable interrupt sources. The interrupt request flag register (IF0) contains an interrupt request flag for each interrupt. The interrupt mask register (MK0) is used to enable or disable any interrupt. The interrupt service mode register (ISM0) specifies whether an interrupt is processed by vectoring or macro service. The priority flag register (PR0) can be used to specify a high or a low priority level for each interrupt.

Two other 8-bit registers are associated with interrupt processing. The interrupt status register (IST) indicates if a nonmaskable interrupt request on the NMI pin is being processed and can be used to allow nesting of nonmaskable interrupt requests. The IE and the ISP bits of the program status word are also used to control interrupts. If the IE bit is zero, all maskable interrupts, but not macro service, are disabled. The IE bit can be set or cleared using the El and DI instructions, respectively, or by directly writing to the PSW. The IE bit is cleared each time an interrupt is accepted. The ISP bit is used by hardware to hold the priority level flag of the interrupt being serviced.

Interrupt Priority. The nonmaskable interrupt (NMI) has priority over all other interrupts. Two hardware controlled priority levels are available for the maskable interrupts. Either a high or a low priority level can be assigned by software to each of the maskable interrupts. Interrupt requests of a priority higher than the processor's current priority level are accepted; requests of the same or lower priority are held pending until the processor's priority state is lowered by program control within the current service routine or by a return instruction from the current service routine.

Interrupt requests programmed to be handled by macro service have priority over all vectored interrupt service regardless of the assigned priority level, and macro service requests are accepted even when the interrupt enable bit in the PSW is set to the disable state (see figure 15).

Figure 15. Interrupt Service Sequence

The default priorities listed in table 3 are fixed by hardware and are effective only when it is necessary to choose between two interrupt requests of the same software assigned priority. For example, the default priorities would be used after the completion of a high priority routine if two interrupts of the same priority routine were pending.

The software interrupt, initiated by the BRK instruction, is executed regardless of the processor's priority level and the state of the IE bit. It does not alter the processor's priority level.

Table 3. Interrupt Sources and Vector Addresses

| Interrupt<br>Request<br>Type | Default<br>Priority | Interrupt Request Generation Source                                | Macro Service<br>Type | Vector<br>Table<br>Address |

|------------------------------|---------------------|--------------------------------------------------------------------|-----------------------|----------------------------|

| Software                     | None                | BRK instruction execution                                          |                       | 003EH                      |

| Nonmaskable                  | None                | NMI (pin input edge detection)                                     | _                     | 0002H                      |

| Maskable                     | 0                   | INTPO (pin input edge detection)                                   | A, B                  | 0006H                      |

|                              | 1                   | INTP1 (pin input edge detection)                                   | А, В                  | 0008H                      |

|                              | 2                   | INTP2 (pin input edge detection)                                   | A, B                  | 000AH                      |

|                              | 3                   | INTP3 (pin input edge detection)                                   | В                     | 000CH                      |

|                              | 4                   | INTC00 (TM0-CR00 coincidence signal generation)                    | В                     | 0014H                      |

|                              | 5                   | INTC01 (TM0-CR01 coincidence signal generation)                    | В                     | 0016H                      |

|                              | 6                   | INTC10 (TM1-CR10 coincidence signal generation)                    | A, B, C               | 0018H                      |

|                              | 7                   | INTC11 (TM1-CR11 coincidence signal generation)                    | A, B, C               | 001AH                      |

|                              | 8                   | INTC21 (TM2-CR21 coincidence signal generation)                    | A, B                  | 001 CH                     |

|                              | 9                   | INTP4 (pin input edge detection)                                   | В                     | 000EH                      |

|                              |                     | INTC30 (TM3-CR30 coincidence signal generation)                    | A, B                  |                            |

|                              | 10                  | INTP5 (pin input edge detection)                                   | В                     | 0010H                      |

|                              |                     | INTAD (end of A/D conversion)                                      | A, B                  |                            |

|                              | 11                  | INTC20 (TM2-CR20 coincidence signal generation)                    | A, B                  | 0012H                      |

|                              | 12                  | INTSER (generation of asynchronous serial interface receive error) |                       | 0020H                      |

|                              | 13                  | INTSR (end of asynchronous serial interface reception)             | A, B                  | 0022H                      |

|                              | 14                  | INTST (end of asynchronous serial interface transmission)          | A, B                  | 0024H                      |

|                              | 15                  | INTCSI (end of clocked serial interface transmission)              | A, B                  | 0026H                      |

**Vectored Interrupt.** When vectored interrupt is specified for a given interrupt request, (1) the program status word and the program counter are saved on the stack, (2) the processor's priority is set to that specified for the interrupt, (3) the IE bit in the PSW is set to zero, and (4) the routine whose address is in the interrupt vector table is entered. At the completion of the service routine, the RETI instruction (RETB instruction for the software interrupt) reverses the process and the  $\mu$ PD78238 family device resumes the interrupted routine.

#### Macro Service

When macro service is specified for a given interrupt, the macro service hardware temporarily stops the executing program and begins to transfer data between the special function register area and the memory space. One byte is transferred each interrupt. When the data transfer is complete, control is returned to the executing program, providing a completely transparent method of interrupt service. Macro service significantly improves response time and makes it unnecessary to save any registers.

For each request on the interrupt line, one operation is performed, and an 8-or 16-bit counter is decremented. When the counter reaches zero, a vectored interrupt service routine is entered according to the specified priority.

Macro service is provided for all of the maskable interrupt requests except INTSER, the asynchronous serial interface receive error interrupt request. Each interrupt request has a dedicated macro service control word stored in Internal RAM (see figure 16). The function to be performed is specified in the control word.

The  $\mu$ PD78238 family provides three different types of macro service transfers:

Macro Service Type A. A byte of data is transferred in either direction between a special function register, preassigned for each interrupt request, and a buffer in internal RAM (FExx). Only the 8-bit macro service counter is available for Type A transfers. The preassigned SFRs for the 12 interrupt requests that support macro service Type A transfers are listed in table 4.

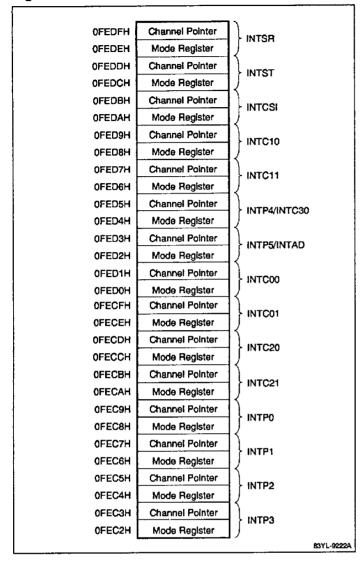

Figure 16. Macro Service Control Word Map

Table 4. Macro Service Type A Interrupts and Assigned SFRs

| Interrupt Request                                         | Source/Destination SFR                           |

|-----------------------------------------------------------|--------------------------------------------------|

| INTC10. TM1-CR10 coincidence                              | CR10. Timer 1 8-bit compare register             |

| INTC11 TM1-CR11 coincidence                               | CR11. Timer 1 8-bit capture/<br>compare register |

| INTC20: TM2-CR20 coincidence                              | CR20 Timer 2 8-bit compare register              |

| INTC21: TM2-CR21 coincidence                              | CR21 Timer 2 8-bit compare register              |

| INTC30 TM3-CR30 coincidence                               | CR30: Timer 3 8-bit compare register             |

| INTSR: End of asynchronous serial interface reception     | RxB. Serial receive buffer                       |

| INTST: End of asynchronous serial interface transmission  | TxS Serial transmit shift register               |

| INTCSI End of clocked serial interface transmission       | SIO Serial shift register                        |

| INTAD: End of A/D conversion                              | ADCR: A/D conversion result register             |

| INTPO: External interrupt pin P0 <sub>1</sub>             | CR11: Timer 1 8-bit capture/<br>compare register |

| INTP1 External interrupt pin P0 <sub>2</sub>              | CR22: Timer 2 8-bit capture register             |

| INTP2 <sup>-</sup> External interrupt pin P0 <sub>3</sub> | TM2 Timer 2 8-bit timer register                 |

Macro Service Type B. A byte of data is transferred in either direction between any specified special function register and a buffer anywhere in the 64K byte address space. Macro service Type B transfers can be initiated by any maskable interrupt except INTSER.

Macro Service Type C. A byte of data is transferred from a buffer anywhere in the 64K byte address space to one of the 8-bit compare registers of timer 1. At the same time, a second byte of data is transferred from a buffer anywhere in the 64K byte address space to the real-time output port buffer. The macro service counter can be programmed either to be an 8- or 16-bit counter. Macro service Type C transfers can be initiated by INTC10 with data transferred to CR10 and P0L or P0H, or by INTC11 with data transferred to CR11 and P0L or P0H.

In addition, the macro service Type C transfer can be initialized to automatically alter timer compare register values or to repeatedly output a prespecified pattern at a fixed or variable rate. By using macro service Type C transfers to control the real-time output ports, the  $\mu$ PD78238 family device can easily and accurately drive two independent stepper motors.

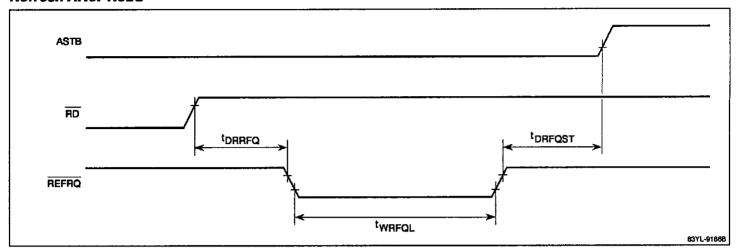

#### Refresh

The refresh signal is used with any pseudostatic RAM equivalent of the NEC  $\mu$ PD428128. The refresh cycle can be set to one of four intervals: 16, 32, 64, or 128/f<sub>CLK</sub> (2.6, 5.3, 10.7, and 21.3  $\mu$ s at 12 MHz). The refresh cycle is timed to follow a read or write operation to avoid interference with external memory access cycles.

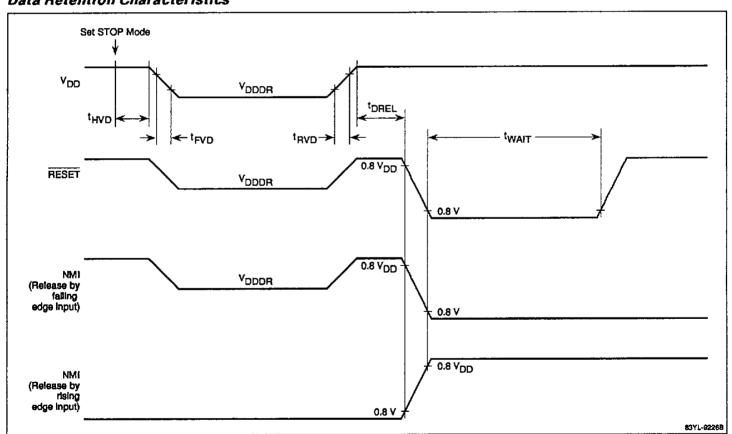

### Standby Modes

HALT and STOP modes are provided to reduce power consumption when CPU action is not required. In HALT mode, the CPU is stopped but the system clock continues to run. The HALT mode is released by any unmasked interrupt, an external NMI, or an external reset pulse. In STOP mode, both the CPU and the system clock are stopped, further minimizing the power consumption. The STOP mode is released by either an external reset pulse or an external NMI. The HALT and STOP modes are entered by programming the standby control register (STBC). This register is a protected location and can be written to only by a special instruction. If the third and fourth bytes of the instruction are not complements of each other, the data is not written and the next instruction is executed.

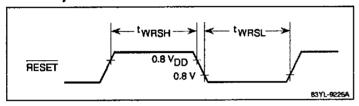

#### **External Reset**

The  $\mu$ PD78238 family is reset by taking the RESET pin low. The RESET input pin contains a noise filter to protect against spurious system resets caused by noise. On power-up, the RESET pin must remain low until the power supply reaches its operating voltage and the oscillator has stabilized. During reset, the program counter is loaded with the address contained in the reset vector table (address 0000H- 0001H); program execution starts at that address upon the RESET pin going high. While RESET is low, all external lines except VSS, VDD, AVSS, AVREF1, AVREF2, AVREF3, X1, and X2 are in the high impedance state.

### **ELECTRICAL SPECIFICATIONS**

# **Absolute Maximum Ratings**

$T_{\Delta} = +25^{\circ}C$

| 1A - 120 0                                                                         |                                                                          |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Operating voltage, V <sub>DD</sub> AV <sub>DD</sub> AV <sub>SS</sub>               | -0.5 to +70V<br>AV <sub>SS</sub> to V <sub>DD</sub> +05V<br>-0.5 to +05V |

| Input voltage, V <sub>I1</sub><br>V <sub>I2</sub> (Note 1 for µPD78P238)           | -0.5 to V <sub>DD</sub> + 0.5 V<br>-0 5 to +13.5 V                       |

| Output voltage, V <sub>O</sub>                                                     | -0.5 to V <sub>DD</sub> + 0.5 V                                          |

| Low-level output current, I <sub>OL</sub><br>Per pin<br>Total, all output pins     | 15 mA<br>100 mA                                                          |

| High-level output current, I <sub>OH</sub> Per pin Total, all output pins          | –10 mA<br>–50 mA                                                         |

| A/D converter reference input voltage, AV <sub>REF1</sub>                          | -0.5 to V <sub>DD</sub> + 0.3 V                                          |

| D/A converter reference<br>input voltage, AV <sub>REF2</sub><br>AV <sub>REF3</sub> | -0.5 to V <sub>DD</sub> + 0.3 V<br>-0.5 to V <sub>DD</sub> + 0.3 V       |

| Operating temperature, T <sub>OPT</sub>                                            | −40 to +85°C                                                             |

| Storage temperature, T <sub>STG</sub>                                              | -65 to +150°C                                                            |

|                                                                                    |                                                                          |

#### Note:

(1) MODE/V<sub>PP</sub> and P2<sub>1</sub>/INTP0/A<sub>9</sub> in programming mode Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the rating could cause permanent damage. The device should be operated within the limits specified under DC and AC chracteristics

# **Operating Conditions**

| Oscillation Frequency                   | TA           | V <sub>DD</sub> |  |

|-----------------------------------------|--------------|-----------------|--|

| $f_{XX} = 4 \text{ to } 12 \text{ MHz}$ | -40 to +85°C | +5 V ±10%       |  |

## Capacitance

$T_A = +25^{\circ}C; V_{DD} = V_{SS} = 0 V$

| Item                     | Symbol          | Max | Unit | Conditions                      |

|--------------------------|-----------------|-----|------|---------------------------------|

| Input capacitance        | Cl              | 20  | рF   | f = 1 MHz; pins<br>not used for |

| Output capacitance       | Co              | 20  | pF   | measurement<br>are at 0 V       |

| Input/output capacitance | C <sub>IO</sub> | 20  | pF   | •                               |

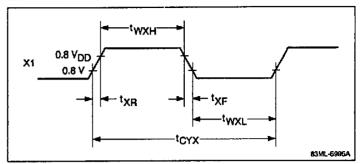

### **External Clock Operation**

$T_A = -40 \text{ to } +85^{\circ}\text{C}; V_{DD} = +5 \text{ V } 10\%; V_{SS} = 0 \text{ V}$

| Item                      | Symbol          | Min | Max | Unit | Conditions |

|---------------------------|-----------------|-----|-----|------|------------|

| X1 input low-level width  | twxl.           | 30  | 130 | ns   |            |

| X1 input high-level width | twxн            | 30  | 130 | ns   |            |

| X1 input rise time        | t <sub>XR</sub> | 0   | 30  | ns   | •          |

| X1 input fall time        | <sup>t</sup> XF | 0   | 30  | пѕ   | •          |

| X1 input clock cycle time | tcyx            | 82  | 250 | ns   | -          |

### **DC** Characteristics

$T_A = -40 \text{ to } +85^{\circ}\text{C}, V_{DD} = \text{AV}_{DD} = +5 \text{ V } \pm 10\%; V_{SS} = \text{AV}_{SS} = 0 \text{ V}$

| item                                 | Symbol            | Min                   | Тур | Max      | Unit | Conditions                                                         |

|--------------------------------------|-------------------|-----------------------|-----|----------|------|--------------------------------------------------------------------|

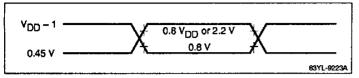

| Low-level input voltage              | V <sub>IL</sub>   | o                     |     | 08       | ٧    |                                                                    |

| High-level input voltage             | V <sub>IH1</sub>  | 22                    |     | $v_{DD}$ | ٧    | Except the specified pins (Note 1)                                 |

| -                                    | V <sub>IH2</sub>  | 0.8 V <sub>DD</sub>   |     | $v_{DD}$ | ٧    | Specified pins (Note 1)                                            |

| Low-level output voltage             | V <sub>OL1</sub>  |                       |     | 0 45     | ٧    | l <sub>OL</sub> = 20 mA                                            |

|                                      | V <sub>OL2</sub>  |                       |     | 1.0      | ٧    | $I_{OL} = 80 \text{ mA (Note 2)}$                                  |

| High-level output voltage            | V <sub>OH1</sub>  | V <sub>DD</sub> – 1.0 |     |          | ٧    | I <sub>OH</sub> = -1 0 mA                                          |

|                                      | V <sub>OH2</sub>  | V <sub>DD</sub> - 05  |     |          | ٧    | $I_{OH} = -100 \mu\text{A}$                                        |

|                                      | V <sub>OH3</sub>  | 20                    |     |          | ٧    | $I_{OH} = -50$ mA (Note 3)                                         |

| X1 low-level input current           | I <sub>I</sub> L  |                       |     | -100     | μΑ   | $0 \text{ V} \leq \text{ V}_{\text{I}} \leq \text{ V}_{\text{IL}}$ |

| X1 high-level input current          | I <sub>IH</sub>   |                       |     | 100      | μΑ   | $V_{\text{IH2}} \leq V_{\text{I}} \leq V_{\text{DD}}$              |

| nput leakage current                 | IL1               |                       |     | ±10      | μΑ   | $0 \text{ V} \leq \text{ V}_{\text{I}} \leq \text{ V}_{\text{DD}}$ |

| Output leakage current               | lo                |                       |     | ±10      | μΑ   | $0 \text{ V} \leq \text{ V}_{\text{O}} \leq \text{ V}_{\text{DD}}$ |

| V <sub>DD</sub> power supply current | <sup> </sup> DD1  |                       | 20  | 40       | mA   | Operating mode, f <sub>XX</sub> = 12 MHz                           |

|                                      | l <sup>DDS</sup>  |                       | 7   | 20       | mA   | HALT mode, f <sub>XX</sub> = 12 MHz                                |

| Data retention voltage               | V <sub>DDDR</sub> | 2 5                   |     | 5.5      | ٧    | STOP mode                                                          |

# DC Characteristics (cont)

| Item                   | Symbol | Min | Тур | Max | Unit | Conditions                           |

|------------------------|--------|-----|-----|-----|------|--------------------------------------|

| Data retention current | DDDR   |     |     | 10  | μΑ   | STOP mode; V <sub>DDDR</sub> = 2.5 V |

|                        |        |     | •   | 20  | μΑ   | STOP mode, $V_{DDDR} = 5 V \pm 10\%$ |

| Pullup resistor        | RL     | 15  | 40  | 80  | kΩ   | V <sub>I</sub> = 0 V                 |

#### Notes:

- (1) X1, X2, RESET, P2<sub>0</sub>/NMI, P2<sub>1</sub>/INTP0, P2<sub>2</sub>/INTP1,P2<sub>3</sub>/INTP2/CI, P2<sub>4</sub>/INTP3, P2<sub>5</sub>/INTP4/ASCK, P2<sub>6</sub>/INTP5, P2<sub>7</sub>/SI, P3<sub>2</sub>/SCK, P3<sub>3</sub>/SO/SB0, and MODE pins.

- (2) Pins P1<sub>0</sub> P1<sub>7</sub>, P4<sub>0</sub>/AD<sub>0</sub> P4<sub>7</sub>/AD<sub>7</sub>, and P5<sub>0</sub>/A<sub>8</sub> P5<sub>7</sub>/A<sub>15</sub>.

- (3) Pins P0<sub>0</sub> P0<sub>7</sub>.

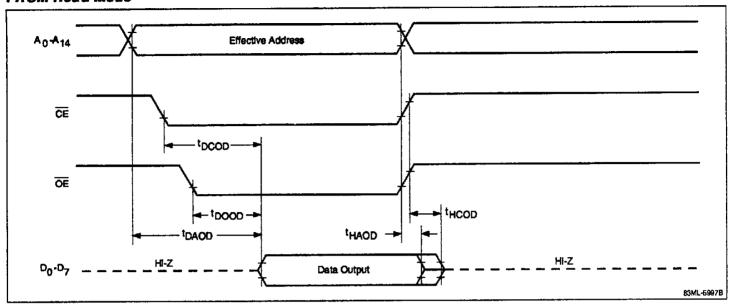

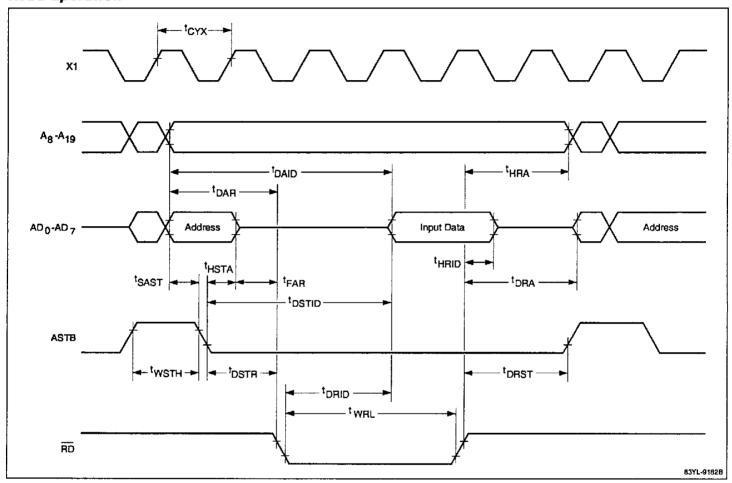

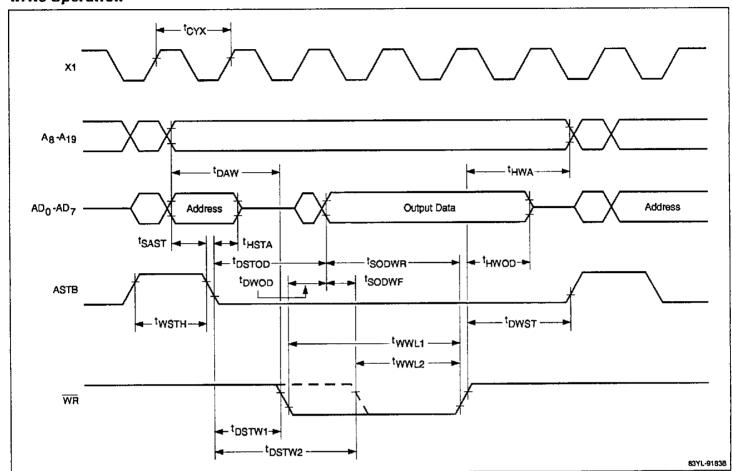

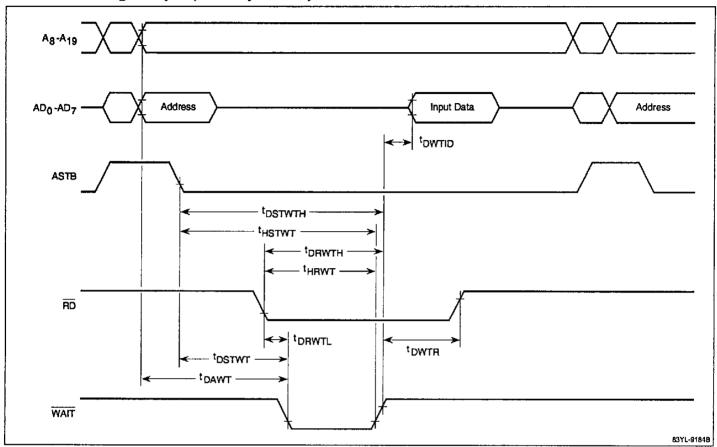

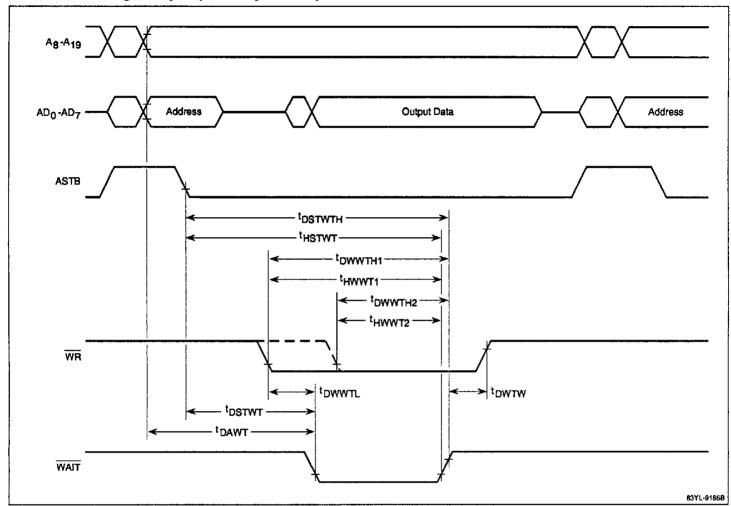

# AC Characteristics—Read/Write Operation

$T_A = -40 \text{ to } +85^{\circ}\text{C}; V_{DD} = +5 \text{ V } \pm 10\%; V_{SS} = 0 \text{ V; } f_{XX} = 12 \text{ MHz; } C_L = 100 \text{ pF}$

| Item                                    | Symbol             | Calculation Formula (Note 2, 3) | Min | Max | Unit | Conditions                              |

|-----------------------------------------|--------------------|---------------------------------|-----|-----|------|-----------------------------------------|

| X1 input clock cycle time               | tcyx               | _                               | 82  | 250 | ns   |                                         |

| Address setup time to ASTB ↓            | <sup>t</sup> SAST  | t <sub>CYX</sub> - 30           | 52  |     | ns   |                                         |

| Address hold time from ASTB ↓ (Note 1)  | <sup>†</sup> HSTA  | <del>-</del>                    | 25  |     | ns   |                                         |

| Address hold time from RD†              | tHRA               | _                               | 30  |     | ns   |                                         |

| Address hold time from WH †             | tHWA               | -                               | 30  |     | ns   |                                         |

| Address to RD ↓ delay time              | †DAR               | 2t <sub>CYX</sub> - 35          | 129 |     | ns   |                                         |

| Address float time to $\overline{RD}$ ↓ | t <sub>FAR</sub>   | t <sub>CYX</sub> /2 - 30        | 11  |     | пз   |                                         |

| Address to data input time              | †DAID              | (4+2n) t <sub>CYX</sub> - 100   |     | 228 | ns   | No wait states                          |

| ASTB ↓ to data input time               | <sup>t</sup> DSTID | (3+2n)t <sub>CYX</sub> - 65     |     | 181 | ns   | No wait states                          |