## **GENERAL DESCRIPTION**

Winbond s W9971CF is a highly-integrated VLSI providing high performance graphics acceleration and TV-quality full screen motion video acceleration for IBM PCs or compatibles. The W9971CF integrates an NTSC/PAL TV encoder with S-Video or composite video for flicker-free and glueless TV output. An on-chip RAMDAC and a dual programmable clock synthesizer with a 170 MHz pixel data rate are also integrated into the chip to simplify system design and reduce cost.

The W9971CF is a high-performance graphics accelerator specially designed for Microsoft Windows, Mac OS, IBM OS/2, and DOS-based applications. In addition to 100% IBM VGA register-level compatibility, the W9971CF incorporates a 64-bit graphics engine (GE) to accelerate drawing functions such as bit block transfer (BitBLT), line drawing, clipping, and hardware cursor manipulation.

The W9971CF s integrated video accelerator (VA) features high-quality video filtering, bilinear interpolating scaling along both the X and Y axes, color space conversion and overlay keying. In addition to accelerating software video playback, the W9971CF also provides an advanced multimedia video interface for glueless interfacing to major TV decoders such as the Philips SAA711X and the Brooktree Bt815A/7A/9A. The 16-bit baseline VESA Advanced Feature Connector (VAFC) and the 8-bit bidirectional IBM Feature Connector are also supported for legacy video applications. By performing scaling and color space conversion on the fly, the W9971CF provides high-quality video playback in 1024 × 768 256-color mode with only 1 MByte of DRAM.

The W9971CF integrates a high quality NTSC/PAL TV encoder to directly interface to TV sets. It allows an NTSC/PAL TV to be used as the primary or secondary display for Windows-based and video playback applications. The TV output capabilities are required for Microsoft Entertainment PC 97 designs that do not come bundled with a VGA monitor. These capabilities provide a more realistic game, video, and multimedia experience for users who use large-screen TVs.

The flexible display memory interface design of the W9971CF allows system designers to select various types of DRAMs, including  $128K \times 8$ ,  $128K \times 16$ ,  $256K \times 4$ ,  $256K \times 8$ , and  $256K \times 16$ . These DRAMs may be used in either fast page or extended data out (EDO) modes.

The W9971CF supports a glueless interface with the 32-bit PCI Local Bus. Green PC power management is supported via VESA Display Power Management Signaling (DPMS) and power-down of the on-chip RAMDAC and clock synthesizers. VESA DDC1 and DDC2 smart monitor control is also supported.

www.DataSheet4U.com

## **FEATURES**

## ☐ Integrated Video Graphics Controller with TV encoder

- 64-bit graphics engine

- Integrated video accelerator

- On-chip 24-bit true color RAMDAC with up to 170 MHz pixel clock rate

- On-chip clock synthesizers generating up to 170 MHz VCLK and 100 MHz MCLK

- On-chip flicker filtering and NTSC/PAL TV encoder

#### □ GUI Acceleration

- 64-bit GUI acceleration

- Fast frame buffer blts include screen to screen blt, pattern blt, color/font expanding blt, color/font expansion, rectangle fill, etc.

- 256 ROPs (Raster Operations) for all 8/15/16/24 bit-per-pixel modes

- · Transparent blt using the color key for source or destination

- Accelerated Bresenham line draw and Short Stroke Vector

- Rectangle and line clipping

- Built-in 64×64×2 or 32×32×2 hardware cursor

#### □ Video Conferencing Acceleration

- Glueless digital camera interface with direct support of CCIR 656 format; analog camera support with external video decoder

- · Hardware 2-dimensional down-scaling for local view capture

- Hardware dual-video window for local and remote viewing

- Built-in Color Space Conversion and 2-dimensional bi-linearly interpolated up-scaling

### □ Video Playback Acceleration

- Video (YUV) and graphics (RGB) shared frame buffer architecture

- RGB 5:5:5, RGB 5:6:5, and YUV 4:2:2 packed video formats support

- Double buffering and single command page flipping for anti-tearing support

- Readable current scan line refresh to allow behind the beam writing in non-double-buffered scenarios

- On-the-fly 2-D bi-linear interpolation and arbitrary up-scaling

- On-chip standard CCIR 601 YUV to RGB CSC (Color Space Conversion)

- On-the-fly interpolated up-scaling to allow 320×200 game image to be displayed at 640× 480 full-screen resolution

- · Color keying, chroma keying, and window keying to overlay video and graphics streams

· On-the-fly blending of video and graphics streams

### □ TV Output

- Integrated TV encoder to support both NTSC and PAL output

- 3-line flicker removal filter for flicker reduction

- Underscan scaling to support 640x480 modes on NTSC and 800x600 modes on PAL

- Support RCA-style composite video and S-Video

- Simultaneous output to both VGA monitor and TV

- Support simultaneous graphics on VGA and video on TV

- TV auto-detect, VGA and TV output can be enabled or disabled independently

#### ■ Multimedia Video Interface

- VMI Bus v.1.4 compliance

- Glueless support for 8/16-bit YUV input and CCIR656 standard, and 16-bit RGB input

- Arbitrary down-scaling for the captured video stream

- I2C serial bus control for other peripherals such as TV tuner, video decoder, etc.

- Glueless Support for 16-bit baseline VESA Advanced Feature Connector (VAFC)

- Glueless Support for 8-bit bi-directional pass-through VGA feature connector

## ☐ RAMDAC and Dual Clock Synthesizer

- Integrated 170 Mhz triple 8-bit RAMDAC

- Integrated dual-clock synthesizer for MCLK speeds up to 100 Mhz and VCLK speeds up to 170 Mhz

#### □ System Bus Interface

- Glueless support for zero wait-state, 32-bit PCI bus

- Big-endian and little-endian byte ordering support

- PCI 2.1 compliant (33 Mhz)

#### ■ Memory Interface

- 64 or 32-bit interface to support 1-, 2-, or 4-MByte frame

- Support FPM and EDO DRAMs with 100 Mhz MCLK

### Extended High Non-Interlaced Refresh and Resolution Support (2 Mbytes DRAM)

- 1280x1024x256, 85 Hz (157.5 Mhz VCLK)

- 1024x768x64K, 85 Hz (94.5 Mhz VCLK)

- 800x600x16M, 85 Hz (56.25 Mhz VCLK)

- 1600x1200x256, 65 Hz (173 Mhz VCLK)

## ☐ Green PC and Monitor Plug and Play Support

- VESA DPMS compliance

- VESA DDC2B compliance

## **□** Software Support

- VESA BIOS extension support and VESA monitor timing compliant

- Drivers for all major operating systems such as Windows 3.11, 95, NT, OS/2 Warp 3.0, etc.

## ☐ 208-pin PQFP Package

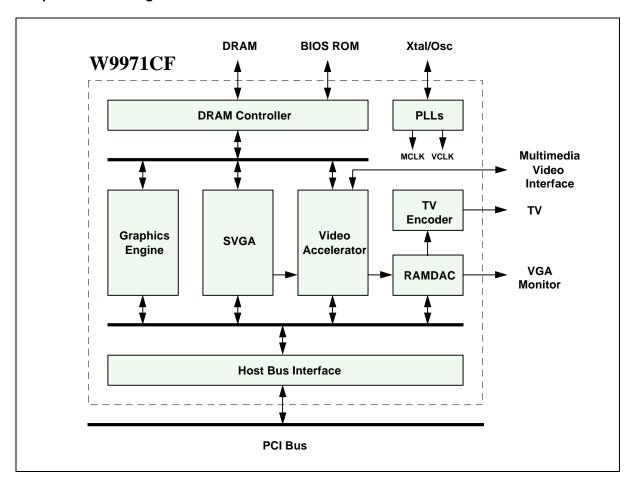

MAN Data Shoot All com Fig. 1. W9971CF Block Diagram

## **FUNCTIONAL DESCRIPTIONS**

## **Graphics Engine**

The 64-bit graphics engine (GE) is specially designed to improve the performance of Microsoft Windows applications and other graphical user interface software. Performance is enhanced by accelerating GUI functions such as BitBLTs, Bresenham line draw, and short stroke vector. The GE performs several types of BitBLTs, including HostBLT, pattern BLT, color/font expanding BLT, transparent BLT, color expansion, and rectangle fill, with 256 ROPS on source, pattern, and destination. The graphics engine operates at all pixel depths in enhanced modes, including 8/16/24 bit-per-pixel modes. A fully Microsoft Windows compatible  $64 \times 64 \times 2$  or  $32 \times 32 \times 2$  hardware cursor, is used to speed up cursor performance and accelerate all graphics operations by eliminating the CPU overhead associated with cursor manipulation.

### Video Accelerator

The Video Accelerator is a high-quality video processor for enhancing and displaying video images. It not only accelerates software video playback but also facilitates the interface to MPEG-1 video decoders and TV decoders.

The video accelerator employs back-end color space conversion and a scaling mechanism. Video and game-generated graphics frames are read from an off-screen buffer and sent to the overlay and blending control block as the secondary stream. Color space conversion and scaling are performed along the way. This on-the-fly video acceleration and overlaying ensure game and video playback at full speed.

#### **Color Space Conversion**

The built-in color space converter converts YUV format to 24-bit RGB format according to the CCIR 601-2 Recommendation.

## **Down Scaling**

The down-scaling function is performed by dropping pixels or lines. To support arbitrary scaling factors, the video accelerator uses a digital differential accumulator (DDA) to drop pixels or lines smoothly. The scaling factor may range from 1/64 to 63/64.

## Scaling up by 2D Interpolation

Rather than duplicating pixels or lines for enlargement, the video accelerator uses a 2-D bilinear interpolation algorithm to enhance the output for high-quality video display.

The interpolation algorithm creates seven weighted, intermediate values between two original pixels or lines. This allows a maximum enlargement of 800%. For non-integer scaling, a 10-bit DDA with 1/1024 resolution is used to interpolate pixels by averaging.

### 2x Scaling

The 2x scaling located in the RAMDAC is used to optionally scale up the overlaid data stream by a factor of 2. This is used to scale  $320 \times 240$  game-generated frames to full screen.

## **Filtering**

The video accelerator provides horizontal RGB or YUV filtering to reduce noise and aliasing artifacts in the video data stream

### Cropping

A rectangular cropping window is supported in the video accelerator for subsampling the incoming video data stream. Only video located in the cropping window can be stored into the off-screen buffer.

### Alpha Blending

Alpha blending is supported for overlaying the primary stream and secondary stream. The alpha value can be 1 bit or 3 bits. The 1-bit alpha depth overlaying (also known as a software key) is supported only for the pixel format of RGB 1:5:5:5, where the alpha bit value of 0 is transparent and value of 1 is opaque.

An overlay control register specifies the 3-bit alpha value for the primary stream (Kp) and secondary stream (Ks). Note that Kp + Ks must be  $\leq$  8. The blending equation is [Pp  $\times$  Kp + Ps  $\times$  Ks] /8, where Pp is the primary stream pixel data and Ps is the secondary stream pixel data.

### **Overlay Control**

The overlay controller provides control for overlaying of four input sources: the primary stream (normally the graphics data), secondary stream, blending stream, and FC/VAFC pass-through data stream. When the hardware cursor is active, it is overlaid on top of all image streams. The W9971CF supports a range of advanced keying forms; these include window key, color key, chroma key, software key (1-bit alpha overlaying in RGB 1:5:5:5 format), external key (FC/VAFC only), and a logical combination of these keys.

#### **Dual Video Windows**

Two video windows may be simultaneously displayed on the monitor. This makes the W9971CF highly suitable for video conferencing applications. If the two video windows are placed at different scan lines, they can be scaled separately with different factors.

#### Flicker Filter and TV Encoder

The W9971CF incorporates an integrated TV encoder, flicker-free filtering, and vertical scaling for TV output. It directly interfaces with a composite or S-video connector for NTSC or PAL TV output.

The software reads the TV output hardware to detect whether a TV is attached to either S-Video or composite output connectors. This allows the operating system and graphics drivers to support a correct display output during the startup sequence (i.e. the correct resolution and refresh rate to use), and for applications to adjust their user interfaces to the screen s capabilities. Simultaneous output to a VGA monitor and TV are also supported. If a VGA monitor is not attached, the TV output works automatically as the primary display. The same image can be simultaneously displayed on the VGA monitor and TV. Alternatively, graphics may be displayed on the VGA monitor while display video is displayed on the TV. The graphics adapter must default to modes compatible with the TV;s output. Adapters manufactured for NTSC countries should default to 60-Hz modes while adapters manufactured for PAL countries should default to 50-Hz modes.

When displayed on an interlaced TV, VGA data as well as PC games are often unusable due to the flicker effect caused by an interlaced monitor. The W9971CF uses a 3-line flicker filtering technique to provide the best flicker-free TV quality. The vertical underscan scaling is also implemented to allow 640x480 resolution modes to fit NTSC displays and 800x600 modes to fit PAL displays.

#### **Gamma Correction**

In most TV systems, CRT displays have an inherent nonlinear relationship between signal voltage and light intensity. Linear digital RGB data (normally, the graphics data) need gamma correction to compensate for the nonlinear CRT characteristics. The linear RGB data is gamma corrected to obtain a voltage that can be applied to the TV monitor.

### Flicker Filter

Without filtering, one contrast VGA line may be encoded into one field of the TV video. This will cause flicker at 30 Hz with NTSC and 25 Hz with PAL. The W9971CF incorporates an advanced flicker-free filter to eliminate such problems by providing three filter modes: High Filter (3-line), Medium Filter (2-line), and No Filter.

#### **TV Auto-detect**

In order for the CPU to determine the presence of a TV monitor, the W9971CF includes circuitry to detect a loaded or unloaded TV output connection. This information can be used to detect the existence and the type of TV connector used.

### Graphics on VGA and Video on TV

The W9971CF can display the same image (including graphics and video) on both a VGA monitor and a TV. It can also display different images, i.e. graphics on VGA and video on TV. This is controlled by the TV Video Select bit of the TV Encoder register.

### **Vertical Scaling**

The W9971CF is able to correct vertical overscan via hardware scaling. This allows 640x480 resolution modes to fit onto NTSC displays and 800x600 modes to fit onto PAL displays. This is done by using a 6-bit DDA which is controlled by the TV Underscan Scaling Control register.

www.DataSheet4U.com

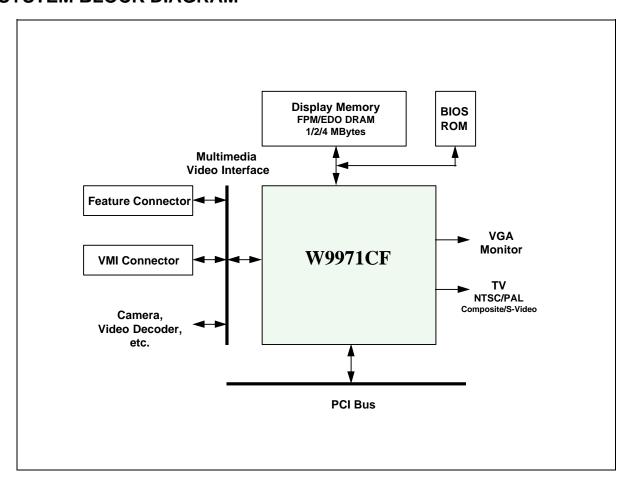

# SYSTEM BLOCK DIAGRAM

Fig. 3. System Block Diagram

### **Headquarters:**

Winbond Electronics Corp. No.4, Creation Rd. III Science Park, Hsinchu Taiwan, ROC T: 886 35 770066

Taiwan, ROC San Jose, CA951:

T: 886 35 770066

F: 886 35 792647

WWW: www.winbond.com.tw

USA:

Winbond Electronics North America Corp. 2730 Orchard Parkway San Jose, CA95134 T: 1 408 9436666 F: 1 408 9436668

## Taipei:

115/11F Ming Sheng E. Rd.

Taipei, Taiwan ROC

T: 886 2 7190505

F: 886 2 7197502

## Hong Kong:

Winbond Electronics [H.K.] Ltd. Rm 803, World Trade Square, Tower II Kowloon, Hong Kong T: 852 27516023 F: 852 27552064

www.DataSheet4U.com