## Advance Information

## **Dual 16-Bit Linear Codec-Filter**

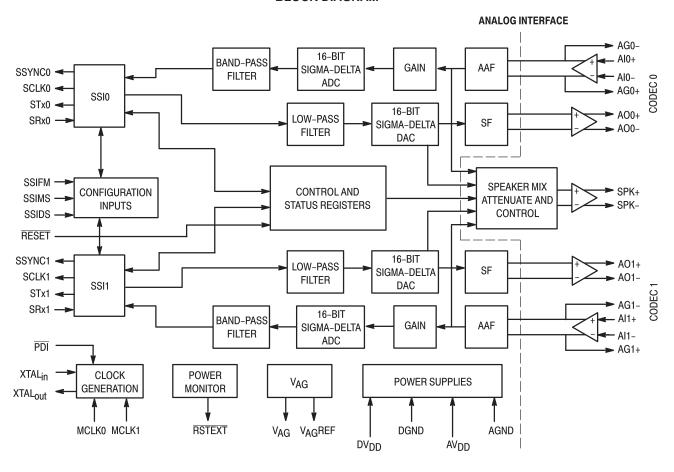

The MC143416 Dual 16–Bit Linear Codec–Filter is a single–chip implementation of the data conversion interface required to design high–speed modems meeting a wide range of standards such as ITU–T V.34 and V.90 modem. It includes two high performance Analog–to–Digital (A/D) and Digital–to–Analog (D/A) data converters. The device performs all filtering operations related to the conditioning and sample rate conversion of signals to and from the data interface. Output from both codecs (COder/DECoder) is in 16–bit 2s complement format.

The MC143416 includes the necessary logic needed to generate all clocks (oversampling, intermediate frequency, and baud rate) required to perform the data processing operations involved in the oversampling conversion of voice and data signals. Sample rates are fully programmable in the range of 8 kilosamples/second (ks/s) to 16 ks/s. The bandwidth of the MC143416 is 0.425 \* Sample Frequency (FS).

The MC143416 includes two Synchronous Serial Interfaces (SSIs) through which an external Digital Signal Processor (DSP) can configure and monitor the operation of the device. Digital sample data is transferred to and from the codecs through the serial ports. In addition, information can be written and read to the control and status registers of the device via the serial port, transparent to the flow of sample data. When used in a high–speed modem application, the MC143416 provides the analog front end interface required to support modem and voice features.

#### MC143416 Features

- Fully-Differential Analog Circuit Design for Lowest Noise

- Two High Performance 16-Bit Sigma-Delta A/D and D/A Converters

- Band–Pass and Low–Pass Filtering for Both Codecs is Performed On–Chip

- Power Monitor Circuit

- Single 5 V ± 5% Power Supply

- Two Configurable Serial Ports

- On-Chip Precision Reference Voltage

- On–Chip Speaker Driver and Mixer with Programmable Gain Capable of Delivering 15 mW of Power into a Small Speaker (32  $\Omega$ )

- Bandwidth is 0.425 \* FS

- No External Filtering Required Because of Flat Response Over Passband

- Capable of Providing the Analog Front End for Wide Range of Modem Standards

MC143416

PB SUFFIX TQFP CASE 824D

**ORDERING INFORMATION**

MC143416PB TQFP

This document contains information on a new product. Specifications and information herein are subject to change without notice.

REV 3 5/98 TN98052800

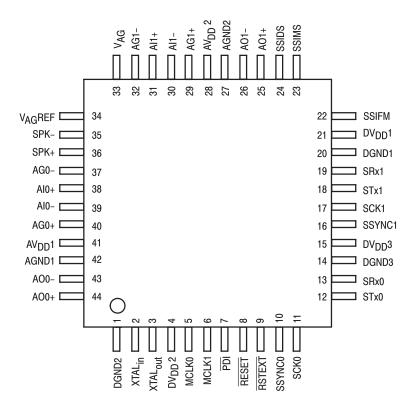

#### **PIN ASSIGNMENT**

#### **BLOCK DIAGRAM**

#### MAXIMUM RATINGS (Voltages Referenced to DGND or AGND)

| Symbol           | Parameter                                     | Value                                  | Unit |

|------------------|-----------------------------------------------|----------------------------------------|------|

| V <sub>DD</sub>  | DC Supply Voltage                             | - 0.5 to 6.0                           | V    |

|                  | Voltage on Any Analog Input or Output<br>Pin  | AGND - 0.3<br>to V <sub>DD</sub> + 0.3 | V    |

|                  | Voltage on Any Digital Input or Output<br>Pin | DGND - 0.3<br>to V <sub>DD</sub> + 0.3 | V    |

| TA               | Operating Temperature Range                   | - 40 to 85                             | °C   |

| T <sub>stg</sub> | Storage Temperature Range                     | - 85 to 150                            | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high—impedance circuit.

#### **POWER SUPPLY** $(T_A = -40 \text{ to } 85^{\circ}\text{C})$

| Characteristics                                                                           |                   | Min  | Тур      | Max        | Unit |

|-------------------------------------------------------------------------------------------|-------------------|------|----------|------------|------|

| DC Supply Voltage                                                                         |                   | 4.75 | 5.0      | 5.25       | V    |

| Active Current Dissipation (V <sub>DD</sub> = 5 V)<br>2 Codecs @ 16 kHz and XTAL @ 25 MHz | Analog            | _    | 6        | 12         | mA   |

| with OSR = 1.632 MHz                                                                      | Digital           | _    | 44       | 52         |      |

| Power–Down Current                                                                        | Analog<br>Digital |      | 60<br>60 | 100<br>100 | μА   |

#### **DIGITAL LEVELS** ( $V_{DD}$ = 4.75 to 5.25 V, DGND = 0 V, $T_A$ = -40 to 85°C)

| Symbol           | Characteristics                                                               | Min         | Max | Unit |

|------------------|-------------------------------------------------------------------------------|-------------|-----|------|

| VIL              | Input Low Voltage                                                             | _           | 0.8 | V    |

| VIH              | Input High Voltage                                                            | 2.4         | _   | V    |

| VOL              | Output Low Voltage (STx Pin, I <sub>OL</sub> = 4 mA @ 5 V V <sub>DD</sub> )   | _           | 0.5 | V    |

| VOH              | Output High Voltage (STx Pin, I <sub>OH</sub> = -4 mA @ 5 V V <sub>DD</sub> ) | 4.25        | _   | V    |

| ΙL               | Input Low Current (DGND $\leq V_{in} \leq V_{DD}$ )                           | <b>– 10</b> | 10  | μΑ   |

| lн               | Input High Current (DGND $\leq V_{in} \leq V_{DD}$ )                          | <b>– 10</b> | 10  | μΑ   |

| loz              | Output Current in High Impedance State (DGND ≤ STx0,1 ≤ V <sub>DD</sub> )     | <b>– 10</b> | 10  | μΑ   |

| C <sub>in</sub>  | Input Capacitance of Digital Pins                                             | _           | 10  | pF   |

| C <sub>out</sub> | Output Capacitance of STx0 and STx1 Pin when High–Z                           | _           | 10  | pF   |

ANALOG ELECTRICAL CHARACTERISTICS (AV $_{DD}$  = 4.75 to 5.25 V, AGND = 0 V,  $T_A$  = - 40 to 85°C)

| Characteristics                                                                                  |                                              | Min                        | Тур             | Max                        | Unit    |

|--------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|----------------------------|---------|

| Differential Mode Input Resistance                                                               |                                              | _                          | 65              | _                          | kΩ      |

| Input Current                                                                                    | Al+, Al-                                     | - 10                       | _               | 10                         | μА      |

| Input Resistance to $V_{AG}$ ( $V_{AG} - 0.5 \text{ V} \le V_{in} \le V_{AG} + 0.5 \text{ V}$ )  | Al+, Al-                                     | 10                         | _               | _                          | МΩ      |

| Input Capacitance                                                                                | Al+, Al-                                     | _                          | 10              | _                          | pF      |

| Input Offset Voltage of AG Op Amp                                                                | Al+, Al-                                     | _                          | 20              | _                          | mV      |

| Input Common Mode Voltage Range                                                                  | Al+, Al-                                     | _                          | 2.5             | _                          | V       |

| Input Common Mode Rejection Ratio<br>(Input Amp Only)                                            | AI+, AI–<br>60 Hz<br>0 – 4 kHz<br>0 – 20 kHz |                            | 120<br>72<br>68 |                            | dB      |

| (Complete A/D Path)                                                                              | 60 Hz<br>0 – 4 kHz                           | _                          | 106<br>75       |                            |         |

| Gain Bandwidth Product (10 kHz) of AG Op Amp ( $R_L \ge 10 \text{ k}\Omega$                      | _                                            | 1000                       | _               | kHz                        |         |

| DC Open Loop Gain of AG Op Amp (R <sub>L</sub> ≥ 10 kΩ)                                          |                                              | _                          | 110             | _                          | dB      |

| Input Amplifier Signal to Noise + Distortion (Between Al+ and $0.2-3.4\ \mathrm{kHz})$           | AI-, 1.5 Vrms,                               | _                          | 95              | _                          | dB      |

| Output Load Capacitance for AG Op Amp                                                            | _                                            | _                          | 220             | pF                         |         |

| Output Voltage Range for AG (R <sub>L</sub> :                                                    | = 2 kΩ to V <sub>AG</sub> )                  | AGND + 1                   | _               | V <sub>DD</sub> – 1        | V       |

| Output Current (0.5 V $\leq$ V <sub>Out</sub> $\leq$ V <sub>DD</sub> $-$ 0.5 V)                  | AG+, AG–                                     | 250                        | _               | _                          | μΑ      |

| Output Load Resistance to V <sub>AG</sub>                                                        | AG+, AG–                                     | 10                         | _               | _                          | kΩ      |

| Output Current (0.5 V $\leq$ V <sub>Out</sub> $\leq$ V <sub>DD</sub> $-$ 0.5 V)                  | AO+, AO-                                     | _                          | 2               | _                          | mA      |

| Output Load Resistance to VAG                                                                    | AO+, AO-                                     | 1.0                        | 1.2             | _                          | kΩ      |

| Differential Output Impedance<br>Series Resistor Inductor @ 53 mA rms<br>from 60 Hz to 100 kHz   | AO+, AO–<br>R<br>L                           | _<br>_                     | 0.7<br>5.7      | 3<br>10                    | Ω<br>μΗ |

| Speaker Driver Output Impedance<br>Series Resistor Inductor @ 85 mA rms<br>from 60 Hz to 100 kHz | SPK+, SPK-<br>R<br>L                         | _<br>_                     | 1.75<br>6.4     | 7.0<br>12.0                | Ω<br>μΗ |

| Output Load Capacitance                                                                          | AO-                                          | _                          | _               | 0.1                        | μF      |

| Differential Output Offset Voltage of AO+ and AO-                                                |                                              |                            | _               | 20                         | mV      |

| VAG Output Voltage Referenced to AGND (No Load)                                                  |                                              | AV <sub>DD</sub> /2 – 0.07 | _               | AV <sub>DD</sub> /2 + 0.07 | V       |

| $V_{\mbox{AG}}$ Output Current with $\pm25$ mV Change in Output Voltage                          |                                              | - 44                       | _               | 44                         | mA      |

| Power Supply Rejection Ratio<br>(2 kHz @0.1 Vrms Applied to V <sub>DD</sub> )                    | A/D<br>D/A                                   | 40<br>40                   | _               |                            | dB      |

#### **ANALOG TRANSMISSION PERFORMANCE**

(V<sub>DD</sub> = 4.75 to 5.25 V, All Analog Signals Referenced to V<sub>AG</sub>, 0.775 Vrms = 0 dBm into 600  $\Omega$ , FS = 8 kHz, Measurement Band = 200 to 0.425 \* FS, T<sub>A</sub> = - 40 to 85°C, Unless Otherwise Noted)

|                                                                                       |                                                                                                                              | A/D                      |                                        |                          | D/A                            |                                                  |                              |       |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------|--------------------------|--------------------------------|--------------------------------------------------|------------------------------|-------|

| Characteristics                                                                       |                                                                                                                              | Min                      | Тур                                    | Max                      | Min                            | Тур                                              | Max                          | Unit  |

| Dynamic Range                                                                         |                                                                                                                              |                          | 78                                     | _                        | _                              | 80                                               | _                            | dB    |

| Absolute Gain (– 3 dBm0 @ 1 kHz, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 5.0 V)      |                                                                                                                              |                          | 1.8                                    | 2.3                      | 9.4                            | 9.55                                             | 9.7                          | dB    |

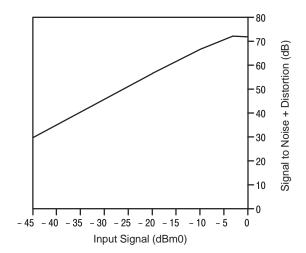

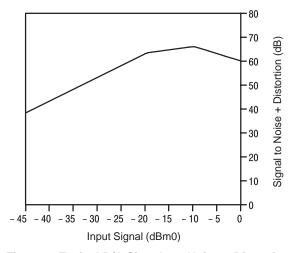

| Signal to Noise + Distortion<br>(See Figures 1 and 2)                                 | - 3 dBm0<br>- 10 dBm0<br>- 20 dBm0                                                                                           | 69<br>63.5<br>53         | 72<br>67<br>57                         | _<br>_<br>_<br>_         | 55.5<br>63<br>60               | 58<br>66<br>63                                   | _<br>_<br>_                  | dB    |

| Idle Channel Noise (dBrn0)                                                            |                                                                                                                              | _                        | 18                                     | _                        | _                              | 22                                               | _                            | dBrn0 |

| Frequency Response (Relative to 1 kHz @ 0 dBm0)  60 Hz 300 to 3000 Hz 3400 Hz 4000 Hz |                                                                                                                              | <br>_ 0.15<br>_ 0.20<br> | -20<br>0<br>-0.14<br>-33               | <br>0.15<br>0.12<br>- 32 | - 0.25<br>- 0.25<br>- 0.25<br> | 0<br>0<br>0<br>- 66                              | 0.25<br>0.25<br>0.25<br>62.5 | dB    |

| Absolute Delay (1600 Hz)                                                              |                                                                                                                              | _                        | 318                                    | _                        | _                              | 214                                              | _                            | μs    |

| Group Delay Referenced to 1600 Hz                                                     | 500 to 600 Hz<br>600 to 800 Hz<br>800 to 1000 Hz<br>1000 to 1600 Hz<br>1600 to 2600 Hz<br>2600 to 2800 Hz<br>2800 to 3000 Hz |                          | 96<br>46<br>2<br>0<br>22<br>189<br>290 |                          |                                | - 26<br>- 24<br>- 20<br>- 18<br>86<br>120<br>169 |                              | μѕ    |

#### **CROSSTALK**

| Characteristics                                   | Min | Тур         | Max           | Unit |

|---------------------------------------------------|-----|-------------|---------------|------|

| Intra–Channel A/D Talking; D/A Listening (Note 1) | _   | <b>- 77</b> | <b>- 69</b>   | dB   |

| Intra-Channel D/A Talking; A/D Listening (Note 2) | _   | - 70        | - 64          | dB   |

| Inter–Channel A/D Talking; D/A Listening (Note 3) | _   | - 78        | - 66.5        | dB   |

| Inter–Channel D/A Talking; A/D Listening (Note 4) | _   | - 73        | <b>- 62.5</b> | dB   |

#### NOTES:

- 1. 2 kHz, 3 dBm0 signal applied to A/D input; 600 Hz, 20 dBm0 signal applied to D/A input of same codec; 2 kHz content measure on D/A output of same codec.

- 2. 2 kHz, 3 dBm0 signal applied to D/A input; 600 Hz, 20 dBm0 signal applied to A/D input of same codec; 2 kHz content measure on A/D output of same codec.

- 3. 2 kHz, 3 dBm0 signal applied to A/D input; 600 Hz, 20 dBm0 signal applied to D/A input of opposite codec; 2 kHz content measure on D/A output of opposite codec.

- 4. 2 kHz, 3 dBm0 signal applied to D/A input; 600 Hz, 20 dBm0 signal applied to A/D input of opposite codec; 2 kHz content measure on A/D output of opposite codec.

Figure 1. Typical A/D Signal-to-Noise + Distortion

Figure 2. Typical D/A Signal-to-Noise + Distortion

**Table 1. Pin Descriptions**

| Pin No. | Pin Name            | Pin Description                                    |

|---------|---------------------|----------------------------------------------------|

| 1       | DGND2               | Digital Ground #2                                  |

| 2       | XTAL <sub>in</sub>  | Input — Crystal Oscillator Input                   |

| 3       | XTAL <sub>out</sub> | Output — Crystal Oscillator Output                 |

| 4       | DV <sub>DD</sub> 2  | Digital Positive Power Supply #2                   |

| 5       | MCLK0               | Input — Master Clock for Codec 0                   |

| 6       | MCLK1               | Input — Master Clock for Codec 1                   |

| 7       | PDI                 | Input — Power Down Input                           |

| 8       | RESET               | Input — System Reset                               |

| 9       | RSTEXT              | Output — External Reset from Power Monitor Circuit |

| 10      | SSYNC0              | Output — Serial Sync for Port 0                    |

| 11      | SCLK0               | Output — Serial Clock for Port 0                   |

| 12      | STx0                | Output — Serial Output for Port 0                  |

| 13      | SRx0                | Input — Serial Input for Port 0                    |

| 14      | DGND3               | Digital Ground #3                                  |

| 15      | DV <sub>DD</sub> 3  | Digital Positive Power Supply #3                   |

| 16      | SSYNC1              | Output — Serial Sync for Port 1                    |

| 17      | SCLK1               | Output — Serial Clock for Port 1                   |

| 18      | STx1                | Output — Serial Output for Port 1                  |

| 19      | SRx1                | Input — Serial Input for Port 1                    |

| 20      | DGND1               | Digital Ground #1                                  |

| 21      | DV <sub>DD</sub> 1  | Digital Positive Power Supply #1                   |

| 22      | SSIFM               | Input — SSI Framing Mode                           |

| 23      | SSIMS               | Input — SSI Mode Select                            |

| 24      | SSIDS               | Input — SSI Data Size                              |

| 25      | AO1+                | Output — Codec 1 Non–Inverting Analog Output       |

| 26      | AO1-                | Output — Codec 1 Inverting Analog Output           |

| 27      | AGND2               | Analog Ground #2                                   |

| 28      | AV <sub>DD</sub> 2  | Analog Positive Power Supply #2                    |

| 29      | AG1+                | Output — Codec 1 Input Op Amp Non–Inverting Output |

| 30      | AI1-                | Input — Codec 1 Input Op Amp Inverting Input       |

| 31      | Al1+                | Input — Codec 1 Input Op Amp Non-Inverting Input   |

| 32      | AG1–                | Output — Codec 1 Input Op Amp Inverting Output     |

| 33      | VAG                 | Output — Analog Ground Voltage                     |

| 34      | V <sub>AG</sub> REF | Output — Analog Ground Reference                   |

| 35      | SPK-                | Output — Speaker Driver Inverting                  |

| 36      | SPK+                | Output — Speaker Driver Non–Inverting              |

| 37      | AG0–                | Output — Codec 0 Input Op Amp Inverting Output     |

| 38      | AI0+                | Input — Codec 0 Input Op Amp Non-Inverting Input   |

| 39      | AIO-                | Input — Codec 0 Input Op Amp Inverting Input       |

| 40      | AG0+                | Output — Codec 0 Input Op Amp Non–Inverting Output |

|         |                     |                                                    |

Continued on next page

Table 1. Pin Descriptions (continued)

| Pin No. | Pin Name           | Pin Description                              |

|---------|--------------------|----------------------------------------------|

| 41      | AV <sub>DD</sub> 1 | Analog Positive Power Supply #1              |

| 42      | AGND1              | Analog Ground #1                             |

| 43      | AO0-               | Output — Codec 0 Inverting Analog Output     |

| 44      | AO0+               | Output — Codec 0 Non-Inverting Analog Output |

#### PIN DESCRIPTIONS

#### **ANALOG POWER SUPPLY**

#### VAGREF Analog Ground Reference (Pin 34)

This pin is used to capacitively bypass the on–chip circuitry that generates the mid–supply voltage for the VAG output pin. This pin should be bypassed to AGND with a 0.01  $\mu F$  and 10  $\mu F$  capacitor using short, low inductance traces. The VAGREF pin is only used for generating the reference voltage for the VAG pin. This pin can be overridden by an external voltage source, such as a resistor divider, using two 2K resistors. No more than 100 na should be required to override this circuit. All analog signal processing within this device is referenced to the VAG pin. If the audio signals to be processed are referenced to AGND, then special precautions must be utilized to avoid noise between AGND and the VAG pin (such as adding coupling capacitors). When this device is in power–down mode, the VAGREF pin is pulled to the AVDD power supply with a non–linear, high–impedance circuit.

#### VAG Analog Common Mode Voltage (Pin 33)

This output pin provides a mid–supply analog ground. This pin should be decoupled to AGND with a 0.01  $\mu\text{F}$  ceramic capacitor. All analog signal processing within this device is referenced to this pin. If the audio signals to be processed are referenced to AGND, then special precautions must be utilized to avoid noise between AGND and the VAG pin. The VAG pin becomes high impedance when this device is in power–down mode.

#### AGND1 and AGND2 Analog Ground Pad (Pins 42 and 27, Respectively)

These pins provide the ground reference for the internal analog circuitry.

#### AV<sub>DD</sub>1 and AV<sub>DD</sub>2 Analog Supply Pad (Pins 41 and 28, Respectively)

These pins are the positive power supplies for the analog circuitry and are internally tied together.

#### **DIGITAL POWER SUPPLY**

## DGND1, DGND2, and DGND3 Digital Ground Pad (Pins 20, 1, and 14, Respectively)

These pins provide the ground reference for the internal digital circuitry.

#### DV<sub>DD</sub>1, DV<sub>DD</sub>2, and DV<sub>DD</sub>3 Digital Supply Pad (Pins 21, 4, and 15, Respectively)

These pins are the positive power supplies for the digital circuitry and are internally tied together.

#### **CONFIGURATION INPUTS**

#### SSIMS

#### Mode Select (Pin 23)

This pin selects whether the chip is operating in Dual SSI, logic 0, or in Single SSI, logic 1. In dual mode, each codec is operated from independent serial interfaces. The timing of each interface is dictated by the associated codec timing. In single serial mode, the timing of the interface is derived from the timing of the faster of the two codecs. The faster codec is defined by bit SSI\_SEL in control register 4.

#### SSIDS

#### SSI Data Size (Pin 24)

When this pin is logic 0, the 24—bit word length of the SSI is enabled. When it is logic 1, the serial data format is adjusted to accommodate 16—bit word length.

#### **SSIFM**

#### SSI Framing Mode (Pin 22)

When this pin is logic 0, Short Frame mode is selected. This is defined as a 1-bit-wide clock pulse occurring before the first bit (MSB) of the data stream. When the pin is logic 1, Long Frame mode is selected. In long framing, the pulse rises simultaneously with the first data bit (MSB) and falls after the last data bit (LSB) has been shifted out.

#### SPEAKER INTERFACE

#### SPK+ and SPK-

## Speaker Positive and Negative Signal Outputs (Pins 36 and 35, Respectively)

These pins are the outputs of the speaker driver and can deliver 15 mW of power into a small 32  $\Omega$  speaker. The external speaker can be dc–coupled to the SPK+ and SPK– pins.

#### **CODEC INTERFACE**

#### Al0+, Al1+, Al0-, and Al1-Analog Inputs for Codec 0 and Codec 1 (Pins 38, 31, 39, and 30, Respectively)

These pins are the non–inverting and inverting inputs of the analog input gain setting amplifier. This fully–differential amplifier is the first stage of the A/D modulator portion of the codec. A low to moderate gain (up to 20 dB) can be obtained from this amplifier using external components. There is an internal 2 pF feedback capacitor to provide high frequency roll–off above 500 kHz.

AG0+, AG1+, AG0-, and AG1-Outputs of Input Amplifier for Codec 0 and Codec 1 (Pins 40, 29, 37, and 32, Respectively)

These pins are the differential outputs of the input gain setting amplifiers.

AO0+, AO1+, AO0-, and AO1-Analog Outputs for Codec 0 and Codec 1 (Pins 44 ,25, 43, and 26, Respectively)

These pins are the non–inverting and inverting outputs of the analog output amplifier. This unity gain line driver represents the final stage of the D/A section of the codec. This amplifier provides a differential output that can be dc–coupled with a hybrid circuit and is able to drive a telephone line.

#### SSI PORT 0 and PORT 1

#### SCLK0 and SCLK1

## Serial Port 0 and Serial Port 1 Clock Signal Output Pins (Pins 11 and 17, Respectively)

These pins are the timing reference for the transmission of data through the STx and SRx pins. Data transfer can only happen if the synchronization frame begins.

#### SSYNC0 and SSYNC1

## Serial Port 0 and Serial Port 1 Sync Signal Output Pins (Pins 10 and 16, Respectively)

These pins output the synchronization frame. The sync signal defines the beginning of each word transmitted through the STx and SRx pins.

#### STx0 and STx1 Serial Port 0 and Serial Port 1 Output Pins (Pins 12 and 18, Respectively)

These pins are used to transmit data from serial ports 0 and 1. Serial transmission data is shifted on the rising edge of the serial clock (SCLK).

#### SRx0 and SRx1 Serial Port 0 and Serial Port 1 Input Pins (Pins 13 and 19, Respectively)

These pins are used to receive data from serial ports 0 and 1. Serial receive data is sampled internally on the falling edge of the serial clock.

#### **RESET**

#### RESET

#### System Reset Input (Pin 8)

This pin is used to force a hardware reset of the MC143416. Note: This is ineffective when the device is in general power down.

#### **RSTEXT**

## External Reset Output to Board Functions from Power Monitor (Pin 9)

The MC143416 provides a voltage level sensing circuit which generates an active low external reset when the power

supply voltage drops below a nominal 4.5 V. The power on reset (POR) does not reset the internal circuitry, but provides an external reset signal for board use. The minimum duration of the external reset is 140 ms.

#### **CLOCKING**

# XTAL<sub>in</sub>, XTAL<sub>out</sub> Crystal Oscillator Input and Output (Pins 2 and 3, Respectively)

These pins form a reference oscillator when connected to terminals of an external parallel–resonant crystal. The internal logic clock timing (system clock) is always derived from the XTALin clock signal. The timing for the codecs can be derived from either the XTALin signal, or from the MCLK input.

Frequency–setting capacitors of appropriate values, as recommended by the crystal supplier, are connected from each pin to ground. The MC143416 has an inverter between XTALin and XTALout. An external resistor below 5 M is required between these two pins to define the trip point. A resistor of around 910 K has been found to be the best value for startup operation. This resistor value will result in a startup time of around 400 ms. Lower values will provide quicker startup times, but the XTALout amplitude will diminish as the resistor size goes down.

During power–down conditions, XTAL<sub>out</sub> is placed in a high–impedance state, and XTAL<sub>in</sub> is internally disconnected, so the device needs to be powered up in order to allow the input of external signals or crystal usage.

During normal operation, an external signal can be applied to XTAL<sub>in</sub>, instead of a crystal. It should be noted that the phase of this signal and the internal signal (derived from XTAL<sub>in</sub>) are inverted.

The drive capability of XTAL<sub>Out</sub> is somewhat small, so it will be harder to start up the oscillation if the external resistor is too large (> 5  $M\Omega$ ). The crystal value and/or external clock signal should be kept below 30 MHz.

# MCLK0 and MCLK1 Master Clock Inputs for Codec 0 and Codec 1 (Pins 5 and 6, Respectively)

These pins are the master clock inputs for the codecs when the timing is not derived from the crystal. The master clock is equal to the oversampling clock.

#### **PDI**

#### Absolute Power–Down Input (Pin 7)

This pin turns off any activity in the MC143416 except the power monitor function by stopping the oscillator. After any assertion of the PDI pin, a 10 ms period is required to resume functional operation. This time constraint is needed for the crystal oscillator to start up and stabilize to its defined operating point. It is mandatory to apply a hardware reset after this oscillator startup phase. Alternatively, a software reset can be applied after this startup phase and after making sure the serial interface framing logic has synced up to the host control/data frame.

#### **FUNCTIONAL DESCRIPTION**

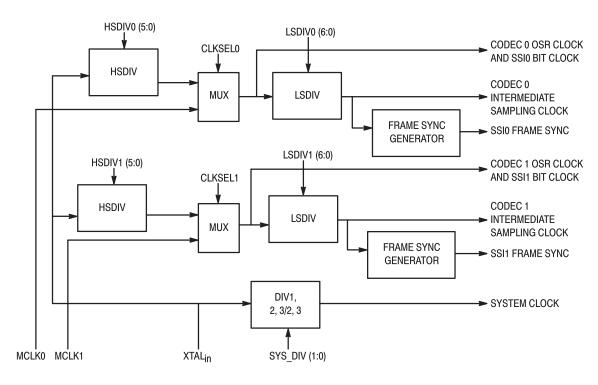

#### **CLOCK GENERATION**

#### Introduction

The clock generation block generates all timing signals necessary for the operation of the device from a crystal input or alternatively from the oversampling clock (OSR CLK) supplied through the MCLK input. The selection between these two modes is controlled by the MCLK SEL register.

The clock generation block generates the oversampling clocks, the intermediate sampling clock (for internal use), and the clocking signals for the SSI ports. The ratio of the oversampling clock to the sampling clock defines the decimation/interpolation rate. When the MCLK input is used, this clock is the OSR clock. The bit clock for the Synchronous Serial Interfaces (SSIs) is equal to the oversampling clock frequency (fOSR).

Note that the MCLK and XTAL<sub>in</sub> frequency need to be integer multiples of the codecs' sampling rates.

#### **Oversampling Clock Selection**

The practical maximum and minimum oversampling ratio at which the device will operate is determined by the hardware implementation. At all times, the following conditions need to be met for proper operation:

- Second order sigma—delta modulation is performed and the oversampling ratio has to be kept in the range of 102 to 254 (LSDIV values 51 to 127).

- · Oversampling frequency is limited to 4 MHz.

- The ratio of the oversampling clock to the system clock should be greater than or equal to 7 when the oversampling clock is derived from the crystal input, and

- greater than or equal to 8 when derived from the MCLK input.

- The system clock should provide a minimum of 580 cycles per sampling period per codec. For example, the Fmin value of two codecs running at 8 ks/s would be:

The maximum crystal frequency and operating system clock frequency is 30 MHz.

#### **Clock Generation and Divide Ratios**

The functional block diagram is shown in Figure 3.

**HSDIV and LSDIV Ratios.** The clock generation block contains separate programmable divisors for each codec. The relationship of XTAL<sub>in</sub> frequency, the dividers, and the sampling frequency (FS) is:

where HSDIV = 7, 8, ..., 63 (default 16), and LSDIV = 51, ..., 127 (default 51).

When the signal is a MCLK input only, the LSDIV value applies; the HSDIV setting is a don't care. Higher settings will positively impact (reduce) power consumption.

Tables 2 through 5 provide examples of the divisor values to derive the OSR and FS from several different crystal values

**System Divide Ratios.** The system clock frequency has to be set to a minimum of seven times the oversampling frequency of the codec running the maximum OSR. This is accomplished when clocking is derived from the crystal when the HSDIV0 and HSDIV1 values are set to 7 or more. When clocking is derived from MCLK0 and/or MCLK1, a minimum ratio of 8 has to be guaranteed between any MCLK and the XTALin frequency.

Figure 3. Block Diagram of the Clock Generation Scheme

Table 2. Suggested Sample Rate Table with a 28.224 MHz Crystal

| FS (Hz) | LSDIV | HSDIV | OSR = 2X LSDIV | FOSR (MHz) |

|---------|-------|-------|----------------|------------|

| 8000    | 126   | 14    | 252            | 2.016      |

| 9600    | 105   | 14    | 210            | 2.016      |

| 11025   | 80    | 16    | 160            | 1.764      |

| 12000   | 98    | 12    | 196            | 2.352      |

| 16000   | 126   | 7     | 252            | 4.032      |

Table 3. Suggested Sample Rate Table with a 24.192 MHz Crystal

| FS (Hz) | LSDIV | HSDIV | OSR = 2X LSDIV | FOSR (MHz) |

|---------|-------|-------|----------------|------------|

| 7200    | 120   | 14    | 240            | 1.728      |

| 8000    | 126   | 12    | 252            | 2.016      |

| 8229*   | 105   | 14    | 210            | 1.728      |

| 8400    | 120   | 12    | 240            | 2.016      |

| 9000    | 112   | 12    | 224            | 2.016      |

| 9600    | 126   | 10    | 252            | 2.4192     |

| 10287*  | 98    | 12    | 196            | 2.016      |

| 12000   | 126   | 8     | 252            | 3.024      |

| 14400   | 120   | 7     | 240            | 3.456      |

| 16000   | 108   | 7     | 216            | 3.456      |

<sup>\*</sup> Values rounded

Table 4. Suggested Sample Rate Table with a 21.504 MHz Crystal

| FS (Hz) | LSDIV                                   | HSDIV | OSR = 2X LSDIV | FOSR (MHz) |  |

|---------|-----------------------------------------|-------|----------------|------------|--|

| 8000    | 112                                     | 12    | 224            | 1.792      |  |

| 9600    | 112                                     | 10    | 224            | 2.104      |  |

| 11025   | Integer Ratio From Crystal Not Possible |       |                |            |  |

| 12000   | 64                                      | 14    | 128            | 1.536      |  |

| 16000   | 96                                      | 7     | 192            | 3.072      |  |

Table 5. Suggested Sample Rate Table with a 20.16 MHz Crystal

| FS (Hz) | LSDIV | HSDIV                | OSR = 2X LSDIV       | FOSR (MHz) |

|---------|-------|----------------------|----------------------|------------|

| 7200    | 100   | 14                   | 200                  | 1.44       |

| 8000    | 126   | 10                   | 252                  | 2.016      |

| 8229*   |       | Integer Ratio From 0 | Crystal Not Possible |            |

| 8400    | 120   | 10                   | 240                  | 2.016      |

| 9000    | 112   | 10                   | 224                  | 2.016      |

| 9600    | 105   | 10                   | 210                  | 2.016      |

| 10287*  | 98    | 10                   | 196                  | 2.016      |

| 12000   | 120   | 7                    | 240                  | 2.88       |

| 14400   | 100   | 7                    | 200                  | 2.88       |

| 16000   | 90    | 7                    | 180                  | 2.88       |

<sup>\*</sup> Values rounded

#### **NOTES FOR TABLES 2 THROUGH 5:**

- 1. FS desired sample rate.

- 2. LSDIV and HSDIV are the values loaded into the control registers in decimal format.

- 3. Values shown try to maximize oversampling rate.

#### **REGISTER PROGRAMMING**

#### REGISTER PROGRAMMING MODEL

Table 6 is the register map of the MC143416's control and status registers. Registers labeled with a 0 suffix are associated with SSI Port 0, and those with a 1 suffix are associated with SSI Port 1. For example, register CNTL0\_0 is associated with SSI Port 0, and CNTL0\_1 is associated with SSI Port 1.

#### **CONTROL AND STATUS REGISTERS**

The MC143416 provides ten 8-bit control/status registers that are available to use. The MSB of all these registers is always 0 as a safety feature against desynchronization (address/data swap). Each register is doubled to serve one associated codec, with the exception of register CNTL4, CNTL5, CNTL6, and CNTL7, which carry global chip controls. These registers are accessible by either SSI port.

In the following paragraphs, the contents of each register are discussed in detail. In the description of each individual bit, two parameters are included: access and reset value. Access indicates whether the bit is read only, write only, or both; reset value indicates the value upon reset. All register bits are static except SWRESET in CNTL4.

#### CNTL0\_0: Power Control Register — Codec 0

**ANARSVD0 (R/W, 0):** This bit is reserved for future use and must be kept 0.

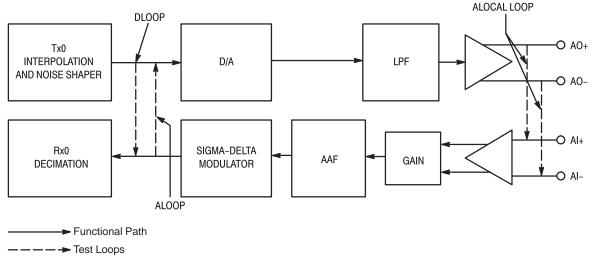

**ALOOP (R/W, 0):** This bit controls the remote loopback function at the analog/digital interface. Setting this bit to 1 will force the single bit modulated output from Rx in the codec to loopback into the single bit input of the D/A. See Figure 4.

**DLOOP (R/W, 0):** Setting this bit to 1 will force a digital loopback in the codec. This occurs at a point between the output of digital interpolator filter and the input of the digital decimator filter. See Figure 4.

**RST (R/W, 1):** Setting this bit to 1 will force a value of 0x00 to all digital processing stages.

**PWDN (R/W, 1):** Setting this bit to 1 will disable all data processing for this codec and power down the associated analog circuitry.

**TxEN (R/W, 0):** Setting this bit to 1 will enable the transmitter on the codec. The transmitter is a differential mode power stage. When disabled, the amplifier maintains a zero differential output voltage (AOO+ = AOO- = VAG).

**ALOCAL LOOP (R/W, 0):** As opposed to the ALOOP bit of this register, ALOCAL LOOP closes a local loopback at the analog interface. When this bit is set active (1), the analog output signal on pins AOO+ and AOO- is fed back into the input amplifier stage on pins AIO+ and AIO-. See Figure 4.

Table 6. Register Map

| Register | Addr | 7 | 6                                           | 5                     | 4       | 3     | 2        | 1     | 0              | Mode |

|----------|------|---|---------------------------------------------|-----------------------|---------|-------|----------|-------|----------------|------|

| CNTL0_0  | 0x0  | 0 | ANARSVD0                                    | ALOOP0                | DLOOP0  | PWDN0 | RST0     | TxEN0 | ALOCAL<br>LOOP | R/W  |

| CNTL0_1  | 0x1  | 0 | ANARSVD1                                    | ALOOP1                | DLOOP1  | PWDN1 | RST1     | TxEN1 | ALOCAL<br>LOOP | R/W  |

| CNTL1_0  | 0x2  | 0 | HPF_EN0                                     | IN_GAI                | N0(1:0) | SPK_R | Rx0(1:0) | SPK_T | x0(1:0)        | R/W  |

| CNTL1_1  | 0x3  | 0 | HPF_EN1                                     | IN_GAI                | N1(1:0) | SPK_R | Rx1(1:0) | SPK_T | x1(1:0)        | R/W  |

| CNTL2_0  | 0x4  | 0 | MCLK0_SEL                                   |                       |         | HSDI  | V0(5:0)  |       |                | R/W  |

| CNTL2_1  | 0x5  | 0 | MCLK1_SEL                                   | MCLK1_SEL HSDIV1(5:0) |         |       |          |       | R/W            |      |

| CNTL3_0  | 0x6  | 0 |                                             | LSDIV0(6:0)           |         |       |          | R/W   |                |      |

| CNTL3_1  | 0x7  | 0 |                                             | LSDIV1(6:0)           |         |       |          | R/W   |                |      |

| CNTL4    | 0x8  | 0 |                                             |                       | SWRESET | RSVD  | SSI_SEL  | SYS_D | IV(1:0)        | R/W  |

| CNTL5    | 0x9  | 0 | SELF_CHECK (2:0)                            |                       |         |       | RO       |       |                |      |

|          |      |   | TEST_RSVD (1:0) SERIAL TEST_MODE (1:0) LOOP |                       |         | WO    |          |       |                |      |

| CNTL6    |      | 0 |                                             |                       |         |       |          | wo    |                |      |

|          |      |   |                                             | RSVD (5:0)            |         |       |          |       | RO             |      |

| CNTL7    |      | 0 |                                             |                       |         |       | wo       |       |                |      |

|          |      |   | RSVD (6:0)                                  |                       |         |       | RO       |       |                |      |

| SYNC     | 0xF  | 0 | SEE DESCRIPTION F                           |                       |         |       | R/W      |       |                |      |

Figure 4. Digital and Analog Loopback Features

#### CNTL0\_1: Power Control Register — Codec 1

For Codec 1, refer to **Power Control Register** — **Codec 0**. The power control register address for Codec 1 is 0x1. Pins AO0+, AO0-, AI0+, and AI0- for Codec 0 correspond to pins AO1+, AO1-, AI1+, and AI1- for Codec 1, respectively.

## CNTL1\_0: Speaker Mixer Control and Other Analog Control — Codec 0

HPF\_EN (R/W, 0): This bit can be set to 1 when the codec is processing voice data. It is used to perform an additional high–pass filtering step on the voice D/A path to remove frequencies below 0.005 \* FS. (40 Hz @ 8 kHz, 60 Hz @ 12 kHz, etc.)

IN\_GAIN (1:0) (R/W, 0x0): These bits define a software controlled gain on the input amplifier to the codec as defined in Table 7.

**Table 7. Input Signal Gain Control**

| IN_GAIN (1:0) | Signal Gain |

|---------------|-------------|

| 00            | 0 dB        |

| 01            | 12 dB       |

| 10            | 24 dB       |

| 11            | 36 dB       |

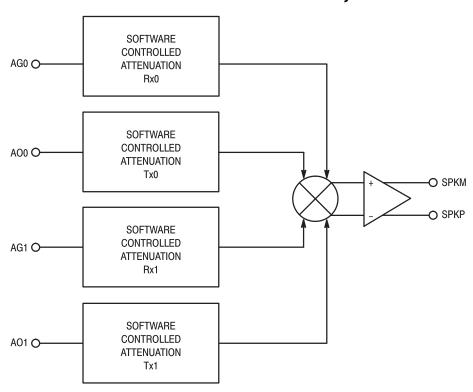

SPK\_Rx (1:0) and SPK\_Tx (1:0) (R/W, 0x0): These register bits provide control to the analog mixer. The mixer combines four separate signal sources (AG0+, AO0+, AG1+, and AO1+, which correspond to Rx0, Tx0, Rx1, and Tx1) and provides a selection of four different amplification levels. The combined and amplified signal is then fed into the speaker driver. Two of these signal sources are from Codec 0 and the other two are from Codec 1. The signal source from the output amplifier is unaffected when the speaker driver amplifier is turned off or by the settings of these control bits.

See the **Speaker Driver and Mixer** section for more detail.

Each of the four channels (Rx0, Tx0, Rx1, and Tx1) can provide one of the four attenuation levels to the signals that source the analog mixer. Table 8 defines the levels for a given channel.

**Table 8. Multiplexed Signal Gain Control**

| SPK_Rx (1:0), | Ga  | ain | Effect on the Signal |        |  |

|---------------|-----|-----|----------------------|--------|--|

| SPK_Tx (1:0)  | Rx  | Tx  | Rx                   | Tx     |  |

| 00            | 0   | 0   | Disconnected         |        |  |

| 01            | 1.5 | 0.5 | 3.5 dB               | – 6 dB |  |

| 10            | 3   | 1   | 9.5 dB               | 0 dB   |  |

| 11            | 6   | 2   | 15.6 dB              | + 6 dB |  |

Note that it is possible to process more than one channel at the same time; this feature provides some flexibility to the user. Setting the amplification level of all the channels to zero (0x0), has the effect of powering down the speaker driver/multiplexer.

## CNTL1\_1: Speaker Mixer Control and Other Analog Control — Codec 1

For Codec 1, refer to **Speaker Mixer Control and Other Analog Control** — **Codec 0**. The speaker mixer control and other analog control register address for Codec 1 is 0x3. Pins Al0+, Al0-, AG0+, and AG0- for Codec 0 correspond to pins Al1+, Al1-, AG1+, and AG1- for Codec 1, respectively.

## CNTL2\_0: OSR Clock Generation Control Register — Codec 0

**HSDIV** (5:0) (R/W, 0x10): This field is used to program the crystal frequency divide value that will determine the frequency of the oversampling converters. The reset value of this register is 0x10 (16 decimal). See **Clock Generation** for a detailed description of the generation of clocks inside this device.

MCLK0\_SEL (WO, 0): When set to 0, the clock generation block is sourced by the signal applied to XTALin. When set to 1, the source of the clocking for Codec 0 is defined to be MCLK0.

## CNTL2\_1: OSR Clock Generation Control Register — Codec 1

For Codec 1, refer to **OSR Clock Generation Control Register** — **Codec 0**. The OSR clock generation control register address for Codec 1 is 0x5. MCLK0 for Codec 0 corresponds to MCLK1 for Codec 1.

## CNTL3\_0: Sampling Clock Generation Control Register — Codec 0

**LSDIV** (6:0) (R/W, 0x33): This field is used to program the sampling clock divide value. See **Clock Generation** for a detailed description of the generation of clocks inside this device. The reset value of 0x33 (decimal = 51 = 0.5 min OSR) is the minimum value for this register. Any attempt to write a lower value will result in writing 0x33.

## CNTL3\_1: Sampling Clock Generation Control Register — Codec 1

For Codec 1, refer to **Sampling Clock Generation Control Register** — **Codec 0**. The sampling clock generation control register address for Codec 1 is 0x7.

#### **CNTL4: Control Register 4**

**SWRESET (WO, 1):** When set to 1 this bit has the same effect as a hardware reset to be applied to the chip. All control, data, and internal registers are reset, including the serial port. This bit auto resets to zero to restore functional operation.

**SSI\_SEL (WO, 0):** This bit is used to select the timing generation path for the SSI port when running a single SSI supporting two codecs. This bit is ignored when running in dual SSI mode(SSIMS = 0). Value 0 selects timing from Codec 0, while value 1 selects timing from Codec 1. The codec running the highest rate must be selected as the SSI timing driver to guarantee enough bandwidth for data sampling.

SYS\_DIV (1:0) (WO, 0x2): These bits control the operating frequency of the system clock through a programmable clock divider. The operating frequency has to be set to a minimum of eight times the oversampling frequency of the codec running the maximum OSR. The reset value for SYS\_DIV is 0x2, which results in a system clock divider of 2. Refer to Clock Generation for a more detailed description.

Table 9. System Clock Divider Setting

| SYS_DIV (1:0) | Divide Ratio |

|---------------|--------------|

| 00            | 1            |

| 01            | 3/2          |

| 10            | 2            |

| 11            | 3            |

#### **CNTL5: Control Register 5**

This register is primarily reserved for test purposes and should be left to its reset value, with the exception of the serial loop bit.

**SELF\_CHECK (2:0) (RO, 0):** This field returns the results of a self test which occurs 1 ms after a hardware or software reset. Any bit other than zero indicates a failure has been detected.

**TEST\_MODE (1:0) (WO, 0):** This bit is reserved for the test and should be kept at 0 for functional operation.

**SerialLoop (WO, 0):** When set to 1, this bit enables a serial loop mode. In this mode, data samples received from the serial port are retransmitted back to the serial output after a processing delay. Control and register data behavior is unchanged.

#### **CNTL6: Control Register 6**

This register is reserved and the reset value should not be changed.

#### **CNTL7: Control Register 7**

This register is reserved and the reset value should not be changed.

#### SYNC: Control Register F

This register is not a functional register in the sense that it is only used to guarantee/verify the framing on the serial interface. This is a mandatory requirement when running in single serial mode to make sure that control/data and sample frames are processed as such. For a more detailed description on the use of this register see **Synchronization of the Serial Ports**.

Requests for synchronization are identified as reads or writes performed to this register. This allows the internal framing hardware to "lock" on to the bit stream sent by the bost

A read to this register returns the value 0x55 when the internal state machine is synchronized to the incoming stream. It returns either 0x00 or indeterminate if the internal hardware is not properly aligned to the incoming data. The write value is ignored.

#### **SERIAL TIMING DESCRIPTION**

#### **Synchronous Serial Interface Ports**

Digital data and control information is transmitted and received through the Synchronous Serial Interface (SSI) ports. The ports and their modes of operation can be configured by hardware pins and software controls. This offers greater flexibility to accommodate different hosts, data formats, and data lengths (size).

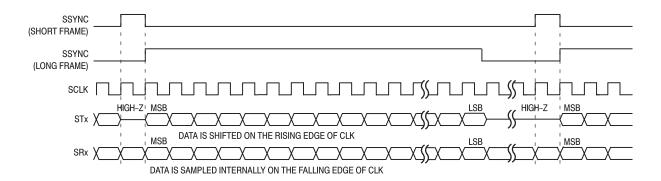

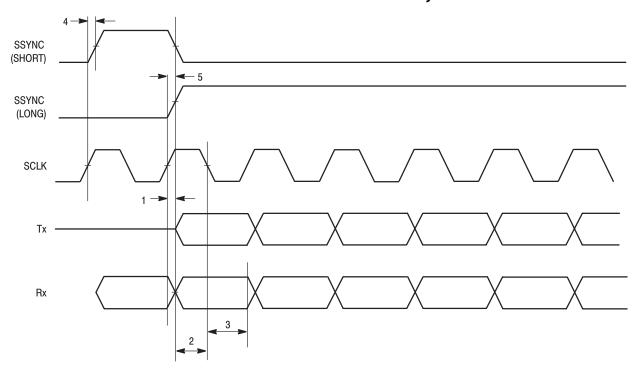

The MC143416 uses two synchronous serial interfaces. These interfaces consist of four pins each: SCLK, STx, SRx, and SSYNC. The timing relationship of these pins can be seen in Figure 5. The output serial data is registered on the rising edge of SCLK so that each input bit can be sampled on the falling edge of SCLK. The SSIs can be operated in 24-bit or 16-bit, Dual SSI or Single SSI, long frame or short frame. The primary difference between these modes is the number of frames per sampling period and the organization of the words. The serial ports can be configured through three independent pins: SSIDS (data size), SSIFM (framing mode), and SSIMS (mode select). These pins need to be permanently tied to either DGND or DVDD. The pins are global controls applied on both serial ports according to Table 10.

**Table 10. SSI Configuration Pins**

| Pin                              | Level | Configuration                                                                                                                                                                            |

|----------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSIDS                            | 0     | 24 Bits per Frame                                                                                                                                                                        |

|                                  | 1     | 16 Bits per Frame                                                                                                                                                                        |

| SSIMS                            | 0     | Dual Serial Mode: Each codec is operated from an independent serial interface. The timing of each interface is dictated by the associated codec timing.                                  |

| timing of SSI0 the faster of the |       | Single Serial Mode: Utilizes only SSI0. The timing of SSI0 is derived from the timing of the faster of the two codecs. The faster codec is defined by bit SSI_SEL in control register 4. |

| SSIFM 0                          |       | Short Frame Mode                                                                                                                                                                         |

| 1                                |       | Long Frame Mode                                                                                                                                                                          |

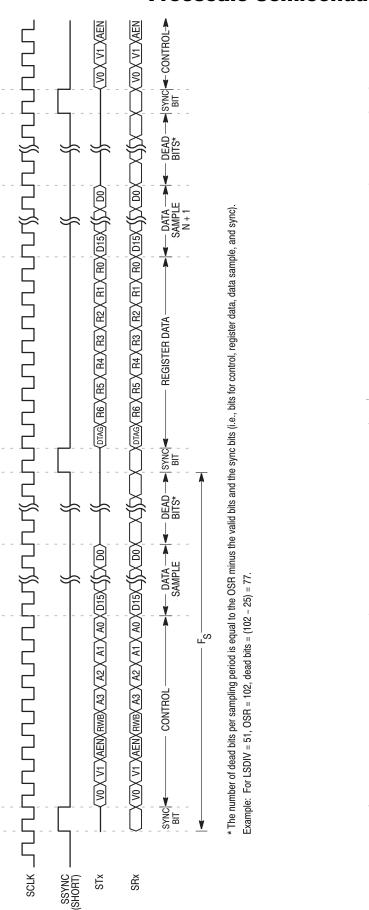

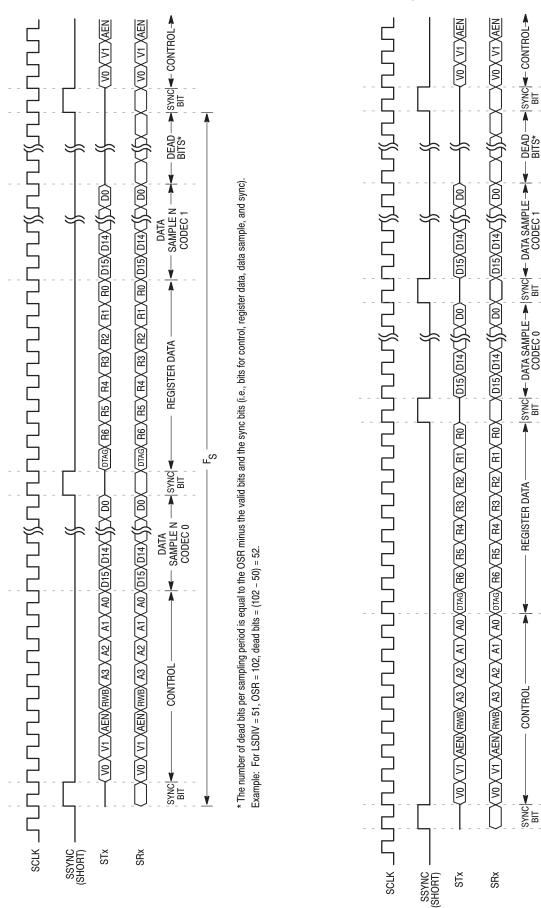

Data Size — 16-Bit Mode and 24-Bit Mode: The data size can be selected by the state of the pin SSIDS. When the pin is tied low, the 24-bit data format is effective. In 24-bit operation, the control data and register data (bits 23:16) alternately precede the data sample (bits 15:0) in each frame. See Figures 6 and 8. When this pin is set high, the serial data format is adjusted to accommodate 16-bit data. In 16-bit operation, the control data and register data are coupled into one frame, and the data sample is contained in a separate frame. See Figures 7 and 9. The ordering of the data words depends on whether the device is in Dual or Single SSI

Data Mode — Dual SSI Mode and Single SSI Mode: The SSIMS pin is used to select either Dual SSI mode or Single SSI mode. When SSIMS is low, the device operates in Dual SSI mode, and when SSIMS is high, the device operates in Single SSI mode. In Dual SSI mode, each codec operates through an independent serial interface (Codec 0 operates through SSIO, and Codec 1 operates through SSI1). The timing of each serial interface is directly related to the timing of its associated codec (bit clock has the same frequency as the oversampling clock). In Single SSI mode, both codecs operate from a single SSI interface (SSI0), and the serial interface timing is dictated by the faster of the two codecs. When in this mode, the SRx1 input should be tied to ground, and the SSI1 port is not functional.

Frame Mode — Long Frame Sync Mode and Short Frame Sync Mode: This device is able to generate both long and short framing signals depending on the state of the pin SSIFM. When SSIFM is low, the device operates in Short Frame mode, which is defined as a one-bit-wide clock pulse occurring before the first bit of the data stream (MSB). When SSIFM is high, the device operates in Long Frame mode. In this mode, the framing pulse rises simultaneously with the first data bit (MSB) and falls after the last data bit (LSB) has been shifted out. The different framing modes are shown in Figure 5.

Figure 5. Serial Interface Timing

#### **Serial Port Data Format**

The serial port is used to transport three classes of data — the control word, the register data, and the data sample. The control word contains eight bits that are used for register addressing, validity, and synchronization. The register data contains eight bits, one of which is a synchronization bit. The data sample is composed of sixteen bits and contains the data to and from the codec. The serial port data format varies depending on which mode the device is operating in. Diagrams of each mode can be seen in Figures 6, 7, 8, and 9.

Figure 6 describes the data format for 24—Bit Dual SSI mode. The STx channel control field of frame 'N' always echoes the control field of the SRx channel with a delay equal to the number of frames in one repetition sequence. For 24—bit dual mode, this repetition is equal to two frames, and the sampling period is one frame. A control word issued in frame 'N' will be echoed in frame 'N+2'. A data read requested through control channel at frame 'N' will therefore be available in frame 'N+3'. (Note: This only applies for 24—bit dual mode.)

Figure 7 describes the data format for 16–Bit Dual SSI mode. Note that the repetition sequence and the sampling period in this mode are equal to two frames.

Figure 8 describes the data format for 24–Bit Single SSI mode. Note that the control word and register data alternate between frames, as well as the data for Codec 0 and Codec 1. The repetition sequence and the sampling period are equal to two frames.

Figure 9 describes the data format for 16–Bit Single SSI mode data. Note that the repetition sequence and the sampling period are equal to three frames.

#### **Control Word**

The control word consists of eight bits: V0, V1, AEN, RWB, and A(3:0). Bits V0, V1, and A0 take on slightly different meanings depending upon which mode the device is operating.

Control(7) = V0: This bit indicates the validity of the data sample following the control byte. If it is set high, the subsequent data sample is valid. If it is set low, the subsequent data sample is not valid. This bit will always read 0 when Codec 0 is powered down.

Single SSI Mode: This bit is primarily intended to support Single SSI mode with codecs operating at different rates. Since the timing for the serial interface is based on the faster codec in this mode, there will be frames when the data associated with the slower codec is not valid. During these frames, this bit will be low to indicate the data is invalid.

Dual SSI Mode: In Dual SSI mode, the sample data will always be valid as the serial interface is operating at the same rate as the associated codec.

**Control(6) = V1:** This bit is used either as a synchronizing bit (Dual SSI mode) or a data validity bit for Codec 1.

Single SSI Mode: In Single SSI mode, this bit acts as a validity bit for the subsequent data sample of Codec 1. The clocking is modified to generate two frames per sampling interval (three frames in 16-bit mode) and the data from both codecs is time multiplexed onto two successive syncs as described in Figures 8 and 9. The sampling interval is defined by the rate of the faster codec. This information is provided to the chip through the SSI\_SEL bit in register CNTL4. The validity bit in the control field may take a logic 0 or logic 1 value depending on the operational rate of the associated codec.

Dual SSI Mode: In Dual SSI mode, this bit is always set to 1 as an identifier for the control byte. If read as a 0, the device will assume desynchronization and ignore the frame. See Synchronization of the Serial Ports for additional information.

**Control(5) = AEN (Access Enable):** This bit acts like a chip select. When set to logic 0, this bit prevents access to the internal control registers. Bits 0 through 4 of the control word and associated register data are ignored.

**Control(4) = RWB:** This bit indicates the access mode of the register addressed by bits A(3:0). A logic 1 indicates read, and a logic 0 indicates write.

Control(3:0) = A(3:0): This is the address of the register for which access is requested. The bit A0 (LSB) is always used in Single SSI mode and conditionally used in Dual SSI mode.

Single SSI Mode: In Single SSI mode, A0 is always valid and either codec can be accessed given the proper register address.

Dual SSI Mode: In Dual SSI mode, information related to a given codec must be transmitted or received through the associated SSI port. For example, if information related to Codec 0 is required, then it must be accessed through SSI Port 0. This means that for the codec specific registers (addresses 0x0 through 0x7), the A0 bit must a zero for Codec 0, and a one for Codec 1. The other registers are global and do not apply to a specific codec, so A0 should be used as needed to access the desired register from either serial port.

Table 11. Bit Sequence

| Mode          | Repetition Sequence                                                      | Frames per FS |

|---------------|--------------------------------------------------------------------------|---------------|

| 24-Bit Dual   | [Control, Data Sample N] [Register Data, Data Sample N+1]                | 1             |

| 16-Bit Dual   | [Control, Register Data] [Data Sample N]                                 | 2             |

| 24-Bit Single | [Control, Codec 0 Data Sample N] [Register Data, Codec 1 Data Sample N]  | 2             |

| 16–Bit Single | [Control, Register Data] [Codec 0 Data Sample N] [Codec 1 Data Sample N] | 3             |

NOTE: The [] symbols represent one frame.

→ SYNC ← CONTROL ■ DEAD-BITS\*  $\overline{\text{D15} \times \text{D14} \times \text{D13} \times \text{D12} \times \text{D11} \times \text{D10} \times \text{D9} \times \mathbb{C} \times \mathbb{C}}$ The number of dead bits per sampling period is equal to the OSR minus the valid bits and the sync bits (i.e., bits for control, register data, data sample, and sync). DATA SAMPLE N SYNC (VO) V1 XAENYRWBX A3 X A2 X A1 X A0 XOTAGY R6 X R5 X R4 X R3 X R2 X R1 X R0 X VO \ V1 \AEN\RWB\ A3 \ A2 \ A1 \ A0 \DTAG\ R6 \ R5 \ R4 \ R3 \ R2 \ R1\ R0  $^{\mathsf{T}}_{\mathcal{S}}$ REGISTER DATA SYNC| BIT SCLK \_ SSYNC (SHORT) STX SRX

For LSDIV = 51, OSR = 102, dead bits = (102 - 34) = 68.

VO X V1 XAEN

Figure 7. Dual SSI 16-Bit Format

Figure 6. Dual SSI 24-Bit Format

Figure 8. Single SSI 24-Bit Format

Figure 9. Single SSI 16-Bit Format

\* The number of dead bits per sampling period is equal to the OSR minus the valid bits and sync bits (i.e., bits for control, register data, data sample, and sync). Example: For LSDIV = 51, OSR = 102, dead bits = (102 - 51) = 51.

$^{\mathsf{T}}_{\mathcal{S}}$

| Ref. No. | Characteristics                                       | Min (ns) | Max (ns) |

|----------|-------------------------------------------------------|----------|----------|

| _        | SCLK Period                                           | 250      | _        |

| _        | SCLK Rise Time                                        | 0        | 10       |

| _        | SCLK Fall Time                                        | 0        | 10       |

| 1        | Data Valid on Tx After Rising Edge of SCLK            | 0        | 50       |

| 2        | Setup Time of Rx Before Falling Edge of SCLK          | 0        | _        |

| 3        | Hold Time of Rx After Falling Edge of SCLK            | 50       | _        |

| 4        | Data Valid on SSYNC (Short) After Rising Edge of SCLK | 0        | 50       |

| 5        | Data Valid on SSYNC (Long) After Rising Edge of SCLK  | 0        | 50       |

NOTE: Timing information based on using the XTAL input driving SYS clock and OSR clock @ 25 MHz.

Figure 10. Timing Characteristics

### **Register Data**

The MSB of the register data is called the 'DTAG' bit and must be set to logic 0 as a frame identifier. If read as a 1, the device will assume desynchronization and ignore the frame. See **Synchronization of the Serial Ports** for additional information. The remaining bits of this word are used to contain the register data.

#### Synchronization of the Serial Ports

Although serial port master, special internal hardware will slave the MC143416 framing sequence to the host processor incoming stream of data based on the known value of bits V1 (logic 1) and DTAG (logic 0). These bits alone are not enough to guarantee correct frame identification because the register value and/or the data sample may imitate the pattern created by those bits. Moreover, in Single SSI mode, only DTAG (MSB of register data) is available. The internal state ma-

chine will shift the framing identification every time the value of the above-mentioned bits are violated, thus performing a resync on the next frame. If the sample(s) imitate the control and/or the register data in Single SSI mode, locking cannot be performed securely. To protect against false locking, the host processor should perform a minimum of two accesses to the SYNC register in Single SSI 24-bit mode and three accesses in Single SSI 16-bit mode. Typically, the host will perform two write accesses to the SYNC register, followed by a read. A read value of 0x55 indicates that the internal state machine has locked on the incoming frame and full operation can begin. The internal state machine, if "unlocked", will use the register address and AEN bit as locking information. Any value other than 0x55 read from the sync register indicates the internal state machine is not ready to perform register access. Note that once synchronized, the timing of the Rx channel (host to MC143416) is mapped onto the Tx channel (MC143416 to host).

#### **ANALOG DESCRIPTION**

#### **Codec Structure**

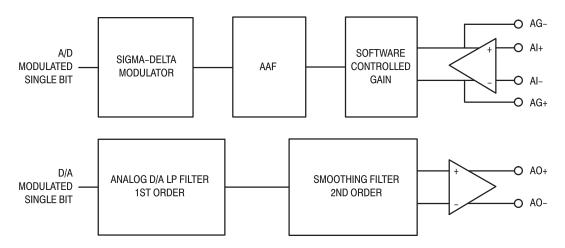

The digital–to–analog (D/A) section is independent of the analog–to–digital (A/D) modulator section although it receives the same clocking controls. There are six package pins that externally interact with each codec. The analog section of one codec is represented in Figure 11.

The D/A takes a sampling clock and a one—bit modulated stream into a switched—capacitor low—pass filter that uses a temperature stable reference in the D/A conversion. The bandwidth for this filter is:

#### $f_{3dB} = f_{OSR} / 58.74$

Then a second order lowpass Butterworth smoothing filter follows. This filter has a cutoff frequency of 64 kHz and a Q of 1.0; the overall D/A filtering is that of a third order filter. The D/A converter ends with a unity gain line driver that is able to drive the telephone line. The complete D/A path is differential, except for the output amplifier which is pseudo-differential. This amplifier could be dc-coupled to an analog modem hybrid circuit using the transmitter pair AO+ and AO- pins.

The A/D modulator has an input amplifier that can be used to complete the hybrid circuit; a low-to-moderate gain (up to 20 dB) can be obtained from this amplifier using the four receiver stage pins: Al-, Al+, AG+, and AG-. In addition, this input amplifier is used in a stage that provides four software controlled gain steps (0, 12, 24, and 36 dB). The overall amplifier is kept with a constant unity gain frequency regardless of the particular gain settings; this helps to maintain the overall amplifier bandwidth defined by the external components attached to the AI+, AI-, AG+, and AG- pins. The input stage amplifier has an internal 2 pF feedback capacitor to provide high frequency roll-off above 500 kHz. The anti-aliasing filter (AAF) is a replica of the smoothing filter of the D/A section. It is recommended that the input amplifier portion of the application be designed with a low-pass filter with a f3db of 64 kHz. This will result in an overall effect of a three-pole system. After the AAF, a second order sigma-delta modulator completes the A/D converter section. This modulator is based on a switched–capacitor approach, which uses a temperature–stable voltage reference and is able to accept a dither frequency to eliminate low frequency tone generation. The complete A/D section is fully differential.

#### **Frequency Response**

The overall bandpass width of the MC143416 is defined as 0.425 \* FS, where FS is the sampling frequency. For example, at a sample rate of 8 ks/s, the bandwidth is 0.425 \* 8000 = 3400 kHz. At 16 ks/s, the bandwidth increases to 0.425 \* 16000 = 6800 kHz.

The high–pass filter option, which is used in voice processing to reduce dc and 60 Hz levels, is actually a notch filter with a zero at 0.005 \* FS.

#### **Speaker Driver and Multiplexer**

An analog output to drive a low level speaker is provided though a four–channel mixer. Signals may come from both input (Rx) and output (Tx) paths according to Figure 12.

The output driver is able to deliver 15 mW of power into a small 32  $\Omega$  speaker for a 1.1 Vrms signal from the Tx paths (equivalent to the output level at the phone line). The circuit performs a current summation at the inputs of a differential power amplifier to emulate the action of a signal mixer. Setting the amplification level of all the channels to 0x0 has the effect of powering down the power amplifier, thus reducing software overhead.

The external speaker can be dc–coupled to the pair of pins SPK+ and SPK–, using a resistor in series to, and a bypass capacitor in parallel to, the speaker. The values of these external components are a function of the particular speaker. The capacitor is used to reduce the impedance of the speaker circuit at high frequencies one decade above the voice bandwidth. Typical values are 0.1  $\mu\text{F}.$

Note that no special hardware is included to guarantee immunity to switching noise when modifying the gain setting of the different channels.

Figure 11. Codec Structure

Figure 12. Speaker Mixer

#### LAYOUT CONSIDERATIONS

#### **Printed Circuit Board Layout Considerations**

The MC143416 is manufactured using high–speed CMOS VLSI technology to implement the complex analog signal processing functions of a PCM Codec–Filter. The fully–differential analog circuit design techniques used for this device result in superior performance for the switched capacitor filters, the analog–to–digital converter (ADC) and the digital–to–analog converter (DAC). Special attention was given to the design of this device to reduce the sensitivities of noise, including power supply rejection and susceptibility to radio frequency noise.

This device was designed for ease of implementation, but due to the large dynamic range and the noisy nature of the environment for this device (digital switches, radio telephones, DSP front—end, etc.), special care must be taken to assure optimum analog transmission performance.

#### **PC Board Mounting**

It is recommended that the device be soldered to the PC board for optimum noise performance. If the device is to be used in a socket, it should be placed in a low parasitic pin inductance (generally, low-profile) socket.

#### Power Supply, Ground, and Noise Considerations

This device is intended to be used in switching applications which often require plugging the PC board into a rack with power applied. This is known as "hot–rack insertion". In these applications, care should be taken to limit the voltage on any pin from going positive of the VDD pins, or negative of the GND pins. One method is to extend the ground and power contacts of the PCB connector. The device has input protection on all pins and may source or sink a limited amount of current without damage. Current limiting may be accomplished by series resistors between the signal pins and the connector contacts.

The most important considerations for PCB layout deal with noise. This includes noise on the power supply, noise generated by the digital circuitry on the device, and cross—coupling digital or radio frequency signals into the audio signals of this device. The best way to prevent noise is to:

- Keep digital signals as far away from audio signals as possible.

- Keep radio frequency signals as far away from the audio signals as possible.

- Use short, low inductance traces for the audio circuitry to reduce inductive, capacitive, and radio frequency noise sensitivities.

- Use short, low inductance traces for digital and RF circuitry to reduce inductive, capacitive, and radio frequency radiated noise.

- Bypass capacitors should be connected from DVDD to DGND, and VAGREF and VAG to AGND with minimal trace length. Ceramic monolithic capacitors of about 0.1  $\mu\text{F}$  are acceptable for the DVDD and VAGREF pins to decouple the device from its own noise. The DVDD capacitor helps supply the instantaneous currents of the digital circuitry in addition to decoupling the noise which may be generated by other sections of the device or other circuitry on the power supply. The VAGREF decoupling capacitor is effecting a low-pass filter to isolate the mid-supply voltage from the power supply noise generated on-chip, as well as external to the device. The VAG decoupling capacitor should be about  $0.01 \mu F$ . This helps to reduce the impedance of the V<sub>AG</sub> pin to AGND at frequencies above the bandwidth of the VAG generator, which reduces the susceptibility to RF

- Use a short, wide, low inductance trace to connect the DGND ground pin to the power supply ground. The DGND pin is the digital ground and the most negative power supply pin for the analog circuitry. All analog signal processing is referenced to the VAG pin, but because digital and RF circuitry will probably be powered by this same ground, care must be taken to minimize high frequency noise in the AGND trace. Depending on the application, a double-sided PCB with a ground plane connecting all of the digital and analog GND pins together would be a good grounding method. A multilayer PC board with a ground plane connecting all of the digital and analog GND pins together would be the optimal ground configuration. These methods will result in the lowest resistance and the lowest inductance in the ground circuit. This is important to reduce voltage spikes in the ground circuit resulting from the high-speed digital current spikes. The magnitude of digitally-induced voltage spikes may be hundreds of times larger than the analog signal the device is required to digitize.

- Use a short, wide, low inductance trace to connect the V<sub>DD</sub> power supply pin to the 5 V power supply. Depending on the application, a double—sided PCB with V<sub>DD</sub> bypass capacitors to the ground plane, as described above, may complete the low impedance coupling for the power supply. For a multilayer PC board with a power plane, connecting all of the V<sub>DD</sub> pins to the power plane would be the optimal power distribution method. The integrated circuit layout and packaging considerations for the 5 V V<sub>DD</sub> power circuit are essentially the same as for the ground circuit.

#### **APPLICATIONS**

The MC143416 is used in several Motorola modem reference design kits. More detailed documentation describing these kits is available from your local Motorola distributor or

semiconductor sales office, or through a Motorola Literature Distribution Center.

| Document Title                                                             | Order Number     |

|----------------------------------------------------------------------------|------------------|

| MC143450RDK External/Embedded Modem Reference Design Kit Product Preview   | MC143450RDKPP/D  |

| MC143450RDK External/Embedded Modem Reference Design Kit User's Manual     | MC143450RDKUM/D* |

| MC143452RDK ISA Controller–less Modem Reference Design Kit Product Preview | MC143452RDKPP/D  |

| MC143452RDK ISA Controller–less Modem Reference Design Kit User's Manual   | MC143452RDKUM/D* |

| MC143455RDK PCI Controller–less Modem Reference Design Kit Product Preview | MC143455RDKPP/D  |

| MC143455RDK PCI Controller–less Modem Reference Design Kit User's Manual   | MC143455RDKUM/D* |

<sup>\*</sup>Call the CTAS Division Service Center for details. U.S. phone 1–800–422–6323.

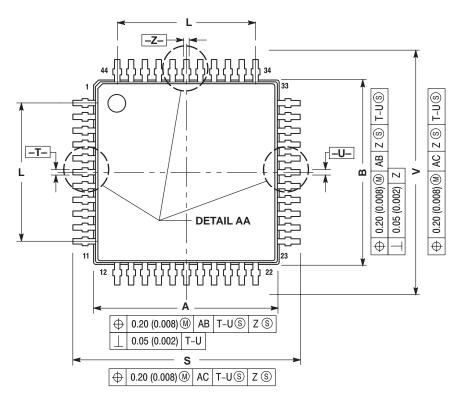

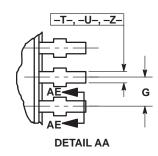

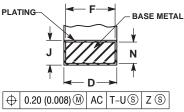

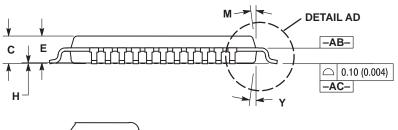

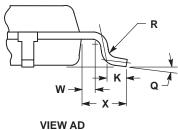

#### **PACKAGE DIMENSIONS**

#### **PB SUFFIX TQFP (THIN QUAD FLAT PACKAGE)** CASE 824D-01

**SECTION AE-AE**

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

DATUM PLANE -AB- IS LOCATED AT BOTTOM OF

- 3. DATUM PLANE AB- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

4. DATUMS -T-, -U- AND -Z- TO BE DETERMINED AT DATUM PLANE -AB-.

5. DIMENSIONS S AND V TO BE DETERMINED AT SEATING PLANE -AC-.

6. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTTUSION IS 0.25 (0.010) PER SIDE DIMENSIONS A AND B DO COMMENSIONS A AND B DO COMMENSIONS A BAD B DO COMM

- (0.010) PER SIDE. DIMENSIONS A AND B DO INCLUDE MOLD MISMATCH AND ARE DETERMINED

- AT DATUM PLANE -AB-.

7. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE D DIMENSION TO EXCEED 0.530

|     | MILLIN    | METERS | INCHES    |       |  |

|-----|-----------|--------|-----------|-------|--|

| DIM | MIN       | MAX    | MIN       | MAX   |  |

| Α   | 9.950     | 10.050 | 0.392     | 0.396 |  |

| В   | 9.950     | 10.050 | 0.392     | 0.396 |  |

| С   | 1.400     | 1.600  | 0.055     | 0.063 |  |

| D   | 0.300     | 0.450  | 0.012     | 0.018 |  |