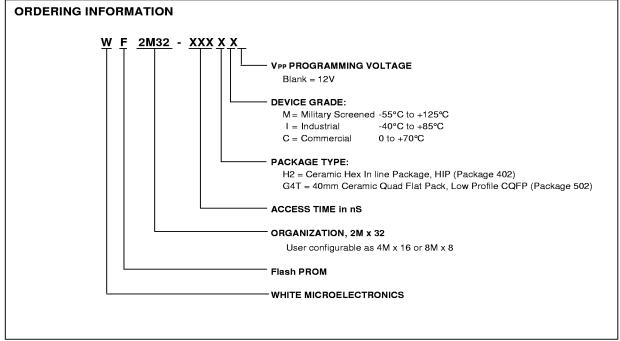

## 2Mx32 12V FLASH MODULE PRELIMINARY\*

## **FEATURES**

- Access Times of 90, 100, 120 nS

- Packaging:

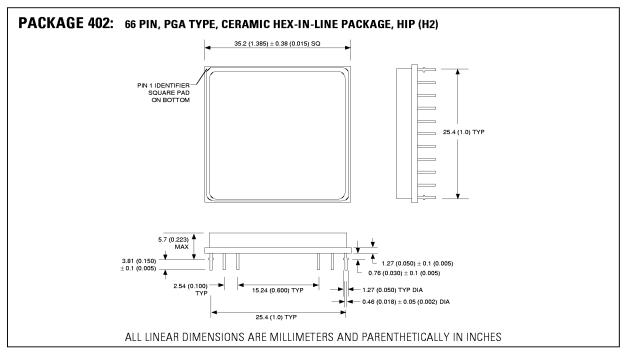

- 66-pin, PGA Type, 1.385 inch square, Hermetic Ceramic HIP (Package 402)

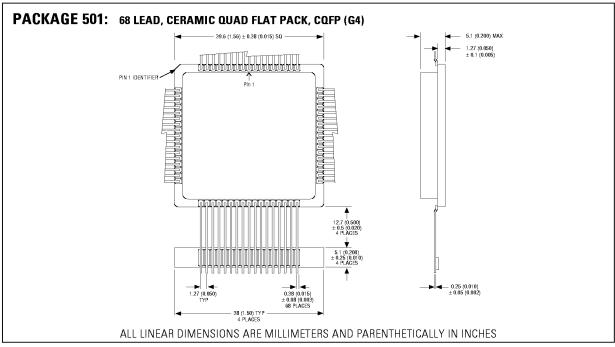

- 68 lead, 40mm square Hermetic CQFP (Package 501), 5.1mm (0.200")

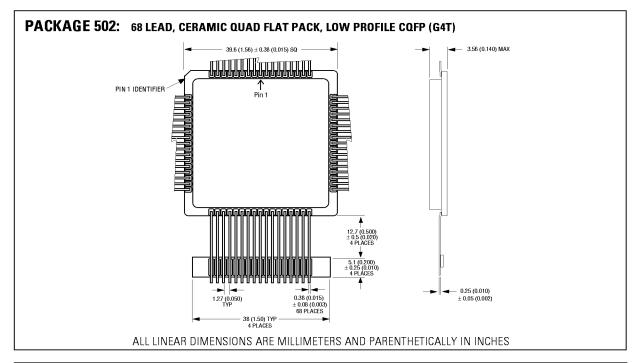

- 68 lead, 40mm Hermetic Low Profile CQFP (Package 502), 3.5mm (0.140")

- Sector Architecture

- 32 equal size sectors of 64KBytes per each 2Mx8 chip

- Two step sequence of erase ensures that memory contents are not accidently erased.

- 100,000 Erase/Program Cycles Minimum (0°C to 70°C)

- Organized as 2Mx32, user configurable as 4Mx16 or 8Mx8.

- Commercial, Industrial and Military Temperature Ranges

- 12 Volt Programming. 5V ± 10% Supply.

- Low Power CMOS, 8mA Standby Typical

- Pipelined Command Execution

- Write During Erase

- Automated Byte Write and Block Erase

- Command User Interface

- Compatible Status Register (CSR)

- Global Status Register (GSR)

- 32 Block Status Registers (BSRs) per Chip

- Built in Decoupling Caps and Multiple Ground Pins for Low Noise Operation

- Weight WF2M32-XH2X - 13 grams typical WF2M32-XG4TX - 20 grams typical

- \* This data sheet describes a product under development, not fully characterized, and is subject to change without notice.

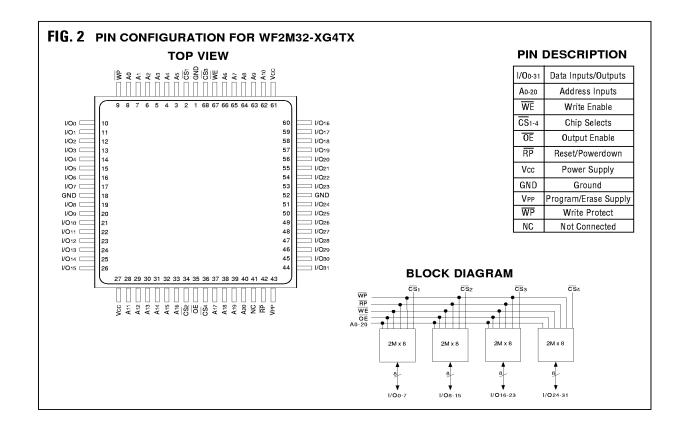

#### FIG. 1 PIN CONFIGURATION FOR WF2M32-XH2X PIN DESCRIPTION **TOP VIEW** 12 45 1/00-31 Data Inputs/Outputs A0-20 Address Inputs OI/O8 ORP ()I/O15 I/O24 O VCC O I/O31 O WE Write Enable ○I/O9 ○CS2 ○I/O14 I/O25 CS4 I/O30 C CS 1-4 Chip Selects OI/O10 OGND OI/O13 I/O26 \ WP \ I/O29 \ 0E Output Enable OA14 OI/011 OI/012 A7 () 1/027 () 1/028 () RP Reset/Powerdown Power Supply OA16 OA10 OŒ A12 A4 O Vcc A1() $V_{PP}$ Program/Erase Supply ()A11 ()A9 ()A17 VPP A5 A2() GND Ground ()WE A13 A6 WP **BLOCK DIAGRAM** Write Protect CS: OA18 OVCC OI/O7 A8 A20 I/O23 WP RP WE I/O16 \(\) \(\overline{CS}\_3\) |/O22 \(\overline{CS}\_3\) ○I/O0 ○CS1 ○I/O6 OE A0-20 I/O17 O GND / I/O21 O ()I/O1 ()A19 O1/O5 2M x 8 2M x 8 2M x 8 2M x 8 1/018 0 1/019 1/020 0 01/02 01/03 01/04 66 1/00-7 1/08-15 1/016-23 1/024-31

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                                |               | Unit |

|--------------------------------------------------------------------------|---------------|------|

| Voltage on Anny Pin with Respect to GND (except Vcc and Vpp)             | -2.0 to +7.0  | V    |

| VPP Program Voltage with Respect to<br>GND during Block Erase/Byte Write | -0.2 to +14.0 | V    |

| Vcc Supply Voltage with Respect to GND                                   | -0.2 to +7.0  | V    |

| Output Short Circuit Current                                             | 100           | mA   |

#### NOTES:

- Minimum DC voltage is -0.5V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <20nS. Maximum DC voltage on input/output pins is Vcc+0.5V which, during transitions, may overshoot to Vcc + 2.0V for periods <20 nS.</li>

- 2. Maximum DC voltage on VPP may overshoot to +14.0V for periods <20 nS.

- Output shorted for no more than one second. No more than one output shorted at a time.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a Stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| Parameter              | Symbol | Min  | Max       | Unit |

|------------------------|--------|------|-----------|------|

| Supply Voltage         | Vcc    | 4.5  | 5.5       | V    |

| Input High Voltage     | Vih    | 2.0  | Vcc + 0.5 | V    |

| Input Low Voltage      | VIL    | -0.5 | +0.8      | V    |

| Operating Temp. (Mil.) | Та     | -55  | +125      | °C   |

#### **CAPACITANCE**

$(TA = +25^{\circ}C)$

| Parameter                                     | Symbol | Conditions              | Max      | Unit |

|-----------------------------------------------|--------|-------------------------|----------|------|

| OE capacitance                                | Coe    | VIN = 0 V, f = 1.0 MHz  | 50       | pF   |

| WE1-4 capacitance<br>HIP (PGA) H2<br>CQFP G4T | Cwe    | VIN = 0 V, f = 1.0 MHz  | 50<br>50 | pF   |

| CS <sub>1-4</sub> capacitance                 | Ccs    | Vin = 0 V, f = 1.0 MHz  | 20       | pF   |

| Data I/O capacitance                          | C1/0   | Vi/o = 0 V, f = 1.0 MHz | 20       | pF   |

| Address input capacitance                     | CAD    | Vin = 0 V, f = 1.0 MHz  | 50       | pF   |

This parameter is guaranteed by design but not tested.

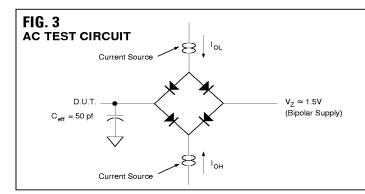

## **AC TEST CONDITIONS**

| Parameter                        | Тур                | Unit |

|----------------------------------|--------------------|------|

| Input Pulse Levels               | VIL = 0, VIH = 3.0 | ٧    |

| Input Rise and Fall              | 5                  | nS   |

| Input and Output Reference Level | 1.5                | ٧    |

| Output Timing Reference Level    | 1.5                | ٧    |

#### NOTES:

Vz is programmable from -2V to +7V.

lot & loн programmable from 0 to 16mA.

Tester Impedance  $Z_0 = 75 \Omega$ .

Vz is typically the midpoint of VoHand VoL.

lo. & loнare adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

## DC CHARACTERISTICS - CMOS COMPATIBLE

(Vcc = 5.0V, Vss = 0V, Ta = -55°C to +125°C)

| Parameter                         | Symbol | Conditions                                                                 | Min  | Max  | Unit |

|-----------------------------------|--------|----------------------------------------------------------------------------|------|------|------|

| Input Leakage Current             | Тш     | Vcc = 5.5, VIN = Vcc to GND                                                |      | 10   | μА   |

| Output Leakage Current            | llo    | Vcc = 5.5, Vout = Vcc to GND                                               |      | 10   | μА   |

| Vcc Standby Current               | lccs   | $Vcc = 5.5, \overline{CS} = \overline{RP} = \overline{WP} = ViH, f = 5MHz$ |      | 16.0 | mA   |

| Vcc Read Current                  | lccr   | Vcc = 5.5, $\overline{\text{CS}}$ = Vil., f = 5 MHz, lout = 0mA            |      | 175  | mA   |

| Vcc Write Current                 | lccw   | Write in Progress                                                          |      | 175  | mA   |

| Vcc Block Erase Current           | Icce   | Block Erase in Progress                                                    |      | 60   | mA   |

| Vcc Powerdown Current             | lccp   | RP = GND                                                                   |      | 8    | mA   |

| VPP Standby Current               | IPPS   | VPP < VCC                                                                  |      | 80   | μА   |

| VPP Powerdown Current             | IPPD   | $\overline{RP} = GND$                                                      |      | 80   | μА   |

| VPP Write Current                 | lppw   | VPP = VPPH, Write in Progress                                              |      | 60   | mA   |

| Vpp Block Erase Current           | IPPE   | Vpp = Vppн, Block Erase in Progress                                        |      | 60   | mA   |

| Output Low Voltage                | Vol    | Vcc = 4.5, lot = 5.8 mA                                                    |      | 0.45 | V    |

| Output High Voltage               | Vон    | Vcc = 4.5, loн = -2.5 mA                                                   | 2.4  |      | ٧    |

| VPP during Erase/Write Operations | VPPH   |                                                                            | 11.4 | 12.6 | V    |

| Vcc Erase/Write Lock Voltage      | VLKO   |                                                                            | 2.0  |      | ٧    |

| VPPL During Normal Operations     | VPPL   |                                                                            | 0.0  | 6.5  | V    |

#### NOTES:

- 1. Block Erases/Writes are inhibited when VPP = VPPL and not guaranteed in the range between VPPL and VPPH.

- 2. DC test conditions VIL = 0.3V, VIH = VCC 0.3V

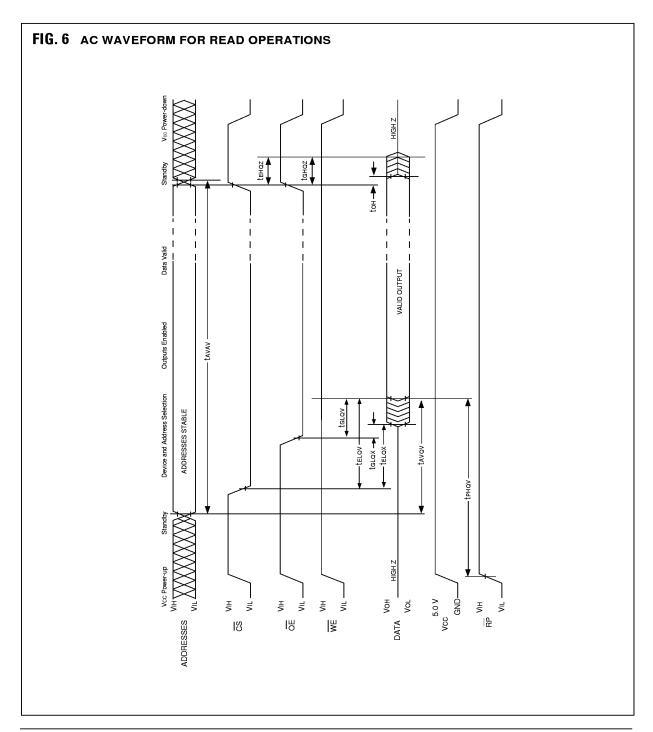

#### **AC CHARACTERISTICS – READ-ONLY OPERATIONS**

$(Vcc = 5.0V, Vss = 0V, TA = -55^{\circ}C to +125^{\circ}C)$

| Parameter                                                                                                            | Syr   | nbol | <u>-9</u> | <u> </u> | <u>-10</u> | <u>)0</u> | <u>-120</u> |     | Unit |

|----------------------------------------------------------------------------------------------------------------------|-------|------|-----------|----------|------------|-----------|-------------|-----|------|

|                                                                                                                      |       |      | Min       | Max      | Min        | Max       | Min         | Max | ł    |

| Read Cycle Time                                                                                                      | tavav | trc  | 90        |          | 100        |           | 120         |     | nS   |

| Address Access Time                                                                                                  | tavqv | tacc |           | 90       |            | 100       |             | 120 | nS   |

| Chip Select to Output Valid (1)                                                                                      | tELQV | tce  |           | 90       |            | 100       |             | 120 | nS   |

| Output Enable to Output Valid (1)                                                                                    | talav | toe  |           | 40       |            | 40        |             | 45  | nS   |

| Chip Select to Output Low Z (2)                                                                                      | telax | tız  | 0         |          | 0          |           | 0           |     | nS   |

| Chip Select High to Output High Z (2)                                                                                | tenoz | tHZ  |           | 35       |            | 35        |             | 40  | nS   |

| Output Enable to Output Low Z (2)                                                                                    | tgLqx | talz | 0         |          | 0          |           | 0           |     | nS   |

| Reset to Output Valid (2)                                                                                            | tphqv | tрwн |           | 550      |            | 550       |             | 620 | nS   |

| Output Enable High to Output High Z(2)                                                                               | tgHQZ | tor  |           | 35       |            | 35        |             | 40  | nS   |

| Output Hold from Addresses, $\overline{\text{CS}}$ or $\overline{\text{OE}}$ Change, Whichever is First <sup>2</sup> | tон   | tон  | 0         |          | 0          |           | 0           |     | nS   |

### NOTES:

- 1.  $\overline{\text{OE}}$  may be delayed up to tcE-toE after the falling edge of  $\overline{\text{CS}}$  without impact on tcs.

- 2. Guaranteed by design, not tested.

## AC CHARACTERISTICS - WRITE/ERASE/PROGRAM OPERATIONS - WE CONTROLLED

$(Vcc = 5.0V, Vss = 0V, Ta = -55^{\circ}C to +125^{\circ}C)$

| Parameter                                 | Syr    | nbol | <u>-9</u> | <u> </u> | <u>-10</u> | 10  | <u>-12</u> | <u>20</u> | Unit |

|-------------------------------------------|--------|------|-----------|----------|------------|-----|------------|-----------|------|

|                                           |        |      | Min       | Max      | Min        | Max | Min        | Max       |      |

| Write Cycle Time                          | tavav  | twc  | 90        |          | 100        |     | 120        |           | nS   |

| Chip Select Setup Time                    | telwl  | tcs  | 0         |          | 0          |     | 0          |           | nS   |

| Write Enable Pulse Width                  | twLwH  | twp  | 50        |          | 50         |     | 50         |           | nS   |

| V <sub>PP</sub> Setup Time (1)            | tvpwn  | tvps | 100       |          | 100        |     | 100        |           | n S  |

| Address Setup to WE Going High            | tavwh  |      | 50        |          | 50         |     | 50         |           | nS   |

| Data Setup Time                           | tovwн  | tos  | 60        |          | 60         |     | 60         |           | nS   |

| Data Hold Time                            | twndx  | tон  | 0         |          | 0          |     | 0          |           | nS   |

| Address Hold Time                         | twhax  | tан  | 10        |          | 10         |     | 10         |           | nS   |

| Chip Select Hold Time                     | twheh  | tсн  | 10        |          | 10         |     | 10         |           | nS   |

| Write Enable Pulse Width High             | twhwL  | twph | 50        |          | 50         |     | 50         |           | nS   |

| Duration of Byte Write Operation (1,2,3)  | twnqv1 |      | 4.5       |          | 4.5        |     | 4.5        |           | μS   |

| Duration of Block Erase Operation (1,2,3) | twHQV2 |      | 0.3       |          | 0.3        |     | 0.3        |           | Sec  |

| Write Recovery before Read                | twngL  |      | 80        |          | 80         |     | 80         |           | nS   |

| RP High Recovery Time (1)                 | tphwl  | tps  | 1         |          | 1          |     | 1          |           | μS   |

#### NOTES:

- 1. Guaranteed by design, not tested.

- 2. The on-chip Write State Machine incorporates all byte write and block erase functions and overhead of the flash memory, this includes byte program and verify, block precondition and verify, erase and verify.

- 3. Byte write and block erase durations are measured to completion (SR. 7 = 1). VPP should be held at VPPH until determination of byte write/block erase success (SR.3/4/5 = 0).

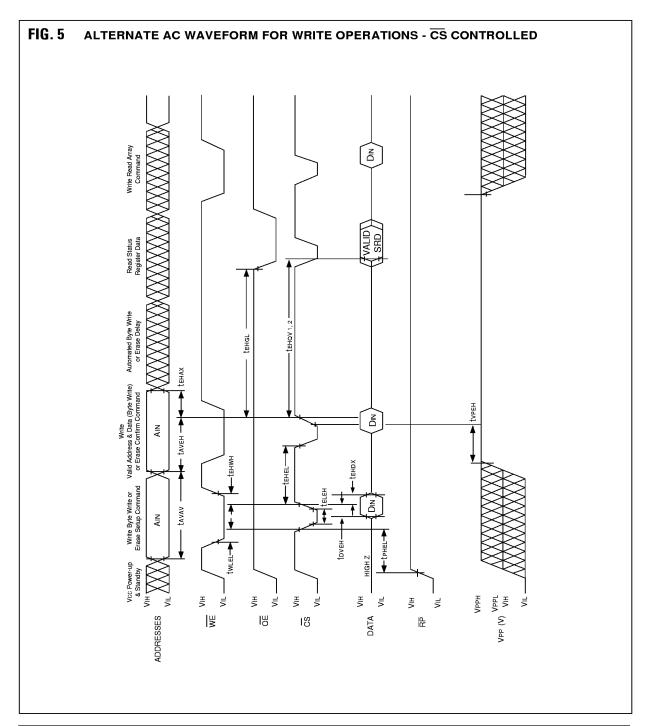

## AC CHARACTERISTICS - WRITE OPERATION - CS CONTROLLED (1)

$(Vcc = 5.0V, Vss = 0V, Ta = -55^{\circ}C to +125^{\circ}C)$

| Parameter                                          | Symbol |      | <u>-9</u> | <u>0</u> | - 1 | 100 | <u>-120</u> |     | Unit |

|----------------------------------------------------|--------|------|-----------|----------|-----|-----|-------------|-----|------|

|                                                    |        |      | Min       | Max      | Min | Max | Min         | Max |      |

| Write Enable Cycle Time                            | tavav  | twc  | 90        |          | 100 |     | 120         |     | nS   |

| Write Enable Setup Time                            | twlel  | tws  | 0         |          | 0   |     | 0           |     | nS   |

| Chip Select Pulse Width                            | teleh  | tcp  | 50        |          | 50  |     | 50          |     | nS   |

| Vpp Setup Time                                     | tvpeh  | tvps | 100       |          | 100 |     | 100         |     | nS   |

| Address Setup to $\overline{\text{CS}}$ Going High | taveh  |      | 50        |          | 50  |     | 50          |     | nS   |

| Data Setup Time                                    | toveh  | tos  | 60        |          | 60  |     | 60          |     | nS   |

| Data Hold Time                                     | tehdx  | tон  | 0         |          | 0   |     | 0           |     | nS   |

| Address Hold Time                                  | tehax  | tah  | 10        |          | 10  |     | 10          |     | nS   |

| Write Enable Hold Time                             | tehwh  | twн  | 10        |          | 10  |     | 10          |     | nS   |

| Chip Select Pulse Width High                       | tehel  | tерн | 50        |          | 50  |     | 50          |     | nS   |

| Duration of Byte Write Operation (2, 3)            | tehqv1 |      | 4.5       |          | 4.5 |     | 4.5         |     | μS   |

| Duration of Block Erase Operation (2, 3)           | tehqv2 |      | 0.3       |          | 0.3 |     | 0.3         |     | Sec  |

| Write Recovery before Read                         | tehgl  |      | 80        |          | 80  |     | 80          |     | nS   |

| RP High Recovery to CS Low (2)                     | †PHEL  | tps  | 1         |          | 1   |     | 1           |     | μS   |

#### NOTES:

<sup>1.</sup> Chip-Select Controlled Writes: Write operations are driven by the valid combination of CS and WE. In systems where CS defines the write pulsewidth (within a longer WE timing waveform), all setup, hold and inactive WE times should be measured relative to the CS waveform.

<sup>2.</sup> Guaranteed by design, not tested.

<sup>3.</sup> Byte write and block erase durations are measured to completion (SR.7 = 1, VoH). VPP should be held at VPPH until determination of byte write/block erase success (SR.3/4/5 = 0).

FIG. 4 AC WAVEFORMS FOR WRITE-ERASE-PROGRAM OPERATIONS, WE CONTROLLED Write Read Array Command VALID Read Status Register Data Automated Byte Write or Erase Delay twhax Write

Valid Address & Data (Byte Write)

or Erase Confirm Command DATA Ā **★** tavwH **★** twHwL Write Byte Write or Erase Setup Command tavav Ā HIGHZ Vcc Power-up & Standby Ĭ. VPP (V) VPPL ₹ ₹ ₹ ₹ VРРH ₹ ₹ ₹ ₹ ₹ 삥 ME IS DATA 먎 ADDRESSES

## PRINCIPLES OF OPERATION

The following Principles of Operation of the WF2M32-XXX MCM is applicable to each of the four memory chips inside the MCM. Chip 1 is distinguished by CS1 and I/Oo-7, Chip 2 by CS2 and I/O8-15, Chip 3 by CS3 and I/O16-23, and Chip 4 by CS4 and 1/024-31.

The WF2M32-XXX includes write automation to manage write and erase functions. The Write State Machine allows for 100% TTL-level control inputs; fixed power supplies during block erasure and byte write; and minimal processor overhead with RAM-like interface timings.

After initial device powerup the WF2M32-XXX functions as a read-only memory. Manipulation of external memory-control pins allow array read, standby and output disable operations. The status register can also be accessed through the command user interface when VPP = VPPL.

This same subset of operations is also available when high voltage is applied to the VPP pin. In addition, high voltage on VPP enables successful block erasure and byte writing of the device. Functions associated with altering memory contents—byte write, block erase—are accessed via the command user interface and verified thru the status register.

Commands are written using standard microprocessor write timings. Command user interface contents serve as input to the write status machine, which controls the block erase and byte write circuitry. Write cycles also internally latch addresses and data needed for byte write or block erase operations.

Interface software to initiate and poll progress of internal byte write and block erase can be stored in any of the blocks. This code is copied to, and executed from, system RAM during actual flash memory update. After successful completion of byte write and/or block erase, code/data reads from the device are again possible via the read array command. Erase suspend/resume capability allows system software to suspend block erase to read data and execute code from any other block.

## **COMPARISON OF WF1M32 TO WF2M32**

A Superset of commands have been added to the basic WF1M32-XXX (formerly WF1024K32-XXX) command-set to achieve higher write performance and provide additional capabilities. These new commands and features include:

- Page Buffer Writes to Flash

- Command Queuing Capability

- Automatic Data Writes During Erase

- Software Locking of Memory Blocks

- Two-Byte Successive Writes in 8-bit Systems

- Erase All Unlocked Blocks

A Block Erase operation erases one of the 32 blocks, which is about 65% improvement over the WF1M32-XXX.

Each block can be written and erased a minimum of 100,000 cycles (0°C to 70°C). Systems can achieve 1 million block erase cycles by providing wear-leveling algorithms and block retirement.

Each chip in WF2M32-XXX incorporates two page buffers of 256 Bytes (128 Words) each to allow page data writes. This feature can improve a system write performance by up to 4.8 times over previous flash memory devices.

All operations are started by a sequence of write commands to the device. Three Status Registers (described in detail later) and a RY/BY output pin provide information on the progress of the requested operation.

While the WF1M32 requires an operation to complete before the next operation can be requested, the WF2M32 allows queueing of the next operation while memory executes the current operation. This eliminates system overhead when writing several bytes in a row to the array or erasing several blocks at the same time. The WF2M32 can also perform write operations to one block of memory while performing erase of another block.

The WF2M32 provides user-selectable block locking to protect code or data. Each block has an associated nonvolatile lock-bit which determines the lock status of the block. In addition, the WF2M32 has a master Write Protect pin (WP) which prevents any modifications to memory blocks whose lock-bits are set.

The WF2M32 contains three types of Status Registers to accomplish various functions:

- A Compatible Status Register (CSR) which is 100% compatible with the WF1M32 flash memory's Status Register. This register, when used alone, provides a straightforward upgrade capability to the WF2M32 from a WF1M32 based design.

- A Global Status Register (GSR) which informs the system of command queue status, page buffer status, and overall Write State Machine (WSM) status.

- 32 Block Status Registers (BSRs) which provide blockspecific status information such as the block lock-bit status.

# COMMAND USER INTERFACE AND WRITE AUTOMATION

An on-chip state machine controls block erase and byte write, freeing the system processor for other tasks. After receiving the Erase Setup and Erase Confirm commands, the state machine controls block preconditioning and erase, returning progress via the Status Register on each of the four memory chips in the MCM. Byte write is similarly controlled, after destination address and expected data are supplied.

## DATA PROTECTION

Depending on the application, the system designer may choose to make the VPP power supply switchable (available only when memory byte writes/block erases are required) or hardwired to VPPH. When VPP = VPPL, memory contents cannot be altered. Additionally, all functions are disabled whenever Vcc is below the write lockout voltage VLKO or when  $\overline{\text{RP}}$  is at VIL. The two-step byte write/block erase command user interface write sequence provides additional software write protection.

## **BUS OPERATION**

Flash memory reads, erase and writes in-system via the local CPU. All bus cycles to or from the flash memory conform to standard microprocessor bus cycles.

## READ

The WF2M32-XXX can be read from any of its blocks, and information can be read from the status register of each chip selected. VPP can be at either VPPL or VPPH.

The first task is to write the appropriate read mode command to the command user interface. The device automatically resets to read array mode upon initial device powerup or after exit from deep powerdown. Chip select CS is the device selection control, and when active enables the selected memory device. Output Enable (OE) is the data input/output (I/Oo-I/O31) direction control, and when active drives data from the select memory onto the I/O bus. RP and WE must also be at ViH. Figure 6 illustrates read bus cycle waveforms.

## **OUTPUT DISABLE**

With  $\overline{\text{OE}}$  at a logic-high level (VIH), the device outputs are disabled. Output pins (I/Oo-31) are placed in a high-impedance state.

## **STANDBY**

$\overline{\text{CS}}$  at a logic-high level (VIH) places the device in a standby mode. Standby operation disables much of the device's circuitry and substantially reduces device power consumption. The outputs (I/Oo-31) are placed in a high-impedance state independent of the status of  $\overline{\text{OE}}$ . If the device is deselected during block erase or byte write, it will continue functioning and consuming normal active power until the operation is completed.

## WRITE

Writes to the command user interface enable reading of device data. They also control inspection and cleaning of the status register. Additionally, when VPP = VPPH, the command user interface controls block erasure and byte write. The contents of the interface register serve as input to the internal state machine.

The command user interface itself does not occupy an addressable memory location. The interface register is a latch used to store the command and address and data information needed to execute the command. Erase setup and erase confirm commands require both appropriate command data and an address within the block to be erased. The Byte Write Setup command requires both appropriate command data and the address of the location to be written, while the Byte Write command consists of the data to be written and the address of the location to be written.

The command user interface is written by bringing  $\overline{WE}$  to a logic-low level (VIL) while  $\overline{CS}$  is low. Address and data are latched on the rising edge of  $\overline{WE}$ . Standard microprocessor write timings are used.

Refer to AC Write Characteristics and the AC Waveforms for Write Operation, Figures 4 and 5, for specific timing parameters.

## COMMAND DEFINITIONS

When VPPL is applied to the VPP pin of the chip selected, read operations from the status register, or array blocks are enabled. Placing VPPH on VPP enables successful byte write and block erase operations as well.

Device operations are selected by writing specific commands into the command user interface of the chip selected. Table 2 defines the WF2M32-XXX commands.

## **READ ARRAY COMMAND**

Upon initial device powerup the device defaults to Read Array mode. This operation is also initiated by writing FFH into the command user interface. Microprocessor read cycles retrieve array data. The device remains enabled for reads until the command user interface contents are altered. Once the internal Write State Machine has started a block erase or byte write operation, the device will not recognize the Read Array command, until the WSM has completed its operation. The Read Array command is functional when VPP = VPPL or VPPH.

10

## WHITE MICROELECTRONICS

## **TABLE 1 - BUS OPERATIONS**

| Mode            | Notes | RP  | CS                | ŌĒ  | WE  | 1/00-7 |

|-----------------|-------|-----|-------------------|-----|-----|--------|

| Read            |       | Vih | VIL               | VIL | Vih | Douт   |

| Output Disable  |       | Vih | VIL               | Vih | Vih | High Z |

| Standby         | 1     | Vih | VIL<br>VIH<br>VIH | Х   | Х   | High Z |

| Deep Power-down | 1,2   | VIL | Х                 | Х   | Х   | High Z |

| Write           | 3     | Vih | VIL               | Vih | VIL | Din    |

#### NOTES:

- 1. X can be VIH or VIL for address or control pins.

- 2. RP at GND ±0.2V ensures the lowest deep power-down current.

- 3. Commands for different Erase operations, Data Write operations or Lock-Block operations can only be successfully completed when VPP = VPPH.

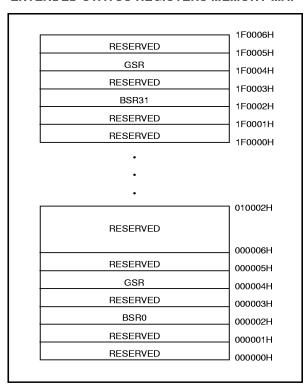

### **EXTENDED STATUS REGISTERS MEMORY MAP**

**NOTE:** The above memory map is for each of the four memory chips in the WF2M32-XXX module.

### TABLE 2 - COMMAND DEFINITIONS - COMPATIBLE MODE (with WF1M32-XXX)

|                                 | Notes |           | First Bus Cycle |      | Second Bus Cycle |         |      |  |

|---------------------------------|-------|-----------|-----------------|------|------------------|---------|------|--|

| Command                         | Hotes | Operation | Address         | Data | Operation        | Address | Data |  |

| Read Array                      |       | Write     | Х               | FFH  | Read             | AA      | AD   |  |

| Read Compatible Status Register | 1     | Write     | Х               | 70H  | Read             | Х       | CSRD |  |

| Clear Status Register           | 2     | Write     | х               | 50H  |                  |         |      |  |

| Word/Byte Write                 |       | Write     | Х               | 40H  | Write            | WA      | WD   |  |

| Alternate Word/Byte Write       |       | Write     | Х               | 10H  | Write            | WA      | WD   |  |

| Block Erase/Confirm             |       | Write     | Х               | 20H  | Write            | ВА      | DOH  |  |

| Erase Suspend/Resume            |       | Write     | х               | вон  | Write            | Х       | DOH  |  |

#### **ADDRESS**

AA = Array Address BA = Block Address WA = Write Address X = Don't Care

#### DATA

AD = Array Data CSRD = CSR Data WD = Write Data

#### NOTES:

- The CSR is automatically available after device enters Data Write, Erase, or Suspend operations.

- Clears CSR.3, CSR.4, CSR.5. Also clears GSR.5 and all BSR.5 and BSR.2 bits.

See Status register definitions.

#### **TABLE 3 - COMMAND DEFINITIONS - ENHANCED MODE**

| Command                              | Notes | Firs      | st Bus Cycl | e            | Sec       | ond Bus Cy | cle          | Third Bus Cycle |         |         |

|--------------------------------------|-------|-----------|-------------|--------------|-----------|------------|--------------|-----------------|---------|---------|

| Cullillallu                          | Notes | Operation | Address     | Data         | Operation | Address    | Data         | Operation       | Address | Data    |

| Read Extended<br>Status Register     | 1     | Write     | Х           | 71H          | Read      | RA         | GSRD<br>BSRD |                 |         |         |

| Page Buffer Swap                     | 5     | Write     | Х           | 72H          |           |            |              |                 |         |         |

| Read Page Buffer                     |       | Write     | Х           | 75H          | Read      | PA         | PD           |                 |         |         |

| Single Load to<br>Page Buffer        |       | Write     | х           | 74H          | Write     | PA         | PD           |                 |         |         |

| Sequential Load to<br>Page Buffer    | 3,4,6 | Write     | Х           | E <b>0</b> H | Write     | Х          | BCL          | Write           | Х       | ВСН     |

| Page Buffer Write to Flash           | 3,6   | Write     | Х           | OCH          | Write     | Ao         | BC(L,H)      | Write           | WA      | BC(H,L) |

| Two Byte <b>W</b> rite               |       | Write     | Х           | FBH          | Write     | Ao         | WD(L,H)      | Write           | WA      | WD(H,L) |

| Lock Block/Confirm                   |       | Write     | Х           | 77H          | Write     | BA         | DOH          |                 |         |         |

| Upload Status Bits/Confirm           | 2     | Write     | Х           | 97H          | Write     | Х          | DOH          |                 |         |         |

| Upload Device Information            |       | Write     | Х           | 99H          | Write     | Х          | DOH          |                 |         |         |

| Erase All Unlocked<br>Blocks/Confirm |       | Write     | х           | <b>A</b> 7H  | Write     | Х          | DOH          |                 |         |         |

| Sleep                                |       | Write     | Х           | F0H          |           |            |              |                 |         |         |

| Abort                                |       | Write     | Х           | <b>80</b> H  |           |            |              |                 |         | •       |

#### **ADDRESS**

BA = Block Address

PA = Page Buffer Address RA = Extended Register Address

WA = Write Address X = Don't Care

#### DATA

AD = Array Data PD = Page Buffer Data BSRD = BSR Data

GSRD = GSR Data

BC (L,H) = Byte Count (Low, High) WD (L,H) = Write Data (Low, High)

#### NOTES:

- 1. RA can be the GSR address or any BSR address.

- 2. Upon device power-up, all BSR lock-bits come up locked. The Upload Status Bits command must be written to reflect the actual lock-bit status.

- 3. BCH/WCH must be at 00H for this product because of the 256-Byte (128 Word) Page Buffer size and to avoid writing the Page Buffer contents into more than one 256-Byte segment within an array block. They are simply shown for future Page Buffer expandability.

- 4. PA and PD (whose count is given in cycles 2 and 3) are supplied starting in the 4th cycle which is not shown.

- 5. This command allows the user to swap between available Page Buffers (0 or 1).

- 6. BCL = 00H corresponds to a Byte count of 1. Similarly, WCL = 00H corresponds to a Word count of 1.

## TABLE 4 COMPATIBLE STATUS REGISTER

| WSMS | ESS | ES | DWS | VPPS | R | R | R |

|------|-----|----|-----|------|---|---|---|

| 7    | 6   | 5  | 4   | 3    | 2 | 1 | 0 |

CSR.7 = WRITE STATE MACHINE STATUS

1 = Ready

0 = Busy

CSR.6 = ERASE-SUSPEND STATUS

1 = Erase Suspended

0 = Erase in Progress/Completed

CSR.5 = ERASE STATUS

1 = Error in Block Erasure

0 = Successful Block Erase

CSR.4 = DATA WRITE STATUS

1 = Error in Data Write

0 = Data Write Successful

CSR.3 = VPP STATUS

1 = VPP Low Detect; Operation Abort

0 = VPP OK

CSR.2-0 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use and should be masked out when polling the CSR.

#### NOTES:

- WSMS bit must be checked to determine completion of an operation (Erase Suspend, Erase or Data Write) before the appropriate Status bit (ESS, ES or DWS) is checked for success.

- If DWS and ES are set to "1" during an erase attempt, an improper command sequence was entered. Clear the CSR and attempt the operation again.

- 3. The VPPS bit, unlike an A/D converter, does not provide continuous indication of VPP level. The WSM interrogates the VPP's level only after the data write or erase command sequences have been entered, and informs the system if VPP has not been switched on. The VPPS is not quaranteed to report accurate feedback between VPPLand VPPH.

## **READ STATUS REGISTER COMMAND**

Each chip of the WF2M32-XXX contains a status register which may be read to determine when a byte write or block erase operation is complete, and whether that operation completed successfully. The status register may be read at any time by writing the read status register command (70H) to the command user interface. After writing this command, all subsequent read operations output data from the status register, until another valid command is written to the command user interface. The contents of the status register are latched on the falling edge of  $\overline{\text{OE}}$  or  $\overline{\text{CS}}$ , whichever occurs last in the read cycle.  $\overline{\text{OE}}$  or  $\overline{\text{CS}}$  must be toggled to VIH before further reads to update the status register latch. The read status register command functions when VPP = VPPL or VPPH.

## **CLEAR STATUS REGISTER COMMAND**

The erase status and byte write status bits are set to "1"s by the Write State Machine on each chip and can only be reset by the clear status register command. These bits indicate various failure conditions (see Table 4). By allowing system software to control the resetting of these bits, several operations may be performed (such as cumulatively writing several bytes or erasing multiple blocks in sequence). The status register may then be

polled to determine if an error occurred during that sequence. This adds flexibility to the way the device may be used.

Additionally, the VPP Status bit (CSR.3) of the chip selected MUST be reset by system software before further byte writes or block erases are attempted. To clear the status register, the clear status register command (50H) is written to the command user interface. The clear status register command is functional when VPP = VPPL or VPPH

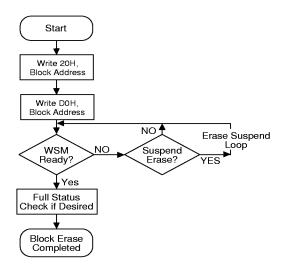

# ERASE SETUP/ERASE CONFIRM COMMANDS

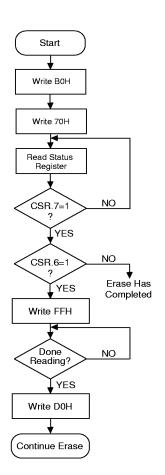

Erase is executed one block at a time, initiated by a two-cycle command sequence. An erase setup command (20H) is first written to the command user interface, followed by the Erase Confirm command (DOH). These commands require both appropriate sequencing and address within the block to be erased to FFH. Block preconditioning, erase and verify are all handled internally by the Write State Machine, invisible to the system. After the two command erase sequence is written to it, the WF2M32-XXX automatically outputs status register data when read (see Figure 8; Block Erase Algorithm). The CPU can detect the completion of the erase event by analyzing the output of the WSM Status bit of the status register.

When erase is completed, the Erase Status bit should be checked. If erase error is detected, the status register should be cleared. The command user interface remains in read status register mode until further commands are issued to it.

This two-step sequence of setup followed by execution ensures that memory contents are not accidentally erased. Also, reliable block ensure can only occur when VPP = VPPH. In the absence of this high voltage, memory contents are protected against

erasure. If block erase is attempted while VPP = VPPL, the VPP status bit will be set to "1". Erase attempts while VPPL < VPP < VPPH produce spurious results and should not be attempted.

## TABLE 5 GLOBAL STATUS REGISTER

| WSMS | oss | DOS | DSS | QS | PBAS | PBS | PBSS |

|------|-----|-----|-----|----|------|-----|------|

| 7    | 6   | 5   | 4   | 3  | 2    | 1   | 0    |

#### NOTES:

WSMS bit must be checked to determine completion

of an operation (Block Lock, Suspend, Upload Status Bits, Erase or Data

Write) before the appropriate Status bit (OSS or DOS) is checked for

success

- GSR.7 = WRITE STATE MACHINE STATUS

- 1 = Ready

- 0 = Busy

- GSR.6 = OPERATION SUSPEND STATUS

- 1 = Operation Suspended

- 0 = Operation in Progress/Completed

- GSR.5 = DEVICE OPERATION STATUS

- 1 = Operation Unsuccessful

- 0 = Operation Successful or Currently Running

- GSR.4 = DEVICE SLEEP STATUS

- 1 = Device in Sleep

- 0 = Device Not in Sleep

#### MATRIX 5/4

- 00 = Operation Successful or Currently Running

- 01 = Device in Sleep Mode or Pending Sleep

- 10 = Operation Unsuccessful

- 11 = Operation Unsuccessful or Aborted

- GSR.3 = QUEUE STATUS

- 1 = Queue Full

- 0 = Queue Available

- GSR.2 = PAGE BUFFER AVAILABLE STATUS

- 1 = One or Two Page Buffers Available

- 0 = No Page Buffer Available

- GSR.1 = PAGE BUFFER STATUS

- 1 = Selected Page Buffer Ready

- 0 = Selected Page Buffer Busy

- GSR.0 = PAGE BUFFER SELECT STATUS

- 1 = Page Buffer 1 Selected

- 0 = Page Buffer 0 Selected

- 2. If operation currently running, then GSR.7 = 0.

- 3. If device pending sleep, then GSR.7 = 0.

- 4. Operation aborted: Unsuccessful due to Abort command.

- 5. The device contains two Page Buffers.

- 6. Selected Page Buffer is currently busy with WSM operation.

#### NOTE:

1. When multiple operations are queued, checking BSR.7 only provides indication of completion for that particular block. GSR.7 provides indication when all queued operations are completed.

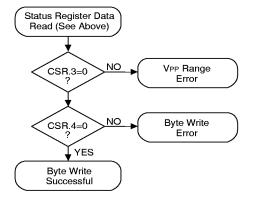

## **BYTE WRITE SETUP/WRITE COMMANDS**

Byte write is executed by a two-command sequence. The byte write setup command (40H) is written to the command user interface of the chip selected, followed by a second write specifying the address and data (latched on the rising edge of WE) to be written. The WSM then takes over, controlling the byte write and write verify algorithms internally. After the two-command byte write sequence is written to it, the device automatically outputs status register data when read (see Figure 7; Byte Write Algorithm). The CPU can detect the completion of the byte write event by analyzing the output of the WSM Status

bit of the status register. Only the read status register command is valid while byte write is active.

When byte write is complete, the byte write status bit should be checked. If byte write error is detected, the status register should be cleared. The internal WSM verify only detects errors for "1"s that do not successfully write to "0"s. The command user interface remains in read status register mode until further commands are issued to it. If byte write is attempted while VPP = VPPL, the VPP status bit will be set to "1". Byte write attempts while VPPL < VPP < VPPH produce spurious results and should not be attempted.

## TABLE 6 BLOCK STATUS REGISTER

| BS | BLS | BOS | BOAS | QS | VPPS | R | R |

|----|-----|-----|------|----|------|---|---|

| 7  | 6   | 5   | 4    | 3  | 2    | 1 | 0 |

#### BSR.7 = BLOCK STATUS

- 1 = Ready

- 0 = Busy

#### BSR.6 = BLOCK-LOCK STATUS

- 1 = Block Unlocked for Write/Erase

- 0 = Block Locked for Write/Erase

#### BSR.5 = BLOCK OPERATION STATUS

- 1 = Operation Unsuccessful

- 0 = Operation Successful or Currently Running

### BSR.4 = BLOCK OPERATION ABORT STATUS

- 1 = Operation Aborted

- 0 = Operation Not Aborted

#### MATRIX 5/4

00 = Operation Successful or Currently Running

- 01 = Not a Valid Combination

- 10 = Operation Unsuccessful

- 11 = Operation Aborted

- BSR.3 = QUEUE STATUS

- 1 = Queue Full

- 0 = Queue Available

- BSR.2 = VPP STATUS

- 1 = VPP Low Detect, Operation Abort

- 0 = VPP OK

- BSR.1-0 = RESERVED FOR FUTURE ENHANCEMENTS

## NOTES:

BS must be checked to determine completion of an operation (Block Lock, Suspend, Erase or Data Write) before the appropriate Status bit (BOS, BLS) is checked for success.

2. The BOAS bit will not be set until BSR.7 = 1.

Operation halted via Abort command.

These bits are reserved for future use; mask them out when polling the BSRs

#### NOTE:

1. When multiple operations are queued, checking BSR.7 only provides indication of completion for that particular block. GSR.7 provides indication when all queued operations are completed.

FIG. 7 **AUTOMATED BYTE WRITE ALGORITHM**

## **FULL STATUS CHECK PROCEDURE**

| Bus<br>Operation | Command             | Comments                                                                                       |

|------------------|---------------------|------------------------------------------------------------------------------------------------|

|                  |                     |                                                                                                |

|                  | B W .:              | 2                                                                                              |

| Write            | Byte Write<br>Setup | Data = 40H (10H) Address = Byte to be Written                                                  |

| Write            | Byte Write          | Data to be written<br>Address = Byte to be Written                                             |

| Standby/Read     |                     | Check WSMS bit VoH = Ready, VoL = Busy or Read Status Register                                 |

|                  |                     | Read Status Register Check CSR.7 1 = Ready, 0 = Busy Toggle OE or CS to update Status Register |

Repeat for subsequent bytes

Full status check can be done after each byte or after a sequence of bytes

Write FFH after the last byte write operation to reset the device to Ready Array Mode

| Bus<br>Operation | Command | Comments                                                                        |

|------------------|---------|---------------------------------------------------------------------------------|

| Optional<br>Read |         | CPU may already have read<br>Status Register data in WSM<br>Ready polling above |

| Standby          |         | Check CSR.3<br>1 = Vpp Low Detect                                               |

| Standby          |         | Check CSR.4<br>Both 1 = Byte Write Error                                        |

CSR.3 MUST be cleared, if set during a block erase attempt, before further attempts are allowed by the Write State Machine.

CSR.4 is only cleared by the clear status register command, in cases where multiple bytes are written before full status is checked.

If error is detected, clear the status register before attempting retry or other error recovery.

FIG. 8

AUTOMATED BLOCK ERASE ALGORITHM

| Bus<br>Operation | Command        | Comments                                                                                                  |

|------------------|----------------|-----------------------------------------------------------------------------------------------------------|

|                  |                |                                                                                                           |

| Write            | Erase<br>Setup | Data = 20H<br>Address = Within block<br>to be erased                                                      |

| Write            | Erase          | Data = D0H<br>Address = Within block<br>to be erased                                                      |

| Standby/Read     |                | Check WSMS bit VoH = Ready, VoL = Busy or Read Compatible Status Register Check CSR.7 1 = Ready, 0 = Busy |

|                  |                | Toggle OE or CS to update<br>Compatible Status Register                                                   |

Repeat for subsequent bytes

Full status check can be done after each byte or after a sequence of bytes

Write FFH after the last byte write operation to reset the device to Ready Array Mode

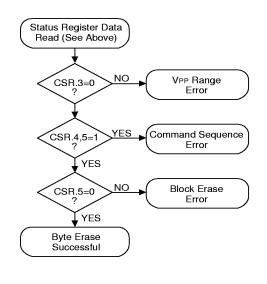

## **FULL STATUS CHECK PROCEDURE**

| Bus              |         |                                                                                            |

|------------------|---------|--------------------------------------------------------------------------------------------|

| Operation        | Command | Comments                                                                                   |

| Optional<br>Read |         | CPU may already have read<br>Compatible Status Register data<br>in WSM Ready polling above |

| Standby          |         | Check CSR.3<br>1 = Vpp Low Detect                                                          |

| Standby          |         | Check CSR.4, 5<br>Both 1 = Command<br>Sequence Error                                       |

| Standby          |         | Check CSR.5<br>1 = Block Erase Error                                                       |

CSR.3 MUST be cleared, if set during a block erase attempt, before further attempts are allowed by the Write State Machine.

CSR.5 is only cleared by the clear status register command, in cases where multiple bytes are written before full status is checked.

If error is detected, clear the status register before attempting retry or other error recovery.

FIG. 9

ERASE SUSPEND/RESUME ALGORITHM

| Bus<br>Operation | Command                 | Comments                                                                           |

|------------------|-------------------------|------------------------------------------------------------------------------------|

|                  |                         |                                                                                    |

|                  |                         |                                                                                    |

|                  |                         |                                                                                    |

| Write            | Erase<br>Suspend        | Data = B0H                                                                         |

| <b>W</b> rite    | Read<br>Status Register | Data = 70H                                                                         |

| Standby/Read     |                         | Read Compatible Status<br>Register                                                 |

|                  |                         | Check CSR.7<br>1 = Ready, 0 = Busy<br>Toggle OE or CS to update<br>Status Register |

| Standby          |                         | Check CSR.6<br>1 = Suspended                                                       |

| Write            | Read Array              | Data = FFH                                                                         |

| Read             |                         | Read array data from block<br>other than that being<br>erased.                     |

| Write            | Erase Resume            | Data = DOH                                                                         |

|                  |                         |                                                                                    |

# ERASE SUSPEND/ERASE RESUME COMMANDS

The erase suspend command allows block erase interruption in order to read data from another block of memory. Once the erase process starts, writing the erase suspend command (B0H) to the command user interface requests that the WSM suspend the erase sequence at a predetermined point in the erase algorithm. The WF2M32-XXX continues to output status register data when read, after the erase suspend command is written to it. Polling the WSM status and erase suspend status bits will determine when the erase operation has been suspended (both will be set to "1").

At this point, a read array command can be written to the command user interface to read data from blocks other than that which is suspended. The only other valid commands at this time are read status register (70H) and erase resume (D0H), at which time the WSM will continue with the erase process. The erase suspend status and WSM status bits of the status register will be automatically cleared. After the erase resume command is written to it, the device automatically outputs status register data when read (see Figure 9). VPP must remain at VPPH while in erase suspend.

# VCC, VPP, RP TRANSITIONS AND THE COMMAND/STATUS REGISTERS

Byte write and block erase completion are not guaranteed if VPP drops below VPPH. If the VPP Status bit of the Status Register (SR.3) is set to "1", a Clear Status Register command MUST be issued before further byte write/block erase attempts are allowed by the WSM. Otherwise, the Byte Write (SR.4) or Erase (SR.5) Status bits of the Status Register will be set to "1"s if error is detected. RP transitions to VIL during byte write and block erase also abort the operations. Data is partially altered in either case, and the command sequence must be repeated after normal operation is restored. Device poweroff, or RP transitions to VIL, clear the Status Register to initial value 10000 for the upper 5 bits.

The Command User Interface latches commands as issued by system software and is not altered by VPP or  $\overline{\text{CS}}$  transitions or WSM actions. Its state upon powerup, after exit from deep powerdown or after Vcc transitions below VLKO, is Read Array Mode.

After byte write or block erase is complete, even after VPP transitions down to VPPL, the Command User interface must be reset to Read Array mode via the Read Array command if access to the memory array is desired.

## **POWER UP/DOWN PROTECTION**

The WF2M32-XXX is designed to offer protection against accidental block erasure or byte writing during power transitions. Upon power-up, the device is indifferent as to which power supply, VPP or Vcc, powers up first. Power supply sequencing is not required. Internal circuitry in the device ensures that the Command User interface is reset to the Read Array mode on power up.

## POWERDOWN AND RESET

The WF2M32-XXX offers a deep power-down feature, entered when RP is a VIL. During read modes, RP-low deselects the memory, places output drivers in a high-impedance state and turns off all internal circuits. The device requires time trwh (see AC Characteristics-Read-Only Operations) after return from powerdown until initial memory access outputs are valid. After this wakeup interval, normal operation is restored. The Command User Interface is reset to Read Array, and the upper 5 bits of the Status Register are cleared to value 10000, upon return to normal operation.

During block erase or bytewrite modes.  $\overline{RP}$  low will abort either operation. Memory contents of the block being altered are no longer valid as the data will be partially written or erased. Time tps after  $\overline{RP}$  goes to logic-high (ViH) is required before another command can be written.

This use of  $\overline{RP}$  during system reset is important with automated write/erase devices. When the system comes out of reset it expects to read from the flash memory. Automated flash memories provide status information when accessed during write/erase modes. If a CPU reset occurs with no flash memory reset, proper CPU initialization would not occur because the flash memory would be providing the status information instead of array data. These flash memories allow proper CPU initialization following a system reset through the use of the  $\overline{RP}$  input. In this application  $\overline{RP}$  is controlled by the same  $\overline{RESET}$  signal that resets the system CPU.