# H0541 H0542

# Parallel Input Dot Matrix LCD Driver

Industrial Electronics Group

#### DESCRIPTION

Hughes 0541 and 0542 are a set of CMOS/LSI circuits which drive a dot matrix LCD display under microcomputer control. The <u>intended</u> display is a 5 x 7 or 5 x 8 alphanumeric dot matrix with nearly any number of characters. Other matrix displays, such as games and custom arrays, could also be driven by this set of circuits.

The 0541 is organized as 8 rows x 23 columns, and thus can handle up to four characters by itself. The 0542 is organized as 0 rows x 32 columns and is used in addition to the 0541 when more than 23 columns are required. Data is input 4 bit parallel to minimize the time required to load in data. This circuit drives (using a multiplexed scheme) the display with proper voltage level AC waveforms, but does not handle refresh or character encoding. This results in lower parts cost and greater design flexibility, but puts more burden on the microcomputer.

The 0541 and 0542 are available in a 40 lead hermetic dual-in-line ceramic package (D suffix), plastic package (P suffix), cerdip (Y suffix) or leadless chip carrier (L suffix). Devices in chip form (H suffix) are available upon request.

#### **FEATURES**

- Direct drive of matrix LCDs

- Cascadable for larger displays

- On chip oscillator

- CMOS construction for:

Wide supply voltage range

Low power operation

High noise immunity

Wide temperature range

- CMOS, NMOS, and PMOS compatible inputs

- Flexible organization allows arbitrary display patterns

- Interrupt Output to request data from microcomputer

# 0541 PIN CONFIGURATION

#### 0542 PIN CONFIGURATION

| +V === | 1 ● | <u> </u> | 40 | ightharpoons | С | 0   |

|--------|-----|----------|----|--------------|---|-----|

| LCDФ □ | 2   |          | 39 | $\vdash$     | С | 1   |

| GND 🗀  | 3   |          | 38 |              | С | 2   |

| CLK 🖂  | 4   |          | 37 | Ы            | С | 3   |

|        | 5   |          | 36 |              | С | 4   |

| D1 🗔   | 6   |          | 35 |              | Č |     |

| D 2 C  | 7   |          | 34 | $\vdash$     | Č |     |

| D 3 C  | 8   |          | 33 |              | Č | -   |

| C 31 🖂 | 9   |          | 32 |              | č |     |

| C 30 🖂 | 10  |          | 31 |              | č |     |

| C 29 🗀 | 11  |          | 30 |              |   | 10  |

| C 28 🖂 | 12  |          | 29 |              |   | 11  |

| C 27 🗀 | 13  |          | 28 | $\equiv$     | č |     |

| C 26 🖂 | 14  |          | 27 | =            | Č |     |

| C 25   | 15  |          | 26 | $\equiv$     | Č | _   |

| C 24 🖂 | 16  |          | 25 | $\equiv$     | C |     |

| C 23   | 17  |          | 24 | $\equiv$     | č | -   |

| C 22   | 18  |          | 23 | =            | C |     |

| C 21   | 19  |          | 22 | =            | č |     |

| C 20   | 20  |          | 21 |              |   | 19  |

|        |     |          | نت |              | _ | , 5 |

|        |     |          |    |              |   |     |

# **ABSOLUTE MAXIMUM RATINGS**

Inputs ..... + V<sub>DD</sub> - 17 to + V<sub>DD</sub> + .3 volts

Power Dissipation ..... 250 mW

**Operating Temperature**

Ceramic Package

— 55 to + 125°C

Plastic Package

— 40 to + 85°C

Storage Temperature

— 65 to + 125°C

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ and $V_{DD} = 5V$ unless otherwise noted.

| PARAMETER                                                                        | SYMBOL                 | CONDITION                                              | MIN.                                            | MAX.                                               | UNITS                       |

|----------------------------------------------------------------------------------|------------------------|--------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|-----------------------------|

| Supply Voltage<br>Supply Current                                                 | V <sub>DD</sub>        |                                                        | 3                                               | 12<br>600                                          | V<br>μΑ                     |

| Input High Level Input Low Level Input Leakage Input Capacitance                 | VIH<br>VIL<br>IL<br>C1 |                                                        | .75V <sub>DD</sub><br>V <sub>DD</sub> —15       | V <sub>DD</sub><br>.25V <sub>DD</sub><br>5<br>5    | V<br>V<br>µA<br>pf          |

| Row Output High<br>Row Output Low<br>Row Output Unselected                       | VOH<br>VOL<br>VOM      |                                                        | V <sub>DD</sub> 05<br>0<br>.5V <sub>DD</sub> 05 | V <sub>DD</sub><br>.05<br>.5V <sub>DD</sub> +.05   | V<br>V                      |

| Column Output High<br>Column Output Low                                          | VOH<br>VOL             |                                                        | .68V <sub>DD</sub> 05<br>.32V <sub>DD</sub> 05  | .68V <sub>DD</sub> +.05<br>.32V <sub>DD</sub> +.05 | V<br>V                      |

| Row and Column Output Impedance Interrupt Output Impedence                       | RON<br>RON             | 1 <u>L</u> = 10μΑ<br>1 <u>L</u> = 100μΑ                |                                                 | 30<br>1                                            | <b>Κ</b> Ω                  |

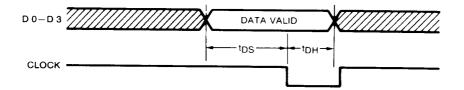

| Clock Rate Data in Setup Time Data in Hold Time LCD of to Interrupt Output Delay | f<br>tDS<br>tDH<br>tD  | Data change to clock fall<br>Clock fall to data change | DC<br>300<br>150<br>300                         | 1.0                                                | MHz<br>nsec<br>nsec<br>nsec |

| LCDФ High Level<br>LCDФ Low Level<br>LCDФ Input Impendence                       | VIH<br>VIL<br>RIN      |                                                        | .9V <sub>DD</sub><br>0<br>1                     | V <sub>DD</sub><br>.1V <sub>DD</sub><br>3          | V<br>V<br>MΩ                |

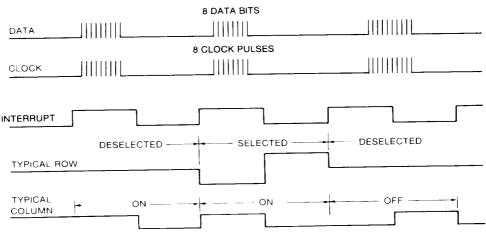

#### **TYPICAL WAVEFORMS**

96

TIMING DIAGRAM H0541/0542

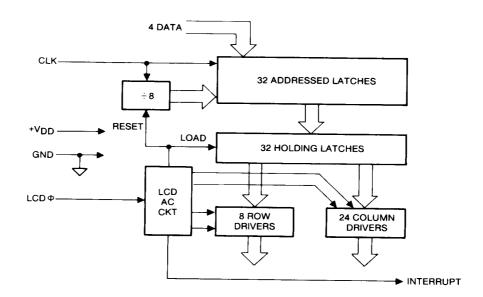

## **BLOCK DIAGRAM**

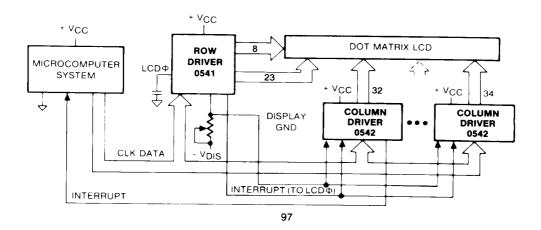

# TYPICAL SYSTEM BLOCK DIAGRAM

### **OPERATING NOTES**

- The addressed latches load when clock is high.

- 2. A logic 1 on Data In selects a row or causes a segment to be visible.

- A parallel transfer of data from the addressed latches register to the holding latches occurs upon the rising edge of Interrupt Output. Also, the ÷8 counter is reset.

- Row waveforms are out of phase with Interrupt Output if selected and at midpoint voltage otherwise. Levels are VDD, 0, and VDD/2.

- Column waveforms are in phase with Interrupt Output if selected and are out of phase if not selected. Levels are .32 VDD and .68 VDD.

- 6. The intended mode of operation is as follows:

- a. Interrupt Output frequency is the minimum no flicker frequency (~30Hz) times the number of backplanes utilized.

- b. Interrupt Output is exactly 50% duty cycle (to keep DC off the display) and is synchronized with loading the data from addressed latches to holding latches.

- c. In between each Interrupt Output rising edge, 4 bit parallel data is clocked in with 8 clock pulses for the next time slot to await the next Interrupt Output rising edge, which causes the parallel transfer.

- d. The Interrupt Output goes to the microcomputer and is treated as a refresh request, or else the microcomputer drives the LCDΦ input.

- e. Backplanes are addressed sequentially and individually.

- The LCDΦ pin can be used in two modes, driven or oscillating. If LCDΦ is driven, the Interrupt Output will follow it. If the LCDΦ

- pin is allowed to oscillate, its frequency is inversely proportional to capacitance and the Interrupt Output waveform has a frequency half that of the oscillator itself. The approximate relationship is fout (KHz) = 380/ c (pf). The frequency is nearly independent of supply voltage.

- 8. To cascade units, either connect Interrupt Output of one circuit to LCDΦ of all other circuits (thus one capacitor provides frequency control for all circuits) or connect LCDΦ of all circuits to a common driving signal. Then tie all corresponding data inputs together and clock each circuit individually when its data is on the bus. In the case of two driver circuits and an 8 bit microcomputer, the clocks could be common and each Data In tied to a different line of the data bus.

- 9. There are two obvious signal races to be avoided:

- a. Changing data when clock is falling, and

- **b.** Allowing Interrupt Output rising edge to be very close to clock falling edge.

- 10. If supply voltage is altered to optimize LCD contrast or for temperature compensation, it is best to tie all positive supply terminals in common and vary the negative supply. This prevents inadvertently forward biasing diodes.

- 11. Input order of 0541.

| Citi Pulse | 1  | 2   | 8   | * 4 |      |      |      | •    |

|------------|----|-----|-----|-----|------|------|------|------|

| Data 0     | R0 | R4  | C 0 | C 4 | С8   | C 12 | C 16 | C 20 |

| Data 0     | R1 | R 5 | C 1 | C 5 | C 9  | C 13 | C 17 | C 21 |

| Data 2     | R2 | R6  | C 2 | C 6 | C 10 | C 14 | C 18 | C 22 |

| Data 3     | R3 | R7  | C 3 | C 7 | C 11 | C 15 | C 19 |      |

12. Input order of 0542 is similar, but starts at C0 (Pulse 1, Data 0) and ends at C 31 (Pulse 8, Data 3).

Information furnished by Hughes is believed to be accurate and reliable. However, no responsibility is assumed by Hughes for its use; nor for any infringements or patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Hughes.

U.S.A.:

Hughes Semiconductor Division

500 Superior Avenue, Box H

Newport Beach, CA 92658-8903

Tele: (714) 759-2727 TWX: 910-596-1374 HACSSPD NPBH

EUROPE: Hughes Microelectronics Limited Clive House, 12/18 Queens Road, Weybridge, Surrey, England Tele: 0932 47262 TWX: 929727

or— Schmaedelstr. 22, 8000 Munich 60, Germany Tele: 49-89-834-7088 Telex: 5213856 HSPD 11/85 Printed in U.S.A.