CMOS LSI

### PARALLEL PROGRAMMED PLL FREQUENCY SYNTHESIZER

#### PRODUCT DESCRIPTION

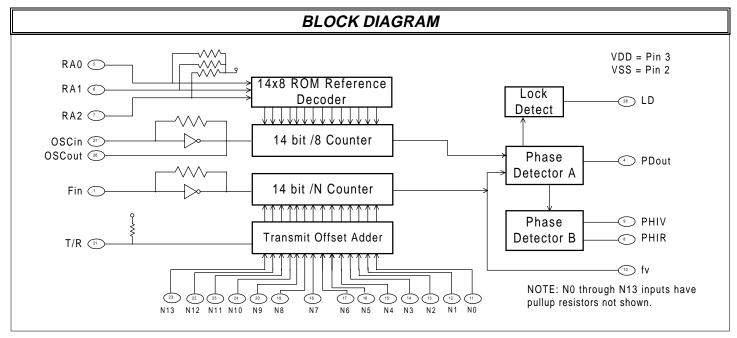

The IMI145151 is a member of a family of phaselock loop synthesizer ICs from International Microcircuits. The IMI145151 is an improved version of the Motorola MC145151 and will provide a synthesizer with noticeably improved performance.

The IMI145151 is programmed with parallel input data lines. Since it does not require a microcontroller as serial and bus programmed units do, the IMI145151 is an excellent choice for synthesizers requiring independence from digital controllers. Such applications include fixed local oscillator signals, whose tuning never changes, and signal sources, which have few operating frequencies.

Blocks in the IMI145151 include a programmable feedback divider, a reference divider, phase detector, and charge pump. The reference divider is programmed by three select lines to one of eight ROM encoded values. Both counter inputs are biased for maximum sensitivity to sinewave input signals. The reference divider input is also configured to operate as a crystal oscillator if desired.

The IMI145151 has a Type IV phase frequency detector which has eliminated by the design the inherent dead zone which causes crossover distortion at the critical center lock point. the IMI circuitry enables consistent low noise loop designs using the simple single ended charge pump output. Differential charge pump outputs are also provided for those who require a more sophisticated differential active loop filter design.

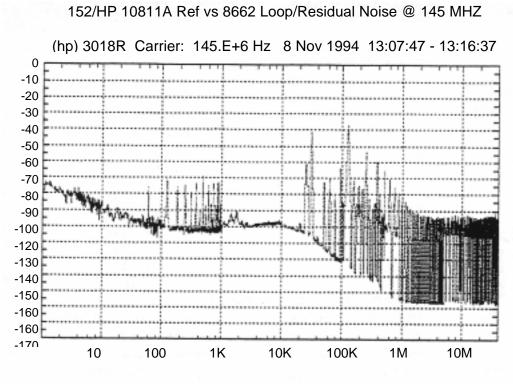

Performance improvements are in the operating bandwidth and phase detector noise floor. With its extremely low phase noise foor and wider input bandwith, prescaler ratios can be minimized to allow wide loop bandwidths for faster settling and lower phase noise.

#### **PRODUCT FEATURES**

- >200 Mhz typical input frequency.

- -163 dBc/Hz total phase noise floor.

- No dead zone, by design.

- Unambiguous PLL acquisition.

- 8 user-selectable reference divider ratios: 8, 128, 256, 512, 1024, 2048, 2410, 8192.

- Lock detect signal.

- 14 bit N counter. Divider range = 3 to 16383.

- On- or off-chip reference oscillator operation.

- 3-volt and 5-volt characterizations.

CMOS LSI

### PARALLEL PROGRAMMED PLL FREQUENCY SYNTHESIZER

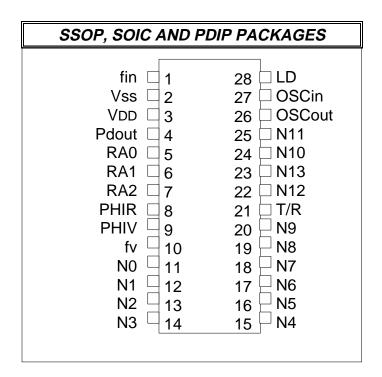

|              | PIN DESCRIPTIONS   |                                                                                                                                                                                                                                                              |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

|--------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin No.      | Name               | Description                                                                                                                                                                                                                                                  |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 1            | Fin                | RF input signal. Applied to both the N and A counters. This signal is intended to be AC coupled for low level sinewave input signals. For CMOS logic level input signals, DC coupling can be used.                                                           |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 2            | Vss                | Circuit ground.                                                                                                                                                                                                                                              |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 3            | Vdd                | Circuit-positive power supply.                                                                                                                                                                                                                               |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 4            | Pdout              | Single-ended charge pump output, usually used with passive loop filters. This signal operates according to the following:  Frequency fv>fr at the phase detector: negative pulses.                                                                           |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

|              |                    |                                                                                                                                                                                                                                                              |                                                                           | detector: positive   |                                                                        |  |  |  |  |  |  |  |

|              |                    |                                                                                                                                                                                                                                                              |                                                                           | e detector: high-im  |                                                                        |  |  |  |  |  |  |  |

| 5            | RA0                |                                                                                                                                                                                                                                                              |                                                                           |                      | p resistors are included on each of                                    |  |  |  |  |  |  |  |

| 6            | RA1                |                                                                                                                                                                                                                                                              |                                                                           |                      | ill remain at a logic ONE.                                             |  |  |  |  |  |  |  |

| 7            | RA2                | The reference divid                                                                                                                                                                                                                                          |                                                                           | -                    |                                                                        |  |  |  |  |  |  |  |

|              |                    | RA2<br>0                                                                                                                                                                                                                                                     | RA1                                                                       | RA0<br>0             | Reference Divider Ratio<br>8                                           |  |  |  |  |  |  |  |

|              |                    | 0                                                                                                                                                                                                                                                            | 0                                                                         | 1                    | 128                                                                    |  |  |  |  |  |  |  |

|              |                    | 0                                                                                                                                                                                                                                                            | 1                                                                         | Ö                    | 256                                                                    |  |  |  |  |  |  |  |

|              |                    | Ö                                                                                                                                                                                                                                                            | 1                                                                         | 1                    | 512                                                                    |  |  |  |  |  |  |  |

|              |                    | 1                                                                                                                                                                                                                                                            | 0                                                                         | 0                    | 1024                                                                   |  |  |  |  |  |  |  |

|              |                    | 1                                                                                                                                                                                                                                                            | 0                                                                         | 1                    | 2048                                                                   |  |  |  |  |  |  |  |

|              |                    | 1                                                                                                                                                                                                                                                            | 1                                                                         | 0                    | 2410                                                                   |  |  |  |  |  |  |  |

|              |                    | 1                                                                                                                                                                                                                                                            | 1                                                                         | 1                    | 8192                                                                   |  |  |  |  |  |  |  |

| 8<br>9<br>10 | PHIR<br>PHIV<br>fv |                                                                                                                                                                                                                                                              | put. This signa                                                           |                      | the feedback frequency is too low. the feedback frequency is too high. |  |  |  |  |  |  |  |

| 11           | NO                 | LSB of the N counter                                                                                                                                                                                                                                         |                                                                           | a input bits. Pull-u | p resistor included.                                                   |  |  |  |  |  |  |  |

| 12           | N1                 |                                                                                                                                                                                                                                                              |                                                                           |                      | II-up resitor included.                                                |  |  |  |  |  |  |  |

| 13           | N2                 |                                                                                                                                                                                                                                                              |                                                                           |                      | II-up resitor included.                                                |  |  |  |  |  |  |  |

| 14           | N3                 | LSB+3 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                     |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 15           | N4                 | LSB+4 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                     |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 16           | N5                 | LSB+5 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                     |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 17           | N6                 | LSB+6 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                     |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 18           | N7                 | LSB+7 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                     |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 19           | N8                 | LSB+8 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                     |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 20           | N9                 | LSB+9 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                     |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 21           | T/R                | This input control an offset that can be added to the programming inputs. Thisoffset is fixed at 856 when T/R is low. When T/R is high, there is no offset added. A pull-up resistor is included.                                                            |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 22           | N12                | LSB+12 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                    |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 23           | N13                | LSB+13 of the N counter programming input bits. Pull-up resitor included.                                                                                                                                                                                    |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 24           | N10                |                                                                                                                                                                                                                                                              | LSB+10 of the N counter programming input bits. Pull-up resitor included. |                      |                                                                        |  |  |  |  |  |  |  |

| 25           | N11                |                                                                                                                                                                                                                                                              |                                                                           |                      | ull-up resitor included.                                               |  |  |  |  |  |  |  |

| 26           | OSCout             | Reference signal or                                                                                                                                                                                                                                          |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 27           | OSCin              |                                                                                                                                                                                                                                                              |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

| 28           | LD                 | AC-coupled reference signal input or input to the oscillator inverter.  Lock detect output. When the PLL is locked, this signal will be essentially HIGH, with very narrow negative spikes at the phase detection frequency. If the PLL is out of lock, this |                                                                           |                      |                                                                        |  |  |  |  |  |  |  |

|              |                    | signal will pusle LO                                                                                                                                                                                                                                         | VV.                                                                       |                      |                                                                        |  |  |  |  |  |  |  |

CMOS LSI

### PARALLEL PROGRAMMED PLL FREQUENCY SYNTHESIZER

#### **MAXIMUM RATINGS**

Voltage Relative to VSS: -0.3V to 7V

Voltage Relative to VDD: 0.3V

Storage Temperature: -65°C to 150°C

Ambient Temperature: -55°C to 125°C

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precaustions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:

Vss<(Vin or Vout)<V<sub>DD</sub>

Unused inputs must always be tied to an appropriate logic voltage level (either Vss or VDD).

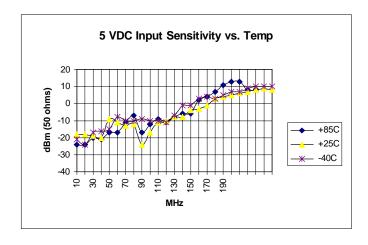

|                | PLL OPERATING CHARACTERISTICS       |        |                 |             |      |      |      |             |              |      |      |     |             |      |            |                        |

|----------------|-------------------------------------|--------|-----------------|-------------|------|------|------|-------------|--------------|------|------|-----|-------------|------|------------|------------------------|

| VDD = 5 VOLTS  |                                     |        |                 |             |      |      |      |             |              |      |      |     |             |      |            |                        |

|                |                                     |        |                 | -40°C 0°C   |      | 25°C |      |             | 70°C         |      | 85°C |     |             |      |            |                        |

| Characteristic |                                     | Symbol |                 | Min         | Max  | Min  | Max  | Min         | Тур          | Max  | Min  | Max | Min         | Max  | Unit       | Conditions             |

|                | Operating                           | Fin    | Sin             | 210         | -    | 200  | -    | 200         | 250          | -    | 180  | -   | 180         | -    | MHz        |                        |

|                | Frequency                           |        | Square          | 210         | -    | 200  | -    | 200         | 250          | -    | 180  | -   | 180         | -    | MHz        |                        |

|                |                                     | Fosc   |                 |             |      |      |      |             |              |      |      |     |             |      | MHz        |                        |

| Dynamic        | Synthesizer<br>Phase Noise<br>Floor | PDNF   |                 |             |      |      |      |             | -160         |      |      |     |             |      | dBc/<br>Hz |                        |

|                | Pin                                 | Cin    |                 | -           | 10   |      |      | -           | 6            | 10   |      |     | -           | 10   | pF         |                        |

|                | Capacitance                         | Cout   |                 | -           | 10   |      |      | -           | 6            | 10   |      |     | -           | 10   | pF         |                        |

|                | Input                               | VIL    |                 | 1           | 1.5  | -    | 1.5  | -           | 2.75         | 1.5  | -    | 1.5 | -           | 1.5  | Vdc        |                        |

|                | Voltages                            | VIH    |                 | 3.5         | -    | 3.5  | -    | 3.5         | 2.75         | -    | 3.5  | -   | 3.5         | -    | Vdc        |                        |

|                | Output                              | VOL    |                 | -           | 0.05 | -    | 0.05 | -           | 0.0          | 0.05 | -    | .05 | -           | 0.05 | Vdc        |                        |

|                | Voltages                            | VOH    |                 | 4.95        | -    | 4.95 | -    | 4.95        | 5.0          | -    | 4.95 | -   | 4.95        | -    | Vdc        |                        |

| Static         |                                     | IOL    | Logic           | 2.4         | -    |      |      | 2.0         | 2.8          | -    |      |     | 1.6         | -    |            | VOL = 0.40             |

|                | Output                              | IOH    | OSCout          | 1.2<br>-2.4 | -    |      |      | 1.0<br>-2.0 | 1.4<br>-2.8  | -    |      |     | 0.8<br>-1.6 | -    | mA<br>mA   | VOH = 4.0              |

|                | Current                             | IOH    | Logic<br>OSCout | -2.4        | -    | -    |      | -2.0        | -2.8<br>-1.4 | -    |      |     | -0.8        | -    | mA<br>mA   | VOH = 4.0<br>VOH = 4.0 |

|                | Charge Pump<br>Current              |        | OSCOUL          | -1.2        | -    |      |      | -1.0        | 12.4         | -    |      |     | -0.6        | -    | mA         | Vdd = 5.0V             |

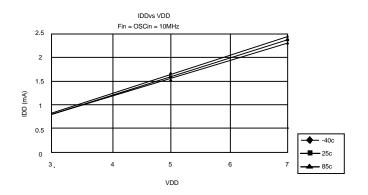

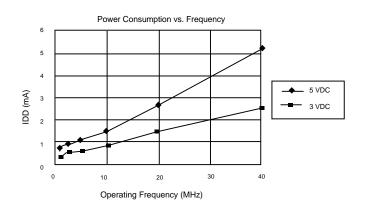

|                | Supply                              | IDD    |                 |             |      |      |      |             |              |      |      |     |             |      | mA         | Fosc=Fin=<br>10 MHz    |

|                | Currents                            | ISB    |                 | -           | 150  |      |      | -           | 40           | 150  |      |     | -           | 150  | uA         | Fosc=Fin=0             |

|                |                                     | IPU    |                 |             |      |      |      |             | 50           |      |      |     |             |      | uA         | VIL = 0                |

CMOS LSI PARALLEL PROGRAMMED PLL FREQUENCY SYNTHESIZER

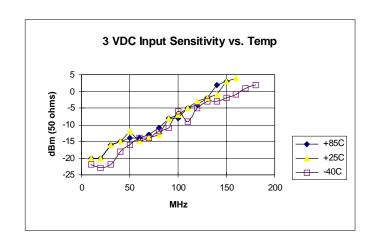

|         | PLL OPERATING CHARACTERISTICS       |      |        |       |      |      |      |      |      |      |      |      |      |      |            |                         |

|---------|-------------------------------------|------|--------|-------|------|------|------|------|------|------|------|------|------|------|------------|-------------------------|

|         | VDD = 3 VOLTS                       |      |        |       |      |      |      |      |      |      |      |      |      |      |            |                         |

|         |                                     |      |        | -40°C |      | 0°C  |      | 25°C |      | 70°C |      | 85°C |      |      |            |                         |

| Chara   | Characteristic                      |      | Symbol |       | Max  | Min  | Max  | Min  | Тур  | Max  | Min  | Max  | Min  | Max  | Unit       | Conditions              |

|         | Operating                           | Fin  | Sin    | 160   | -    | 140  | -    | 130  | 150  | -    | 120  | -    | 110  | -    | MHz        |                         |

|         | Frequency                           |      | Square | 160   | -    | 140  | -    | 130  | 150  | -    | 120  | -    | 110  | -    | MHz        |                         |

|         |                                     | Fosc |        |       |      |      |      |      |      |      |      |      |      |      | MHz        |                         |

| Dynamic | Synthesizer<br>Phase Noise<br>Floor | PDNF |        |       |      |      |      |      | -155 |      |      |      |      |      | dBc/<br>Hz |                         |

|         | Pin                                 | Cin  |        | -     | 10   |      |      | -    | 6    | 10   |      |      | -    | 10   | pF         |                         |

|         | Capacitance                         | Cout |        | -     | 10   |      |      | -    | 6    | 10   |      |      | -    | 10   | pF         |                         |

|         | Input                               | VIL  |        | -     | 0.9  |      |      | -    | 1.35 | 0.9  |      |      | -    | 0.9  | Vdc        |                         |

|         | Voltages                            | VIH  |        | 2.1   | -    |      |      | 2.1  | 1.65 | -    |      |      | 2.1  | -    | Vdc        |                         |

|         | Output                              | VOL  |        | -     | 0.05 | -    | 0.05 | -    | 0.0  | 0.05 | -    | .05  | -    | 0.05 | Vdc        |                         |

|         | Voltages                            | VOH  |        | 2.95  | -    | 2.95 | -    | 2.95 | 3.0  | -    | 2.95 | -    | 2.95 | -    | Vdc        |                         |

| Static  | _                                   | IOL  | Logic  | 1.6   | -    |      |      | 1.4  | 2.0  | -    |      |      | 0.8  | -    |            | VOL = 0.30              |

|         | Output                              |      | OSCout | 0.8   | -    |      |      | 0.7  | 1.0  | -    |      |      | 0.4  | -    | mA         |                         |

|         | Current                             | IOH  | Logic  | -1.6  | -    |      |      | -1.4 | -1.0 | -    |      |      | -0.8 | -    | mA         | VOH = 2.4               |

|         | Charge Pump                         |      | OSCout | -0.8  | -    |      |      | -0.7 | -1.0 | -    |      |      | -0.4 | -    | mA         | VOH = 2.4<br>Vdd = 3.0V |

|         | Charge Pump<br>Current              |      |        |       |      |      |      |      | 5.0  |      |      |      |      |      | mA         |                         |

|         | Supply                              | IDD  |        |       |      |      |      |      |      |      |      |      |      |      | mA         | Fosc=Fin=<br>10 MHz     |

|         | Currents                            | ISB  |        | -     | 150  |      |      | -    | 40   | 150  |      |      | -    | 150  | uA         | Fosc=Fin=0              |

|         |                                     | IPU  |        |       |      |      |      |      | 30   |      |      |      |      |      | uA         | VIL = 0                 |

CMOS LSI PARALLEL PROGRAMMED PLL FREQUENCY SYNTHESIZER

#### PHASE NOISE FLOOR

Fosc = 1 Mhz Fref = 125 Khz fin = 145 Mhz N = 1160 Measured floor @ 500 Hz = -102 dBc/Hz -20 log (N) = - 61 dB - 163 dBc/Hz

CMOS LSI

### PARALLEL PROGRAMMED PLL FREQUENCY SYNTHESIZER

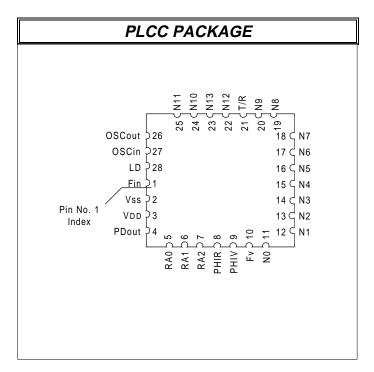

#### **CONNECTION DIAGRAMS**

CMOS LSI

### PARALLEL PROGRAMMED PLL FREQUENCY SYNTHESIZER

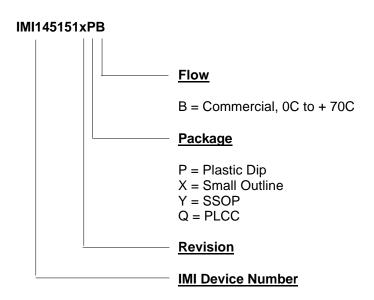

| ORDERING INFORMATION |              |                          |  |  |  |  |  |  |  |

|----------------------|--------------|--------------------------|--|--|--|--|--|--|--|

| Part Number          | Package Type | Production Flow          |  |  |  |  |  |  |  |

| IMI145151xPB         | Plastic Dip  | Commercial, 0°C to +70°C |  |  |  |  |  |  |  |

| IMI145151xXB         | SOIC         | Commercial, 0°C to +70°C |  |  |  |  |  |  |  |

| IMI145151xYB         | SSOP         | Commercial, 0°C to +70°C |  |  |  |  |  |  |  |

| IMI145151xQB         | PLCC         | Commercial, 0°C to +70°C |  |  |  |  |  |  |  |

<sup>\*</sup>Please contact factory for other options.

**NOTE**: The "x" following the IMI Device Number denotes the device revision. The ordering part number is formed by a combination of device number, device revision, package style, and screening as shown below.

Marking: Example: IMI

145151xPB Date Code, Lot #