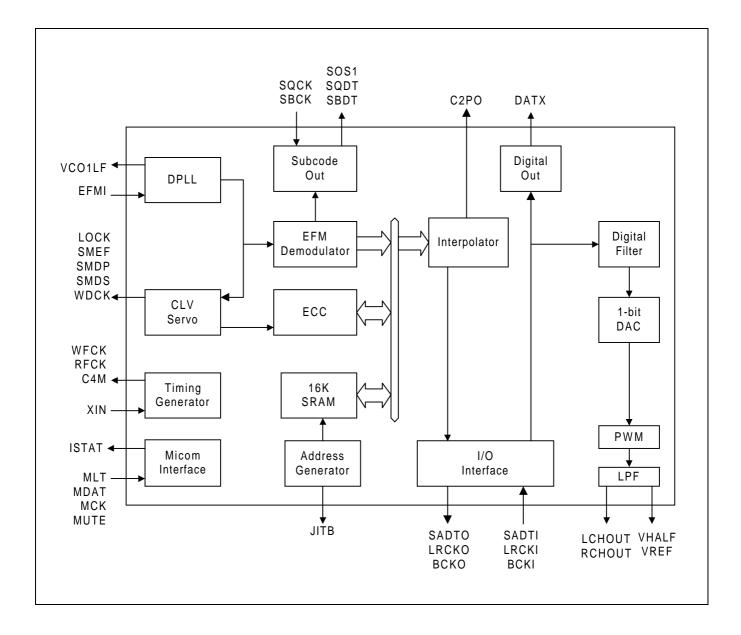

# INTRODUCTION

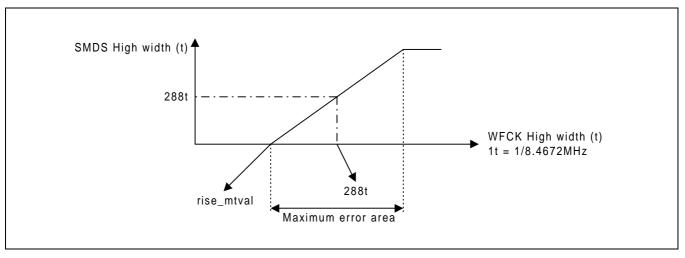

S5L9290X02 is a signal processing LSI for the Internet Audio (CD-MP3 etc) interface only. Digital processing function (EFM demodulation, error correction), spindle motor servo processing, wide capture range DPLL and 1-bit DAC for the Internet Audio CD player are installed in S5L9290X02.

# FEATURES

- Signal processing part

- EFM data demodulation

- Frame sync detection, protection, insertion

- Sub code data processing (Q data CRC check, Q data register installed)

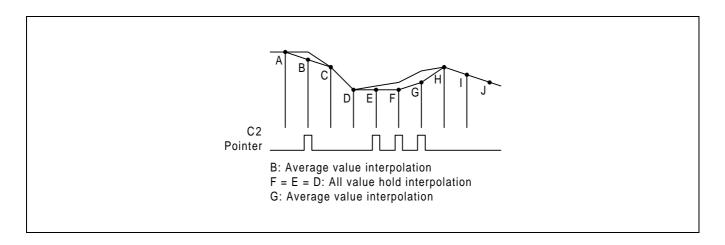

- Error correction (C1: 2 error correction, C2: 4 erasure correction)

- Installed 16K SRAM for De-interleave

- Interpolation

- Digital audio interface

- CLV servo control (X1, X2)

- Wide capture range digital PLL ( ± 50%)

- Digital filter, DAC part

- 4 times over sampling digital filter

- Digital de-emphasis (can be process the 32kHz, 44.1kHz, 48kHz)

- Sigma-delta stereo DAC installed

- Audio L.P.F installed

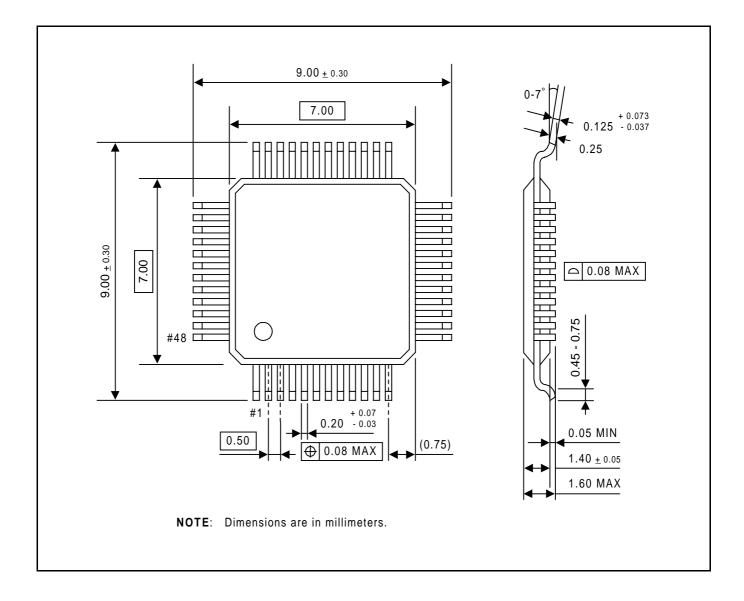

# **ORDERING INFORMATION**

| Device          | Package      | Supply Voltage                                                 | Operating Temperature |

|-----------------|--------------|----------------------------------------------------------------|-----------------------|

| S5L9290X02-E0R0 | 48-LQFP-0707 | 2.7 to 3.3V (Analog, Internal logic)<br>2.7 to 5.5V (I/O port) | -20 to +75°C          |

# **BLOCK DIAGRAM**

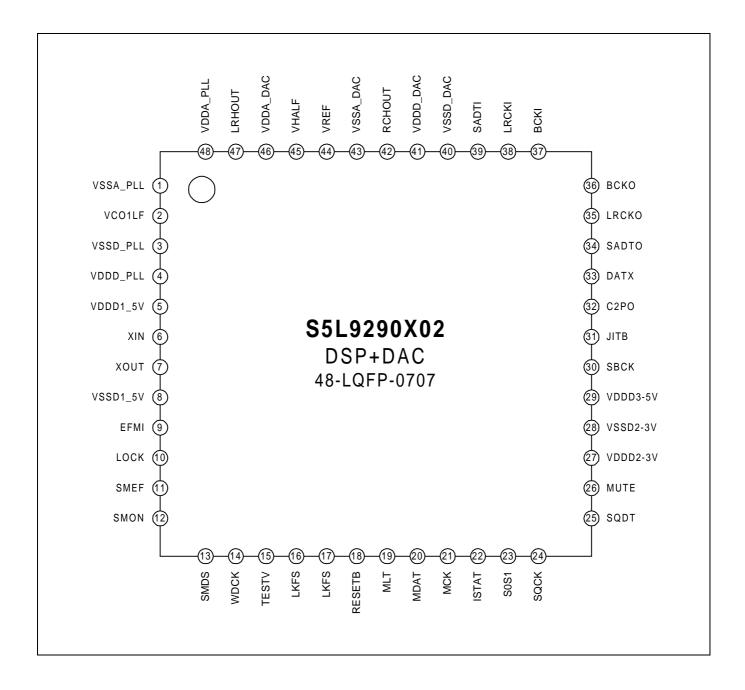

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| NO. | NAME     | I/O | Pin Description                                                     |

|-----|----------|-----|---------------------------------------------------------------------|

| 1   | VSSA_PLL | -   | Analog Ground for DPLL                                              |

| 2   | VCO1LF   | 0   | Pump out for VCO1                                                   |

| 3   | VSSD_PLL | -   | Digital Ground Separated Bulk Bias for DPLL                         |

| 4   | VDDD_PLL | -   | Digital Power Separated Bulk Bias for DPLL (3V Power)               |

| 5   | VDDD1-5V | -   | Digital Power (5V Power, I/O PAD)                                   |

| 6   | XIN      | I   | X'tal oscillator input (16.9344MHz)                                 |

| 7   | XOUT     | 0   | X'tal oscillator output                                             |

| 8   | VSSD1    | -   | Digital Ground (I/O PAD)                                            |

| 9   | EFMI     | I   | EFM signal input                                                    |

| 10  | LOCK     | 0   | CLV Servo locking status output                                     |

| 11  | SMEF     | 0   | LPF time constant control of the spindle servo error signal         |

| 12  | SMDP     | 0   | Phase control output for Spindle Motor drive                        |

| 13  | SMDS     | 0   | Speed control output for Spindle Motor drive                        |

| 14  | WDCK     | 0   | Word clock output (Normal Speed : 88.2kHz, Double Speed : 176.4kHz) |

| 15  | TESTV    | I   | Various Data/Clock Input                                            |

| 16  | LKFS     | 0   | The Lock status output of frame sync                                |

| 17  | C4M      | 0   | 4.2336MHz clock output                                              |

| 18  | RESETB   | I   | System Reset at 'L'                                                 |

| 19  | MLT      | I   | Latch signal input from Micom                                       |

| 20  | MDAT     | I   | Serial data input from Micom                                        |

| 21  | MCK      | I   | Serial data receiving clock input from Micom                        |

| 22  | ISTAT    | 0   | The internal status output to Micom                                 |

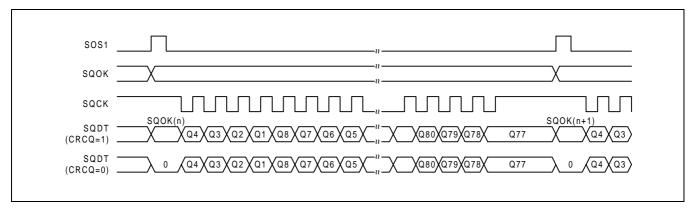

| 23  | S0S1     | 0   | Subcode sync signal(S0+S1) output                                   |

| 24  | SQCK     | I   | Subcode-Q data transfering bit clock input                          |

# PIN DESCRIPTION(Continued)

| NO. | NAME     | I/O | Function Description                          |

|-----|----------|-----|-----------------------------------------------|

| 25  | SQDT     | 0   | Subcode-Q data serial output                  |

| 26  | MUTE     | Ι   | System mute at 'H'                            |

| 27  | VDDD2-3V | -   | Digital Power (3V Power, Internal Logic)      |

| 28  | VSSD2    | -   | Digital Ground (Internal Logic)               |

| 28  | VDDD3-5V | -   | Digital Power (5V Power, I/O PAD)             |

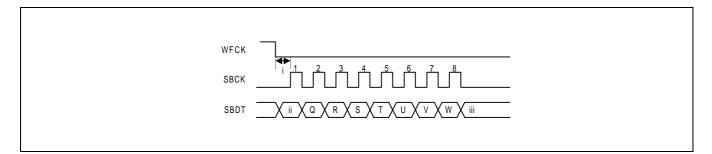

| 30  | SBCK     | Ι   | Subcode data transfering bit clock            |

| 31  | JITB     | 0   | Internal SRAM jitter margin status output     |

| 32  | C2PO     | 0   | C2 pointer output                             |

| 33  | DATX     | 0   | Digital audio data output                     |

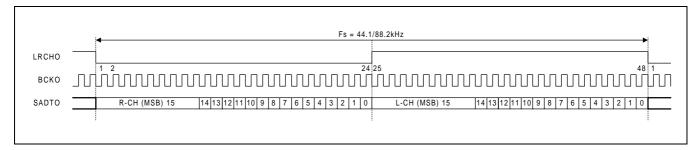

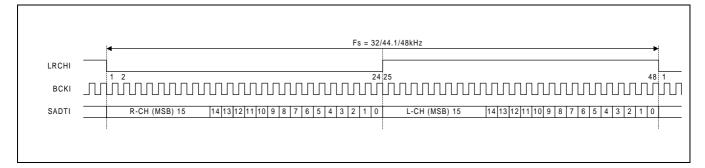

| 34  | SADTO    | 0   | Serial audio data output (48 slot, MSB first) |

| 35  | LRCKO    | 0   | Channel clock output                          |

| 36  | ВСКО     | 0   | Bit clock output                              |

| 37  | BCKI     | Ι   | Bit clock input                               |

| 38  | LRCKI    | Ι   | Channel clock input                           |

| 39  | SADTI    | Ι   | Serial audio data input (48 slot, MSB first)  |

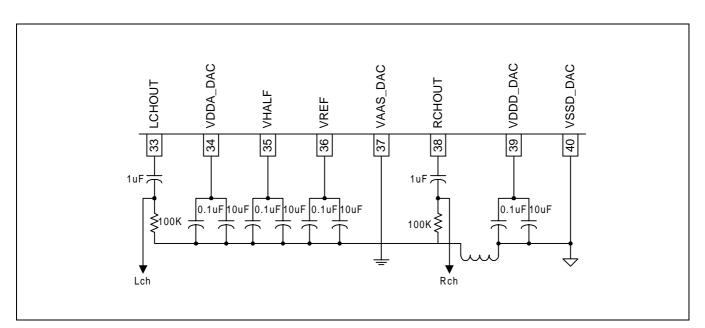

| 40  | VSSD_DAC | -   | Digital Ground for DAC                        |

| 41  | VDDD_DAC | -   | Digital Power for DAC (3V Power)              |

| 42  | RCHOUT   | 0   | Right-Channel audio output through DAC        |

| 43  | VSSA_DAC | -   | Analog Ground for DAC                         |

| 44  | VREF     | 0   | Referance Voltage output for bypass           |

| 45  | VHALF    | 0   | Referance Voltage output for bypass           |

| 46  | VDDA_DAC | -   | Analog Power for DAC (3V Power)               |

| 47  | LCHOUT   | 0   | Left-Channel audio output through DAC         |

| 48  | VDDA_PLL | -   | Analog Power for PLL (3V Power)               |

# MAXIMUM ABSOLUTE RATINGS

| Item                  | Symbol           | Rating                                                       | Unit |

|-----------------------|------------------|--------------------------------------------------------------|------|

| Power supply voltage  | V <sub>DD</sub>  | 3V: -0.3 to 3.8<br>5V: -0.3 to 7.0                           | V    |

| Input supply voltage  | VI               | 3V I/O: -0.3 to V <sub>DD</sub> + 0.3<br>5V I/O: -0.3 to 5.5 | V    |

| Operating temperature | T <sub>OPR</sub> | -20 to 75                                                    | °C   |

| Storage temperature   | T <sub>STG</sub> | -40 to 125                                                   | °C   |

# **ELECTRICAL CHARACTERISTICS**

## **OPERATING CONDITION**

| Item                 | Symbol           | Operating Range | Unit |

|----------------------|------------------|-----------------|------|

| Power supply voltage | V <sub>DD</sub>  | 3V: 2.7 to 3.3  | V    |

|                      |                  | 5V: 4.5 to 5.5  |      |

| Operating temp.      | T <sub>OPR</sub> | -20 to 75       | °C   |

# DC CHARACTERISTIC (V<sub>DD</sub> = 3.0V, V<sub>SS</sub> = 0V, Ta = $25^{\circ}C$ )

| ltem                            | Symbol          | Condition  | De  | sign Valu | ies | Unit | Comment  |

|---------------------------------|-----------------|------------|-----|-----------|-----|------|----------|

| item                            | Symbol          | Condition  | Min | Тур       | Max | Unit | Comment  |

| 'H' input voltage               | VIH             |            | 2.4 | -         | -   | V    | (Note 1) |

| 'L' input voltage               | VIL             |            | -   | -         | 0.8 | V    |          |

| 'H' output voltage              | VOH(1)          | IOH = -1mA | 2.4 | -         | -   | V    | (Note 2) |

| 'L' output voltage              | VOL(1)          | IOL = 1mA  | -   | -         | 0.4 | V    |          |

| Input leak current              | ILKG            | VI = 0-VDD | -10 | -         | 10  | uA   | (Note 3) |

| Three state output leak current | I <sub>OZ</sub> | VO = 0-VDD | -10 | -         | 10  | uA   | (Note 4) |

### NOTES:

- 1. Related pins: All input terminal

- 2. Related pins: All output terminal

- 3. Related pins: All input terminal

- 4. Related pins: SMEF, SMDP, SMDS, ISTAT

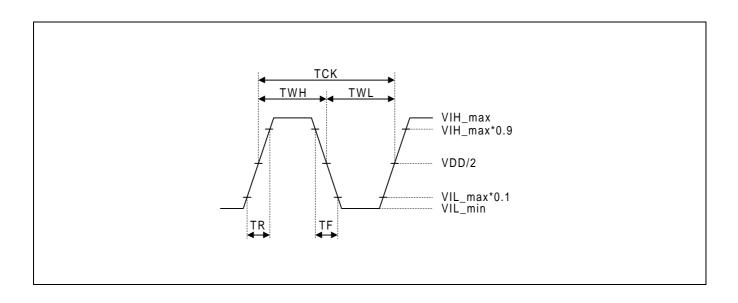

# AC CHARACTERISTIC

# When Pulse is Applied to XIN (Ta = 25°C, VDD = 3.0V, VSS = 0V)

| ltem                  | Symbol | Min | Тур | Max | Unit |

|-----------------------|--------|-----|-----|-----|------|

| 'H' level pulse width | TWH    | 13  | -   | -   | ns   |

| 'L' level pulse width | TWL    | 13  | -   | -   | ns   |

| Pulse frequency       | ТСК    | 26  | -   | -   | ns   |

| Input 'H' level       | VIH    | 2.4 | -   | -   | V    |

| Input 'L' level       | VIL    | -   | -   | 0.8 | V    |

| Rising & falling time | TR,TF  | -   | -   | 10  | ns   |

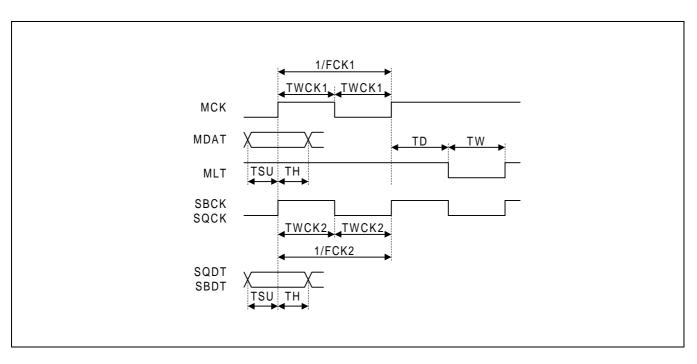

| ltem              | Symbol | Max | Тур | Min  | Unit |

|-------------------|--------|-----|-----|------|------|

| Clock frequency   | FCK1   | 1   | -   | -    | MHz  |

| Clock pulse width | TWCK1  | -   | -   | 500  | ns   |

| Setup time        | TSU    | -   | -   | 300  | ns   |

| Hold time         | TH     | -   | -   | 300  | ns   |

| Delay time        | TD     | -   | -   | 300  | ns   |

| Latch pulse width | TW     | -   | -   | 1000 | ns   |

| SQCK frequency    | FCK2   | 1   | -   | -    | MHz  |

| SQCK pulse width  | TWCK2  | -   | -   | 500  | ns   |

# MCK, MDAT, MLT (Ta = 25°C, VDD = 3.0V, VSS = 0V)

# **DESCRIPTION OF OPERATION**

### **MICOM INTERFACE**

Each command is executed when data and command is input as LSB first according to timing shown in the figure below through MDAT, MCK, and MLT inputs and ISTAT output.

- Address: 8-bit

- Data: 8-bit (writing), 8/16-bit (reading)

| MDAT     | <u> </u> |

|----------|----------|

| мск —    |          |

| MLT —    |          |

| Register | X valio  |

# **DSP Command**

| Command               | Address            |              |               |               | Da          | ata         |             |              |                | ISTAT       |  |

|-----------------------|--------------------|--------------|---------------|---------------|-------------|-------------|-------------|--------------|----------------|-------------|--|

| Command               | Address            | D7           | D6            | D5            | D4          | D3          | D2          | D1           | D0             | pin         |  |

| DPLL control 1        | 10001000<br>(\$88) | WIDE         | PHSE<br>DET   | PHASE<br>GAIN | DLF<br>GAIN | ACC3t       | INC3T       | СОЗТ         | RET<br>REF     | Hi-Z        |  |

| DPLL control 2        | 10001001<br>(\$89) | REF9         | 8[1:0]        | REF9          | 8[1:0]      | MAXTG       | AIN[1:0]    | CAPRAN       | CAPRANGE [1:0] |             |  |

| DPLL control 3        | 10001010<br>(\$8A) | DIVS         | 1 [1:0]       |               | DIVP1 [1:0] |             |             |              |                |             |  |

| DPLL control 4        | 10001100<br>(\$8C) |              |               |               | DIVM        | 1[7:0]      |             |              |                | Hi-Z        |  |

| DPLL control 5        | 10001101<br>(\$8D) | CMD<br>SPLIT | PHASE<br>ONLY | MRAN          | GE[1:0]     | FSREG       | PLL<br>TEST | PLL<br>PWDN1 | -              | Hi-Z        |  |

| Function control      | 10010000<br>(\$90) | CDROM        | FDEEM         | DEEM          | ERA<br>OFF  | C1PNT       | -           | -            | JITM           | EMPH        |  |

| Audio control         | 10010001<br>(\$91) | MUTE         | ZCMT          | ZDENL         | ATTN        | DAC<br>MUTE | VFLGC       | DATX<br>MUTE | DATX<br>OENB   | S0S1        |  |

| Frame Sync<br>control | 10010010<br>(\$92) | FSEL         | [1:0]         | WSEL[1:0]     |             | FSMD [1:0]  |             | -            | -              | LKFS        |  |

| Mode control 1        | 10010011<br>(\$93) | GNR<br>PWDN  | -             | DAC<br>PWDNB  | -           | ECLV        | ECLV<br>PD  | NCLV         | CRCQ           | JITB        |  |

| Mode control 2        | 10010100<br>(\$94) | MSCK<br>SW   | -             | -             | -           | RFCK<br>SW  | -           | -            | JTFRV1         | LOCK        |  |

| CLV gain<br>control   | 10011000<br>(\$98) | OVSPL        | WBN           | WPN           | -           | OVSPL<br>MS | WB          | WP           | GAIN           | EFMFLA<br>G |  |

| CLV mode<br>control   | 10011001<br>(\$99) | UNLO         | CK[1:0]       | CLV<br>IDLE   | PCEN        | CM3         | CM2         | CM1          | CM0            | /(PW≥64)    |  |

| CLV control 1         | 10011010<br>(\$9A) | STRIO        | SMM           | PME           | SME         | PCKS        | EL[1:0]     | PGAI         | N[1:0]         | Hi-Z        |  |

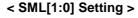

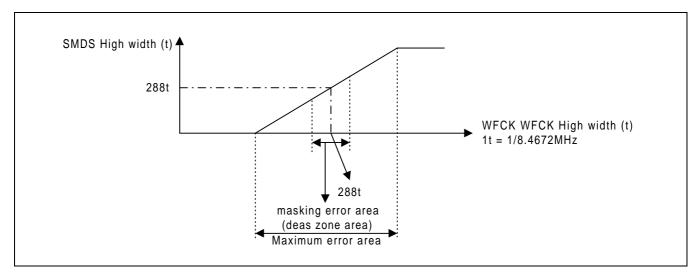

| CLV control 2         | 10011011<br>(\$9B) | LC           | PML           | SML           | [1:0]       | POS         |             | SGAIN[2:0    | )]             | Hi-Z        |  |

| CLV control 3         | 10011100<br>(\$9C) |              |               | l             | POFFS       | SET[7:0]    |             |              |                | Hi-Z        |  |

| CLV control 4         | 10011101<br>(\$9D) | SPLUS        | SDD           | PHASE         | DIV[1:0]    |             | SMOFF       | SET[3:0]     |                | Hi-Z        |  |

| CLV control 5         | 10011110<br>(\$9E) |              |               |               | SOFFS       | SET[7:0]    |             |              |                | Hi-Z        |  |

| CLV control 6         | 10011111<br>(\$9F) | SMEF<br>OUTB | CLV<br>DEFT   | -             | DSVEN       | DSV3T       | DSVINV      | DSVG         | AIN[1:0]       | Hi-Z        |  |

| Command                             | Address            | Data |      |       |    |    |       |              |               |      |  |

|-------------------------------------|--------------------|------|------|-------|----|----|-------|--------------|---------------|------|--|

| Command                             | Audress            | D7   | D6   | D5    | D4 | D3 | D2    | D1           | D0            | pin  |  |

| 1-bit DAC &<br>DATX control         | 10100011<br>(\$A3) |      | TXSF | [3:0] |    | SC | [3:0] | SPLFR        | EQ[1:0]       | Hi-Z |  |

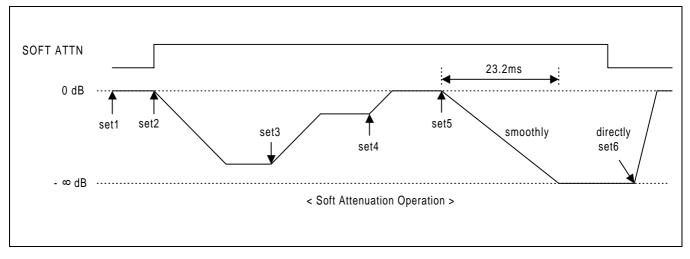

| 1-bit DAC<br>attenuation<br>control | 10100100<br>(\$A4) | M5   | M4   | М3    | M2 | M1 | MO    | SOFT<br>ATTN | CMD<br>DIRECT | Hi-Z |  |

| Output port<br>control              | 10101001<br>(\$A9) |      | TALK | [3:0] |    | -  | -     | -            | -             | Hi-Z |  |

| SADT I/F<br>control                 | 10110000<br>(\$B0) | -    | -    | -     | -  | -  | -     | -            | MSON          | Hi-Z |  |

| Play mode<br>control                | 11110000<br>(\$F0) | DS1  | DS0  | -     | -  | -  | DFCK  | -            | -             | Hi-Z |  |

| TEST mode<br>control                | 11111111<br>(\$FF) |      | TEST | [3:0] |    | -  | -     | -            | -             | Hi-Z |  |

# \$88 Command

Digital PLL control

| Command        | Address            |      |              |               | Da          | ata   |    |      |        |

|----------------|--------------------|------|--------------|---------------|-------------|-------|----|------|--------|

| Command        | Address            | D7   | D6           | D5            | D4          | D3    | D2 | D1   | D0     |

| DPLL control 1 | 10001000<br>(\$88) | WIDE | PHASE<br>DET | PHASE<br>GAIN | DLF<br>GAIN | ACC3t | -  | СОЗТ | RETREF |

| Bit | Name       | Data = 0    | Data = 1    | Comment                                     |

|-----|------------|-------------|-------------|---------------------------------------------|

| D7  | WIDE       | Normal      | Wide        | Wide mode selection                         |

| D6  | PHASE-DET  | Now         | new         | Phase detection method selection (option)   |

| D5  | PHASE-GAIN | 1/2t        | 1t          | Phase Adjust gain selection (option)        |

| D4  | DLF-GAIN   | 1/2^10      | 1/2^9       | Digital loop filter gain selection (option) |

| D3  | ACC3t      | ignore ± 3t | accept ± 3t | ROM coefficient selection (option)          |

| D2  | INC3T      | ignore 3T   | accept 3T   | Selection 3T error                          |

| D1  | CO3T       | Normal      | 3Т          | 3T correction (option)                      |

| D0  | REFRET     | ± 1.1%      | ± 2.3%      | Reference when return to M1 = 98            |

# \$89 Command

Digital PLL control

| Command         | Address            |            |    |     | Da       | ata |               |    |               |  |

|-----------------|--------------------|------------|----|-----|----------|-----|---------------|----|---------------|--|

| Command Address |                    | D7         | D6 | D5  | D4       | D3  | D2            | D1 | D0            |  |

| DPLL control 2  | 10001001<br>(\$89) | REF98[1:0] |    | REF | REF[1:0] |     | MAXTGAIN[1:0] |    | CAPRANGE[1:0] |  |

| Bits   | Name          | Data = 00 | Data = 01 | Data = 10 | Data = 11 | Comment                        |

|--------|---------------|-----------|-----------|-----------|-----------|--------------------------------|

| D[7:6] | REF98[1:0]    | ± 1.7%    | ± 2.3%    | ± 3.4%    | ± 4.6%    | Outward reference when M1 = 98 |

| D[5:4] | REF[1:0]      | ± 1.7%    | ± 2.3%    | ± 3.4%    | ± 4.6%    | Outward reference when M1≠ 98  |

| D[3:2] | MAXTGAIN[1:0] | 1         | 1/2       | 1/4       | 1/8       | MAX T accumulation gain        |

| D[1:0] | CAPRANGE[1:0] | 50%       | 40%       | 30%       | 20%       | Capture range selection        |

# \$8A Command

Digital PLL control

| Command        | Address            |      |            |    | Da         | ata |    |    |    |

|----------------|--------------------|------|------------|----|------------|-----|----|----|----|

| Command        | Audress            | D7   | D6         | D5 | D4         | D3  | D2 | D1 | D0 |

| DPLL control 3 | 10001010<br>(\$8A) | DIVS | DIVS1[1:0] |    | DIVP1[5:0] |     |    |    |    |

| Bits   | Name       | Data = 00 | Data = 01 | Data = 10 | Data = 11 | Comment          |

|--------|------------|-----------|-----------|-----------|-----------|------------------|

| D[7:6] | DIVS1[1:0] | 1         | 1/2       | 1/4       | 1/8       | PLL1 post scalar |

| Bits   | Name       | Data = 000000 - 111111 | Comment          |  |  |

|--------|------------|------------------------|------------------|--|--|

| D[5:0] | DIVP1[5:0] | 0 - 63                 | PLL1 pre divider |  |  |

# \$8C Command

Digital PLL Control

| Command        | Address            |    |            |    | Da | ata |    |    |    |  |

|----------------|--------------------|----|------------|----|----|-----|----|----|----|--|

|                | Address            | D7 | D6         | D5 | D4 | D3  | D2 | D1 | D0 |  |

| DPLL control 4 | 10001100<br>(\$8C) |    | DIVM1[7:0] |    |    |     |    |    |    |  |

| Bits   | Name       | Data = 00000000 - 11111111 | Comment           |  |  |

|--------|------------|----------------------------|-------------------|--|--|

| D[7:0] | DIVM1[7:0] | 0 - 255                    | PLL1 main divider |  |  |

## \$8D Command

**Digital PLL control**

| Command        | Address            |              |               |             | Da | ata   |         |               |    |

|----------------|--------------------|--------------|---------------|-------------|----|-------|---------|---------------|----|

|                | Address            | D7           | D6            | D5          | D4 | D3    | D2      | D1            | D0 |

| DPLL control 5 | 10001101<br>(\$8D) | CMD<br>SPLIT | PHASE<br>ONLY | MRANGE[1:0] |    | FSREG | PLLTEST | PLL<br>PWRDN1 | -  |

## CMD\_SPLIT (option)

The digital PLL control micom command is automatically applied when the speed is changed(\$F0) or at Jitter Free2(\$94).

H : Each DPLL control Micom Commands (\$8A, \$8B, \$8B) are applied using the Micom Interface terminals (MCK, MDAT, MLT).

L : DPLL control Micom Command (\$8A, \$8B, \$8B) is applied automatically inside.

## PHASE\_ONLY (option)

Controls phase compensation status at DPLL.

H : Phase compensation

L : Phase compensation + Frequency compensation

## MRANGE[1:0]

Controls the range of the PLL1 Main Divider M value range

| Bits   | Name        | Data = 00 | Data = 01 | Data = 10 | Data = 11 | Comment    |

|--------|-------------|-----------|-----------|-----------|-----------|------------|

| D[5:4] | MRANGE[1:0] | 50%       | 40%       | 30%       | 20%       | Lock Range |

### FSREG

Verifies the Frame Sync status(|Thigh-Tlow|  $\leq$  1) at MAX T H : Verify L : Ignore

## PLLTEST

| PLL1 TEST mode<br>H : TEST (M1<=M2), | L : Normal |

|--------------------------------------|------------|

| PLL PWDN1                            |            |

| DI I 1 Dower Down mode               |            |

PLL1 Power Down mode H : Power Down,

L : Normal

## \$90 Command

**DSP** Function Control

| Command          | Address            | Data  |       |      |         |       |    |    |      |

|------------------|--------------------|-------|-------|------|---------|-------|----|----|------|

|                  | Audress            | D7    | D6    | D5   | D4      | D3    | D2 | D1 | D0   |

| Function control | 10010000<br>(\$90) | CDROM | FDEEM | DEEM | ERA OFF | C1PNT | -  | -  | JITM |

## CDROM

H: CDROM mode

L: CDP mode

## FDEEM, DEEM

De-Emphasis Automatic control and compulsion control select

| FDEEM | DEEM | De-emphasis on/off | Comment                                                            |

|-------|------|--------------------|--------------------------------------------------------------------|

| 0     | 0    | Off                | -                                                                  |

| 0     | 1    | On/Off             | Automatic operate to detect emphasis signal of subcode information |

| 1     | 0    | Off                | -                                                                  |

| 1     | 1    | On                 | Operate without regard to emphasis signal of subcode information   |

### ERA\_OFF:

H: Erasure correction off

L: Erasure correction on

### C1PNT :

C1 2 Error correction C1 pointer set/reset control H: C1PNT = reset L: C1PNT = set

### C1PNT (option)

Mute SRAM Address copy permission (Write base count copy from read base counter)

H: Accept L: Reject

# \$91 Command (Default value: 0000000)

Control of each function related to audio data

| Audio control10010001<br>(\$91)MUTEZCMTZDENLATTNDAC<br>MUTEBVFALGDATX<br>MUTEDATX<br>MUTEAUTEDSP MUTE enable signal<br>H: DSP MUTE on<br>L: DSP MUTE offSignal<br>H: DSP MUTE offSignal<br>H: DSP MUTE offSignal (effective when MUTE signal is ON)<br>H: DSP Zero cross mute enable signal (effective when MUTE signal is ON)<br>H: DSP Zero cross mute on<br>L: DSP Zero detection MUTE disable signal<br>H: 1-bit DAC Zero detection MUTE offSignal<br>H: 1-bit DAC Zero detection MUTE off<br>L: 1-bit DAC Zero detection MUTE onSignal<br>H: DSP Attenuation enable signal<br>H: DSP Attenuation off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Command        | Address      |                        |               |             | D            | ata        |       |    |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|------------------------|---------------|-------------|--------------|------------|-------|----|----|

| Audio control     (\$91)     MUTE     ZUNI     ZUENL     ATTN     MUTEB     VPALG     MUTE     ENB       NUTE     DSP MUTE enable signal     H: DSP MUTE off     Image: Signal is DSP Zero cross mute enable signal (effective when MUTE signal is ON)     H: DSP Zero cross mute on     L: DSP Zero cross mute off     Image: Signal is DSP Zero cross of Cero detection MUTE off     Image: Signal is DSP Zero cross of Cero detection MUTE off     Image: Signal is DSP Zero cross cross of Cero detection block to 'L'     Image: Signal is DSP Zero cross of Cero detection block to 'L'     Image: Signal is DSP Zero cross crocos cross cross crocos cross c | Command        | Audress      | D7                     | D6            | D5          | D4           | D3         | D2    | D1 | D0 |

| DSP MUTE enable signal         H: DSP MUTE on         L: DSP MUTE off         CMT         DSP Zero cross mute enable signal (effective when MUTE signal is ON)         H: DSP Zero cross mute off         ZDENL         1-bit DAC Zero detection MUTE disable signal         H: 1-bit DAC Zero detection MUTE off         L: 1-bit DAC Zero detection MUTE off         L: 1-bit DAC Zero detection MUTE off         L: 1-bit DAC Zero detection MUTE off         NTTN         DSP Attenuation on         L: DSP Attenuation off         DAC MUTEB         Set the input data 1-bit DAC function block to 'L'         H: DAC MUTE off.         L: C2PO use         DATX_MUTE:         Set the input data to digital audio interface function block to 'L'         H: DATX MUTE off         DATX_MUTE off         DATX_MUTE off         DATX_ENB:         DATX function disabled, fixed DATX output.         H: DATX output disable         DATX output enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Audio control  |              | MUTE                   | ZCMT          | ZDENL       | ATTN         |            | VFALG |    |    |

| H: DSP MUTE on<br>L: DSP MUTE off<br>ZCMT<br>DSP Zero cross mute enable signal (effective when MUTE signal is ON)<br>H: DSP Zero cross mute off<br>ZDENL<br>1-bit DAC Zero detection MUTE disable signal<br>H: 1-bit DAC Zero detection MUTE off<br>L: 1-bit DAC Zero detection MUTE off<br>L: 1-bit DAC Zero detection MUTE on<br>MUTE on<br>MUTE DSP Attenuation enable signal<br>H: DSP Attenuation off<br>DAC MUTEB<br>Set the input data 1-bit DAC function block to 'L'<br>H: DAC MUTE off.<br>L: DAC MUTE on<br>XFALG:<br>Control the input V-bit to DATX Block<br>H: L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE off<br>DATX MUTE off<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable<br>L: DATX output disable<br>MUTE dB<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MUTE<br>DSP MI | JTE enable   | signal                 |               |             |              |            |       |    |    |

| DSP Zero cross mute enable signal (effective when MUTE signal is ON)         H: DSP Zero cross mute off         ZDENL         1-bit DAC Zero detection MUTE disable signal         H: 1-bit DAC Zero detection MUTE off         L: 1-bit DAC Zero detection MUTE off         DSP -12dB attenuation enable signal         H: DSP Attenuation off         DAC MUTEB         Set the input data 1-bit DAC function block to 'L'         H: DAC MUTE off.         L: DAC MUTE off.         Control the input V-bit to DATX Block         H: 'L' set         L: C2PO use         DATX_MUTE:         Set the input data to digital audio interface function block to 'L'         H: DATX MUTE off         DATX_ENB:         DATX function disabled, fixed DATX output.         H: DATX output disable         L: DATX output disable         DATX output enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | H: DSP         | MUTE on      | 5                      |               |             |              |            |       |    |    |

| H: DSP Zero cross mute on         L: DSP Zero cross mute off         ZDENL         1-bit DAC Zero detection MUTE disable signal         H: 1-bit DAC Zero detection MUTE off         L: 1-bit DAC Zero detection MUTE on         XTTN         DSP -12dB attenuation enable signal         H: DSP Attenuation on         L: DSP Attenuation off         DAC MUTEB         Set the input data 1-bit DAC function block to 'L'         H: DAC MUTE off.         L: CAPO use         DATX_MUTE:         Set the input data to digital audio interface function block to 'L'         H: DATX MUTE on         L: DATX MUTE off         DATX_MUTE         DATX function disabled, fixed DATX output.         H: DATX output disable         L: DATX output enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ZCMT           |              |                        |               |             |              |            |       |    |    |

| 2DENL       1-bit DAC Zero detection MUTE disable signal         H: 1-bit DAC Zero detection MUTE off         L: 1-bit DAC Zero detection MUTE on         XTTN         DSP -12dB attenuation enable signal         H: DSP Attenuation on         L: DSP Attenuation off         DAC MUTEB         Set the input data 1-bit DAC function block to 'L'         H: DAC MUTE off.         L: DAC MUTE off.         L: C2PO use         DATX_MUTE:         Set the input data to digital audio interface function block to 'L'         H: DATX MUTE on         L: DATX MUTE off         DATX_ENB:         DATX function disabled, fixed DATX output.         H: DATX output disable         Q       Q         Q       Q         Q       Q         Q       Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | H: DSP         | Zero cross   | mute on                | signal (effe  | ective when | MUTE sig     | nal is ON) |       |    |    |

| 1-bit DAC Zero detection MUTE disable signal         H: 1-bit DAC Zero detection MUTE off         L: 1-bit DAC Zero detection MUTE on         XTTN         DSP -12dB attenuation enable signal         H: DSP Attenuation on         L: DSP Attenuation off         DAC MUTEB         Set the input data 1-bit DAC function block to 'L'         H: DAC MUTE off.         Control the input V-bit to DATX Block         H: 'L' set         L: C2PO use         DATX_MUTE:         Set the input data to digital audio interface function block to 'L'         H: DATX MUTE on         L: DATX MUTE off         DATX_ENB:         DATX function disabled, fixed DATX output.         H: DATX output disable         L: DATX output disable         DATX function disabled, fixed DATX output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ZDENL          |              |                        |               |             |              |            |       |    |    |

| L: 1-bit DAC Zero detection MUTE on NTTN DSP -12dB attenuation enable signal H: DSP Attenuation on L: DSP Attenuation off DAC MUTEB Set the input data 1-bit DAC function block to 'L' H: DAC MUTE off. L: DAC MUTE off. L: DAC MUTE off. VFALG: Control the input V-bit to DATX Block H: 'L' set L: C2PO use DATX_MUTE: Set the input data to digital audio interface function block to 'L' H: DATX MUTE on L: DATX MUTE off DATX function disabled, fixed DATX output. H: DATX function disabled, fixed DATX output. H: DATX output disable L: DATX output enable $ \frac{ATTN MUTE dB}{0 0 0} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                | C Zero det   | ection MU <sup>-</sup> | TE disable    | signal      |              |            |       |    |    |

| NTTN       DSP -12dB attenuation enable signal         H: DSP Attenuation on       L: DSP Attenuation off         DAC MUTEB       Set the input data 1-bit DAC function block to 'L'         H: DAC MUTE off.       L: DAC MUTE on         /FALG:       Control the input V-bit to DATX Block         H: 'L' set       L: C2PO use         DATX_MUTE:       Set the input data to digital audio interface function block to 'L'         H: DATX MUTE on       L: DATX MUTE on         DATX_MUTE in       DATX MUTE off         DATX function disabled, fixed DATX output.       H: DATX output disable         L: DATX output disable       Image: Control disable         DATX function disabled, fixed DATX output.       H: DATX output disable         DATX function disabled, fixed DATX output.       H: DATX output disable         DATX function disabled, fixed DATX output.       Image: Context of the data for the data f                                                                                                                             |                |              |                        |               |             |              |            |       |    |    |

| DSP -12dB attenuation enable signal<br>H: DSP Attenuation on<br>L: DSP Attenuation off<br>DAC MUTEB<br>Set the input data 1-bit DAC function block to 'L'<br>H: DAC MUTE off.<br>L: DAC MUTE on<br>/FALG:<br>Control the input V-bit to DATX Block<br>H: 'L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable<br>DATX output disable<br>DATX output disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | DAC Zero c   | detection IV           | IUIE on       |             |              |            |       |    |    |

| H: DSP Attenuation on<br>L: DSP Attenuation off<br>DAC MUTEB<br>Set the input data 1-bit DAC function block to 'L'<br>H: DAC MUTE off.<br>/FALG:<br>Control the input V-bit to DATX Block<br>H: 'L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable<br>L: DATX output enable<br>MUTE dB<br>0 0 0 0<br>0 1 -∞                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ATTN           |              | tion anabl             |               |             |              |            |       |    |    |

| Set the input data 1-bit DAC function block to 'L'<br>H: DAC MUTE off. L: DAC MUTE on<br>/FALG:<br>Control the input V-bit to DATX Block<br>H: 'L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable<br>DATX output enable<br>$\frac{ATTN MUTE dB}{0 0 0}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | H: DSP         | Attenuatior  | n on                   | e signai      |             |              |            |       |    |    |

| Set the input data 1-bit DAC function block to 'L'<br>H: DAC MUTE off. L: DAC MUTE on<br>/FALG:<br>Control the input V-bit to DATX Block<br>H: 'L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable<br>DATX output enable<br>$\frac{ATTN MUTE dB}{0 0 0}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DAC MUTEB      |              |                        |               |             |              |            |       |    |    |

| /FALG:<br>Control the input V-bit to DATX Block<br>H: 'L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable<br>L: DATX output enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |              | I-bit DAC f            | unction blo   |             |              |            |       |    |    |

| Control the input V-bit to DATX Block<br>H: 'L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable<br>DATX output enable<br>MUTE dB<br>0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | H: DAC         | MUTE off.    |                        |               | L: DA       | C MUTE o     | on         |       |    |    |

| Control the input V-bit to DATX Block<br>H: 'L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output disable<br>DATX output enable<br>MUTE dB<br>0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |              |                        |               |             |              |            |       |    |    |

| H: 'L' set<br>L: C2PO use<br>DATX_MUTE:<br>Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output enable<br>$\frac{ATTN MUTE dB}{0 0 0}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | the input V- | -bit to DAT            | X Block       |             |              |            |       |    |    |

| Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output enable<br>$\frac{\text{ATTN}  \text{MUTE}  \text{dB}}{0  0  0}$ $0  1  -\infty$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | H: 'L' se      | t            | BILLO DAL              | A DIOCK       |             |              |            |       |    |    |

| Set the input data to digital audio interface function block to 'L'<br>H: DATX MUTE on<br>L: DATX MUTE off<br>DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output enable<br>$\frac{\text{ATTN}  \text{MUTE}  \text{dB}}{0  0  0}$ $0  1  -\infty$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DATX MUTE:     |              |                        |               |             |              |            |       |    |    |

| DATX_ENB:<br>DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output enable<br>$\frac{\textbf{ATTN}  \textbf{MUTE}  \textbf{dB}}{0  0  0}$ $0  1  -\infty$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Set the H: DAT | K MUTE on    |                        | idio interfac | ce function | block to 'L' | 1          |       |    |    |

| DATX function disabled, fixed DATX output.<br>H: DATX output disable<br>L: DATX output enable<br>ATTN     MUTE     dB       0     0     0       0     1     -∞                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |              |                        |               |             |              |            |       |    |    |

| H: DATX output disable<br>L: DATX output enable<br>$\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                | inction disa | bled fixed             |               | tuc         |              |            |       |    |    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | H: DAT)        | < output dis | able                   | Drived        | Juli        |              |            |       |    |    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |              |                        | ATTN          | MUTE        |              | dB         | ]     |    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |              |                        |               | 0           |              | 0          |       |    |    |

| 1 0 - 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |              |                        | 0             | 1           |              | - ∞        |       |    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |              |                        | 1             | 0           |              | - 12       |       |    |    |

<ATTN and MUTE Relation>

1

- 12

1

## \$92 Command

Control of functions related to frame sync

| Command               | Address            |      |        |     | Da     | ata |         |    |    |

|-----------------------|--------------------|------|--------|-----|--------|-----|---------|----|----|

| Command               | Address            | D7   | D6     | D5  | D4     | D3  | D2      | D1 | D0 |

| Frame sync<br>control | 10010010<br>(\$92) | FSEI | L[1:0] | WSE | L[1:0] | FSM | D [1:0] | -  | -  |

FSEL[1:0]: Control of cycle for frame sync protection and insertion

| FSEL[1:0] | Control Cycle (Frame) |

|-----------|-----------------------|

| 00        | 2                     |

| 01        | 4                     |

| 10        | 8                     |

| 11        | 13                    |

WSEL[1:0]: Control of window size related to frame sync protection

| WSEL[1:0] | Window Size(t) |

|-----------|----------------|

| 00        | ± 3            |

| 01        | ± 7            |

| 10        | ± 13           |

| 11        | ± 26           |

FSMD: [1:0] Frame sync detection method control

| FSMD [1:0] | Detection Method | Comment                                               |

|------------|------------------|-------------------------------------------------------|

| 00         | Pattern          | 11t — 11t                                             |

| 01         | Compensation     | 11t — 11t, 10 — 12t, 12t — 10t                        |

| 10         | Cycle 1          | 10t — 11t, 11t — 12t, 11t — 11t, 11t — 10t, 12t — 11t |

| 11         | Cycle 2          | cycle 1, 10t — 12t, 12t — 10t                         |

# \$93 Command

Control of modes of functions in DSP

| Command        | Address            |              | Data |               |    |      |            |      |      |  |

|----------------|--------------------|--------------|------|---------------|----|------|------------|------|------|--|

|                |                    | D7           | D6   | D5            | D4 | D3   | D2         | D1   | D0   |  |

| Mode control 1 | 10010011<br>(\$93) | GNR<br>PWRDN | -    | DAC<br>PWPDNB | -  | ECLV | ECLV<br>PD | NCLV | CRCQ |  |

# GNR\_PWDN

DSP Power Down H : Power Down On, L : Power Down Off

### DAC\_PWDNB

1-bit DAC function Power Down H : Power Down Off, L : Power Down On

### ECLV

Emergency CLV Servo, Overflow prevention

H : Repeat output of H, Hi-Z, and L at a regular cycle through the SMDP terminal

L : normal operation

## ECLV\_PD

SMDP output cycle control at ECLV H: Bottom Hold cycle (Refer to \$98)

L : Peak Hold cycle(Refer to \$98)

### NCLV

- H : CLV phase servo driven by frame sync

- L : CLV phase servo driven by base counter

## CRCQ

- L : SQDT without SQOK

- H : SQDT with SQOK (If S0S1 is 'H', SQDT = SQOK)

# \$94 Command

Control of function modes in DSP

| Command        | Address            |            | Data       |    |    |            |    |    |        |  |

|----------------|--------------------|------------|------------|----|----|------------|----|----|--------|--|

|                |                    | D7         | D6         | D5 | D4 | D3         | D2 | D1 | D0     |  |

| Mode control 2 | 10010100<br>(\$94) | MSCK<br>SW | WDCK<br>SW | -  | -  | RFCK<br>SW | -  | -  | JTFRV1 |  |

| Bit | Name    | Data = 0 | Data = 1 | Comment                                                               |

|-----|---------|----------|----------|-----------------------------------------------------------------------|

| D7  | MSCK_SW | Internal | External | Input SBCK terminal when input the 1-bit DAC master clock in external |

| D6  | WDCK_SW | X'tal    | VCO2     | WDCK frequency selection                                              |

| D5  | -       | -        | -        | -                                                                     |

| D4  | -       | -        | -        | -                                                                     |

| D3  | RFCK_SW | MICOM    | TESTV    | Use RFCK clock in CLV sero processing according to jitter mode        |

| D2  | -       | -        | -        | -                                                                     |

| D1  | -       | -        | -        | -                                                                     |

| D0  | JTFRV1  | X'tal    | VCO1     | Use VCO1 clock in data processing                                     |

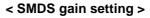

# \$98 Command

Control cycle and gain control in CLV speed mode

| Command          | Address                               |                |                   |                  | Da         | ata                      |    |    |      |

|------------------|---------------------------------------|----------------|-------------------|------------------|------------|--------------------------|----|----|------|

| Commanu          | Address                               | D7             | D6                | D5               | D4         | D3                       | D2 | D1 | D0   |

| CLV gain control | 10011000<br>(\$98)                    | OVSPL          | WBN               | WPN              | -          | OVSPL<br>MS              | WB | WP | GAIN |