# Advance Information

# System Basis Chip with Low Speed Fault Tolerant CAN

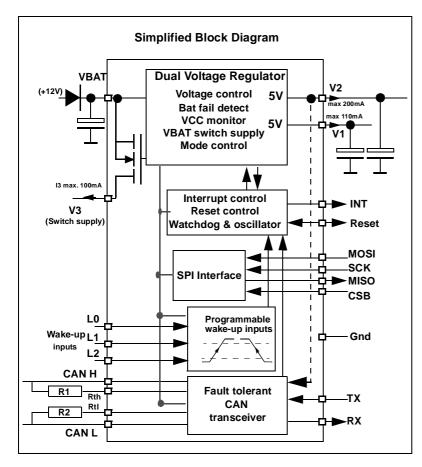

The MC33389 is a monolithic integrated circuit combining many functions frequently used by automotive ECUs. It incorporates a low speed fault tolerant CAN transceiver.

- Dual Low Drop Voltage Regulators, with Respectively 100mA and 200mA Current Capabilities, Current Limitation and Over Temperature Detection with Prewarning

- 5V Output Voltage for V1 Regulator

- Three Operational Modes (Normal, Standby and Sleep Mode) Separated from the CAN Interface Operating Modes

- Low Speed 125kBaud Fault Tolerant CAN Interface, Compatible with MC33388 Standalone Physical Interface

- V1 Regulator Monitoring and Reset Function

- Three External High Voltage Wake-up Inputs, Associated with V3 V<sub>bat</sub> Switch

- 100mA Output Current Capability for V3 V<sub>bat</sub> Switch Allowing Drive of External Switches or Relays

- Low Standby and Sleep Current Consumption

- V<sub>bat</sub> Monitoring and V<sub>bat</sub> Failure Detection Capabilities

- DC Operating Voltage up to 27V

- 40V Maximum Transient Voltage

- Programmable Software Window Watchog and Reset

- Wake up Capabilities (CAN Interface, Local Programmable Cyclic Wake up)

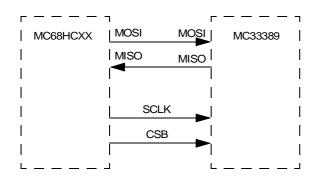

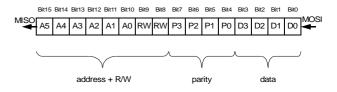

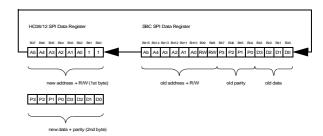

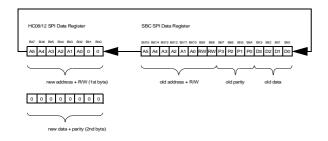

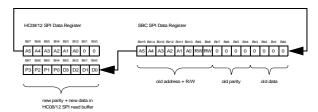

- Interface with MCU through SPI

- Programmable Interupt Function

# MC33389

# AUTOMOTIVE SBC SYSTEM BASIS CHIP

SILICON MONOLITHIC INTEGRATED CIRCUIT

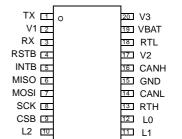

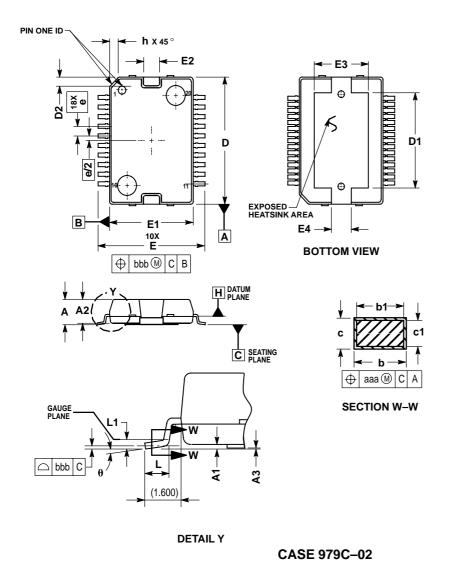

# PIN CONNECTIONS

# DH SUFFIX POWER PACKAGE

CASE 979C HSOP-20

order Number: MC33389/D Rev 3.3, 15th April 02

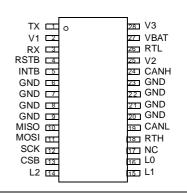

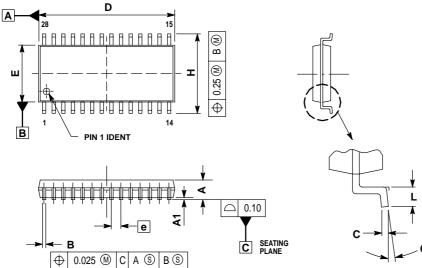

# **DW SUFFIX**

PLASTIC PACKAGE CASE 751F SO-28

| ORDERING INFORMATION |                                             |         |  |  |  |  |  |  |  |

|----------------------|---------------------------------------------|---------|--|--|--|--|--|--|--|

| Device and version   | Operating<br>Temperature Range              | Package |  |  |  |  |  |  |  |

| MC33389ADW(1)        | $T_A = -40 \text{ to } 125^{\circ}\text{C}$ | SO-28   |  |  |  |  |  |  |  |

| MC33389CDW(2)        | $T_A = -40 \text{ to } 125^{\circ}\text{C}$ | SO-28   |  |  |  |  |  |  |  |

| MC33389CDH(2)        | $T_A = -40 \text{ to } 125^{\circ}\text{C}$ | HSOP20  |  |  |  |  |  |  |  |

- (1) Version A: If device remains in reset greater than 100ms due to V1 undervoltage, device switches to sleep mode to minimise current consumption. Wake-up configuration active.

- (2) Version C: In V1 undervoltage condition, device remains in permanent reset state until V1 returns to nominal conditions. V1 protected by overcurrent and over temperature functions.

# **MAXIMUM RATINGS**

| Description                                             | Symbol           | Min  | Тур | Max | Unit | Test Conditions                                                    |

|---------------------------------------------------------|------------------|------|-----|-----|------|--------------------------------------------------------------------|

| DC Voltage at Pin V <sub>bat</sub>                      | V <sub>bat</sub> | -0.3 |     | 27  | V    |                                                                    |

| Transient Voltage at Pin V <sub>bat</sub>               |                  |      |     | 40  | V    | t<500ms (Load Dump)                                                |

| DC Voltage at Pins CANH CANL                            |                  | -20  |     | 27  | V    |                                                                    |

| Transient Voltage at Pins<br>CANH CANL                  |                  | -40  |     | 40  | V    | 0 <v2<5.5, v<sub="">bat&gt;0,<br/>t&lt;500ms</v2<5.5,>             |

| Coupled Transient Voltage at Pins<br>CANH CANL          |                  | -100 |     | 100 | V    | With 100Ω Termination<br>Resistors. Coupled<br>Through 1nF (note1) |

| DC Voltage at Pins V1 V2                                |                  | -0.3 |     | 6   | V    |                                                                    |

| DC Current at output pins: RX, MISO, RSTB, INTB         |                  | -20  |     | 20  | mA   |                                                                    |

| DC Voltage at input pins TX, MOSI, SCLK, CSB, RSTB      |                  | -0.3 |     | 6   | V    |                                                                    |

| DC Voltage at Pins L0, L1, L2                           |                  | -0.3 |     | 40  | V    | 0 <v<sub>bat&lt;40V</v<sub>                                        |

| Current at Pins L0, L1, L2                              |                  | -15  |     |     | mA   |                                                                    |

| Transient Current at Pin V3                             |                  | -30  |     | 20  | mA   |                                                                    |

| DC Voltage at Pins RTH, RTL                             |                  | -0.3 |     | 40  | V    |                                                                    |

| ESD Voltage on any Pin<br>(HBM 100pF, 1.5K)             |                  | -2   |     | 2   | kV   |                                                                    |

| ESD Voltage on L0, L1, L2, CANH, CANL, V <sub>bat</sub> |                  | -2   |     | 2   | kV   |                                                                    |

| ESD Voltage on any Pin (MM 200pF, 0Ω).                  |                  | -150 |     | 150 | V    |                                                                    |

| Junction Temperature                                    | Tj               | -40  |     | 150 | °C   |                                                                    |

| Junction Temperature                                    | T <sub>jt</sub>  | -40  |     | 160 | °C   |                                                                    |

| Storage Temperature                                     | T <sub>s</sub>   | -65  |     | 150 | °C   |                                                                    |

| RTH, RTL Termination Resistance                         |                  | 500  |     | 16k | Ω    |                                                                    |

| Junction to Heatsink Thermal<br>Resistance for HSOP20   |                  |      | 3.1 |     | K/W  | 33% Power on V1, 66% on V2 (Including CAN), Note 2                 |

| Junction to Pin Thermal<br>Resistance for SO28WB        |                  |      | 17  |     | K/W  | Note 2, Note 3                                                     |

NOTE 1: Pulses 1, 2, 3a, 3b according to ISO7637. NOTE 2: Refer to thermal management in device description section. NOTE 3: pins 6,7,8,9,20,21,22,23 of SO28WB package

# **ELECTRICAL PARAMETERS** $V_{bat}$ =5.5V to 18V, -40°< Tj < 150°C, unless otherwise specified

| Parameter                        | Symbol                             | Min  | Тур             | Max  | Unit | Test Conditions                                                                                         |

|----------------------------------|------------------------------------|------|-----------------|------|------|---------------------------------------------------------------------------------------------------------|

| V <sub>bat</sub> PIN             |                                    |      | I               |      |      | 1                                                                                                       |

| Nominal Vbat Operating Range     |                                    | 5.5  |                 | 18   | V    |                                                                                                         |

| Functional Vbat Operating Range  |                                    | 5.5  |                 | 27   | V    |                                                                                                         |

| Vbat Threshold for BatFail Flag  | BatFail                            | 2    |                 | 4    | V    | 0 <v1<5,1v< td=""></v1<5,1v<>                                                                           |

| Delay for Signalling BatFail     | T <sub>fail</sub>                  |      | 150             | 400  | μs   | V <sub>bat</sub> <batfail, active<="" from="" int="" low="" measured="" td="" to="" vbat=""></batfail,> |

| Overvoltage Vbat Threshold       | BAThigh                            | 18   | 20              | 22   | V    |                                                                                                         |

| Delay for Setting BAThigh Flag   | T <sub>high</sub>                  | 4    | 18              | 50   | μs   | V <sub>bat</sub> >BatHigh                                                                               |

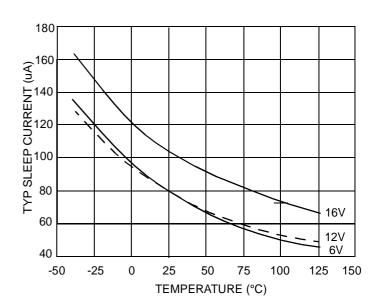

| Supply Current in Sleep Mode     | I <sub>sleep1</sub>                |      | 75              | 125  | μΑ   | Forced Wake-up and Cyclic<br>Sense Disabled<br>V <sub>bat</sub> =12V,Tj = 25°C to150°C                  |

| Supply Current in Sleep Mode     | I <sub>sleep2</sub>                |      |                 | 210  | μΑ   | Forced Wake-up and Cyclic<br>Sense Disabled<br>V <sub>bat</sub> =12V, Tj = -40°C to 25°C                |

| Supply current in sleep mode     | I <sub>sleep3</sub>                |      | 105             | 155  | μΑ   | Forced Wake-up or Cyclic<br>Sense Enabled. V <sub>bat</sub> =12V, Tj =<br>25°C to 150°C                 |

| Supply Current in Sleep Mode     | I <sub>sleep4</sub>                |      |                 | 250  |      | Forced Wake-up or Cyclic<br>Sense Enabled<br>V <sub>bat</sub> 12V, Tj -40 to 25°C,                      |

| Supply Current in Sleep Mode     | I <sub>sleep5</sub>                |      |                 | 300  |      | Forced Wake-up or Cyclic<br>Sense Enabled. V <sub>bat</sub> 6V to 16V,<br>Tj -40 to 150°C               |

| Supply Current in Standby Mode   | I <sub>stb2</sub>                  |      | 0.5             | 1    | mA   |                                                                                                         |

| Supply Current in Normal Mode    | I <sub>nrec</sub>                  |      | 3.5             | 7    | mA   | Normal Mode with I(V1)=I(V2)=0 Bus in Recessive State                                                   |

| V1 PIN 5V                        |                                    |      |                 |      | •    |                                                                                                         |

| Output Voltage                   | V1 <sub>nom</sub>                  | 4.85 | 5               | 5.15 | V    | 0mA <i<sub>out&lt;100mA<br/>5.5V<v<sub>bat&lt;27V</v<sub></i<sub>                                       |

| Output Voltage                   | V1                                 | 4.8  | 5               | 5.2  | V    | I <sub>out</sub> =<100mA<br>27V <v<sub>bat&lt;40V</v<sub>                                               |

| Drop Voltage                     | V1 <sub>drop</sub>                 |      | 0.35            | 0.5  | V    | I <sub>out</sub> =100mA (Note 4)                                                                        |

| Output Current Limitation        | I1 <sub>max</sub>                  | 130  | 170             | 200  | mA   | V1 <sub>nom</sub> -100mV                                                                                |

| V1 Overtemp Shut-off Threshold   | TV1 <sub>h</sub>                   | 160  |                 | 190  | °C   | Junction Temperature                                                                                    |

| V1 Pre-warning Temp Threshold    | TV1 <sub>I</sub>                   | 130  |                 | 160  | °C   | Junction Temperature                                                                                    |

| Temperature Threholds Difference | TV1 <sub>h</sub> -TV1 <sub>l</sub> | 20   |                 | 40   | °C   |                                                                                                         |

| Reset Threshold on V1            | V <sub>r1</sub>                    | 4.1  | 4.3             | 4.8  | V    | 5.5V <v<sub>bat&lt;27V</v<sub>                                                                          |

| Reset Active V1 Range            | V1 <sub>r</sub>                    | 1    | V <sub>r1</sub> |      | V    |                                                                                                         |

| Parameter                                           | Symbol           | Min | Тур | Max | Unit | Test Conditions                                                                                        |

|-----------------------------------------------------|------------------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------------|

| Reset Delay Time                                    | t <sub>d</sub>   | 2   |     | 20  | μs   |                                                                                                        |

| Line Regulation                                     |                  | -15 | 2   | +15 | mV   | 9V <v<sub>bat&lt;16.5,I<sub>load</sub>=10mA</v<sub>                                                    |

| Line Regulation                                     |                  | -50 | 10  | +50 | mV   | 5.5V <v<sub>bat&lt;27V,I<sub>load</sub>=10mA</v<sub>                                                   |

| Load Regulation                                     |                  | -50 |     | +50 | mV   | 1mA <i<sub>load&lt;100mA</i<sub>                                                                       |

| Line Ripple Rejection                               |                  | 30  | 55  |     | dB   | 100Hz, 1V <sub>pp</sub> on V <sub>bat</sub> =12V,<br>I <sub>load</sub> =100mA, guaranteed by<br>design |

| Line Transient Response                             |                  |     | 27  |     | mV   | $V_{bat}$ from 12V to 40V in 1μs,(10μF, ESR=3 $\Omega$ )                                               |

| Load Transient Response                             |                  |     | 400 |     | mV   | $I_{load}$ from 10μA to 100mA in 1μs ( $C_{load}$ =10μF esr=3 $\Omega$ ) (Note 5)                      |

| Load Transient Response                             |                  |     | 16  |     | mV   | $I_{load}$ from 10μA to 100mA in 1μs ( $C_{load}$ =10μF esr=0.1 $\Omega$ )                             |

| Reverse Current From V1 to V <sub>bat</sub> and Gnd | I <sub>Rev</sub> |     |     | 1   | mA   | V1=4.9V, 0 <v<sub>bat&lt;4.9 V</v<sub>                                                                 |

NOTE 4: Measured when V1 has dropped 100mV below its nominal value. NOTE 5: This condition does not produce reset.

# **V2 PIN**

| Output Voltage                    | V2 <sub>nom</sub>  | 4.75 | 5    | 5.25 | V  | 0mA <i<sub>out&lt;200mA<br/>5.5V<v<sub>bat&lt;40V</v<sub></i<sub>       |

|-----------------------------------|--------------------|------|------|------|----|-------------------------------------------------------------------------|

| Drop Voltage                      | V2 <sub>drop</sub> |      | 0.2  | 0.5  | V  | I <sub>out</sub> =200mA (Note 6)                                        |

| Drop Voltage                      | V2 <sub>drop</sub> |      | 0.05 | 0.15 | V  | I <sub>out</sub> =20mA (Note 6)                                         |

| Output Current Limitation         | I1 <sub>max</sub>  | 220  | 280  | 350  | mA | V2 <sub>nom</sub> -100mV                                                |

| Threshold on V2 to Report V2 off  | V <sub>r2</sub>    | 4.1  | 4.55 | 4.75 | V  | V2 Nominal                                                              |

| V <sub>r2</sub> Delay Time        |                    | 20   |      | 70   | μs |                                                                         |

| V2 Overtemp Pre-warning Threshold | T <sub>V2I</sub>   | 130  |      | 160  | °C | V2 Junction Temperature                                                 |

| V2 Overtemp Switch-off Threshold  | T <sub>V2h</sub>   | 155  |      | 185  | °C | V2 Junction Temperature                                                 |

| Line Regulation                   |                    | -15  |      | +15  | mV | 9V <v<sub>bat&lt;16.5</v<sub>                                           |

| Load Regulation                   |                    | -75  |      | +75  | mV | 4mA <i<sub>load&lt;200mA</i<sub>                                        |

| Line Ripple Rejection             |                    | 30   | 55   |      | dB | 100Hz, 1V <sub>pp</sub> on V <sub>bat</sub> , guar-<br>anteed by design |

| Percentage Difference V2-V1       |                    | -3   |      | 3    | %  | V <sub>bat</sub> >9V, I <sub>V1</sub> =20mA,<br>I <sub>V2</sub> =40mA   |

NOTE 6: Measured when V2 has dropped 100mV below its nominal value.

# V3 PIN

| High Level Voltage Drop | V3 <sub>drop</sub> | 0.4 | 1   | V | I <sub>V3</sub> =-50mA, 9V <v<sub>bat&lt;40V</v<sub> |

|-------------------------|--------------------|-----|-----|---|------------------------------------------------------|

| High Level Voltage Drop | V3 <sub>drop</sub> |     | 1.5 | V | I <sub>V3</sub> =50mA, 6V <v<sub>bat&lt;9V</v<sub>   |

| Parameter                                                     | Symbol                                 | Min                   | Тур  | Max                   | Unit | Test Conditions                                                  |

|---------------------------------------------------------------|----------------------------------------|-----------------------|------|-----------------------|------|------------------------------------------------------------------|

| V3 Output Current Limitation                                  | I3 <sub>lim</sub>                      | 100                   | 15   | 250                   | mA   | 5.5V <v<sub>bat&lt;27V</v<sub>                                   |

| V3 Leakage Current                                            | I3 <sub>leak</sub>                     |                       |      | 15                    | μΑ   | V3=0 (V3 off)                                                    |

| V3 Overtemp Detection                                         | T <sub>V3</sub>                        | 155                   |      | 185                   | °C   | Junction Temperature                                             |

| V3 voltage with -30mA (negative current for Relay Switch off) | V <sub>V3</sub>                        | 0.3                   |      | 0.5                   | V    | For t≤100ms, no<br>Functional Error Allowed                      |

| CAN TRANSCEIVER                                               |                                        |                       |      |                       |      |                                                                  |

| V2 for Forced BusStandby Mode<br>(Fail Safe)                  | V <sub>rc2</sub>                       | 3                     | 3.9  | 4.7                   | V    |                                                                  |

| CANH, CANL Pins                                               |                                        |                       |      |                       |      |                                                                  |

| Differential Receiver, Threshold Voltage                      |                                        | -3.2                  |      | -2.5                  | V    |                                                                  |

| Differential Receiver, Dominant to Recessive Threshold        |                                        | -3.2                  |      | -2.5                  | V    | (Bus failures 1, 2, 5)                                           |

| CANH Recessive Output Voltage                                 | V <sub>canh</sub>                      |                       |      | 0.2                   | V    | TX=high, R(RTH)<4k                                               |

| CANL Recessive Output Voltage                                 | V <sub>canl</sub>                      | V2-0.2                |      |                       | V    | TX=high, R(RTL)<4k                                               |

| CANH Output Voltage, Dominant                                 | V <sub>canh</sub>                      | V2-1.4                |      |                       | V    | TX=0V ; BusNormal Mode, I <sub>canh</sub> = -40mA                |

| CANL Output Voltage, Dominant                                 | V <sub>canl</sub>                      |                       |      | 1.4                   | V    | TX=0V ; BusNormal Mode,<br>I <sub>canl</sub> =40mA               |

| CANH Output Current Limit                                     | I <sub>canh</sub>                      | 50                    | 75   | 100                   | mA   | (V <sub>canh</sub> =0, TX=0)                                     |

| CANL Output Current Limit                                     | I <sub>canl</sub>                      | 50                    | 95   | 130                   | mA   | (V <sub>canl</sub> =14V, TX=0)                                   |

| Detection Threshold for Short-circuit to Battery Voltage      | $V_{canh}V_{canl}$                     | 7.3                   | 7.9  | 8.9                   | V    | BusNormal Mode                                                   |

| Detection Threshold for Short-circuit to Battery Voltage      | V <sub>canh</sub>                      | V <sub>bat</sub> /2+3 |      | V <sub>bat</sub> /2+5 | V    | BusStandby Mode                                                  |

| CANH Output Current, Failure3                                 |                                        |                       | 5    | 10                    | μΑ   | BusStandby Mode V <sub>canh</sub> =12V                           |

| CANL Output Current, Failure4                                 |                                        |                       | 0    | 2                     | μА   | BusStandby Mode,<br>V <sub>canl</sub> =0V, V <sub>bat</sub> =12V |

| CANL Wake up Voltage Threshold                                | V <sub>wakeL</sub>                     | 2.5                   | 3.3  | 3.9                   | V    | BusStandby Mode                                                  |

| CANH Wake up Voltage Threshold                                | V <sub>wakeH</sub>                     | 1.2                   | 2    | 2.7                   | V    | BusStandby Mode                                                  |

| Wake up Threshold Difference                                  | V <sub>wakeL</sub> -V <sub>wakeH</sub> | 0.2                   |      |                       | V    |                                                                  |

| CANH Single Ended<br>Receiver Threshold                       | V <sub>canh</sub>                      | 1.5                   | 1.85 | 2.15                  | V    | Failures 4,6,7                                                   |

| CANL Single Ended<br>Receiver Threshold                       | V <sub>canl</sub>                      | 2.8                   | 3.05 | 3.4                   | V    | Failures 3,8                                                     |

| CANL Pull up Current                                          | I <sub>canlpu</sub>                    | 45                    | 75   | 90                    | μΑ   | BusNormal Mode                                                   |

| Parameter                                                                              | Symbol              | Min  | Тур  | Max  | Unit | Test Conditions                                        |

|----------------------------------------------------------------------------------------|---------------------|------|------|------|------|--------------------------------------------------------|

| CANH Pull Down Current                                                                 | I <sub>canlpd</sub> | 45   | 75   | 90   | μΑ   | BusNormal Mode                                         |

| Receiver Differential Input<br>Impedance CANH / CANL                                   | R <sub>diff</sub>   | 100  |      | 180  | kΩ   |                                                        |

| Differential Receiver Common<br>Mode Voltage Range                                     | V <sub>com</sub>    | -8   |      | 8    | V    |                                                        |

| RTH, RTL Pins                                                                          |                     |      |      |      |      | 1                                                      |

| RTL to V2 Switch on Resistance                                                         | R <sub>rtl</sub>    | 10   | 25   | 70   | Ω    | I <sub>out</sub> <-10mA, BusNormal<br>Operating Mode   |

| RTL to BAT Switch Series Resistance                                                    | R <sub>rtl</sub>    | 8    | 12.5 | 20   | kΩ   | BusStandby Mode                                        |

| RTH to Ground Switch on Resistance                                                     | R <sub>rth</sub>    |      | 25   | 70   | Ω    | I <sub>out</sub> <10mA, All Mode                       |

| THERMAL SHUTDOWN                                                                       |                     |      |      |      |      |                                                        |

| Shutdown Temperature                                                                   | T <sub>sd</sub>     |      | 165  |      | °C   |                                                        |

| AC CHARACTERISTICS                                                                     |                     |      |      |      |      | 1                                                      |

| CANL and CANH Slew Rates, Rising or Falling Edges, Tx from Recessive to Dominant State |                     | 3.5  | 5    | 10   | V/μs | C <sub>load</sub> =10nF, 133Ω<br>Termination Resistors |

| CANL and CANH Slew Rates, Rising or Falling Edges, Tx from Dominant to Recessive State |                     | 2    | 3.5  | 10   | V/μs | C <sub>load</sub> =10nF, 133Ω<br>Termination Resistors |

| Propagation Delay TX to RX Low                                                         | T <sub>dh</sub>     |      | 1.2  | 2    | μs   | C <sub>load</sub> =10nF, 133Ω<br>Termination Resistors |

| Propagation Delay TX to RX High                                                        | T <sub>dl</sub>     |      | 2    | 3    | μs   | C <sub>load</sub> =10nF, 133Ω<br>Termination Resistors |

| Min. Dominant Time for Wake-up on CANL or CANH                                         | T <sub>wake</sub>   | 4    |      | 40   | μs   | BusStandby Mode,<br>V <sub>bat</sub> =12V              |

| Failure 3 Detection Time                                                               |                     | 10   |      | 60   | μs   | BusNormal Mode                                         |

| Failure 3 Recovery Time                                                                |                     | 10   |      | 60   | μs   | BusNormal Mode                                         |

| Failure 6 Detection Time                                                               |                     | 50   |      | 400  | μs   | BusNormal Mode                                         |

| Failure 6 Recovery Time                                                                |                     | 150  |      | 1000 | μs   | BusNormal Mode                                         |

| Failure 4, 7, 8 Detection Time                                                         |                     | 0.75 |      | 4    | ms   | BusNormal Mode                                         |

| Failure 4, 7, 8 Recovery Time                                                          |                     | 10   |      | 60   | μs   | BusNormal Mode                                         |

| Failure 3, 4, 7 Detection Time                                                         |                     | 0.8  |      | 8    | ms   | BusStandby Mode, V <sub>bat</sub> =12V                 |

| Failure 3, 4, 7 Recovery Time                                                          |                     |      | 2.5  |      | ms   | BusStandby Mode, V <sub>bat</sub> =12V                 |

| Edge Count Difference Between<br>CANH and CANL for<br>Failures 1, 2, 5 Detection       |                     |      | 3    |      |      | BusNormal Mode                                         |

| Edge Count Difference Between<br>CANH and CANL for<br>Failures 1, 2, 5 Recovery        |                     |      | 3    |      |      | BusNormal Mode                                         |

| Parameter                                        | Symbol            | Min    | Тур  | Max     | Unit | Test Conditions                         |

|--------------------------------------------------|-------------------|--------|------|---------|------|-----------------------------------------|

| TX Permanent Dominant<br>Timer Disable Time      | T <sub>txd</sub>  | 0.75   |      | 4       | ms   | BusNormal Mode and<br>Failure Mode      |

| TX, MOSI, SCK, CSB                               |                   |        |      | •       |      |                                         |

| High Level Input Voltage                         |                   | 0.7V1  |      | V1+0.3V |      |                                         |

| CSB Threshold for SPI Wake-up                    |                   |        | 2.2  |         | V    | SBC in Sleep Mode,<br>V1<1.5V           |

| CSB Filter Time for SPI Wake-up                  |                   |        |      | 3       | μs   | SBC in Sleep Mode, V1<1                 |

| Low Level Input Voltage                          |                   | -0.3   |      | 0.3 V1  | V    |                                         |

| High Level Input Current on CSB                  |                   | -100   |      | -20     | μΑ   | V <sub>i</sub> =4V                      |

| Low Level Input Current (CSB)                    |                   | -100   |      | -20     | μΑ   | V <sub>i</sub> =1V                      |

| TX High Level Input Current                      | I <sub>TX</sub>   | -200   | -80  | -25     | μΑ   | V <sub>i</sub> =4V                      |

| TX Low Level Input Current                       | I <sub>TX</sub>   | -800   | -320 | -100    | μΑ   | V <sub>i</sub> =1V                      |

| SI, SCK Input Current                            |                   | -10    |      | 10      | μΑ   | 0 <v<sub>IN<v1< td=""></v1<></v<sub>    |

| RX, INTB, MISO                                   | l                 |        |      | 1       |      | -                                       |

| High Level Output Voltage                        | Voh               | V1-0.9 |      | V1      | V    | I <sub>0</sub> =-250μA                  |

| Low Level Output Voltage                         | Vol               | 0      |      | 0.9     | V    | I <sub>0</sub> =1.5mA                   |

| Tristated SO Output Current                      | lz                | -2     |      | +2      | μΑ   | 0V <v<sub>so<v1< td=""></v1<></v<sub>   |

| RSTB Pin                                         |                   |        |      |         |      |                                         |

| High Level Input Voltage                         | Vih               | 0.7V1  |      | V1+0.3V |      |                                         |

| Low Level Input Voltage                          | Vil               | -0.3   |      | 0.3V1   | V    |                                         |

| High Level Output current 1                      |                   | -50    | -30  | -10     | μΑ   | 0 <v<sub>out&lt;0.5V1</v<sub>           |

| High Level Output current 2                      |                   |        | -300 |         | μΑ   | 0.5 <v<sub>out<v1< td=""></v1<></v<sub> |

| Low Level Output Voltage (I <sub>0</sub> =1.5mA) |                   | 0      |      | 0.9     | V    | 1v <v<sub>bat&lt;27V</v<sub>            |

| Reset Duration after V1High                      | t <sub>res</sub>  |        | 1    |         | ms   |                                         |

| L0, L1, L2 WAKE-UP INPUTS                        | <u>'</u>          |        |      | 1       |      | 1                                       |

| Positive Switching Threshold                     | V <sub>wup</sub>  | 3      | 3.7  | 4.5     | V    | 6V <v<sub>bat&lt;16V</v<sub>            |

| Negative Switching Threshold                     | V <sub>wun</sub>  | 2.5    | 3    | 3.8     | V    | 6V <v<sub>bat&lt;16V</v<sub>            |

| Hysteresis                                       | V <sub>hyst</sub> |        | 700  |         | mV   | 6V <v<sub>bat&lt;16V</v<sub>            |

| Leakage Current 0 <vwu<v<sub>bat</vwu<v<sub>     |                   | -5     |      | +5      | μΑ   |                                         |

| Wake up Filter Time                              |                   | 8      | 20   | 38      | μs   |                                         |

| Lx input current @ 40V                           | Vin               |        | 350  | 600     | μΑ   |                                         |

| Parameter                                                              | Symbol                | Min | Тур | Max        | Unit | Test Conditions                                     |

|------------------------------------------------------------------------|-----------------------|-----|-----|------------|------|-----------------------------------------------------|

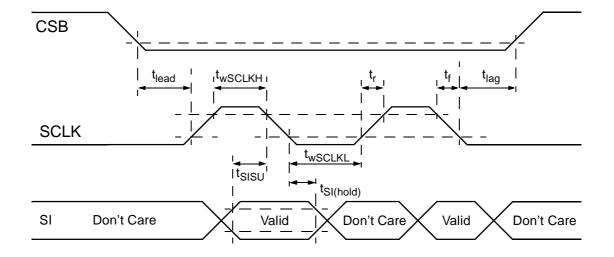

| DIGITAL INTERFACE TIMING                                               |                       |     |     |            | 1    | ,                                                   |

| SCLK Clock Period                                                      | t <sub>pSCLK</sub>    | 500 |     |            | ns   |                                                     |

| SCLK Clock High Time                                                   | t <sub>wSCLKH</sub>   | 175 |     |            | ns   |                                                     |

| SCLK Clock Low Time                                                    | t <sub>wSCLKL</sub>   | 175 |     |            | ns   |                                                     |

| Falling Edge of CSB to Rising Edge of SCLK                             | t <sub>lead</sub>     | 250 | 50  |            | ns   |                                                     |

| Falling Edge of SCLK to Rising Edge of CSB                             | t <sub>lead</sub>     | 250 | 50  |            | ns   |                                                     |

| SI to Falling Edge of SCLK                                             | t <sub>SISU</sub>     | 125 | 25  |            | ns   |                                                     |

| Falling Edge of SCLK to SI                                             | t <sub>SI(hold)</sub> | 125 | 25  |            | ns   |                                                     |

| SO Rise Time (CL = 220pF)                                              | t <sub>rSO</sub>      |     | 25  | 75         | ns   |                                                     |

| SO Fall Time (CL = 220pF)                                              | t <sub>fSO</sub>      |     | 25  | 75         | ns   |                                                     |

| SI, CSB, SCLK Incoming<br>Signal Rise Time                             | t <sub>rSI</sub>      |     |     | 200        | ns   |                                                     |

| SI, CSB, SCLK Incoming<br>Signal Fall Time                             | t <sub>fSI</sub>      |     |     | 200        |      |                                                     |

| Time from Falling Edge of CSB to SO<br>Low Impedance<br>High Impedance | t <sub>SO(en)</sub>   |     |     | 200<br>200 | ns   |                                                     |

| Time from Rising Edge of SCLK to SO Data Valid                         | t <sub>valid</sub>    |     | 50  | 125        |      | 0.2 V1 or V2≤SO≥ 0.8V1 or V2, C <sub>L</sub> =200pF |

# **SOFTWARE WATCHDOG TIMINGS**

(note 1: software watchdog timing accuracy are based on the running mode oscillator tolerance)

|                                   |      |      | ı   | ı    | 1  | Γ                                                  |

|-----------------------------------|------|------|-----|------|----|----------------------------------------------------|

| Running mode oscillator tolerance |      | -12  |     | +12  | %  | normal request, normal and standby modes. (Note 1) |

| Software Watchdog Timing 1        | SWt1 | 4.4  | 5   | 5.6  | ms | (Note 1)                                           |

| Software Watchdog Timing 2        | SWt2 | 8.8  | 10  | 11.2 | ms | (Note 1)                                           |

| Software Watchdog Timing 3        | SWt3 | 17.6 | 20  | 22.4 | ms | (Note 1)                                           |

| Software Watchdog Timing 4        | SWt4 | 28   | 32  | 36   | ms | (Note 1)                                           |

| Software Watchdog Timing 5        | SWt5 | 44.8 | 51  | 58   | ms | (Note 1)                                           |

| Software Watchdog Timing 6        | SWt6 | 65   | 74  | 83   | ms | (Note 1)                                           |

| Software Watchdog Timing 7        | SWt7 | 88   | 100 | 112  | ms | (Note 1)                                           |

| Software Watchdog Timing 8        | SWt8 | 167  | 190 | 213  | ms | (Note 1)                                           |

# FORCED WAKE-UP AND CYCLIC SENSE TIMINGS

$(note\ 2:\ cyclic\ sense\ and\ forced\ wake\ up\ timing\ accuracy\ are\ based\ on\ the\ sleep\ mode\ oscillator\ tolerance)$

| Sleep mode oscillator tolerance |      | -30  |    | +30  | %  | sleep mode (Note 2) |

|---------------------------------|------|------|----|------|----|---------------------|

| Cyclic Sense / FWU timing 1     | CYt1 | 22.4 | 32 | 41.6 | ms | sleep mode (Note 2) |

| Cyclic Sense / FWU timing 2     | CYt2 | 44.8 | 64 | 83.2 | ms | sleep mode (Note 2) |

| Parameter                   | Symbol | Min  | Тур  | Max   | Unit | Test Conditions     |

|-----------------------------|--------|------|------|-------|------|---------------------|

| Cyclic Sense / FWU timing 3 | CYt3   | 89.6 | 128  | 166.4 | ms   | sleep mode (Note 2) |

| Cyclic Sense / FWU timing 4 | CYt4   | 179  | 256  | 333   | ms   | sleep mode (Note 2) |

| Cyclic Sense / FWU timing 5 | CYt5   | 358  | 512  | 665   | ms   | sleep mode (Note 2) |

| Cyclic Sense / FWU timing 6 | CYt6   | 717  | 1024 | 1331  | ms   | sleep mode (Note 2) |

| Cyclic Sense / FWU timing 7 | CYt7   | 1434 | 2048 | 2662  | ms   | sleep mode (Note 2) |

| Cyclic Sense / FWU timing 8 | CYt8   | 5734 | 8192 | 10650 | ms   | sleep mode (Note 2) |

# **GND SHIFT DETECTION**

(note 3: no over lap between two adjacent thresholds).

| Ground Shift Threshold 1 (Note 3) | GS1 | -1   | -0.7 | -0.3 | V | CAN Transceiver Active In<br>Two-wire Operation |

|-----------------------------------|-----|------|------|------|---|-------------------------------------------------|

| Ground Shift Threshold 2 (Note 3) | GS2 | -1.5 | -1.2 | -0.8 | V | CAN Transceiver Active In<br>Two-wire Operation |

| Ground Shift Threshold 3 (Note 3) | GS3 | -2   | -1.7 | -1.3 | V | CAN Transceiver Active In<br>Two-wire Operation |

| Ground Shift Threshold 4 (Note 3) | GS4 | -2.6 | -2.2 | -1.7 | V | CAN Transceiver Active In<br>Two-wire Operation |

Figure 1. Input Timing Switch Characteristics

# **Thermal Management**

The MC33389 is proposed in two different packages. HSOP20 for high power applications and SO28WB with 8 pins to the leadframe for medium power applications.

# **HSOP20 Package**

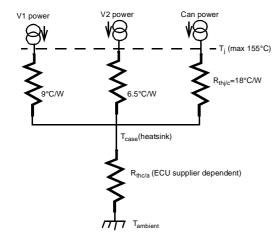

For such a package, the heat flow is mainly vertical and each heat source (dissipating element) can be seen as an independent thermal resistance to the Heatsink. The thermal network can be roughly depicted as:

Figure 2. HSOP20 Simplified Thermal Model

# Example

Assuming I $_{V1}$ =100mA at V $_{bat}$ =16V, I $_{V2}$ =150mA at V $_{bat}$ =16V (Excluding CAN consumption). I $_{CAN}$ =50mA at V $_{bat}$ =16V, we have : P $_{V1}$ =1.1W, P $_{V2}$ =1.65W, P $_{can}$ =0.55W

# System assumptions:

If  $T_{amb}=85^{\circ}C$  and  $R_{thc/a}=18^{\circ}C/W$ , this gives:  $T_{case}=T_{amb}+R_{th\ c/a}\times 3.3W=85+18\times 3.3=145^{\circ}C$  and  $T_{i}V1=T_{i}V2=T_{jcan}=155^{\circ}C$ .

This example represents the limit for the maximum power dissipations with a HSOP20.

# SO28WB Package

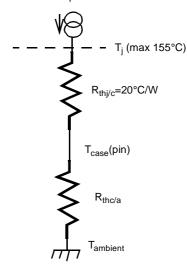

The case(pin) to junction R<sub>th</sub> is here represented by only one thermal resistance for the total power since the 3 power sources strongly interact on the silicon for such a package.

Figure 3. SO28WB Simplified Thermal Model

Total power

# Example

Assuming I $_{V1}$ =45mA at V $_{bat}$ =16V, I $_{V2}$ =45mA at V $_{bat}$ =16V (Excluding CAN consumption). I $_{CAN}$ =50mA at V $_{bat}$ =16V, we have : P $_{V1}$ =0.5W, P $_{V2}$ =0.5W, P $_{can}$ =0.55W thus P $_{total}$ =1.55W

# System assumptions:

If  $T_{amb}$ =85°C and  $R_{thc/a}$ =25°C/W, this gives:  $T_{case}$ = $T_{amb}$ + $R_{thc/a}$ x 1.55W=85+25x1.55 =124°C and  $T_i$ V1=124 + 20 x 1.55= 155°C.

This example represents the limit for the maximum power dissipations with a SO28WB.

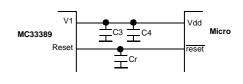

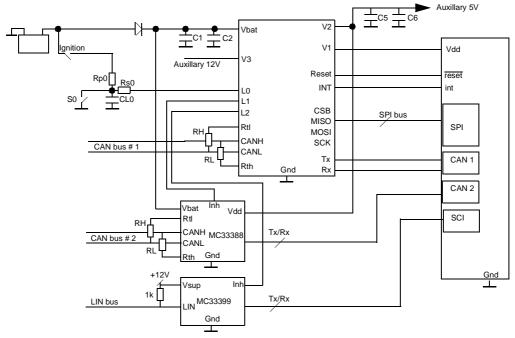

#### Introduction

The System Basis Chip is an integrated circuit dedicated to car body applications. It includes three main blocks:

- A dual voltage regulator

- Reset, watchdog, wake up inputs, cyclic wake up

- CAN low speed fault tolerant physical interface

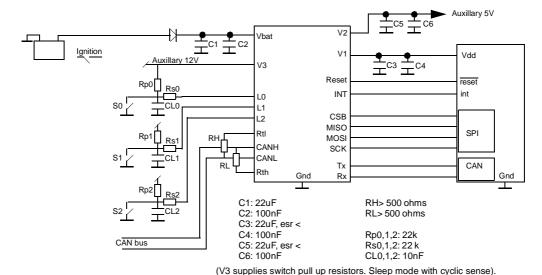

# **Supplies**

Two low drop regulators and one switch to  $V_{bat}$  are provided to supply the ECU microcontroller or peripherals, with independent control and monitoring through SPI.

# Voltage Regulator V1

V1 is a 5V, 3% low drop voltage regulator dedicated to the microcontroller supply. It can deliver up to 100mA and is totally protected against short to ground (current limitation) and overtemperature. V1 is active in Normal request, Normal and standby modes.

No forward parasitic diode exists from V1 to  $V_{bat}$ . This means that, if  $V_{bat}$  voltage drops below V1, no high current flowing from V1 to  $V_{bat}$  will discharge the capacitor connected to V1. Its stored energy will only be used to supply the microcontroller and gives time to save all relevant data.

# Undervoltage Reset

V1 is monitored for undervoltage (power up, power down) and a reset is provided at RSTB output for 1ms. This ensures proper initialization of the microcontroller at power-on or after supply is lost. On top of that, a flag is set in RSR register readable via the SPI.

#### Overtemperature Protection

V1 internal ballast transistor is monitored for overtemperature. Two detection thresholds are provided. A pre-warning threshold at 145°C and a shut-off threshold at 175°C. Once the first threshold is reached, a flag is set in the OTSR register. A maskable interrupt can be sent to the microcontroller. Once the second threshold is reached, a flag is set in the OTSR register, a maskable interrupt is sent to the microcontroller and V1 is switched off.

Once the junction temperature is back to the pre-warning threshold, V1 regulator it will be automatically switched on.

Table 4. V1 Control

| Conditions For V1 On                       | Conditions For V1 Off                         |

|--------------------------------------------|-----------------------------------------------|

| NormalRequest mode<br>(at V1 power on)     | Sleep mode (via SPI)                          |

| Normal mode (via SPI)                      | Shut-off temperature threshold reached        |

| Standby mode<br>(via SPI)                  | No V <sub>bat</sub> power supply (cold start) |

| V1 below pre-warning temperature threshold | Emergency mode                                |

| During Reset                               |                                               |

Note: current capability of V1, V2 and V3 depends upon the thermal management. Over temperature shutdown might be reached and lead to turn off of V1, V2 and V3 for output current below their max current capability.

# Voltage Regulator V2

V2 is a 5V low drop voltage regulator dedicated to peripherals supply. It can deliver up to 200mA and is protected against short to ground (current limitation) and overtemperature. V2 is active in Normal mode.

# <u>Undervoltage Detection</u>

V2 is monitored for undervoltage and a flag is set in the VSSR register.

# Overtemperature Protection

V2 internal ballast transistor is monitored for overtemperature. Two detection thresholds are provided. A pre-warning threshold at 140°C and a shut-off threshold at 165°C. Once the first threshold is reached, a flag is set in the OTSR register which is readable. A maskable interrupt can be sent to microcontroller.

Once the second threshold is reached, a flag is set in the OTSR register, V2 is switched off. It can only be switched on again via the SPI.

Table 5. V2 Control

| Conditions For V2 On      | Conditions For V2 Off    |

|---------------------------|--------------------------|

| Normal mode (via SPI) AND | Sleep mode, or standby   |

| V2 below shut off         | mode or NormalRequest or |

| temperature threshold     | emergency mode (via SPI) |

|                           | Shut-off temp.           |

|                           | threshold reached        |

|                           | V1 disabled              |

|                           | (for any reason)         |

#### Switch V3

V3 is a  $10\Omega$  switch to  $V_{bat}$ , it can be used to supply external contacts or relays. A great flexibility is given for the different possible ways for its control. It is protected against short to ground (current limitation).

# Overtemperature Protection

V3 output transistor is monitored for overtemperature. Once the threshold is reached, a flag is set in the VSSR register, V3 is switched off. It will be automatically switched on once the junction temperature is back to the pre-warning threshold.

Table 6. V3 Control

| Conditions For V3 On                                            | Conditions For V3 Off                                                  |

|-----------------------------------------------------------------|------------------------------------------------------------------------|

| Permanently in Normal mode if configured via SPI                | Permanently in Normal mode if configured                               |

| Permanently in Standby mode if configured via SPI               | NormalRequest mode                                                     |

| In sleep mode, during enable time of cyclic sense if configured | Permanently in Standby mode if configured                              |

|                                                                 | Permanently in sleep mode if configured                                |

|                                                                 | In sleep mode, during<br>disable time of cyclic<br>sense if configured |

|                                                                 | Overtemp threshold reached                                             |

|                                                                 | V1 disabled (for any reason)                                           |

|                                                                 | V2 over temperature shutdown                                           |

# Supply and V<sub>bat</sub> Block

# **V**bat Monitoring

V<sub>bat</sub> is the main power supply coming from the Battery voltage after an external protection diode (for reverse battery).

V<sub>bat</sub> is monitored for undervoltage and overvoltage.

# V<sub>bat</sub> Undervoltage

V<sub>bat</sub> is monitored for undervoltage, if it is below 4V the BatFail flag is set in the VSSR register and a maskable interrupt is sent to the microcontroller.

# **V**bat Overvoltage

When  $V_{bat}$  is > 20V, the BatHigh flag is set in the VSSR register. A maskable interrupt is sent to the microcontroller. No specific action is taken to reduce current consumption (to limit power dissipation). This is to let the entire flexibility at the microcontroller for decision.

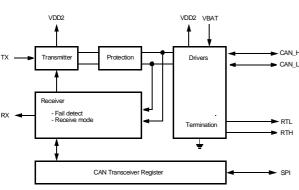

#### **CAN Transceiver**

The device incorporates a low speed 125kBaud CAN physical interface. Its electrical parameters for the CANL, CANH, Rtl,Rth,RX and TX pins are identical to the MC33388, standalone CAN physical interface.

The mode control for the CAN transceiver (normal, V<sub>bat</sub> standby, sleep, etc...) are selectable through the MC33389 SPI interface.

- Baud Rate up to 125kBit/s

- · Supports unshielded bus wires

- Short-circuit proof to Battery and Ground in 12V powered systems

- Supports single-wire transmission modes with Ground offset voltages up to 1.5V

- Automatic switching to single wire mode in case of Bus failures

- Automatic reset to differential mode if bus failure is removed

- Low EMI due to built in slope control and signal symmetry.

- · Fully integrated receiver filters

- Thermally protected

- Bus lines protected against Automotive transients.

- Low Current BusStandby mode with wake-up capability via the Bus.

- An unpowered node does not disturb the bus lines.

CAN transceiver simplified block diagramm

# VDD BAT S2 S3 RTL CANIH CANH RTH

# **CAN Transceiver Description**

The CAN transceiver is an interface between CAN protocol controller and the physical bus. It is intended for low speed applications up to 125kBit/s in passenger cars. It provides differential transmission capability, but will switch in error condition to single wire transmitter and/or receiver.

The rise and fall slopes are limited to reduce RFI. This allows use of an unshielded twisted pair or a parallel pair of wires for the bus. It supports transmission capability on either bus wire if one of the bus wire is corrupted. The logic failure detection automatically selects a suitable transmission mode.

In normal operation (no wiring failures), the differential bus state is output to RX. The differential receiver inputs are connected to CANH and CANL through integrated filters. The filtered inputs signals are also used for the single wire receivers. The CANH and CANL receivers have threshold voltages that assure maximum noise margin in single wire

modes. In the RXOnly mode, the transmitter is disabled but the receive part of the transceiver remains active. In this mode, RX reports bus and TX activity  $\overline{(RX)} = \overline{TX}$  or Bus dominant). Failure detection and management is the same as BusNormal mode.

#### **Failure Detector**

The failure detector is active in RXTX and RXOnly operation mode and detects the following single bus failures and switches to an appropriate mode.

- 1- CANH wire interrupted

- 2- CANL wire interrupted or shorted to 5V

- 3- CANH short-circuited to battery

- 4- CANL short-circuited to ground

- 5- CANH short-circuited to ground

- 6- CANL short-circuited to battery

- 7- CANL mutually shorted to CANH

- 8- CANH to V2 (5V)

Note: Shorts-circuit failures are detected for 0 to  $50\Omega$  shorts.

The differential receiver (CANH-CANL) threshold is set at -2.8V, this assures a proper reception in the normal operating modes. In case of failures 1, 2 and 5 the on-going message is not destroyed due to noise margin

Failures 3 and 6 are detected by comparators respectively connected to CANH and CANL. If the comparator threshold is exceeded for a certain time, the reception is switched to single wire mode. This time is needed to avoid false triggering by external RF fields. Recovery from these failures is detected automatically after a certain time-out (filtering).

Failures 4 and 7 initially result in a permanent dominant level at RX. After a time out, the CANL driver and the RTL pin are switched off, only a weak pull up at CANL remains. Reception continues by switching to single wire mode through CANH. When the failures 4 or 7 are removed, the recessive bus levels are restored. If the differential voltage remains below the recessive threshold for a certain time, reception and transmission switch back to the differential mode.

If any of the 8 wiring failure occurs, a flag is set in the TESRH and TESRL status registers. 8 different types of errors are distinguished out of these 8 errors and are separately stored in these register (See SPI Register Description Section on page 21). A maskable interrupt is sent to the microcontroller. On error recovery, the corresponding flag is reset after read-out operation.

During all single wire transmissions, the EMC performance (both immunity and emission) is worse than in differential mode. Integrated receiver filters suppress any HF noise induced into the bus wires. The cut-off frequency of these filters is a compromise between propagation delay and HF suppression. In single wire mode, low frequency noise can not be distinguished from the wanted signal.

In the event of a permanent dominant TX state (for more than 2ms) the output drivers are disabled. That assures the operation of the complete system in case of a permanent dominant TX state of one control unit. A defect control unit autonomous go to RXOnly or TermVCC mode.

#### **Low Power Modes**

The transceiver provides a low power modes which can be entered and exit by a SPI command. This is the BusStandby mode with the lowest power consumption (for the transceiver). CANL is biassed to the battery voltage via the RTL output and the pull-up current source on CANL and pull-down current source on CANH are disabled. Wake-up requests are recognized by the transceiver, when a dominant state is detected on either bus lines (Bus wake-up). On a Bus wake-up request the SBC will activate the INTB output or, if it is in sleep mode, switch to NormalRequest mode. This event is stored in the WUISR status register.

To prevent false wake-up due to transients or RF fields, wake-up threshold levels have to be maintained for a certain time. In the transceiver low power mode, failure detection circuit remains partly active to prevent increased power consumption in cases of error 3, 4,7 and 8.

#### **Power On**

After the  $V_{\text{bat}}$  supply is switched on, the SBC is in NormalRequest mode. The corresponding mode for the CAN transceiver is BusStandby.

The CAN transceiver is supplied by V2. As long as V2 is below its undervoltage threshold, the transceiver is forced to BusStandby mode (fail safe property).

#### **Protection**

A current limiting circuit protects the transmitter output stages against short-circuit to positive and negative battery voltage. If the junction temperature exceeds a maximum value, the transmitter output stages are disabled. Because the transmitter is responsible for a part of the power dissipation, this will result in a reduced power dissipation and hence a lower chip temperature. All other parts of the transceiver will remain operating. The CANH and CANL inputs are protected against electrical transients which may occur in an automotive environment.

#### **Consequence Of Failure Detections**

S1 is the switch from RTH to Ground

S2 is the switch from RTL to V2 and

S3 is the switch from RTL to V<sub>bat</sub>

For each failure type is given which switch is open and which driver is disabled.

Failure 1 : nothing done Failure 2 : nothing done

Failure3: S1 open. Driver CANH is disabled

Failure4: S2 and S3 open. Driver CANL is disabled

Failure5: Nothing done

Failure6: S2 and S3 open. Driver CANL disabled Failure7: S2 and S3 open. Driver CANL disabled

Failure8: S1 open. CANH driver disabled

# **CAN Transceiver Modes**

The CAN transceiver has its own functioning modes: RXTX mode, TermVBAT/TermVCC mode, and RXOnly mode. They are controlled by TCR register.

#### RXTX mode

Full transmitting and receiving capabilities are enabled. Full failure detection is enabled.

Note: Standard/RXTX and Extended/RXTX are equivalent.

#### RXOnly mode

The transmitter is disabled but the receive part of the transceiver remains active. In this mode, RX reports bus and TX activity  $(\overline{RX} = \overline{TX})$  or Bus dominant).

Note: Standard/RXOnly and Extended/RXOnly are equivalent.

# BusStandby Mode

This is the low power mode for the CAN transceiver. The driver and receivers are disabled. Wake-up capability on both bus lines as well as failure 3, 4, 7, 8 detection are enabled. In bus standby mode RTL termination is set to  $V_{\text{hat}}$ .

# **SBC MODES**

# **Global Power Save Concept**

The SBC allows to minimize power consumption of the ECU. Several operating modes are available to go to low power consumption when the full activity is not required. Several possibilities are provided to wake-up the ECU. This allows to have peripherals or the microcontroller switched off when no activity on the ECU is required.

Two switchable independent supply voltages (V1 and V2) are provided for optimum ECU power management.

#### Generalities

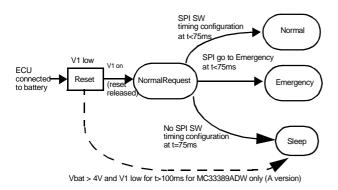

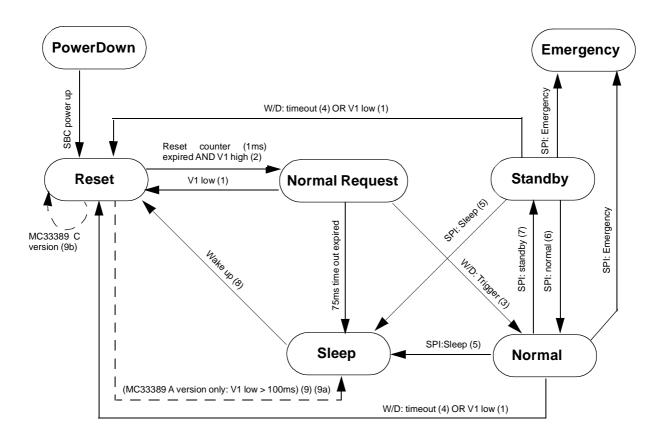

The SBC can be operated in four modes: Sleep, Standby, Normal and Emergency mode. After reset, the MC33389 is automatically initialised to a temporally mode, NormalRequest, Waiting for microcontroller configuration.

# **Reset Mode**

This mode is entered after SBC power up, or if an incorrect Software W/D trigger occurs. The minimum duration for reset mode is 1ms typical, and unless a V1 failure condition, the SBC enters the NormalRequest mode after reset.

In case of V1 failure condition leading to V1 low (ex: short to gnd), the SBC goes in reset mode. If V1 is still below reset threshold after 100ms, the behavior depends upon the device version A or C:

- A version: the MC33389ADW will enter sleep mode.

- C version: the MC33389CDW and the MC33389CDH will stay in reset mode.

# NormalRequest Mode

This is the default mode after MC33389 reset. V1 is active, V2 and V3 are passive. The SBC is not configured. The default values are set in the registers. The SBC is waiting for configuration data via the SPI.

If no SPI data is received 75ms after the Reset is released, then the SBC switches itself to sleep mode.

The data the SBC must receive to consider that the microcontroller starts the configuration sequence is the SW timing word (in SWCR register). Once received this SW timing word, the watchdog timer becomes active. Then any other control data can be sent from the microcontroller to SBC.

The watchdog is not active in NormalRequest mode before the SW timing word is programmed into the SBC. In this mode, neither V2 nor the CAN transmitter are active.

Table 8. NormalRequest: V1 active, V2&V3 passive

| Entering NormalRequest  | Leaving NormalRequest                                                |

|-------------------------|----------------------------------------------------------------------|

| SBC reset just released | When firstly receiving the<br>SW timing word, SBC<br>goes to Normal  |

|                         | If time-out without receiving SPI commands (75ms), SBC goes to sleep |

#### **SBC Normal Mode**

In this mode, V1 and V2 are active, V3 can be set active or passive via the SPI. Therefore, the whole ECU can be operated. Normal mode is entered by a SWCR register configuration in NormalRequest mode.

Table 9. SBC Normal Mode: V1 And V2 Are Active. V3 Is

Active Or Passive

| <b>Entering Normal Mode</b>                             | Leaving Normal Mode                                                                 |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| By SPI command                                          | By SPI command, going to any other mode                                             |  |

| After SWCR register configuration in NormalRequest mode | Watchdog time out, going to NormalRequest after activating Reset                    |  |

|                                                         | V1 undervoltage detection,<br>going to NormalRequest<br>mode after activating Reset |  |

# **SBC Standby Mode**

In this mode V1 is active, V2 is passive. V3 can be either permanently active or permanently passive. This is a low power mode with V1 active in order to have a fast reaction time in case of any wake-up.

For standby mode, the SBC monitors the SW. It means the microcontroller runs and is monitored and must serve a watchdog trigger.

Table 10. Standby: V1 Active V2 Passive, V3 Active Or Passive, Watchdog Is Active

| Entering Standby | Leaving Standby                                                                     |

|------------------|-------------------------------------------------------------------------------------|

|                  | If SW time-out going to<br>NormalRequest after<br>microcontroller Reset             |

| By SPI command   | By SPI command going to any other mode                                              |

|                  | V1 undervoltage detection,<br>going to NormalRequest<br>mode after activating Reset |

|                  | External activation of the RSTB pin                                                 |

# DEVICE DESCRIPTION SBC MODES

# **SBC Sleep Mode**

This is a low power consumption mode. V1 and V2 are disabled. V3 can be permanently disabled or cyclically active.

Table 11. SBC Sleep Mode: V1 And V2 Are Passive, V3

Passive Or Cyclic.

| Entering Sleep Mode                                                      | Leaving Sleep Mode                                                          |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| If SW timing not configured<br>75ms after entering<br>NormalRequest mode | CAN wake-up, going to<br>NormalRequest                                      |

| By SPI command                                                           | If a wake-up is detected with cyclic sense                                  |

| For MC33389ADW only: If<br>V1 is below V1 reset for<br>more than 100ms   | If a wake-up is detected with wake-up not connected to V3 (permanent sense) |

|                                                                          | Forced wake-up (See Forced Wake up Section)                                 |

|                                                                          | SPI wake-up (See Wake up<br>by SPI Section)                                 |

# **Emergency Mode**

In case the microcontroller detects the ECU or the system is not under control any more, it may decide to switch the SBC to the Emergency mode. V1, V2, V3 will be passive and wake-up are not detected. The only way to leave this mode is to disconnect the ECU from the Battery voltage (BatFail detection).

Table 12. SBC Emergency Mode: V1 And V2 V3 Are Passive

| Entering Emergency Mode | Leaving Emergency Mode                                       |  |

|-------------------------|--------------------------------------------------------------|--|

| By SPI command          | SBC BatFail detection (Disconnection of the Battery voltage) |  |

Figure 13. Typical Behaviour At Power On

Note: In Normalrequest, if an SPI command is received before the SW timing configuration (SWCR register), it will not be taken into account by the SBC (except for the go to Emergency mode).

# Correspondence between SBC and CAN Transceiver Modes

The table here below gives the different possible CAN transceiver modes versus SBC modes.

**Table 14. CAN Modes Versus SBC Modes**

| When SBC Is In The Following Mode  | CAN Transceiver<br>Can Be In |

|------------------------------------|------------------------------|

| Reset condition                    | Bus Standby mode             |

| NormalRequest                      | Bus Standby mode             |

| Normal                             | RXTX or RXOnly or BusStandby |

| Standby                            | Bus Standby                  |

| Sleep                              | Bus Standby                  |

| Emergency                          | Bus Standby                  |

| Normal & V2 off (over load) (note) | Bus standby                  |

Note: In case V2 is turned off either by SPI command (standby mode) or by the SBC itself due to V2 over load condition (V2 short to gnd or V2 over temperature) the CAN is automatically set into the Bus standby mode and does not return to TXRX mode automatically when V2 is back to 5V. The CAN must be re configured to TXRX or RXonly mode after a V2 turn off.

# Watchdog

#### General

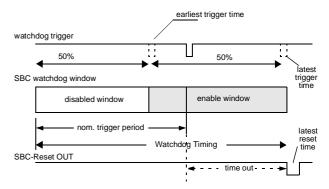

The software window watchdog function is used to monitors the microcontroller operation in Normal and in Standby modes. The window watchdog timing is derived from the SBC-clock. The desired watchdog timing must be first transmitted during the SBC configuration, in NormalRequest mode, via SPI to SWCR register. It can also be changed later on. Selectable watchdog timings are 5ms, 10ms, 20ms, 33ms, 50ms, 75ms, 100ms and 200ms. These timings correspond to the full disable window plus full enable window.

Figure 15. Window Watchdog Timing

As soon as the watchdog trigger is received in the enable window, the internal counter is reset and start a new disable window. The SBC triggers the watchdog word at CSB low to high transition. Any watchdog trigger outside the enable window leads to SBC reset.

# In Normal and Standby Modes

In normal mode the SBC get the watchdog word from the microcontroller via SPI. In case of a trigger time failure (no trigger or trigger outside the enable window) the SBC-reset is switched to active.

NormalRequest, Sleep And Emergency Mode Watchdog is not active in this modes.

# **WAKE-UP CAPABILITIES**

Several wake up capabilities are available.

# Forced Wake-up

The forced wake-up is enabled and disabled by SPI in V3R register. It is used in sleep mode to automatically wake-up the system by supplying V1 with proper reset. This correspond to jump into NormalRequest mode. If then, the SBC is not properly configured within 75ms, it switches back to sleep mode till the next wake-up. If both Cyclic sense and forced wake-up are enabled by the SPI in sleep mode, only Cyclic sense will be active.

The period of forced wake-up are 32ms, 64ms, 128ms, 256ms, 512ms, 1024ms, 2048ms, 8192ms, chosen by SPI in CYTCR register.

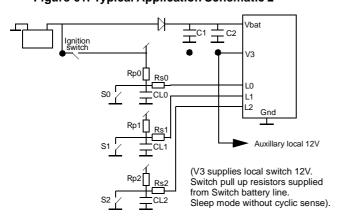

# Wake-up Inputs (Local Wake-up) / Cyclic Sense

SBC provides 3 wake-up inputs to monitor external events such as closing/opening of switches. The wake-up feature is available in Normal, Standby and sleep modes. The switches can be directly connected to  $V_{bat}$  or to V3. The SBC must be properly configured by setting bit WI2V3 in register V3R. In this case, wake-ups are only detected when V3 is On. It can take advantage of V3 cyclic sense feature. If both Cyclic sense and forced wake-up are enabled by the SPI in sleep mode, only Cyclic sense will be active.

# **Options For Wake Input**

Different conditions for wake-up can be chosen for wakeup input pins (via SPI in WUICR register).

No wake-up: No wake-up is detected, whatever occurs on wake-up inputs.

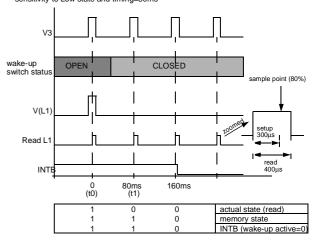

High state: if the input pin voltage is above the detection threshold during more than a 20µs filter time, a wake-up is detected. A flag is set in the WUISR register.

Low state: if the input pin voltage is below the detection threshold during more than a 20µs filter time, a wake-up is detected. A flag is set in the WUISR register.

Change of state: each change of the wake-up input pin is considered as a wake-up, if it lasts more than a  $20\mu s$  filter time. The first reference state (no wake-up) is the wake-up input state when the SBC is programmed to this option. A flag is set in the WUISR register.

Multiple sampling events: when wake-up inputs are used with V3 in cyclic sense in sleep mode.

For positive edge sensitivity, 2 samples Low followed by 2 samples High are necessary to validate the wake-up condition.

For negative edge sensitivity, 2 samples High followed by 2 samples Low are necessary to validate the wake-up condition.

For both edge sensitivity, 2 samples at a given state followed by 2 samples in the opposite state are necessary to validate the wake-up condition.

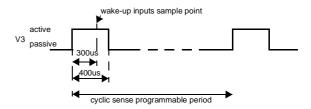

# Wake-up Inputs With Cyclic Sense

Connecting the external switches to V3 allows power saving since V3 can be programmed to be active, passive or cyclic (cyclic sense). This gives a great flexibility to reduce

total power consumption while allowing full wake-up capabilities. Cyclic sense is available only in sleep mode.

The period of the Cyclic sense can be chosen out of 8 different timings: 32ms, 64ms, 128ms, 256ms, 512ms, 1024ms, 2048ms, 8192ms programmable via SPI in CYTCR register. Once activated, V3 remains 'on' during  $400\mu s$ . The wake-up inputs states are sampled at  $300\mu s$ .

Figure 16. V3 Timing

Note: In sleep mode, the Cyclic Sense feature 'EXCLUSIVE OR' the forced Wake-up is chosen (not both).

Figure 17. Cyclic Sense Timing

Cyclic sense connected to wake-up inputs. Example with wake-up input L1 sensitivity to Low state and timing=80ms

# Wake Up Inputs With Permanent Sense

Wake up detection can also be done on a permanent way in Normal and Standby mode. If the contacts are connected to V3, wake ups are only detected if V3 is on.

Wake ups are also detected on a permanent way in sleep mode if the contacts are directly connected to V<sub>bat</sub> (if they are connected to V3, only cyclic sense is available in sleep mode).

#### **Local Wake-up Consequences**

In normal or standby modes, the real time state of each wake-up input pin is stored in the readable register WUIRTI. Wake-ups are detected according to the option chosen. A flag is set in the WUISR register. A maskable interrupt is sent via INTB output.

In sleep mode, a local wake-up leads to a jump to NormalRequest mode (via proper reset of the microcontroller). A flag is set in the WUISR register.

# **WAKE-UP CAPABILITIES**

Table 18. SBC Mode Versus Local Wake-up Behaviour

| SBC Modes             | Local Wake-up Behaviour                                                                                                                                                                  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NormalRequest         | No detection                                                                                                                                                                             |

| Normal and<br>Standby | Detection active according to the option. The event is stored in WUISR register.The SBC may activate INTB output. Real time state of each wake-up input pin available in WUIRTI register |

| Sleep                 | Detection active according to the option. The event is stored in WUISR register. The SBC switches to NormalRequest mode                                                                  |

| Emergency             | No detection                                                                                                                                                                             |

# Wake-up By SPI

In some applications, the microcontroller might be supplied by an external VDD and remains powered in SBC Sleep mode. In this case, a feature is provided which makes possible to wake-up the SBC by SPI activity.

After V1 is totally switched off in sleep mode (V1<1.5V), if a falling edge occurs on CSB (crossing 2.5V threshold), a wake-up by SPI is detected, the SBC switches to NormalRequest mode. A flag is set in ISR2.

#### **Interrupt Output**

The INTB output may be activated in the following cases:

- V<sub>bat</sub> overvoltage (BatHigh)

- V<sub>hat</sub> undervoltage (BatFail)

- High temperature on V1 or V2

- Pre-warning temperature on V1 or V2

- CAN bus failure

- SPI error

- Local wake-up (can be used for low battery detection)

- Bus wake-up

All these interrupts are maskable (See Register Description Section).

# **RSTB Input/Output**

The RSTB (reset) pin is an input/output pin. The typical reset duration from SBC to microcontroller is 1ms. If longer times are required, an external capacitor can be used. SBC provides two RSTB output pull-up currents.

A typical 30μA pull up when Vreset is below 2.5V and a 300uA pull up when reset voltage is higher than 2.5V.

RSTB is also an input for the SBC. It means the MC33389 is forced to NormalRequest mode after RSTB is released by the microcontroller

#### **GND SHIFT DETECTION**

# General

When normally working in two-wire operating mode, the CAN transmission can afford some ground shift between different nodes without trouble. Nevertheless, in case of bus failure, the transceiver switches to single-wire operation, therefore working with less noise margin. The affordable ground shift is decreased in this case.

The SBC is provided with a ground shift detection for diagnosis purpose. Four ground shift levels are selectable and the detection is stored in the GSLR register which is accessible via the SPI.

# **Detection Principle**

The gnd shift to detect is selected via the SPI out of 4 different values (-0.7V, -1.2V, -1.7V, -2.2V). At each TX falling edge (end of recessive state) CANH voltage is sensed. If it is detected to be below the selected gnd shift threshold, the bit SHIFT is set at 1 in GSLR register. No filter is implemented. Required filtering for reliable detection should be done by software (e.g. several trials).

# **DEVICE DESCRIPTION**

# Differences between MC33389ADW and MC33389CDW and CDH

In addition to the package there is a behavioural difference between the A and C version. In the A version: if in reset mode V1 stays below reset threshold for more than 100ms, the SBC automatically enters sleep mode. This could be the case if V1 is shorted or permanently over loaded, and going to sleep mode would then avoid system over current consumption. In the C version: if V1 is below reset threshold, the SBC enters and stays in reset mode (reset low) permanently. The table below summarizes the SBC operation modes.

**Table 19. SBC Operation Mode**

| mode              | V1 & V2 regulators, V3 switch                             | Wake up<br>capabilities<br>(if enabled)                | Reset pin                                                                     | INT                                                                                | Software<br>Watchdog | CAN cell                             |

|-------------------|-----------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------|--------------------------------------|

| Reset<br>state    | V1: ON (unless<br>failure condition<br>V2: OFF<br>V3: OFF |                                                        | Low<br>(duration 1ms)                                                         |                                                                                    |                      | TermVbat                             |

| Normal<br>Request | V1: ON (75ms<br>time out)<br>V2: OFF<br>V3: OFF           |                                                        | High.<br>(Active low -go to<br>reset state- if V1<br>under voltage<br>occurs) |                                                                                    |                      | Term Vbat                            |

| Normal            | V1: ON<br>V2: ON<br>V3: ON or OFF                         |                                                        | High. (Active low -go to reset state- if W/D or V1 under voltage occurs)      | If enabled,<br>signal failure<br>condition or L0/<br>L1/L2 inputs<br>state change. | Running              | Tx/Rx, or<br>Rx Only,<br>or TermVbat |