## **LXT9784**

#### Low-Power Octal PHY

#### **Datasheet**

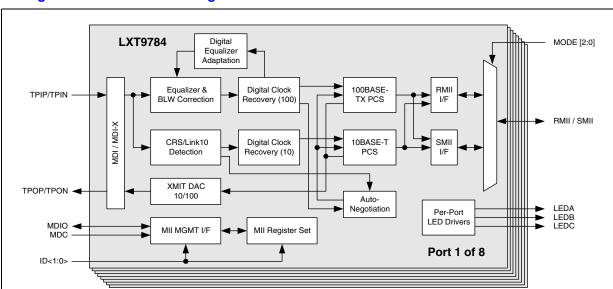

The LXT9784 is an eight-port Fast Ethernet PHY Transceiver supporting IEEE 802.3 10Mbps and 100Mbps physical layer applications. It provides both a Reduced Media Independent Interface (RMII) and a Serial Media Independent Interface (SMII) for switching and other independent port applications. In RMII mode, each PHY has a discrete exposed RMII interface, and in SMII mode a discrete exposed SMII interface. All network ports provide a Twisted-Pair (TP) interface for a 10/100BASE-TX connection.

The LXT9784 provides three discrete LED driver outputs for each port. The device supports both half- and full-duplex 10Mbps and 100Mbps operation, and requires only a single 3.3V power supply. For low power applications the devices may be powered by a single 3.0V power supply. Advanced design techniques result in very low power requirements.

The LXT9784 also supports an auto-MDIX feature as well as an integrated Hardware Integrity (HWI) feature that utilizes a Time Domain Reflectometry (TDR) technique to locate and report problems with the cable plant.

#### **Product Features**

- Eight IEEE 802.3 Standard-compliant 10BASE-T or 100BASE-TX ports with integrated filters.

- Automatic MDI/MDIX switch over capability.

- Integrated Hardware Integrity (HWI): device ports detect and report cabling problems via MDIO.

- Uses 1:1 magnetic device for 10/100 Mbps operation, allowing low-cost design.

- Supports both IEEE 802.3u Auto-Negotiation and parallel detection operation.

- Controls all 8 ports through one single IEEE 802.3 Standard compliant MII management bus.

- Automatic polarity correction at 10M data rate.

- Robust baseline wander correction for improved 100BASE-TX performance.

- Eight Reduced MII (RMII) and Serial MII (SMII) ports for independent PHY port operation.

- Low power consumption, 3.0V and 3.3V operation.

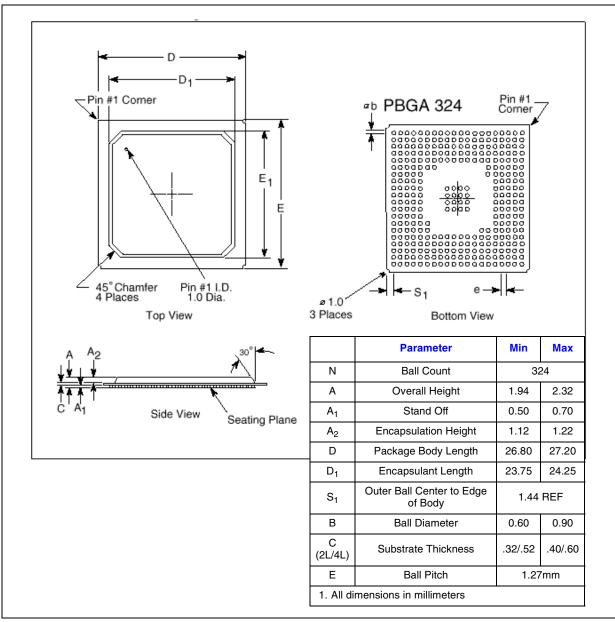

- 324-lead PBGA package.

- —LXT9784BC Commercial (0° to 70°C ambient).

- —LXT9784BE Extended (-40° to 85°C ambient).

Order Number: 249272-001

January 2001

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT9784 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Pin A | Assignments and Signal Descriptions                      | 10 |

|-----|-------|----------------------------------------------------------|----|

| 2.0 | Fund  | ctional Description                                      | 29 |

|     | 2.1   | Introduction                                             |    |

|     | 2.2   | LXT9784 Configuration                                    |    |

|     | 2.3   | 100BASE-TX Mode                                          |    |

|     | 2.0   | 2.3.1 100BASE-TX Receiver                                |    |

|     |       | 2.3.1.1 Digital Adaptive Equalizer                       |    |

|     |       | 2.3.1.1 Digital Adaptive Equalizer                       |    |

|     |       | 2.3.1.3 Baseline Wander Correction                       |    |

|     |       | 2.3.1.4 Decoder                                          |    |

|     |       | 2.3.1.5 100BASE-TX Receive Framing                       |    |

|     |       | 2.3.1.6 100BASE-TX RMII Data Reception                   |    |

|     |       | 2.3.1.7 100BASE-TX SMII Data Reception                   | 31 |

|     |       | 2.3.1.8 100BASE-TX Receive Error Detection and Reporting |    |

|     |       | 2.3.2 100BASE-TX Transmitter                             |    |

|     |       | 2.3.2.1 100BASE-TX 4B/5B Encoder                         | 33 |

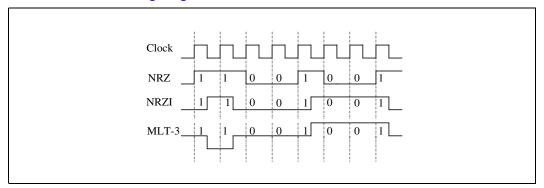

|     |       | 2.3.2.2 100BASE-TX Scrambler and MLT-3 Encoder           |    |

|     |       | 2.3.2.3 Transmit Driver                                  |    |

|     |       | 2.3.2.4 100BASE-TX Transmit Framing                      |    |

|     | 2.4   | 10BASE-T Mode                                            | 36 |

|     |       | 2.4.1 10BASE-T Receiver                                  |    |

|     |       | 2.4.1.1 10BASE-T Manchester Decoder                      |    |

|     |       | 2.4.1.2 10BASE-T Receive Buffer and Filter               |    |

|     |       | 2.4.1.3 10BASE-T Error Detection and Reporting           |    |

|     |       | 2.4.1.4 10BASE-T Link Integrity                          |    |

|     |       | 2.4.1.5 10BASE-T Jabber Control Function                 |    |

|     |       | 2.4.1.6 10BASE-T Full Duplex                             |    |

|     |       | 2.4.2 10BASE-T Transmit                                  |    |

|     |       | 2.4.2.1 10BASE-T Manchester Encoder                      |    |

|     |       | 2.4.2.2 10BASE-T Driver and Filter                       |    |

|     | 2.5   | MDI/MDI-X Function                                       |    |

|     |       | 2.5.1 MDI/MDI-X Auto Switching Activation                |    |

|     |       | 2.5.2 MDI/MDI-X Algorithm                                |    |

|     | 2.6   | Hardware Control Interface                               |    |

|     |       | 2.6.1 MDI-X (MDI Crossover)                              |    |

|     |       | 2.6.2 FRCLNK (Force Link)                                |    |

|     |       | 2.6.3 FRC34 (Force 34 Transmit Pattern)                  |    |

|     |       | 2.6.4 BP4B5B (4B/5B Bypass)                              |    |

|     |       | 2.6.5 SCRMBP (Scrambler Bypass)                          |    |

|     | 2.7   | PHY Addresses                                            |    |

|     | 2.8   | Link Status Interrupt                                    |    |

|     | 2.9   | Reset                                                    |    |

|     | 2.10  | LED Operation                                            |    |

|     | 2.11  | MII Management Interface Operation                       |    |

|     | 2.12  | Test Port Operation                                      | 44 |

|     |       | 2.12.1 NAND-Tree Test                                    | 44 |

|     |       | 2.12.2 XNOR-Tree Test                                    | 45 |

#### LXT9784 — Low-Power Octal PHY

|     |      | 2.12.3 NAND/XNOR Tree Chain Order | 45 |

|-----|------|-----------------------------------|----|

| 3.0 | Арр  | olication Information             | 48 |

|     | 3.1  | Magnetics                         | 48 |

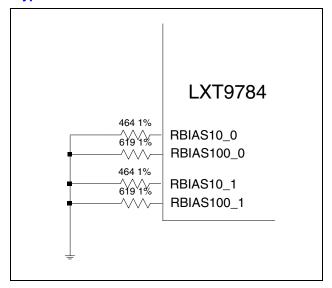

|     | 3.2  | Analog References (RBIAS)         | 48 |

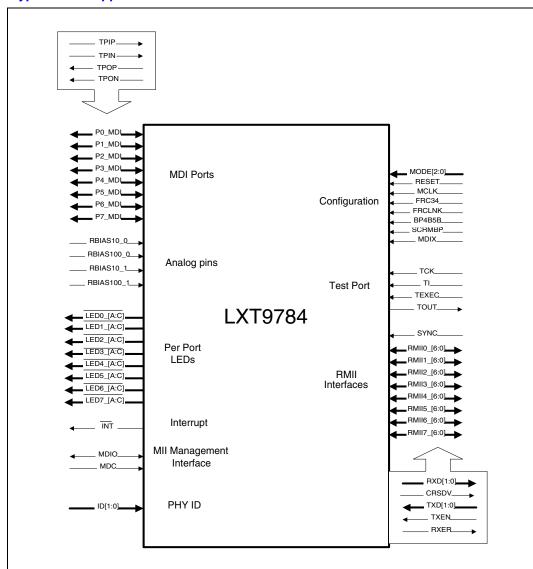

|     | 3.3  | RMII Applications                 | 48 |

|     |      | 3.3.1 RMII Clock                  | 49 |

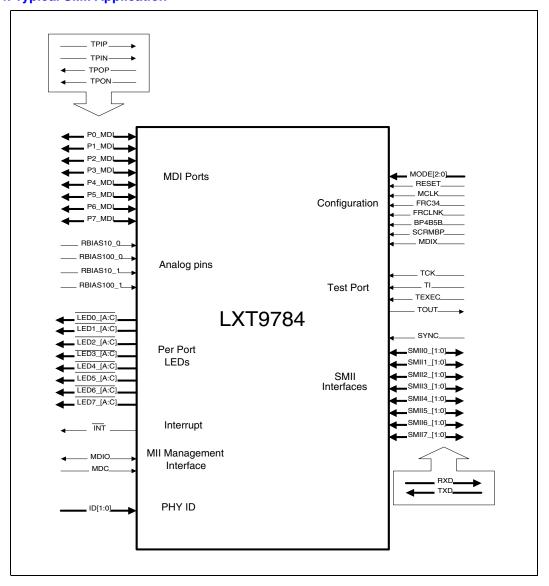

|     | 3.4  | SMII Applications                 | 49 |

|     |      | 3.4.1 SMII Clock                  | 50 |

| 4.0 | Test | t Specifications                  | 51 |

|     | 4.1  | DC Characteristics                | 52 |

|     | 4.2  | AC Characteristics                |    |

|     |      | 4.2.1 Common Characteristics      |    |

|     | 4.3  | RMII Interface                    |    |

|     | 4.4  | SMII Interface                    |    |

|     | 4.5  | Reset Timing Parameters           |    |

|     | 4.6  | Clock Specifications              |    |

|     |      | 4.6.1 MCLK Specifications         | 59 |

| 5.0 | Reg  | gister Definitions                | 60 |

| 6.0 | Mec  | chanical Specifications           | 68 |

# Figures

| 1  | LXT9784 Block Diagram                          | 9  |

|----|------------------------------------------------|----|

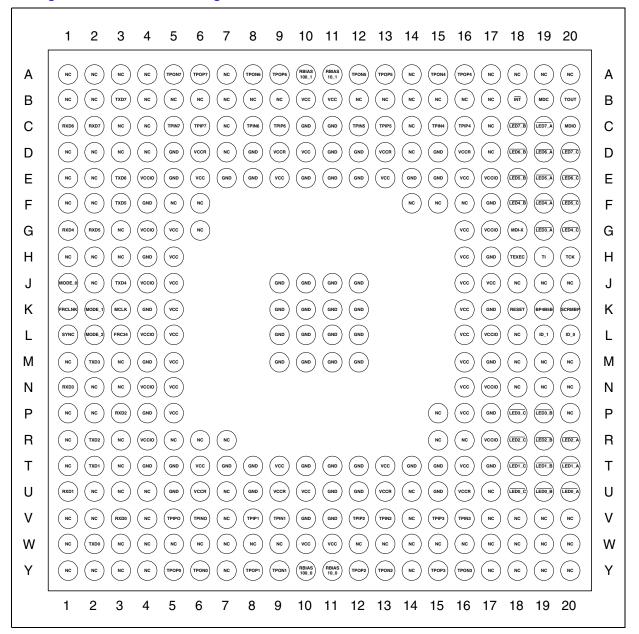

| 2  | LXT9784 Ball Assignments - RMII Mode           | 10 |

| 3  | LXT9784 Ball Assignments - SMII Mode           | 11 |

| 4  | LXT9784 PHY in a 10/100 Mbps Ethernet Solution | 29 |

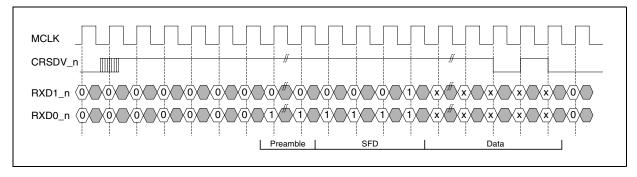

| 5  | RMII Data Reception                            | 32 |

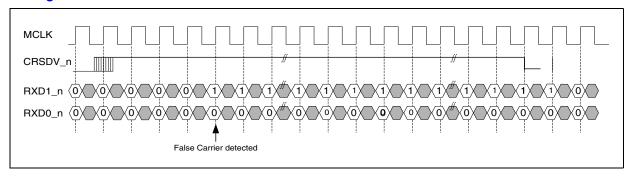

| 6  | False Carrier Detect                           |    |

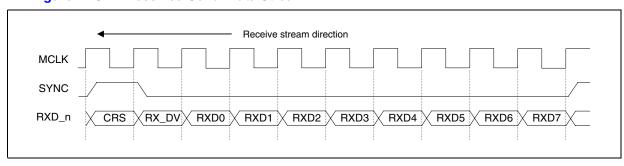

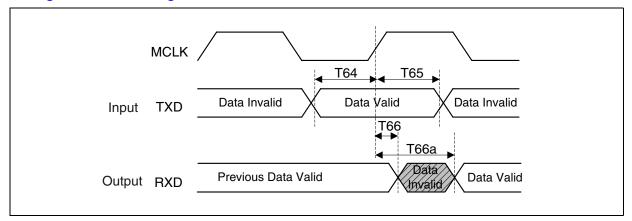

| 7  | SMII Received Serial Data Stream               | 33 |

| 8  | NRZ to MLT-3 encoding diagram                  | 34 |

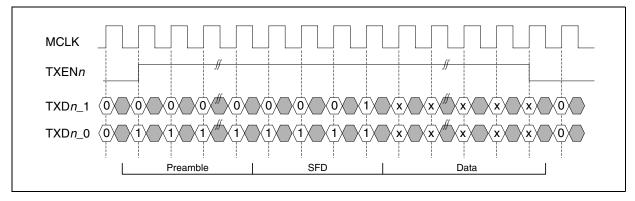

| 9  | RMII Data Transmission                         |    |

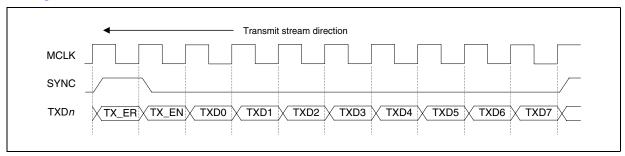

| 10 | SMII Transmit Data Serial Stream               | 36 |

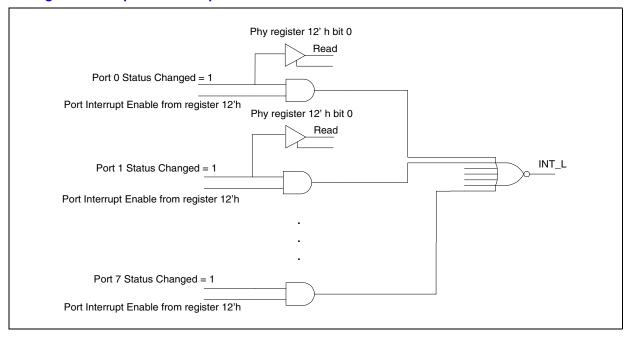

| 11 | Simplified Interrupt Structure                 | 42 |

| 12 | Typical RBIAS Circuit                          | 48 |

| 13 | Typical RMII Application                       | 49 |

| 14 | Typical SMII Application                       | 50 |

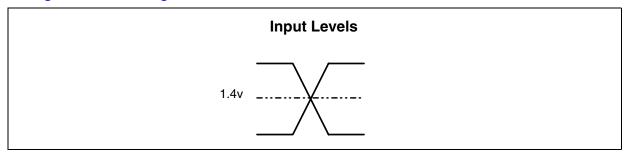

| 15 | AC Testing Level Conditions                    | 54 |

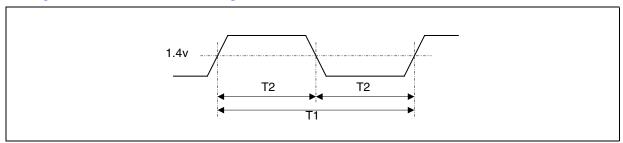

| 16 | MDC Clock AC Timing                            |    |

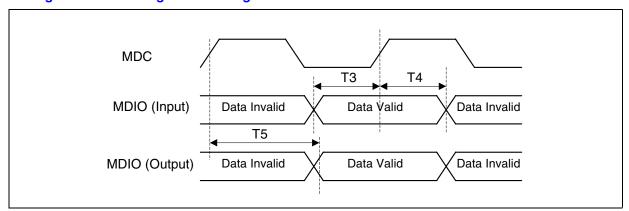

| 17 | MII Management Timing Parameters: MDC/MDIO     | 54 |

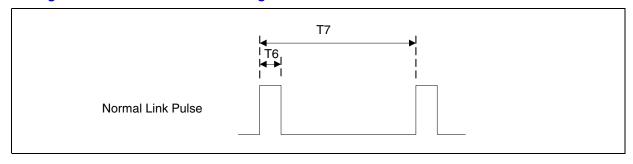

| 18 | Normal Link Pulse Timings                      | 55 |

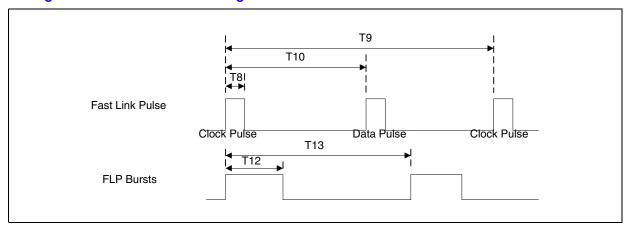

| 19 | Fast Link Pulse Timings                        | 55 |

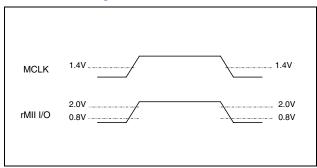

| 20 | RMII AC Testing Level Conditions               | 56 |

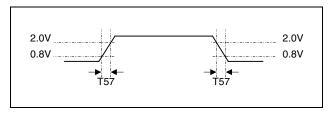

| 21 | RMII Rise and Fall Timings                     | 56 |

| 22 | RMII Timing Parameters                         | 57 |

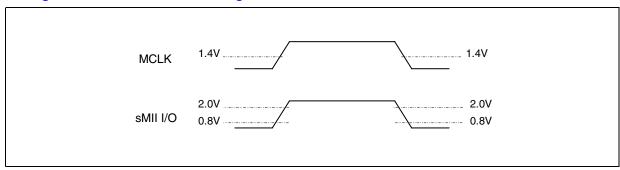

| 23 | SMII Mode - AC Testing Level Conditions        | 57 |

| 24 | SMII Timing Parameters                         | 58 |

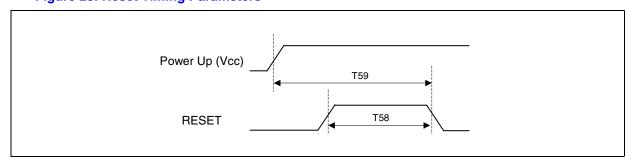

| 25 | Reset Timing Parameters                        | 58 |

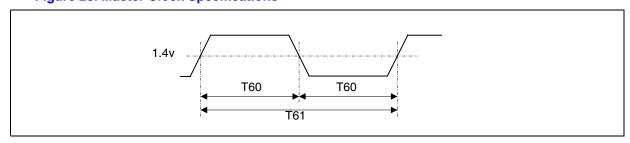

| 26 | Master Clock Specifications                    |    |

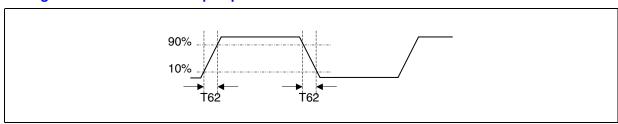

| 27 | Master Clock Slope Specifications              |    |

| 28 | Package Specifications                         |    |

## **Tables**

| 1  | Signal Types                                                         | 11 |

|----|----------------------------------------------------------------------|----|

| 2  | Numeric Pad Assignments                                              | 12 |

| 3  | Network Interface Signal Descriptions                                | 22 |

| 4  | MDIO Signal Descriptions                                             | 23 |

| 5  | LED Signal Descriptions                                              | 23 |

| 6  | Power Supply Signal Descriptions                                     | 24 |

| 7  | Miscellaneous Signal Descriptions                                    |    |

| 8  | RMII Mode Signal Descriptions                                        |    |

| 9  | SMII Mode Signal Descriptions                                        | 27 |

| 10 | Unused Pins                                                          |    |

| 11 | LXT9784 Modes of Operation                                           | 30 |

| 12 | SMII RXD_[7:0] Contents                                              |    |

| 13 | 4B/5B Coding                                                         |    |

| 14 | Straight-through Pin Assignments                                     |    |

| 15 | Crossed-over Pin Assignments                                         |    |

| 16 | PHY Addresses                                                        |    |

| 17 | LED Functionality                                                    |    |

| 18 | Activity LED Blink Rates                                             |    |

| 19 | MII Management Frame Format                                          | 43 |

| 20 | Glossary of Protocol Terms                                           | 44 |

| 21 | Test Mode Configuration                                              | 44 |

| 22 | Test Scan Chain                                                      | 45 |

| 23 | Magnetics Module Vendor                                              | 48 |

| 24 | Absolute Maximum Ratings                                             | 51 |

| 25 | Operating Conditions                                                 |    |

| 26 | Clock DC Characteristics                                             | 52 |

| 27 | RMII/SMII and General Interface1 DC Characteristics                  | 52 |

| 28 | LED DC Characteristics                                               | 52 |

| 29 | 10BASE-T Receiver Voltage/Current DC Characteristics                 | 52 |

| 30 | 10BASE-T Transmitter Voltage/Current DC Characteristics              | 53 |

| 31 | 100BASE-TX Receiver Voltage/Current DC Characteristics               | 53 |

| 32 | 100BASE-TX Transmitter Voltage/Current DC Characteristics            | 53 |

| 33 | MII Management Clock Specifications                                  | 54 |

| 34 | MII Management Interface Timing Parameters                           | 55 |

| 35 | 10BASE-T Normal Link Pulse (NLP) Timing Parameters                   | 55 |

| 36 | Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters             | 55 |

| 37 | 100BASE-TX Transmitter AC Specifications                             | 56 |

| 38 | RMII Interface Timing Parameters                                     | 57 |

| 39 | SMII Interface Timing Parameters                                     | 58 |

| 40 | Reset Timing Parameters                                              | 58 |

| 41 | MCLK Specifications                                                  | 59 |

| 42 | Bit Type Designations                                                | 60 |

| 43 | Control Register (Register 0) Bit Definitions                        | 60 |

| 44 | Status Register (Register 1) Bit Definitions                         | 61 |

| 45 | PHY Identifier Register (Register 2) Bit Definitions                 |    |

| 46 | PHY Identifier Register (Register 3) Bit Definitions                 |    |

| 47 | Auto-Negotiation Advertisement Register (Register 4) Bit Definitions | 62 |

| 48 | Auto-Negotiation Link Partner Ability Register (Base Page)           |    |

|    | (Register 5) Bit Definitions                                         | 63 |

#### Low-Power Octal PHY — LXT9784

| 49 | Auto-Negotiation Expansion Register (Register 6) Bit Definitions       | .63  |

|----|------------------------------------------------------------------------|------|

| 50 | Register 16 (10 Hex) Status and Control                                | .64  |

| 51 | Register 17 (11 Hex) Special Control                                   | .64  |

| 52 | Register 18 (12 Hex) PHY Interrupt Register                            | .65  |

| 53 | Reg 19 (13 Hex) 100 BASE-TX RCV False Carrier Counter                  | .65  |

| 54 | Reg 20 (14 Hex) 100BASETx Receive Disconnect Counter                   | .66  |

| 55 | Reg 21 (15 Hex) 100BASETx Receive Error Frame Counter                  | . 66 |

| 56 | Reg 22 (16 Hex) Receive Symbol Error Counter                           | . 66 |

| 57 | Reg 23 (17 Hex) 100BASETx Receive Premature End of Frame Error Counter | 66   |

| 58 | Reg 24 (18 Hex) 10BASET Receive End of Frame Error Counter             | . 66 |

| 59 | Reg 25 (19 Hex) 10BASET Transmit Jabber Detect Counter                 | . 66 |

| 60 | Reg 26 (1A Hex) Reserved                                               | .67  |

| 61 | Register 27 (1B Hex) PHY Special Control                               | .67  |

|    |                                                                        |      |

## **Revision History**

| Revision | Date | Description |

|----------|------|-------------|

|          |      |             |

|          |      |             |

|          |      |             |

Figure 1. LXT9784 Block Diagram

## 1.0 Pin Assignments and Signal Descriptions

Figure 2. LXT9784 Ball Assignments - RMII Mode

|   | 1      | 2      | 3        | 4     | 5       | 6       | 7   | 8       | 9       | 10             | 11            | 12      | 13      | 14  | 15      | 16      | 17    | 18       | 19       | 20     | 1      |

|---|--------|--------|----------|-------|---------|---------|-----|---------|---------|----------------|---------------|---------|---------|-----|---------|---------|-------|----------|----------|--------|--------|

| Α | NC     | TXD7_1 | NC       | NC    | (TPON7) | (TPOP7) | NC  | (TPON6) | (TPOP6) | RBIAS 100_1    | RBIAS 10_1    | (TPON5) | (TPOP5) | NC  | (TPON4) | TPOP4   | NC    | NC       | NC       | NC     | Α      |

| В | CRSDV7 | TXEN7  | TXD7_0   | NC    | NC      | NC      | NC  | NC      | NC      | VCC            | VCC           | NC      | NC      | NC  | NC      | NC      | NC    | (INT)    | MDC      | TOUT   | В      |

| С | RXD6_0 | RXD7_0 | RXD7_1   | NC    | (TPIN7) | (TPIP7) | NC  | (TPIN6) | (TPIP6  | GND            | GND           | (TPIN5) | (TPIP5) | NC  | (TPIN4) | (TPIP4) | NC    | (LED7_B) | (LED7_A  | MDIO   | С      |

| D | TXEN6  | CRSDV6 | RXD6_1   | NC    | GND     | VCCR    | NC  | GND     | VCCR    | vcc            | GND           | GND     | VCCR    | NC  | GND     | VCCR    | NC    | (LED6_B) | LED6_A   | LED7_C | D      |

| E | TXD5_1 | TXD6_1 | (TXD6_0) | VCCIO | GND     | VCC     | GND | GND     | VCC     | GND            | GND           | GND     | VCC     | GND | GND     | vcc     | VCCIO | (LED5_B) | LED5_A   | LED6_C | Е      |

| F | CRSDV5 | TXEN5  | TXD5_0   | GND   | NC      | NC      |     |         |         |                |               |         |         | NC  | NC      | NC      | GND   | LED4_B   | (LED4_A) | LED5_C | F      |

| G | RXD4_0 | RXD5_0 | (RXD5_1) | VCCIO | vcc     | NC      |     |         |         |                |               |         |         |     |         | VCC     | VCCIO | MDI-X    | (LED3_A  | LED4_C | G      |

| Н | TXEN4  | CRSDV4 | RXD4_1   | GND   | vcc     |         |     |         |         |                |               |         |         |     |         | vcc     | GND   | TEXEC    | П        | TCK    | Н      |

| J | MODE_0 | TXD4_1 | TXD4_0   | VCCIO | vcc     |         |     |         | GND     | GND            | GND           | GND     |         |     |         | vcc     | vcc   | NC       | NC       | NC     | J      |

| K | FRCLNK | MODE_1 | MCLK     | GND   | vcc     |         |     |         | GND     | GND            | GND           | GND     |         |     |         | VCC     | GND   | RESET    | BP4B5B   | SCRMBP | K      |

| L | TXD4   | MODE_2 | FRC34    | VCCIO | vcc     |         |     |         | GND     | GND            | GND           | GND     |         |     |         | vcc     | VCCIO | RXERO    | (ID_1)   | (ID_0  | L      |

| М | TXEN3  | TXD3_0 | (TXD3_1) | GND   | vcc     |         |     |         | GND     | GND            | GND           | GND     |         |     |         | vcc     | GND   | RXER3    | RXER2    | RXER1  | М      |

| N | RXD3_0 | RXD3_1 | CRSDV3   | VCCIO | vcc     |         |     |         |         |                |               |         |         |     |         | vcc     | VCCIO | (RXER6)  | (RXER5)  | RXER4  | N      |

| Р | CRSDV2 | RXD2_1 | RXD2_0   | GND   | vcc     |         |     |         |         |                |               |         |         |     | NC      | vcc     | GND   | (LED3_C  | (LED3_B) | RXER7  | Р      |

| R | TXD2_1 | TXD2_0 | TXEN2    | VCCIO | NC      | NC      | NC  |         |         |                |               |         |         |     | NC      | NC      | VCCIO | (LED2_C  | LED2_B   | LED2_A | R      |

| Т | TXEN1  | TXD1_0 | (TXD1_1) | GND   | GND     | vcc     | GND | GND     | vcc     | GND            | GND           | GND     | vcc     | GND | GND     | VCC     | GND   | (LED1_C  | (LED1_B) | LED1_A | Т      |

| U | RXD1_0 | RXD1_1 | CRSDV1)  | NC    | GND     | VCCR    | NC  | GND     | VCCR    | VCC            | GND           | GND     | VCCR    | NC  | GND     | VCCR    | NC    | (LEDO_C  | LEDO_B   | LEDO_A | U      |

| V | CRSDVO | RXD0_1 | RXD0_0   | NC    | TPIPO   | TPINO   | NC  | (TPIP1  | (TPIN1) | GND            | GND           | (TPIP2  | (TPIN2) | NC  | TPIP3   | (TPIN3) | NC    | NC       | NC       | NC     | V      |

| W | TXD0_1 | TXD0_0 | TXENO    | NC    | NC      | NC      | NC  | NC      | NC      | VCC            | vcc           | NC      | NC      | NC  | NC      | NC      | NC    | NC       | NC       | NC     | W      |

| Υ | NC     | NC     | NC       | NC    | (TPOP0) | TPONO   | NC  | (TPOP1) | (TPON1) | RBIAS<br>100_0 | RBIAS<br>10_0 | (TPOP2) | (TPON2) | NC  | (трорз) | (TPON3) | NC    | NC       | NC       | NC     | Υ      |

|   | 1      | 2      | 3        | 4     | 5       | 6       | 7   | 8       | 9       | 10             | 11            | 12      | 13      | 14  | 15      | 16      | 17    | 18       | 19       | 20     | ,<br>T |

Figure 3. LXT9784 Ball Assignments - SMII Mode

Table 1. Signal Types

| Туре | Name                                            | Definition                   |  |  |  |  |

|------|-------------------------------------------------|------------------------------|--|--|--|--|

| 1    | Input                                           | Standard input only signal.  |  |  |  |  |

| 0    | Output                                          | Standard output-only signal. |  |  |  |  |

| I/O  | Bidirectional This is an input and output ball. |                              |  |  |  |  |

Table 1. Signal Types

| Туре                 | Name                    | Definition                                                                         |  |  |  |  |  |

|----------------------|-------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| OD Open-drain output |                         | This open drain ball allows multiple devices to share this signal as a wired-ORed. |  |  |  |  |  |

| OZ                   | Tri-state output        | High impedance                                                                     |  |  |  |  |  |

| PU                   | Internal weak pull-up   | Input ball, external pull-up device is not required.                               |  |  |  |  |  |

| PD                   | Internal weak pull-down | Input ball, external pull-down device is not required.                             |  |  |  |  |  |

| EPU                  | External pull up        | Pull this ball up to 3.3V through a 10K ohm resistor.                              |  |  |  |  |  |

| EPD                  | External pull down      | Pull this ball down to ground through a 10K ohm resistor.                          |  |  |  |  |  |

| MLT                  | Multi-level analog I/O  | Presented on MDI balls while in 100M mode of operation.                            |  |  |  |  |  |

| A_PWR                | Power (analog)          | Connect the marked balls to separate analog planes.                                |  |  |  |  |  |

| NC                   | No Connect              | This ball is not used and can be left floating.                                    |  |  |  |  |  |

**Table 2. Numeric Pad Assignments**

| Ball       | Symbol             | Type <sup>1</sup> | Reference for Full Description |

|------------|--------------------|-------------------|--------------------------------|

| A1         | -                  | NC                | -                              |

| A2         | TXD7_1 (RMII)      | I                 | Table 8 on page 26             |

| AZ         | Not Used (SMII)    | NC                | -                              |

| A3         | -                  | NC                | -                              |

| A4         | -                  | NC                | -                              |

| <b>A</b> 5 | TPON7              | MLT               | Table 3 on page 22             |

| A6         | TPOP7              | MLT               | Table 3 on page 22             |

| A7         | -                  | NC                | -                              |

| A8         | TPON6              | MLT               | Table 3 on page 22             |

| A9         | TPOP6              | MLT               | Table 3 on page 22             |

| A10        | RBIAS100_1         | I                 | Table 7 on page 25             |

| A11        | RBIAS10_1          | I                 | Table 7 on page 25             |

| A12        | TPON5              | MLT               | Table 3 on page 22             |

| A13        | TPOP5              | MLT               | Table 3 on page 22             |

| A14        | -                  | NC                | -                              |

| A15        | TPON4              | MLT               | Table 3 on page 22             |

| A16        | TPOP4              | MLT               | Table 3 on page 22             |

| A17        | -                  | NC                |                                |

| A18        | -                  | NC                | -                              |

| A19        | -                  | NC                | -                              |

| A20        | -                  | NC                | -                              |

| B1         | CRSDV7 (RMII)      | 0                 | Table 3 on page 22             |

| DI         | Not Used (SMII)    | NC                | -                              |

| 1. Refer   | to Table 1 on page | 11 for Signal     | Type definitions.              |

Table 2. Numeric Pad Assignments (Continued)

| Ball     | Symbol               | Type <sup>1</sup> | Reference for Full Description |

|----------|----------------------|-------------------|--------------------------------|

| _        | TXEN7 (RMII)         | I                 | Table 8 on page 26             |

| B2       | Not Used (SMII)      | NC                | -                              |

| B        | TXD7_0 (RMII)        | I                 | Table 9 on page 27             |

| В3       | TXD7 (SMII)          | I                 | Table 9 on page 27             |

| B4       | -                    | NC                | -                              |

| B5       | -                    | NC                | -                              |

| В6       | -                    | NC                | -                              |

| B7       | -                    | NC                | -                              |

| B8       | -                    | NC                | -                              |

| В9       | -                    | NC                | -                              |

| B10      | VCC                  |                   | Table 6 on page 24             |

| B11      | VCC                  |                   | Table 6 on page 24             |

| B12      | -                    | NC                | -                              |

| B13      | -                    | NC                |                                |

| B14      | -                    | NC                |                                |

| B15      | -                    | NC                |                                |

| B16      | -                    | NC                |                                |

| B17      | -                    | NC                |                                |

| B18      | ĪNT                  | OD                | Table 7 on page 25             |

| B19      | MDC                  | 1                 | Table 4 on page 23             |

| B20      | TOUT                 | 0                 | Table 7 on page 25             |

| C1       | RXD6_0 (RMII)        | 0                 | Table 8 on page 26             |

|          | RXD6 (SMII)          | 0                 | Table 9 on page 27             |

| C2       | RXD7_0 (RMII)        | 0                 | Table 8 on page 26             |

| - J2     | RXD7 (SMII)          | 0                 | Table 9 on page 27             |

| C3       | RXD7_1 (RMII)        | 0                 | Table 8 on page 26             |

|          | Not Used (SMII)      | NC                |                                |

| C4       | -                    | NC                |                                |

| C5       | TPIN7                | MLT               | Table 3 on page 22             |

| C6       | TPIP7                | MLT               | Table 3 on page 22             |

| C7       | -                    | NC                |                                |

| C8       | TPIN6                | MLT               | Table 3 on page 22             |

| C9       | TPIP6                | MLT               | Table 3 on page 22             |

| C10      | GND                  |                   |                                |

| C11      | GND                  |                   |                                |

| C12      | TPIN5                | MLT               | Table 3 on page 22             |

| C13      | TPIP5                | MLT               | Table 3 on page 22             |

| 1. Refer | to Table 1 on page 1 | 11 for Signal     | Type definitions.              |

Table 2. Numeric Pad Assignments (Continued)

| Ball    | Symbol               | Type <sup>1</sup> | Reference for Full Description |

|---------|----------------------|-------------------|--------------------------------|

| C14     | -                    | NC                |                                |

| C15     | TPIN4                | MLT               | Table 3 on page 22             |

| C16     | TPIP4                | MLT               | Table 3 on page 22             |

| C17     | -                    | NC                |                                |

| C18     | LED7_B               | 0                 | Table 5 on page 23             |

| C19     | LED7_A               | 0                 | Table 5 on page 23             |

| C20     | MDIO                 | I/O               | Table 4 on page 23             |

| D1      | TXEN6 (RMII)         | I                 | Table 8 on page 26             |

| וט      | Not Used (SMII)      | NC                |                                |

| D2      | CRSDV6 (RMII)        | 0                 | Table 8 on page 26             |

| DΖ      | Not Used (SMII)      | NC                |                                |

| D3      | RXD6_1 (RMII)        | 0                 | Table 8 on page 26             |

|         | Not Used (SMII)      | NC                |                                |

| D4      | -                    | NC                |                                |

| D5      | GND                  |                   |                                |

| D6      | VCCR                 | A_PWR             |                                |

| D7      | -                    | NC                |                                |

| D8      | GND                  |                   |                                |

| D9      | VCCR                 | A_PWR             |                                |

| D10     | VCC                  |                   |                                |

| D11     | GND                  |                   |                                |

| D12     | GND                  |                   |                                |

| D13     | VCCR                 | A_PWR             |                                |

| D14     | -                    | NC                |                                |

| D15     | GND                  |                   |                                |

| D16     | VCCR                 | A_PWR             |                                |

| D17     | -                    | NC                |                                |

| D18     | LED6_B               | 0                 | Table 5 on page 23             |

| D19     | LED6_A               | 0                 | Table 5 on page 23             |

| D20     | LED7_C               | 0                 | Table 5 on page 23             |

| E1      | TXD5_1 (RMII)        | I                 | Table 8 on page 26             |

| E1      | Not Used (SMII)      | NC                |                                |

| E2      | TXD6_1 (RMII)        | I                 | Table 8 on page 26             |

| EZ      | Not Used (SMII)      | NC                |                                |

| Eo      | TXD6_0 (RMII)        | I                 | Table 8 on page 26             |

| E3      | TXD6 (SMII)          | I                 | Table 9 on page 27             |

| E4      | VCCIO                |                   |                                |

| 1. Refe | r to Table 1 on page | 11 for Signal     | Type definitions.              |

Table 2. Numeric Pad Assignments (Continued)

| Ball     | Symbol             | Type <sup>1</sup> | Reference for Full Description |

|----------|--------------------|-------------------|--------------------------------|

| E5       | GND                |                   |                                |

| E6       | VCC                |                   |                                |

| E7       | GND                |                   |                                |

| E8       | GND                |                   |                                |

| E9       | VCC                |                   |                                |

| E10      | GND                |                   |                                |

| E11      | GND                |                   |                                |

| E12      | GND                |                   |                                |

| E13      | VCC                |                   |                                |

| E14      | GND                |                   |                                |

| E15      | GND                |                   |                                |

| E16      | VCC                |                   |                                |

| E17      | VCCIO              |                   |                                |

| E18      | LED5_B             | 0                 | Table 5 on page 23             |

| E19      | LED5_A             | 0                 | Table 5 on page 23             |

| E20      | LED6_C             | 0                 | Table 5 on page 23             |

| F4       | CRSDV5 (RMII)      | 0                 | Table 8 on page 26             |

| F1       | Not Used (SMII)    | NC                |                                |

| F0.      | TXEN5 (RMII)       | 1                 | Table 8 on page 26             |

| F2       | Not Used (SMII)    | NC                |                                |

| F0       | TXD5_0 (RMII)      | 1                 | Table 8 on page 26             |

| F3       | TXD5               | I                 | Table 9 on page 27             |

| F4       | GND                |                   |                                |

| F5       | -                  | NC                |                                |

| F6       | -                  | NC                |                                |

| F14      | -                  | NC                |                                |

| F15      | -                  | NC                |                                |

| F16      | -                  | NC                |                                |

| F17      | GND                |                   |                                |

| F18      | LED4_B             | 0                 | Table 5 on page 23             |

| F19      | LED4_A             | 0                 | Table 5 on page 23             |

| F20      | LED5_C             | 0                 | Table 5 on page 23             |

| C1       | RXD4_0 (RMII)      | 0                 | Table 8 on page 26             |

| G1       | RXD4 (SMII)        | 0                 | Table 9 on page 27             |

| 00       | RXD5_0 (RMII)      | 0                 | Table 8 on page 26             |

| G2       | RXD5 (SMII)        | 0                 | Table 9 on page 27             |

| 1. Refer | to Table 1 on page | 11 for Signal     | Type definitions.              |

Table 2. Numeric Pad Assignments (Continued)

| Ball    | Symbol               | Type <sup>1</sup> | Reference for Full Description |

|---------|----------------------|-------------------|--------------------------------|

| C2      | RXD5_1 (RMII)        | 0                 | Table 8 on page 26             |

| G3      | Not Used (SMII)      | NC                |                                |

| G4      | VCCIO                |                   |                                |

| G5      | VCC                  |                   |                                |

| G6      | -                    | NC                |                                |

| G16     | VCC                  |                   |                                |

| G17     | VCCIO                |                   |                                |

| G18     | MDI-X                | I-PU              | Table 7 on page 25             |

| G19     | LED3_A               | 0                 | Table 5 on page 23             |

| G20     | LED4_C               | 0                 | Table 5 on page 23             |

| H1      | TXEN4 (RMII)         | I                 | Table 8 on page 26             |

|         | NC (SMII)            | PD                |                                |

| H2      | CRSDV4 (RMII)        | 0                 | Table 8 on page 26             |

| 112     | NC (SMII)            | PD                |                                |

| Н3      | RXD4_1 (RMII)        | 0                 | Table 8 on page 26             |

| 113     | NC (SMII)            | PD                |                                |

| H4      | GND                  |                   |                                |

| H5      | VCC                  |                   |                                |

| H16     | VCC                  |                   |                                |

| H17     | GND                  |                   |                                |

| H18     | TEXEC                | I                 | Table 7 on page 25             |

| H19     | TI                   | I                 | Table 7 on page 25             |

| H20     | TCK                  | I                 | Table 7 on page 25             |

| J1      | MODE_0               | I                 | Table 7 on page 25             |

| J2      | TXD4_1 (RMII)        | I                 | Table 7 on page 25             |

| JZ      | Not Used (SMII)      | NC                |                                |

| J3      | TXD4_0 (RMII)        | I                 | Table 8 on page 26             |

| JS      | TXD4 (SMII)          | I                 | Table 9 on page 27             |

| J4      | VCCIO                |                   | Table 8 on page 26             |

| J5      | VCC                  |                   |                                |

| J9      | GND                  |                   |                                |

| J10     | GND                  |                   |                                |

| J11     | GND                  |                   |                                |

| J12     | GND                  |                   |                                |

| J16     | VCC                  |                   |                                |

| J17     | VCC                  |                   |                                |

| J18     | -                    | NC                |                                |

| 1. Refe | r to Table 1 on page | 11 for Signa      | Type definitions.              |

Table 2. Numeric Pad Assignments (Continued)

| Ball     | Symbol             | Type <sup>1</sup> | Reference for Full Description |

|----------|--------------------|-------------------|--------------------------------|

| J19      | -                  | NC                |                                |

| J20      | -                  | NC                |                                |

| K1       | FRCLNK             | I-PD              | Table 7 on page 25             |

| K2       | MODE_1             | I                 | Table 7 on page 25             |

| K3       | MCLK               | I                 | Table 7 on page 25             |

| K4       | GND                |                   |                                |

| K5       | VCC                |                   |                                |

| K9       | GND                |                   |                                |

| K10      | GND                |                   |                                |

| K11      | GND                |                   |                                |

| K12      | GND                |                   |                                |

| K16      | VCC                |                   |                                |

| K17      | GND                |                   |                                |

| K18      | RESET              | I                 | Table 7 on page 25             |

| K19      | BP4B5B             | I-PD              | Table 7 on page 25             |

| K20      | SCRMBP             | I-PD              | Table 7 on page 25             |

|          | TXD4 (RMII)        | 1                 | Table 8 on page 26             |

| L1       | SYNC (SMII)        | I                 | Table 9 on page 27             |

| L2       | MODE_2             | Ext-PD            | Table 7 on page 25             |

| L3       | FRC34              | I-PD              | Table 7 on page 25             |

| L4       | VCCIO              |                   |                                |

| L5       | VCC                |                   |                                |

| L9       | GND                |                   |                                |

| L10      | GND                |                   |                                |

| L11      | GND                |                   |                                |

| L12      | GND                |                   |                                |

| L16      | VCC                |                   |                                |

| L17      | VCCIO              |                   |                                |

| 140      | RXER0 (RMII)       | 0                 | Table 8 on page 26             |

| L18      | Not Used (SMII)    | NC                |                                |

| L19      | ID_1               | I-PD              | Table 7 on page 25             |

| L20      | ID_0               | I-PD              | Table 7 on page 25             |

| 1.44     | TXEN3 (RMII)       | 1                 | Table 8 on page 26             |

| M1       | Not Used (SMII)    | NC                |                                |

| 140      | TXD3_0 (RMII)      | I                 | Table 8 on page 26             |

| M2       | TXD3 (SMII)        |                   | Table 9 on page 27             |

| 1. Refer | to Table 1 on page | 11 for Signal     | Type definitions.              |

Table 2. Numeric Pad Assignments (Continued)

| Ball    | Symbol               | Type <sup>1</sup> | Reference for Full Description |  |  |

|---------|----------------------|-------------------|--------------------------------|--|--|

| M3      | TXD3_1 (RMII)        | I                 | Table 8 on page 26             |  |  |

| IVIO    | Not Used (SMII)      | NC                |                                |  |  |

| M4      | GND                  |                   |                                |  |  |

| M5      | VCC                  |                   |                                |  |  |

| M9      | GND                  |                   |                                |  |  |

| M10     | GND                  |                   |                                |  |  |

| M11     | GND                  |                   |                                |  |  |

| M12     | GND                  |                   |                                |  |  |

| M16     | VCC                  |                   |                                |  |  |

| M17     | GND                  |                   |                                |  |  |

| M18     | RXER3                | 0                 | Table 8 on page 26             |  |  |

| M19     | RXER2                | 0                 | Table 8 on page 26             |  |  |

| M20     | RXER1                | 0                 | Table 8 on page 26             |  |  |

| NI4     | RXD3_0 (RMII)        | 0                 | Table 8 on page 26             |  |  |

| N1      | RXD3 (SMII)          | 0                 | Table 9 on page 27             |  |  |

| NO      | RXD3_1 (RMII)        | 0                 | Table 8 on page 26             |  |  |

| N2      | Not Used (SMII)      | NC                |                                |  |  |

| No      | CRSDV3 (RMII)        | 0                 | Table 8 on page 26             |  |  |

| N3      | Not Used (SMII)      | NC                |                                |  |  |

| N4      | VCCIO                |                   |                                |  |  |

| N5      | VCC                  |                   |                                |  |  |

| N16     | VCC                  |                   |                                |  |  |

| N17     | VCCIO                |                   |                                |  |  |

| NIAO    | RXER6 (RMII)         | 0                 | Table 8 on page 26             |  |  |

| N18     | Not Used (SMII)      | NC                |                                |  |  |

| NIIO    | RXER5 (RMII)         | 0                 | Table 8 on page 26             |  |  |

| N19     | Not Used (SMII)      | NC                |                                |  |  |

| NICO    | RXER4 (RMII)         | 0                 | Table 8 on page 26             |  |  |

| N20     | Not Used (SMII)      | NC                |                                |  |  |

| D4      | CRSDV2 (RMII)        | 0                 | Table 8 on page 26             |  |  |

| P1      | Not Used (SMII)      | NC                |                                |  |  |

| P2      | RXD2_1 (RMII)        | 0                 | Table 8 on page 26             |  |  |

|         | Not Used (SMII)      | NC                |                                |  |  |

| P3      | RXD2_0               | 0                 | Table 8 on page 26             |  |  |

|         | RXD2                 | 0                 | Table 8 on page 26             |  |  |

| P4      | GND                  |                   |                                |  |  |

| P5      | vcc                  |                   |                                |  |  |

| 1. Refe | r to Table 1 on page | 11 for Signa      | I Type definitions.            |  |  |

Table 2. Numeric Pad Assignments (Continued)

| Ball     | Symbol             | Type <sup>1</sup> | Reference for Full Description |

|----------|--------------------|-------------------|--------------------------------|

| P15      | -                  | NC                |                                |

| P16      | VCC                |                   |                                |

| P17      | GND                |                   |                                |

| P18      | LED3_C             | 0                 | Table 5 on page 23             |

| P19      | LED3_B             | 0                 | Table 5 on page 23             |

| P20      | RXER7              | 0                 | Table 8 on page 26             |

| R1       | TXD2_1 (RMII)      | I                 | Table 8 on page 26             |

| n i      | Not Used (SMII)    | NC                |                                |

| R2       | TXD2_0 (RMII)      | I                 | Table 8 on page 26             |

|          | TXD2 (SMII)        | I                 | Table 9 on page 27             |

| R3       | TXEN2 (RMII)       | I                 | Table 8 on page 26             |

| 110      | Not Used (SMII)    | NC                |                                |

| R4       | VCCIO              |                   | Table 8 on page 26             |

| R5       | -                  | NC                |                                |

| R6       | -                  | NC                |                                |

| R7       | -                  | NC                |                                |

| R15      | -                  | NC                |                                |

| R16      | -                  | NC                |                                |

| R17      | VCCIO              |                   |                                |

| R18      | LED2_C             | 0                 | Table 5 on page 23             |

| R19      | LED2_B             | 0                 | Table 5 on page 23             |

| R20      | LED2_A             | 0                 | Table 5 on page 23             |

| T1       | TXEN1 (RMII)       | I                 | Table 8 on page 26             |

|          | Not Used (SMII)    | NC                |                                |

| T2       | TXD1_0 (RMII)      | I                 | Table 8 on page 26             |

|          | TXD1 (SMII)        | I                 | Table 9 on page 27             |

| Т3       | TXD1_1 (RMII)      | I                 | Table 8 on page 26             |

|          | Not Used (SMII)    | NC                |                                |

| T4       | GND                |                   |                                |

| T5       | GND                |                   |                                |

| Т6       | VCC                |                   |                                |

| T7       | GND                |                   |                                |

| T8       | GND                |                   |                                |

| T9       | VCC                |                   |                                |

| T10      | GND                |                   |                                |

| T11      | GND                |                   |                                |

| T12      | GND                |                   |                                |

| 1. Refer | to Table 1 on page | 11 for Signa      | l Type definitions.            |

Table 2. Numeric Pad Assignments (Continued)

| Ball    | Symbol               | Type <sup>1</sup> | Reference for Full Description |

|---------|----------------------|-------------------|--------------------------------|

| T13     | VCC                  |                   |                                |

| T14     | GND                  |                   |                                |

| T15     | GND                  |                   |                                |

| T16     | VCC                  |                   |                                |

| T17     | GND                  |                   |                                |

| T18     | LED1_C               | 0                 | Table 5 on page 23             |

| T19     | LED1_B               | 0                 | Table 5 on page 23             |

| T20     | LED1_A               | 0                 | Table 5 on page 23             |

| 114     | RXD1_0 (RMII)        | 0                 | Table 8 on page 26             |

| U1      | RXD1 (SMII)          | 0                 | Table 9 on page 27             |

| 110     | RXD1_1 (RMII)        | 0                 | Table 8 on page 26             |

| U2      | Not Used (SMII)      | NC                |                                |

| 110     | CRSDV1 (RMII)        | 0                 | Table 8 on page 26             |

| U3      | Not Used (SMII)      | NC                |                                |

| U4      | -                    | NC                |                                |

| U5      | GND                  |                   |                                |

| U6      | VCCR                 | A_PWR             |                                |

| U7      | -                    | NC                |                                |

| U8      | GND                  |                   |                                |

| U9      | VCCR                 | A_PWR             |                                |

| U10     | VCC                  |                   |                                |

| U11     | GND                  |                   |                                |

| U12     | GND                  |                   |                                |

| U13     | VCCR                 | A_PWR             |                                |

| U14     | -                    | NC                |                                |

| U15     | GND                  |                   |                                |

| U16     | VCCR                 | A_PWR             |                                |

| U17     | -                    | NC                |                                |

| U18     | LED0_C               | 0                 | Table 5 on page 23             |

| U19     | LED0_B               | 0                 | Table 5 on page 23             |

| U20     | LED0_A               | 0                 | Table 5 on page 23             |

| V1      | CRSDV0 (RMII)        | 0                 | Table 8 on page 26             |

|         | Not Used (SMII)      | NC                |                                |

| 1/0     | RXD0_1 (RMII)        | 0                 | Table 8 on page 26             |

| V2      | Not Used (SMII)      | NC                |                                |

| V3      | RXD0_0 (RMII)        | 0                 | Table 8 on page 26             |

| vs      | RXD0 (SMII)          | 0                 | Table 9 on page 27             |

| 1. Refe | r to Table 1 on page | 11 for Signal     | Type definitions.              |

Table 2. Numeric Pad Assignments (Continued)

| Ball     | Symbol               | Type <sup>1</sup> | Reference for Full Description |

|----------|----------------------|-------------------|--------------------------------|

| V4       | -                    | NC                |                                |

| V5       | TPIP0                | MLT               | Table 3 on page 22             |

| V6       | TPIN0                | MLT               | Table 3 on page 22             |

| V7       | -                    | NC                |                                |

| V8       | TPIP1                | MLT               | Table 3 on page 22             |

| V9       | TPIN1                | MLT               | Table 3 on page 22             |

| V10      | GND                  |                   |                                |

| V11      | GND                  |                   |                                |

| V12      | TPIP2                | MLT               | Table 3 on page 22             |

| V13      | TPIN2                | MLT               | Table 3 on page 22             |

| V14      | -                    | NC                |                                |

| V15      | TPIP3                | MLT               | Table 3 on page 22             |

| V16      | TPIN3                | MLT               | Table 3 on page 22             |

| V17      | -                    | NC                |                                |

| V18      | -                    | NC                |                                |

| V19      | -                    | NC                |                                |

| V20      | -                    | NC                |                                |

| 10/4     | TXD0_1 (RMII)        | I                 | Table 8 on page 26             |

| W1       | Not Used (SMII)      | NC                |                                |

|          | TXD0_0 (RMII)        | I                 | Table 8 on page 26             |

| W2       | TXD0 (SMII)          | I                 | Table 9 on page 27             |

| W3       | TXEN0 (RMII)         | I                 | Table 8 on page 26             |

| VV3      | Not Used (SMII)      | NC                | -                              |

| W4       | -                    | NC                | -                              |

| W5       | -                    | NC                | -                              |

| W6       | -                    | NC                | -                              |

| W7       | -                    | NC                | -                              |

| W8       | -                    | NC                | -                              |

| W9       | -                    | NC                | -                              |

| W10      | VCC                  |                   | -                              |

| W11      | VCC                  |                   | -                              |

| W12      | -                    | NC                | -                              |

| W13      | -                    | NC                | -                              |

| W14      | -                    | NC                | -                              |

| W15      | -                    | NC                | -                              |

| W16      | -                    | NC                | -                              |

| W17      | -                    | NC                | -                              |

| 1. Refer | to Table 1 on page 1 | 11 for Signal     | Type definitions.              |

Table 2. Numeric Pad Assignments (Continued)

| Ball                                                     | Symbol     | Type <sup>1</sup> | Reference for Full Description |  |  |

|----------------------------------------------------------|------------|-------------------|--------------------------------|--|--|

| W18                                                      | -          | NC                | -                              |  |  |

| W19                                                      | -          | NC                | -                              |  |  |

| W20                                                      | -          | NC                | -                              |  |  |

| Y1                                                       | -          | NC                | -                              |  |  |

| Y2                                                       | -          | NC                | -                              |  |  |

| Y3                                                       | -          | NC                | -                              |  |  |

| Y4                                                       | -          | NC                |                                |  |  |

| Y5                                                       | TPOP0      | MLT               | Table 3 on page 22             |  |  |

| Y6                                                       | TPON0      | MLT               | Table 3 on page 22             |  |  |

| Y7                                                       | -          | NC                |                                |  |  |

| Y8                                                       | TPOP1      | MLT               | Table 3 on page 22             |  |  |

| Y9                                                       | TPON1      | MLT               | Table 3 on page 22             |  |  |

| Y10                                                      | RBIAS100_0 | I                 | Table 7 on page 25             |  |  |

| Y11                                                      | RBIAS10_0  | I                 | Table 7 on page 25             |  |  |

| Y12                                                      | TPOP2      | MLT               | Table 3 on page 22             |  |  |

| Y13                                                      | TPON2      | MLT               | Table 3 on page 22             |  |  |

| Y14                                                      | -          | NC                |                                |  |  |

| Y15                                                      | TPOP3      | MLT               | Table 3 on page 22             |  |  |

| Y16                                                      | TPON3      | MLT               | Table 3 on page 22             |  |  |

| Y17                                                      | -          | NC                | -                              |  |  |

| Y18                                                      | -          | NC                | -                              |  |  |

| Y19                                                      | -          | NC                | -                              |  |  |

| Y20                                                      | -          | NC                | -                              |  |  |

| Refer to Table 1 on page 11 for Signal Type definitions. |            |                   |                                |  |  |

**Table 3. Network Interface Signal Descriptions**

| Ball ID          | Signal Name                                                 | Type <sup>1</sup> | Signal Description                                                                                                        |  |  |

|------------------|-------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| Y5, Y6           | TPOP0, TPON0                                                |                   |                                                                                                                           |  |  |

| Y8, Y9           | TPOP1, TPON1                                                |                   |                                                                                                                           |  |  |

| Y12, Y13         | TPOP2, TPON2                                                | - MLT             | Transmit Differential Pair, Ports 0-7. These pins transmit the                                                            |  |  |

| Y15, Y16         | TPOP3, TPON3                                                |                   | serial bit-stream on an unshielded twisted pair (UTP) cable. The differential pair is a two-level signal in 10BASE-T mode |  |  |

| A16, A15         | TPOP4, TPON4                                                |                   | (Manchester) or a three-level signal in 100BASE-TX mode (MLT-                                                             |  |  |

| A13, A12         | TPOP5, TPON5                                                |                   | 3). These signals interface directly with an isolation transformer.                                                       |  |  |

| A9, A8           | TPOP6, TPON6                                                |                   |                                                                                                                           |  |  |

| A6, A5           | TPOP7, TPON7                                                |                   |                                                                                                                           |  |  |

| 1. Refer to Tabl | 1. Refer to Table 1 on page 11 for Signal Type Definitions. |                   |                                                                                                                           |  |  |

Table 3. Network Interface Signal Descriptions (Continued)

| Ball ID          | Signal Name                                                 | Type <sup>1</sup> | Signal Description                                                                                                        |  |

|------------------|-------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| V5, V6           | TPIP0, TPIN0                                                |                   |                                                                                                                           |  |

| V8, V9           | TPIP1, TPIN1                                                |                   |                                                                                                                           |  |

| V12, V13         | TPIP2, TPIN2                                                | MLT               | Receive Differential Pair, Ports 0-7. These pins receive the                                                              |  |

| V15, V16         | TPIP3, TPIN3                                                |                   | serial bit-stream on an unshielded twisted pair (UTP) cable. The differential pair is a two-level signal in 10BASE-T mode |  |

| C16, C15         | TPIP4, TPIN4                                                |                   | (Manchester) or a three-level signal in 100BASE-TX mode (MLT-                                                             |  |

| C13, C12         | TPIP5, TPIN5                                                |                   | 3). These signals interface directly with an isolation transformer.                                                       |  |

| C9, C8           | TPIP6, TPIN6                                                |                   |                                                                                                                           |  |

| C6, C5           | TPIP7, TPIN7                                                |                   |                                                                                                                           |  |

| 1. Refer to Tabl | 1. Refer to Table 1 on page 11 for Signal Type Definitions. |                   |                                                                                                                           |  |

### **Table 4. MDIO Signal Descriptions**

| Ball ID | Signal Name                                             | Type <sup>1</sup> | Signal Description                                                                                                                                                                                              |  |  |  |

|---------|---------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| C20     | MDIO                                                    | I/O               | <b>Management Data Input/Output.</b> The MDIO signal is a bi-directional data pin for the Management Data Interface. When this signal is not used, a pull-up resistor is required.                              |  |  |  |

| B19     | MDC                                                     | I                 | <b>Management Data Clock.</b> The MDC signal functions as a clock reference for the MDIO signal. MDC can operate at a maximum frequency of 3 MHz. When this signal is not used, a pull-up resistor is required. |  |  |  |

| 1. Refe | Refer to Table 1 on page 6 for Signal Type Definitions. |                   |                                                                                                                                                                                                                 |  |  |  |

#### **Table 5. LED Signal Descriptions**

| Ball ID | Signal Name                                                             | Type <sup>1</sup> | Signal Description                                                                                                               |  |  |

|---------|-------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| U20     | LED0_A                                                                  |                   |                                                                                                                                  |  |  |

| T20     | LED1_A                                                                  |                   |                                                                                                                                  |  |  |

| R20     | LED2_A                                                                  | 0                 |                                                                                                                                  |  |  |

| G19     | LED3_A                                                                  |                   | <b>Link/Activity LED, Ports 0-7.</b> With a good link the output is Low. The output blinks at a rate related to the utilization. |  |  |

| F19     | LED4_A                                                                  |                   |                                                                                                                                  |  |  |

| E19     | LED5_A                                                                  |                   |                                                                                                                                  |  |  |

| D19     | LED6_A                                                                  |                   |                                                                                                                                  |  |  |

| C19     | LED7_A                                                                  |                   |                                                                                                                                  |  |  |

| 1. 0 =  | 1. O = Output. Refer to Table 1 for additional Signal Type Definitions. |                   |                                                                                                                                  |  |  |

Table 5. LED Signal Descriptions (Continued)

| Ball ID  | Signal Name      | Type <sup>1</sup> | Signal Description                                                    |  |  |  |  |

|----------|------------------|-------------------|-----------------------------------------------------------------------|--|--|--|--|

| U19      | LED0_B           |                   |                                                                       |  |  |  |  |

| T19      | LED1_B           |                   |                                                                       |  |  |  |  |

| R19      | LED2_B           |                   |                                                                       |  |  |  |  |

| P19      | LED3_B           | 0                 | Speed LED, Ports 0-7. Indicates speed of operation. The output is Low |  |  |  |  |

| F18      | LED4_B           |                   | for 100 Mbps, and High for 10 Mbps.                                   |  |  |  |  |

| E18      | LED5_B           |                   |                                                                       |  |  |  |  |

| D18      | LED6_B           |                   |                                                                       |  |  |  |  |

| C18      | LED7_B           |                   |                                                                       |  |  |  |  |

| U18      | LED0_C           |                   |                                                                       |  |  |  |  |

| T18      | LED1_C           |                   |                                                                       |  |  |  |  |

| R18      | LED2_C           |                   |                                                                       |  |  |  |  |

| P18      | LED3_C           | 0                 | Collision LED, Ports 0-7. When in RMII or SMII modes of operation,    |  |  |  |  |

| G20      | LED4_C           | O                 | the output blinks Low with collisions stretch rate of 10 ms.          |  |  |  |  |

| F20      | LED5_C           |                   |                                                                       |  |  |  |  |

| E20      | LED6_C           |                   |                                                                       |  |  |  |  |

| D20      | LED7_C           |                   |                                                                       |  |  |  |  |

| 1. O = 0 | Output. Refer to | Table 1 for a     | dditional Signal Type Definitions.                                    |  |  |  |  |

### **Table 6. Power Supply Signal Descriptions**

| Ball ID                                                                                                                                                                                                                                                                   | Symbol | Туре    | Signal Description                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|------------------------------------------------------------------------------|

| D6, D9, D13, D16,<br>U6, U9, U13, U16                                                                                                                                                                                                                                     | VCCR   | Analog  | Receiver Power Supply. +3.3V supply for core analog circuits.                |

| E4, E17, G4, G17, J4, L4, L17, N4, N17, R4, R17                                                                                                                                                                                                                           | VCCI/O | Digital | I/O Power Supply. +3.3V supply for core digital circuits.                    |

| B10, B11, D10, E6, E9, E13, E16, G5, G16, H5, H16, J5, J16, J17, K5, K16, L5, L16, M5, M16, N5, N16, P5, P16, T6, T9, T13, T16, U10, W10, W11                                                                                                                             | VCC    | A/D     | Primary Power Supply. +3.3V supply for all circuits except Receiver and I/O. |