# **Concurrent Signal Processor**

# ADSP-21csp01

#### **FEATURES**

#### PERFORMANCE

20 ns Instruction Cycle Time from 25 MHz Crystal @ 5.0 V

50 MIPS Sustained Performance

24-Bit Address Bus with a Unified 16M Address Space

32 Flexible Data Registers Provide Local Variable Storage

64 Data Addressing Registers Support 16 Data Structures Background Registers Provide Single-Cycle Context

Multifunction Instructions Combine Memory Read or Write with Arithmetic Operation

Single-Cycle Linked-List Update

64-Word, Selective Instruction Cache Provides Three Bus Performance

Single-Cycle Arithmetic Execution

Two 40-Bit Accumulators

Powerdown Mode Featuring Low CMOS Standby Power Dissipation with Fast Recovery from

Powerdown Condition

Low Power Dissipation in Idle Mode

Low Three-Cycle Interrupt Latency

#### INTEGRATION

20K Bytes of On-Chip RAM, Configured as:

4K Words of On-Chip Program or Data RAM (24 Bits)

4K Words of On-Chip Data RAM (16 Bits)

**Five-Channel DMA Controller**

Dual Purpose Program Memory for Both Instruction and Data Storage

Independent ALU, Multiplier/Accumulator, & Barrel Shifter Computational Units

Two Independent Data Address Generators Provide:

Pre-Modify and Post-Modify Addressing

**Modification with a Constant**

Circular/Modulo Addressing

**Powerful Program Sequencer Provides:**

Zero Overhead Looping

**Conditional Instruction Execution**

Programmable 16-Bit Interval Timer with Prescaler

#### SYSTEM INTERFACE

16-Bit DMA Port for High Speed Access to On-Chip Memory

Four Memory Strobes & Separate I/O Memory Space Permits "Glueless" System Design

**Programmable Wait State Generation**

Acknowledge Pin Supports Asynchronous Memory Interface

Two Synchronous Serial Ports with Companding

Hardware, Four 8-Word FIFOs, Separate Receive and

Transmit Clocks, DMA, and TDM Multichannel Support

Automatic Booting of On-Chip Program Memory from Byte-Wide External Memory (e.g., EPROM) or through DMA Port

12 Programmable Flag Pins (6 Input and 6 Output)

Provide Flexible System Signaling

Four External Interrupts (Plus 12 Internal and Software Interrupts for a Total of 16)

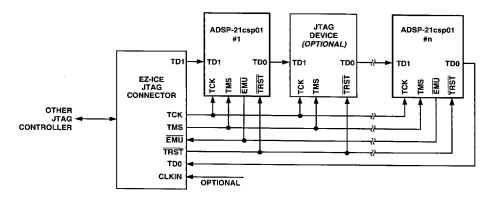

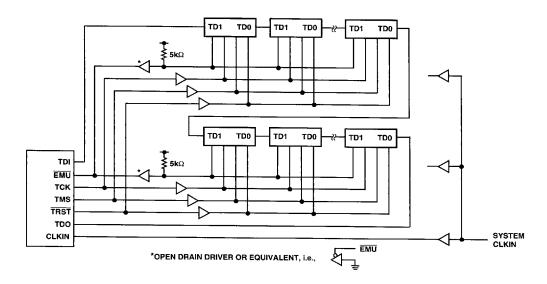

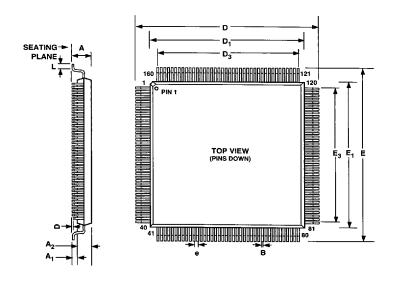

IEEE JTAG Standard 1149.1 Test and Emulation Port 160-Lead PQFP

#### GENERAL DESCRIPTION

The ADSP-21csp01 is a single chip DSP optimized for concurrent signal processing (CSP) and other high speed numeric processing applications. The ADSP-21csp01 combines high performance, high bandwidth, 16M address space, DMA port, and fast task switching support to provide efficient multisignal or multichannel processing. The ADSP-21csp01 processor is based on the architecture used for the ADSP-2100 Family. Although this architecture has been modified to improve the processor's performance and add new features, the ADSP-2100 Family code can be ported to the ADSP-21csp01.

The ADSP-21csp01 core architecture consists of three computational units, two data address generators, a program sequencer, and an instruction cache. The ADSP-21csp01 also has a programmable timer, extensive interrupt capabilities, two serial ports, a parallel DMA port, and on-chip memory. The on-chip memory is organized into a single, unified memory space containing four memory blocks with 2K locations in each block. Two blocks are  $2K \times 24$  bits and can be used to store instructions or data, while the others are  $2K \times 16$  bits and can be used to store data.

Fabricated in a high speed, low power CMOS process, the ADSP-21csp01 processor operates at 50 MHz with a 20 ns instruction cycle time. With its on-chip instruction cache, the processor can execute most instructions in a single cycle.

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1996

**=** 0816800 0050498 634 **=**

The ADSP-21csp01's flexible architecture and comprehensive instruction set supports a high degree of parallelism. In one cycle the ADSP-21csp01 can perform all of the following operations:

- perform a computation

- · perform one or two data moves

- · update one or two data address pointers

- · generate a program address

- · fetch an instruction

- decode an instruction

- · test an arithmetic condition

- · saturate the accumulator

These operations take place while the processor continues to complete the following tasks:

- · receive and transmit data through one or two serial ports

- receive or transmit data through the DMA port

- · decrement the timer

#### **Development Tools**

A complete Windows\*95 or WindowsNT based Integrated Design Environment (IDE) that includes software and hardware tools for system development supports the ADSP-21csp01. The ADSP-21csp01 Development Software includes C and assembly language tools that let you write code for the ADSP-21csp01 processor. The ANSI C compliant compiler generates ADSP-21csp01 assembly source code, while the C runtime library provides ANSI standard and custom DSP library routines. The ADSP-21csp01 assembler produces object code modules that the linker combines into an executable file. The simulator provides interactive instruction-level simulation and debugging with a Windows95 or WindowsNT interface. The IDE also generates PROM programmer compatible files and parallel DMA boot formatted files.

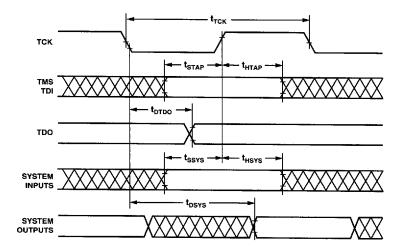

The EZ-ICE® in-circuit emulator allows full speed debugging of ADSP-21csp01 systems by providing a full range of emulation functions such as modification of memory and register values and execution breakpoints. The EZ-ICE emulator uses the IEEE 1149.1 JTAG test access port of the ADSP-21csp01 to

monitor and control the target board processor during emulation. The EZ-LAB® development system (that includes a MAFE and 32K external memory) is a complete DSP system that executes EPROM-based programs in a stand-alone configuration for prototyping, or plugs into the PC's ISA bus for program development. The IDE provides you with a single command window for the simulator, EZ-LAB, and EZ-ICE.

#### ARCHITECTURE OVERVIEW

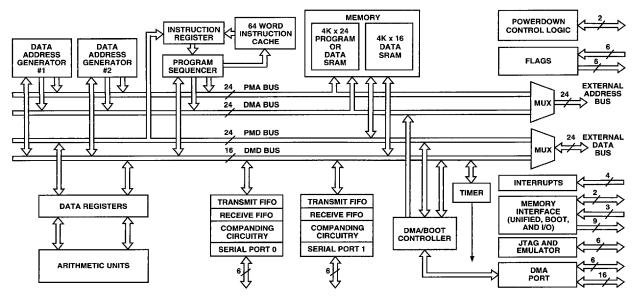

Figure 1 is a block diagram of the ADSP-21csp01 architecture. The processor contains three independent computational units: the ALU, the multiplier/accumulator with dual accumulators (MAC), and the shifter. The computational units process 16-bit data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic, logic, and bit manipulation operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add, and multiply/subtract operations. The shifter performs logical and arithmetic shifts, normalization, denormalization, and derive exponent operations. The shifter lets you efficiently implement numeric format control including multiword floating-point representations.

The computational units are fed by a set of 16 data registers or 16 background registers. For most instructions, you can use any data register as an input for any computation; this architectural feature provides a code structure that is flexible and easy to use. Multifunction and bit manipulation instructions, however, do have some register restrictions.

A powerful program sequencer and two dedicated data address generators (DAGs) ensure efficient use of these computational units. The sequencer supports most conditional jumps, subroutine calls, and returns in a single cycle. With internal loop counters and loop stacks, the ADSP-21csp01 supports zero overhead looping of code segments, which eliminates the need for jump instructions to maintain loops. You can also nest loops five levels deep.

Figure 1. ADSP-21csp01 Block Diagram

\*Windows is a registered trademark of Microsoft Corporation. EZ-ICE and EZ-LAB are registered trademarks of Analog Devices, Inc.

■ 0816800 0050499 570 ■

REV. 0

Two data address generators provide addresses for simultaneous dual operand fetches. The DAGs can be used for pre- and post-modify direct addressing. Each DAG maintains and updates four address pointers. When a pointer is used to access data (indirect addressing), it can be pre- or post-modified by the value of one of four modify registers or by a direct modify value. A length value also may be associated with each pointer in a buffer length register to implement automatic modulo addressing for circular buffers. You can place the starting locations for circular buffers at any memory location by loading the starting address into the base register. The 32 DAG registers are shadowed by a set of 32 background registers that enable fast context switching.

The ADSP-21csp01 includes a 64-word on-chip instruction cache that enables three bus operation for fetching an instruction and two data values. The cache is selective—only the instructions whose fetches conflict with data accesses are cached. The cache lets the processor execute core, looped operations, such as digital filter multiply/accumulates and FFT butterfly processing, without bus contention.

Efficient data transfer comes from the DSP's four internal buses:

- · Program Memory Address (PMA) Bus

- · Program Memory Data (PMD) Bus

- · Data Memory Address (DMA) Bus

- · Data Memory Data (DMD) Bus

The two address buses (PMA, DMA) share a single external address bus, allowing memory to be expanded off-chip. The two data buses (PMD, DMD) also share a single external data bus.

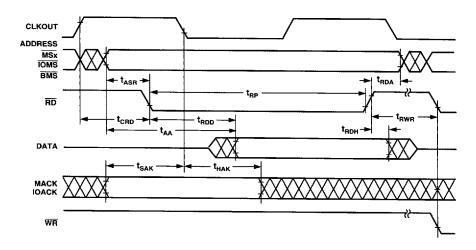

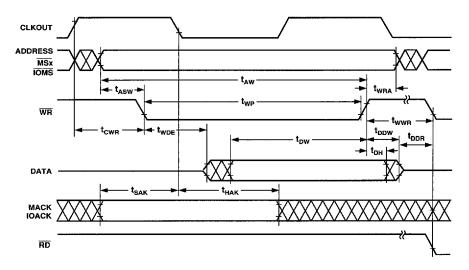

The memory interface supports slow memories with programmable wait state generation and a hardware acknowledge pin (MACK). External devices can gain control of the processor's buses with the bus request/grant signals  $(\overline{BR}, \overline{BG})$ . The memory interface also supports a separate memory-mapped peripheral space with its own select  $(\overline{IOMS})$  and acknowledge  $(\overline{IOACK})$  pins.

In addition to the address and data bus for external memory connection, the ADSP-21csp01 has a 16-bit DMA port for connection to external systems. The DMA port has 16 data/address pins and six control pins. The DMA port provides the host system direct access to the DSP's on-chip and off-chip RAM. The ADSP-21csp01 also can be booted through the DMA port.

The ADSP-21csp01 responds to 16 interrupts including a master RESET signal. There can be up to four external interrupts and 12 internal interrupts generated by the timer, the serial ports, the DMA port, and powerdown circuitry.

The ADSP-21csp01 has a full set of background registers for all data and DAG registers (plus page registers) that provide a single-cycle context switch.

The ADSP-21csp01 also has two serial ports that provide a synchronous serial interface. The serial port receive and transmit channels can be synchronized separately to programmable internal or external serial clocks. The serial ports also support time division multiplexed channels. Each serial port has 8-word transmit and receive FIFOs to simplify data processing.

The ADSP-21csp01's DMA controller supports automatic data transfers to and from the serial ports and memory.

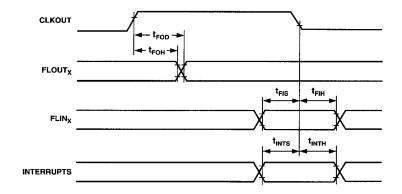

The ADSP-21csp01 has 12 flag pins: six input pins and six output pins. You can use the input flag pins to control software flow and you can use the output flag pins to control external hardware.

The ADSP-21csp01 has a programmable countdown interval timer that generates periodic interrupts. When the value of the count register reaches zero, the timer generates an interrupt, pulses or toggles the external timer expire pin (TIMEXP), and restarts the countdown.

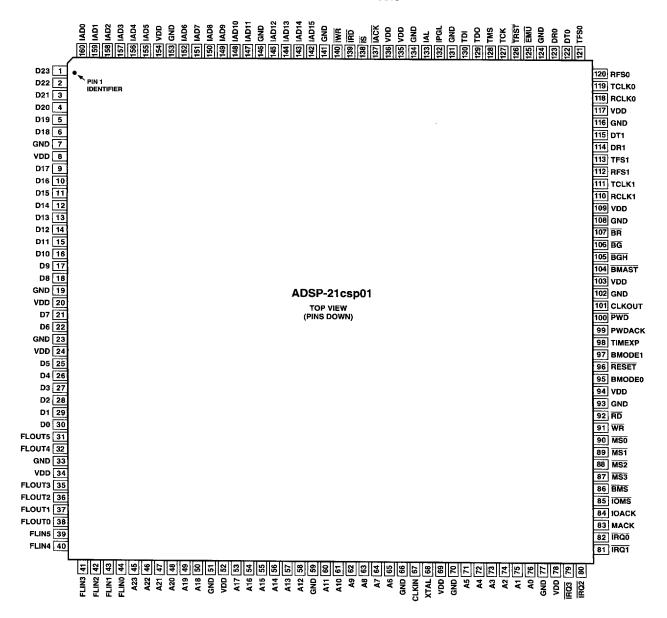

#### PIN DESCRIPTIONS

Table I shows the pin definitions for the ADSP-21csp01 processor. Pins are identified as input (I), output (O), bidirectional (I/O), or configurable (I or O).

Table I. ADSP-21csp01 Pin Descriptions

| Pin<br>Name(s)                | # of<br>Pins                           | Input/<br>Output | Function                                     |

|-------------------------------|----------------------------------------|------------------|----------------------------------------------|

| Address                       | 24                                     | 0                | Address Output Pins                          |

| Data                          | 24                                     | I/O              | Data I/O Pins. Input only when               |

|                               |                                        |                  | reading boot memory; unused                  |

|                               |                                        |                  | data lines may be left floating.             |

| $\overline{\mathrm{RD}}$      | 1                                      | 0                | External Memory Read Enable                  |

|                               |                                        |                  | Pin                                          |

| $\overline{WR}$               | 1                                      | 0                | External Memory Write Enable                 |

|                               |                                        | _                | Pin                                          |

| $\overline{\text{MS}}_{3-0}$  | 4                                      | 0                | Memory Select Pins                           |

| IOMS                          | 1                                      | 0                | I/O Select Pin                               |

| BMS                           | 1                                      | 0                | Boot Memory Select Pin                       |

| IOACK                         | 1                                      | I                | I/O Acknowledge Pin                          |

| MACK                          | 1                                      | I                | Memory Acknowledge Pin                       |

| BR                            | 1                                      | I or O           | External Bus Request Input Pin.              |

|                               |                                        |                  | Input for Bus Master Mode.                   |

| $\overline{\mathrm{BG}}$      | ,                                      | O T              | Output for Bus Slave Mode.                   |

| ВG                            | 1                                      | O or I           | External Bus Grant Output Pin.               |

|                               |                                        |                  | Output for Bus Master Mode.                  |

| $\overline{	ext{BGH}}$        | 1                                      | О                | Input for Bus Slave Mode.                    |

|                               | $\begin{vmatrix} 1 \\ 2 \end{vmatrix}$ | I                | External Bus Hang Pin Boot Mode Control Pins |

| $\frac{BMODE_{1-0}}{BMAST}$   | 1                                      | Ī                | Bus Master/Bus Slave Control                 |

| DMASI                         | 1                                      | 1                | Pin                                          |

| XTAL                          | 1                                      | I                | 1/2X External Quartz Crystal                 |

| ATTAL                         | 1                                      | 1                | Input Pin                                    |

| CLKIN                         | 1                                      | I                | 1/2X External Clock or Quartz                |

| CLICIT                        | 1                                      | ^                | Crystal Input Pin                            |

| CLKOUT                        | 1                                      | 0                | 1X Processor Clock Output Pin                |

|                               |                                        | _                |                                              |

| RESET                         | 1                                      | I                | Processor Reset Input Pin                    |

| $\overline{\text{IRQ}}_{3-0}$ | 4                                      | I                | External Interrupt Pins                      |

| $\overline{	ext{PWD}}$        | 1                                      | I                | Powerdown Pin puts Device in                 |

| DIVID A OU                    |                                        |                  | Powerdown Mode.                              |

| PWDACK                        | 1                                      | О                | Powerdown Acknowledge Pin                    |

| DT0                           | 1                                      | 0                | Data Transmit SPORT0 Pin                     |

| DR0                           | 1                                      | I                | Data Receive SPORT0 Pin                      |

| TFS0                          | 1                                      | I or O           | Transmit Frame Sync SPORT0 Pin               |

| RFS0                          | 1                                      | I or O           | Receive Frame Sync SPORT0                    |

|                               | -                                      |                  | Pin                                          |

| TCLK0                         | 1                                      | I or O           | Transmit Clock SPORT0 Pin                    |

|                               | 1                                      |                  |                                              |

Table I. ADSP-21csp01 Pin Descriptions (continued)

| Pin<br>Name(s)                                        | # of<br>Pins                           | Input/<br>Output                  | Function                                                                                                                                              |  |  |

|-------------------------------------------------------|----------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RCLK0                                                 | 1                                      | I or O                            | Receive Clock SPORT0 Pin                                                                                                                              |  |  |

| DT1<br>DR1<br>TFS1                                    | 1<br>1<br>1                            | O<br>I<br>I or O                  | Data Transmit SPORT1 Pin Data Receive SPORT1 Pin Transmit Frame Sync SPORT1 Pin                                                                       |  |  |

| RFS1<br>TCLK1<br>RCLK1                                | 1 1 1                                  | I or O I or O I or O              | Receive Frame Sync SPORT1 Pin Transmit Clock SPORT1 Pin Receive Clock SPORT1 Pin Flag Input Pins                                                      |  |  |

| FLIN <sub>5-0</sub><br>FLOUT <sub>5-0</sub><br>TIMEXP | 6<br>6<br>1                            | I<br>O<br>O                       | Flag Input Pins Flag Output Pins Timer Expired Pin                                                                                                    |  |  |

| IAD <sub>15-0</sub> IWR IRD IS IACK IAL IPGL          | 16<br>1<br>1<br>1<br>1<br>1            | I/O<br>I<br>I<br>I<br>O<br>I<br>I | IDMA Address and Data Pins IDMA Write Enable Pin IDMA Read Enable Pin IDMA Select Pin IDMA Acknowledge Pin IDMA Address Latch Pin IDMA Page Latch Pin |  |  |

| TDI TDO TMS TCK TRST EMU VDD GND                      | 1<br>1<br>1<br>1<br>1<br>1<br>14<br>19 | I<br>O<br>I<br>I<br>I<br>O        | JTAG Data Input Pin JTAG Data Output Pin JTAG Sync Pin JTAG Clock Pin JTAG Reset Pin Emulator Event Pin Power Supply Pins Ground Pins                 |  |  |

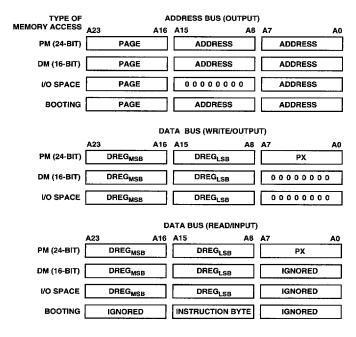

#### **MEMORY MAP & MEMORY INTERFACE**

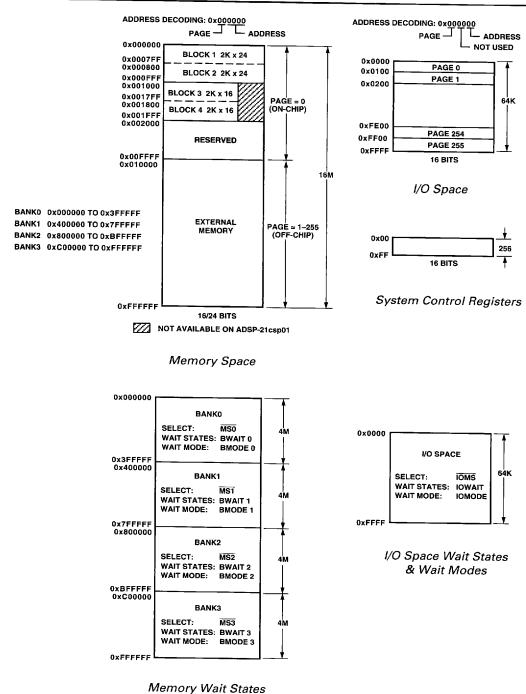

Figure 2 shows the ADSP-21csp01 memory map. The 8K words of on-chip RAM are divided into four separately bussed blocks. Block 1 and Block 2 are  $2K \times 24$  bits each and can be used to store instructions or data. Block 3 and Block 4 are  $2K \times 16$  bits each and are used only to store data.

The ADSP-21csp01 has 24 address lines that can address up to 16 million memory locations. The ADSP-21csp01 has a unified memory space; you can store 16-bit data at any valid memory location.

You can treat all 16M memory locations of the ADSP-21csp01 address range as a single memory space. Four memory select pins  $(\overline{MS}_{3-0})$  let you divide the memory into four separate banks. These pins may also eliminate the need for external memory address decoding circuitry. Separating the memory selects can lower the overall system power when tying the  $\overline{MS}_{3-0}$  pins to the chip selects on static RAMs. The processor uses the 2 MSBs of the address to generate the four memory strobes,  $\overline{MS}_{3-0}$ .

$\overline{\text{MS}}_{3-0}$  are not active when  $\overline{\text{IOMS}}$  or  $\overline{\text{BMS}}$  is active.

From a programmer's perspective, the ADSP-21csp01 has 16M words of linear instruction, paged data, and I/O space. The instruction space is considered to be linear because the user can jump or call to any address in the memory space without setting up a page register.

The ADSP-21csp01 provides three-bus bandwidth by supporting the following combinations of instruction and operand fetches:

- an instruction fetch from cache and two operand fetches from any two on-chip memory blocks

- an instruction fetch from cache, one operand fetch from onchip memory, and one operand fetch from off-chip memory.

Each memory block supports one access per cycle. Dual data accesses to 16-bit memory can be supported by using Block 3 and Block 4. When accessing Block 1 or Block 2 using the DMD bus, the upper 16 bits are transferred while the lower eight bits are stored in the PX register.

#### Memory Pages For Data Accesses

The memory space for data accesses is divided into 256 64K word pages. The internal memory is always in Page 0 which has 8K memory words available. There are four page registers used for memory addressing during data accesses. The 8 MSBs of the 24-bit data memory address bus is driven by one of the four page registers (DMPG1, DMPG2, DMAPAGE, and SPORTPAGE) and the 16 LSBs are driven from the instruction, DAG, or DMA controller. Page register selection is implicit in the operation type, as shown by the following sentences:

- Immediate address instructions and DAG1 instructions use the DMPG1 register.

- · DAG2 instructions use the DMPG2 register.

- DMA controller accesses use the system control register (DMAPAGE 0) for DMA transfers and the serial port page register (SPORTPAGE) for serial port transfers.

Typically, all the page registers are loaded with the same page number; however, if you load the registers with different page numbers, you can increase the flexibility of the memory. For example:

- The DMA space could be kept separate from the application data space.

- High speed copies from one page to another can be accomplished by exploiting the separate DMPG1 and DMPG2 registers attached to the two DAGs.

#### I/O Space

The I/O space is 256 pages of 256 locations and is externally accessed with special port I/O instructions. The IOPG register is used to form the eight MSBs (A23–A16) of the page address. The location is specified by the eight LSBs (A7–A0). During I/O operations the IOMS pin is asserted.

#### **System Control Register Space**

The system control register space is 256 linear locations that contain the system control registers. The DSP has specific instructions to access this space and to separate these registers from standard memory space. This feature simplifies the memory map, all standard memory becomes available for data.

Figure 2. ADSP-21csp01 Memory Map

& Wait Modes

#### **DIRECT MEMORY ACCESS**

#### **DMA** Controller

The DMA controller transfers 16-bit and 24-bit words between ADSP-21csp01 peripherals or host CPU and the ADSP-21csp01's memory (internal or external). Registers in the DMA controller let you specify the source and destination in memory for DMA transfers from the serial ports and DMA port. Once the DMA is initialized, the DMA controller can automatically increment the address and begin the next transfer. The DMA controller supports booting during powerup.

The following DMA channels can be active simultaneously:

- Bidirectional DMA Port

- Serial Port 0 Transmit

- \_ Serial Port 0 Receive

- Serial Port 1 Transmit

- \_ Serial Port 1 Receive

For each 16-bit or 24-bit word transferred, there is only one processor cycle of overhead.

#### **Serial Ports**

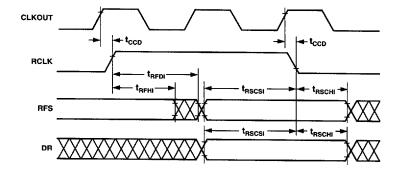

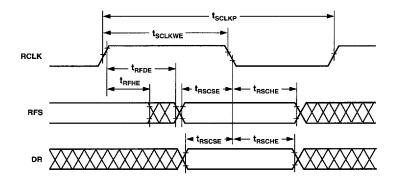

The ADSP-21csp01 processor includes two synchronous serial ports (SPORT0 and SPORT1) for peripheral and interprocessor communication.

The serial ports provide a complete synchronous serial interface with optional companding in hardware. Serial data can be automatically buffered in memory using the DMA controller. A wide variety of framed or frameless data transmit and receive modes of operation are available. Each SPORT can generate an internal or accept an external programmable transmit or receive serial clock. SPORTs can also generate internal or accept external frame synchronization signals.

Each serial port has a 6-pin interface consisting of the following signals:

| Pin Name     | Function                                     |

|--------------|----------------------------------------------|

| DT0 (or 1)   | Data Transmit SPORT0 (or 1)                  |

| DR0 (or 1)   | Data Receive SPORT0 (or 1)                   |

| RFS0 (or 1)  | Receive Frame Synchronization SPORT0 (or 1)  |

| TFS0 (or 1)  | Transmit Frame Synchronization SPORT0 (or 1) |

| TCLK0 (or 1) | Transmit Clock SPORT0 (or 1)                 |

| RCLK0 (or 1) | Receive Clock SPORT0 (or 1)                  |

Here is a brief list of the ADSP-21csp01 SPORT features:

- **Bidirectional**—each SPORT has a separate, double-buffered transmit and receive function.

- Flexible Clocking—each SPORT can use an external transmit or receive serial clock or generate its own clock internally.

- Flexible Framing—each SPORT section (receive and transmit) can operate with or without frame synchronization signals for each data word; with internally-generated or externally-generated frame signals; with active high or active low frame signals; with either of two pulse widths and frame signal timing.

- **Different Word Lengths**—each SPORT supports serial data word lengths from 3 to 16 bits.

- Companding in Hardware—each SPORT provides optional A-law and μ-law companding according to CCITT recommendation G.711.

- Separate Transmit and Receive Companding Controllets companding control be independent for the receiver and the transmitter.

- Flexible Interrupt Scheme—receive and transmit functions can generate unique interrupts upon completion of a data word transfer.

- Autobuffering with Single-Cycle Overhead—each SPORT

can automatically receive or transmit the contents of an entire

data buffer with only one overhead cycle per data word; an

interrupt is generated after the transfer of the entire buffer is

completed.

- Separate Transmit and Receive Clocks—includes separate divide registers for the transmit and receive clocks and associated counters and temporary registers, and separate I/O control for the clock pins.

- Transmit Empty Status—serial port status bit to signify

that transmission through the shift register is complete. This

is in addition to the status that shows the transmit buffer is

empty.

- Dual Multichannel Modes—multichannel capability is available on both SPORTs.

- Multichannel Block Sizes of 1-32—the ADSP-21csp01 has fully programmable block sizes for TDM systems.

- Multichannel Companding Register—SPORTs compand on a per channel basis in multichannel mode.

- FIFO for Transmit and Receive Buffers—each transmit and receive register (TX0, RX0, TX1, RX1) has an eight location trickle through FIFO. This feature makes the hardware less sensitive to software timing. You can program the various TX and RX interrupts to occur at any location in the FIFO. An internal register in the companding section makes the FIFO effectively nine locations long.

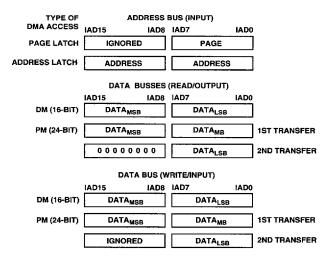

#### **DMA Port**

The DMA port provides an efficient means of communication between a host system and the ADSP-21csp01. The host uses the port to access on-chip and off-chip memory with only one DSP cycle per word overhead.

The DMA port has a 16-bit multiplexed address and data bus and supports 24-bit program memory. The DMA port is completely asynchronous and can be written to while the ADSP-21csp01 is operating at full speed.

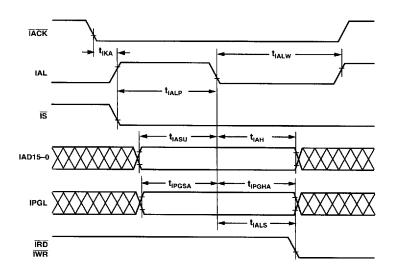

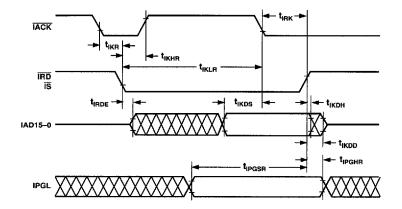

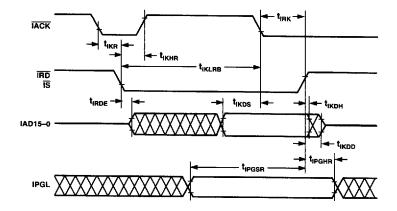

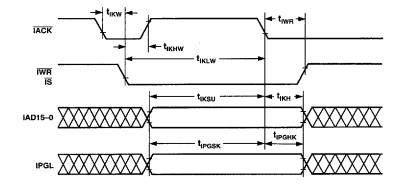

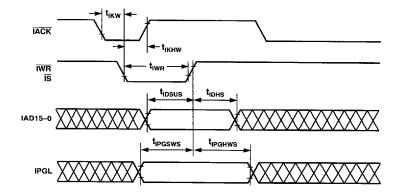

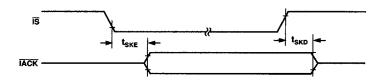

The host accesses data through the DMA port in two phases. The first phase is DMA address and page latching. When the ADSP-21csp01 asserts an acknowledge, an external device can drive an 8-bit page designation and a 16-bit address onto the bus sequentially. The upper eight bits of the address specifies the page. Page 0, which is the default, specifies on-chip memory; pages 0x01-0xFF specify off-chip memory. When the host asserts the IPGL signal, the falling edge of the IAL signal latches the page into the IDMAPAGE register. The falling edge of the IAL signal latches the 16 bits of the address into the IDMAADR register when the host deasserts IPGL. The  $\overline{\text{IS}}$  signal must be asserted to select the DSP during these cycles.

The second phase is the data transfer. Once the address is stored, the host can read data from or write data to the ADSP-21csp01's memory space. While the select line  $(\overline{IS})$  is asserted, the host signals the ADSP-21csp01, with the appropriate read or write line  $(\overline{IRD})$  and  $\overline{IWR}$  respectively), that it requires a particular transaction. In either case, there is a one to three processor cycle delay for synchronization. The memory access consumes one additional processor cycle. The DMA address is automatically incremented by one address for each transfer.

Through the IDMAADR and IDMAPAGE registers, the DSP can specify the starting address and the 8-bit page of the DMA operation. Also, the IDMAADR and IDMAPAGE registers, in conjunction with the NEXTADR and NEXTPAGE registers, can be set in software for automatic roll-over to the next DMA transfer.

You can read large amounts of data more efficiently through the DMA read block mode. In this mode, internal prefetching reduces the synchronization delay from three processor cycles to one cycle when the host reads data from the ADSP-21csp01. When you use the DMA read block mode, all transfers in the block must be read; you cannot mix reads and writes.

The DMA port also supports 24-bit data transfers. The transfers require two DMA port data cycles. In the first cycle, IPGL is asserted with the appropriate read or write line (IRD or IWR) and the 16 MSBs of data are transferred on IAD15–0. In the second cycle IPGL is deasserted and the eight LSBs of the data are transferred on IAD7–0. Only one processor overhead cycle is required for 24-bit data transfers.

#### Booting

On powerup, the ADSP-21csp01 can be booted from an 8-bit wide EPROM or from a host through the DMA port. Booting can also be initiated in software after reset. The destination for boot instructions can be internal or external memory.

#### **Boot Mode Control**

There are two pins that control booting, BMODE1 and BMODE0. These pins determine if the ADSP-21csp01 boots under software control and on RESET and they determine the source for the boot. Table II summarizes the boot configurations.

Table II. Boot Mode Control

| BMODE1 | BMODE0 | RESET Function                            | Boot Source                                                        |

|--------|--------|-------------------------------------------|--------------------------------------------------------------------|

| 0      | 0      | Boot on RESET                             | From Boot Memory<br>(Byte-Wide EPROM)                              |

| 0      | 1      | Boot on RESET                             | From DMA Port                                                      |

| 1      | 0      | Processor Runs<br>from External<br>Memory | From Boot Memory<br>(Byte-Wide EPROM)<br>Under Software<br>Control |

| 1      | 1      | Reserved                                  |                                                                    |

When BMODE1 is high, the software may still force a boot after RESET.

#### **DMA Port Booting**

The ADSP-21csp01 can also boot programs through its DMA port. If BMODE0 = high and BMODE1 = low, the ADSP-21csp01 boots from the DMA port. This DMA feature can load as much on-chip memory as desired.

On  $\overline{\text{RESET}}$ , the host CPU writes to the DMA port as it does in any other DMA transfer. However, all bytes in the boot stream are considered to be data, so the port address and page select signals should not be active during booting. Program execution is held until code is written to memory location 0x0000 on any page.

#### **Byte-Wide EPROM Booting**

You can boot up to 256 pages (64K bytes each) from EPROM. When booting from an EPROM, the DSP uses the external memory bus to access the EPROM. The  $\overline{RD}$  strobe and the  $\overline{BMS}$  pins are used. The byte-wide EPROM is mapped onto bits 15–8 of the 24-bit data bus.

On RESET, booting starts at address 0x000000 and continues through the EPROM until an end-of-stream marker is read. After RESET, you can boot any boot page through software control by specifying the boot page number in the BOOTPAGE register. The upper eight address bits specify the boot page. Booting starts from address 0x0000 on each page.

The number of wait states for each EPROM access is specified by four bits in the System Control (SYSCNTL) register. On RESET, the default is 15 wait states.

#### PROGRAM SEQUENCING

The ADSP-21csp01 program sequencer supports most jumps, calls, and returns in a single cycle. Jumps and calls may be conditional and may be indirect through an index register using the IJPG page register. JUMPs and CALLs within ±4K PC offset execute in a single cycle; long jumps and long calls (LJUMP and LCALL) require two instruction locations and an additional execution cycle.

You can use most branch instructions with or without the delayed-branch (dB) option. The delayed-branch instructions change the program flow after executing the two instructions that follow the branch instruction. Delayed-branch instructions do not require any extra cycles. The nondelayed-branch instructions change program flow immediately after the branch instruction, but you must insert two extra stall cycles in your code (for example, NOP instructions) for proper operation. (All long jumps and calls use nondelayed branching.)

The ADSP-21csp01 supports powerful zero-overhead looping. With a single setup instruction, your code can execute loops from one to 8192 instructions. These loops may be conditional based on computation status or loop count and you can nest loops up to five deep.

#### Interrupts

The interrupt controller lets the processor respond to the 16 possible interrupts, including RESET, with minimum overhead. The ADSP-21csp01 provides four external interrupt pins, IRQ0, IRQ1, IRQ2, and IRQ3. The ADSP-21csp01 also supports loop stack overflow interrupts and three user-defined software interrupts, as well as internal interrupts generated by the timer, the serial ports, the DMA port, and powerdown circuitry. The interrupts are prioritized internally and individually maskable (except RESET and powerdown). You can also set bits in the interrupt control register to nest interrupts or mask interrupts globally. The external interrupt pins can be programmed to be either edge- or level-sensitive; level-sensitive is the powerup default. Table III shows the priorities and vector addresses of the interrupts.

Table III. Interrupt Vector Address & Interrupt Priority

| Source of Interrupt          | Interrupt<br>Vector Address | IRPTL Bit       |

|------------------------------|-----------------------------|-----------------|

| RESET                        | 0x0000                      | 0 (nonmaskable) |

| (Powerup with PUCR = 1)      | (highest priority)          |                 |

| Powerdown                    | 0x0004                      | 1 (nonmaskable) |

| Stack Status                 | 0x0008                      | 2               |

| ĪRQ3                         | 0x000C                      | 3               |

| Timer                        | 0x0010                      | 4               |

| User Interrupt 2             | 0x0014                      | 5               |

| IRQ2                         | 0x0018                      | 6               |

| DMA/Host Interface Port Read | 0x001C                      | 7               |

| ĪRQ1                         | 0x0020                      | 8               |

| SPORT0 Transmit              | 0x0024                      | 9               |

| SPORT0 Receive               | 0x0028                      | 10              |

| SPORT1 Transmit              | 0x002C                      | 11              |

| SPORT1 Receive               | 0x0030                      | 12              |

| ĪRQ0                         | 0x0034                      | 13              |

| User Interrupt 1             | 0x0038                      | 14              |

| User Interrupt 0             | 0x003C                      | 15              |

|                              | (lowest priority)           |                 |

Each interrupt has four vector locations for the interrupt service routine. RESET is the first interrupt and starts at address 0x0000.

The IRPTL register can be used to force or clear individual interrupts (except  $\overline{RESET}$  and Powerdown). When a bit in the IRPTL register is set through software control, the interrupt will be serviced.

Interrupts, except RESET and Powerdown, can be masked or unmasked with the 16-bit IMASK register. Individual interrupt requests are logically ANDed with the bits in IMASK; the highest priority interrupt is then selected.

You can also access pending interrupt status. When read, a bit set in IRPTL designates a pending interrupt. There is a one-for-one correspondence between IRPTL bits and IMASK bits.

The interrupt control and mode extension register (ICNTL) is used to set the edge- or level-sensitivity of the external interrupt pins. ICNTL also includes the following bits:

- Nesting Mode Enable—This bit enables the nested interrupt mode of the ADSP-21csp01; a higher priority service request will interrupt the currently serviced interrupt routine. When this mode is disabled, pending interrupts are not serviced until the processor finishes servicing the current interrupt.

- **Global Interrupt Enable**—This bit is a global interrupt enable and disable bit. The global interrupt enable bit can be set and cleared through software control.

#### **Instruction Cache**

The instruction cache is a two-way set-associative cache that is 64 locations deep. The operation of the cache is completely transparent to the user. The purpose of the cache is to eliminate bus contention that may occur on the internal PM data bus, the external bus, or memory blocks because of a data access that attempts to use the same resource as the instruction fetch. The ADSP-21csp01 only caches instructions that conflict with memory accesses (selective caching).

The instruction cache has controls to allow for flushing (invalidating) the entire cache under program control. You can also freeze the contents of the instruction cache. When the cache is frozen, no new instructions can be written into the cache, but the processor continues to execute instructions saved in the cache.

The instruction cache is a two-way set-associative tagged cache (with 32 sets). Each entry consists of an address tag and an instruction word. A set consists of two entries and a least recently used (LRU) bit. The LRU bit is used to determine which entry in the set has been used or updated least recently. At processor reset, the cache is cleared.

#### Stacks

The ADSP-21csp01 PC and LOOP stacks are each 24 bits wide. Two stack registers, STACKA and STACKP, are used to accommodate the width of these stacks. When you use POP PC and POP LOOP commands, 24-bit values are written to these

registers: STACKA holds the 16 LSBs and STACKP holds the 8 MSBs. When you use PUSH PC and PUSH LOOP commands, 24-bit values are read from these registers: STACKA yields the 16 LSBs and STACKP yields the 8 MSBs.

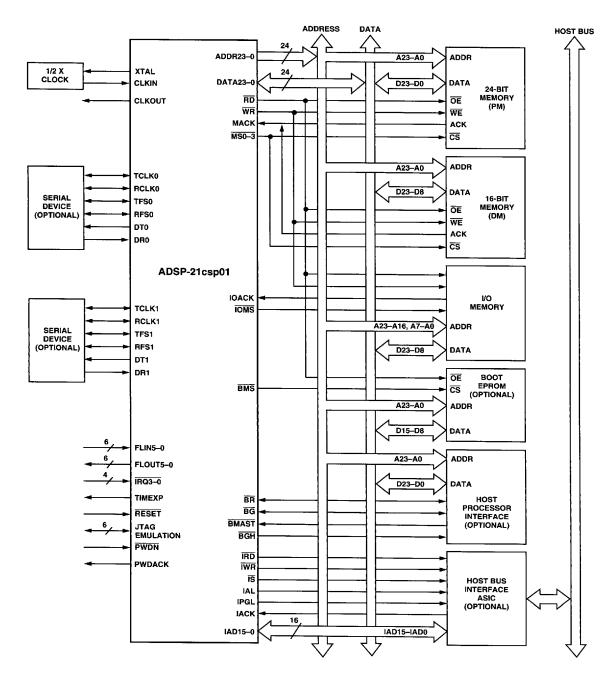

Figure 3. ADSP-21csp01 Basic System Configuration

#### Stack Depth

One additional stack location is included in the PC and status (STS) stacks for use with the emulator interrupt. In summary, the stack depths available to the user are:

- $_{-}$  PC = 31

- \_ STS = 15

- $_{-}$  LOOP = 5

- \_ CNTR = 5

#### **SYSTEM INTERFACE**

Figure 3 shows a basic system configuration that includes the ADSP-21csp01, two serial devices, external program and data memory, an external boot EPROM, a host processor interface, and host bus interface.

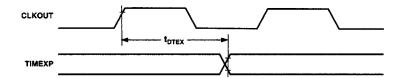

#### **Clock Signals**

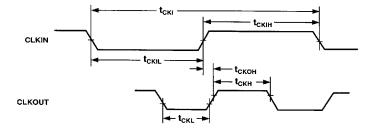

The ADSP-21csp01 uses an input clock with a frequency equal to half the instruction rate; a 25 MHz input clock yields a 20 ns processor cycle (which is equivalent to 50 MHz). Normally, instructions are executed in a single processor cycle. All device timing is relative to the internal instruction clock rate indicated by the CLKOUT signal.

The CLKIN input cannot be halted, changed during operation, or operated below the specified frequency during normal operation. The only exception is while the processor is in the power-down state.

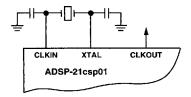

The ADSP-21csp01 can be clocked by a crystal or by a TTL-compatible clock signal.

If an external clock is used, it should be a TTL-compatible signal running at half the instruction rate. The signal is connected to the processor's CLKIN input. When an external clock is used, the XTAL input *must* be left unconnected.

Because the ADSP-21csp01 includes an on-chip oscillator circuit, an external crystal may be used. The crystal should be connected across the CLKIN and XTAL pins, with two capacitors connected as shown in Figure 4. Capacitor values depend on the crystal type and should be specified by the crystal manufacturer. A parallel-resonant, fundamental-frequency, microprocessor-grade crystal should be used.

Figure 4. External Crystal Connections

A clock output (CLKOUT) signal is generated by the processor and is equal to the processor's instruction rate. The clock output can be held low (disabled) through software control by setting the CLKODIS bit in the System Control Register.

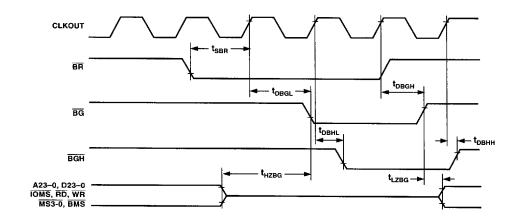

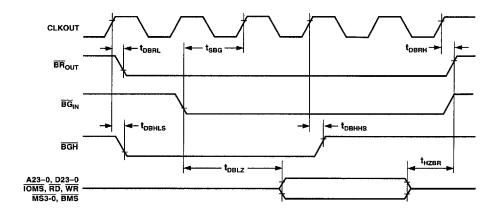

#### Bus Request, Bus Grant, and Bus Hang

The ADSP-21csp01 can be run in bus master or bus slave mode, depending on the state of the  $\overline{BMAST}$  pin. When this pin is driven low (normal in single processor systems), the processor is the bus master; when it is driven high, the processor becomes a bus slave. Bus master/slave mode determines the function of the bus request, bus grant, and bus hang pins  $(\overline{BR}, \overline{BG})$ , and  $\overline{BGH}$ ).

In bus master mode:

- BR is an INPUT that tells the ADSP-21csp01 that another device requests control of the external memory bus.

- $\overline{BG}$  is an OUTPUT whereby the ADSP-21csp01 grants control of the external memory bus to another device.

In bus slave mode:

- BR is an OUTPUT that tells other devices the ADSP-21csp01 requests control of the external memory bus.

- BG is an INPUT that grants the ADSP-21csp01 external memory bus control.

BGH (bus hang) lets other devices know that the ADSP-21csp01 wants to perform an external access, but it does not have control of the bus. Bus lock mode can give the ADSP-21csp01 exclusive access to the external bus. BGH is valid in both master and slave modes, but its function is affected by bus lock mode.

- In bus master mode, bus lock "locks out" bus granting to an external device. BG remains inactive after receiving BR, even if external memory accesses are not currently underway. If the bus has already been granted when bus lock is enabled, BG stays active until BR is removed.

- In bus slave mode, bus lock automatically generates a bus request. The ADSP-21csp01 takes control of the bus on  $\overline{BG}$  regardless of whether an external memory access is ongoing.  $\overline{BGH}$  will not go active unless an external access is actually attempted before  $\overline{BG}$  is returned.

#### Timer Expired

The ADSP-21csp01 has a timer expired (TIMEXP) output pin. When the timer is enabled, this pin pulses or toggles each time the timer expires. Bit 15 (EXPMODE bit) of the TSCALE register programs TIMEXP to pulse or toggle. Once the timer is enabled, TIMEXP is generated whether or not the timer interrupt is enabled or the interrupt is serviced. The TSCALE register is undefined after a reset. TIMEXP is low when the timer is disabled.

REV. 0

### **Terminating Unused Pins**

Table IV shows the recommendations for terminating unused pins.

Table IV. ADSP-21csp01 Pin Terminations

| Pin<br>Name(s)        | Unused<br>Connection | # of<br>Pins | Input/<br>Output | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|----------------------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address               | Float                | 24           | 0                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Data                  | Float                | 24           | I/O              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\overline{	ext{RD}}$ | Float                | 1            | o o              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WR                    | Float                | i            | ő                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\frac{MR}{MS3-0}$    | Float                | 4            | o l              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IOMS                  | Float                | 1            | o l              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BMS                   | Float                | 1            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IOACK                 | HIGH                 |              | O                | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MACK                  |                      | 1            | Ī                | Active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                       | HIGH                 | 1            | I                | Active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BR                    | HIGH                 | 1            | I                | Master Mode, Default at RESET, Inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <del></del>           | Float                |              | 0                | Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

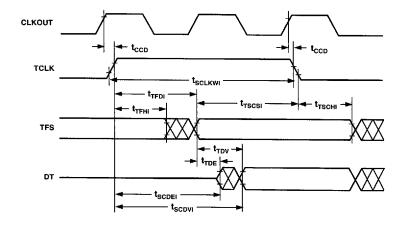

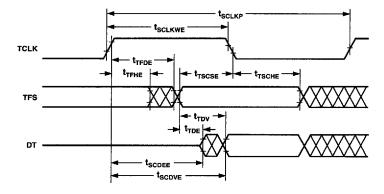

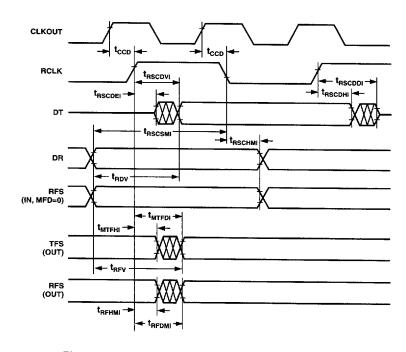

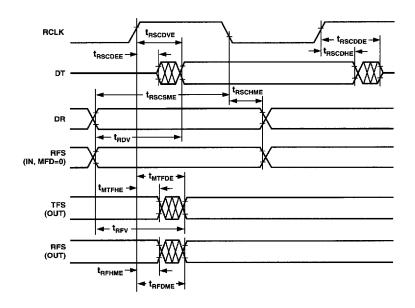

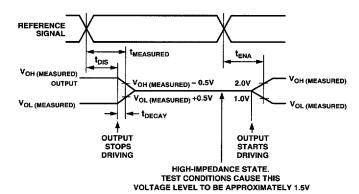

| BG                    | Float                | 1            | 0                | Master Mode, Default at RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |