# **NEC**

## **User's Manual**

# **OSD LSIs**

μPD6461 μPD6462 μPD6464Α μPD6465 μPD6466

Document No. S13197EJ1V0UMJ1 (1st Edition) Publication Date October 2000 N CP(K) [MEMO]

#### NOTES FOR CMOS DEVICES -

#### 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

MS-DOS, Windows, and Windows NT are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT and PC DOS are trademarks of International Business Machines Corporation.

- The information in this document is current as of May, 1998. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data

books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products

and/or types are available in every country. Please check with an NEC sales representative for

availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of

third parties by or arising from the use of NEC semiconductor products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of customer's equipment shall be done under the full

responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third

parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

- "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

#### **PREFACE**

Target users This user's manual is intended for users who understand the functions of the  $\mu$ PC6461,

$\mu$ PD6462,  $\mu$ PD6464A,  $\mu$ PD6465, and  $\mu$ PD6466 on-screen character display CMOS LSIs (OSD LSIs) and who will design and develop application systems for them.

**Purpose** The purpose of this user's manual is to help users understand the basic functions of OSD

LSIs. Hardware configurations that appear in this manual are illustrative examples only,

and there is no plan for their mass production.

**Configuration** This user's manual consists of the following chapters.

CHAPTER 1 OVERVIEW

CHAPTER 2 BASIC OPERATION

• CHAPTER 3 APPLICATION EXAMPLES

• CHAPTER 4 FAQ

CHAPTER 5 DEVELOPMENT TOOLS

How to read this manual Readers of this manual should have a general understanding of electrical and logic

circuits, microcontrollers, and video signal processing.

Legend Data significance : Higher digits on the left and lower digits on the right

Note : Footnote for item marked with Note in the text

**Caution** : Information requiring particular attention

**Remark** : Supplementary information

Numerical representation: Binary ...... xxxx or 0bxxxx

Decimal ..... ××××

Hexadecimal .... 0x×××

#### Related documents

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

Data sheets

μPD6461 (Document number: S12588E) μPD6462 (Document number: S12593E) μPD6464A, μPD6465 (Document number: S11043E) μPD6466 (Document number: S10991E)

User's manuals

OSD LSIs (This manual)

OSD LSI Character Pattern Editor for Windows™ (To be prepared)

Character Pattern Editor for On-Screen Display LSI<sup>Note</sup> (Document number: S10153E)

Note This manual is for MS-DOS™ (for PC-9801) and PC DOS™ (for IBM PC/AT™).

Information

ROM Code Ordering Method (Document number: C10302J)Note

Note This document number is that of Japanese version.

Caution The related documents listed above may be changed without notice. Be sure to use the latest documents for design and other purposes.

### CONTENTS

| CHAPTE | ER 1 OVERVIEW                                                     | 13 |  |  |  |  |

|--------|-------------------------------------------------------------------|----|--|--|--|--|

| 1.1    | List of OSD LSIs                                                  | 14 |  |  |  |  |

| 1.2    |                                                                   |    |  |  |  |  |

| 1.3    | •                                                                 |    |  |  |  |  |

| 1.4    | Block Diagrams                                                    | 24 |  |  |  |  |

| СНАРТЕ | ER 2 BASIC OPERATION                                              | 27 |  |  |  |  |

| 2.1    | OSD LSI Configuration                                             | 27 |  |  |  |  |

|        | 2.1.1 Dot clock oscillation circuit                               | 27 |  |  |  |  |

|        | 2.1.2 Timing generator                                            | 29 |  |  |  |  |

|        | 2.1.3 Horizontal control section                                  | 29 |  |  |  |  |

|        | 2.1.4 Vertical control section                                    | 30 |  |  |  |  |

|        | 2.1.5 Video RAM control section                                   | 30 |  |  |  |  |

|        | 2.1.6 Video RAM                                                   | 31 |  |  |  |  |

|        | 2.1.7 Character generator ROM                                     | 31 |  |  |  |  |

|        | 2.1.8 Output controller                                           | 31 |  |  |  |  |

| 2.2    | Basic Operation of a Video-System OSD LSI                         | 32 |  |  |  |  |

|        | 2.2.1 Quadruple/4fsc crystal oscillation circuit                  | 32 |  |  |  |  |

|        | 2.2.2 Synchronization separation circuit                          | 34 |  |  |  |  |

|        | 2.2.3 Video signal output section                                 | 39 |  |  |  |  |

| 2.3    | Basic Operation of an RGB-System OSD LSI                          | 41 |  |  |  |  |

|        | 2.3.1 Synchronization protection circuit                          | 41 |  |  |  |  |

|        | 2.3.2 R, G, B, and BLK outputs when RGB + Vc1 + Vc2 is selected   | 45 |  |  |  |  |

|        | 2.3.3 R, G, B, and BLK outputs when RGB + blanking corresponding  |    |  |  |  |  |

|        | to RGB (3BLK) is selected                                         | 47 |  |  |  |  |

| 2.4    | Characters                                                        | 49 |  |  |  |  |

|        | 2.4.1 Character display                                           | 49 |  |  |  |  |

|        | 2.4.2 Character patterns                                          | 50 |  |  |  |  |

| 2.5    | Commands                                                          | 50 |  |  |  |  |

|        | 2.5.1 Command format                                              | 50 |  |  |  |  |

|        | 2.5.2 Command list                                                | 51 |  |  |  |  |

| 2.6    | OSD LSI Power-ON Initialization                                   | 56 |  |  |  |  |

| CHAPTE | ER 3 APPLICATION EXAMPLES                                         | 57 |  |  |  |  |

| 3.1    | Video-System OSD LSI Application Examples                         | 57 |  |  |  |  |

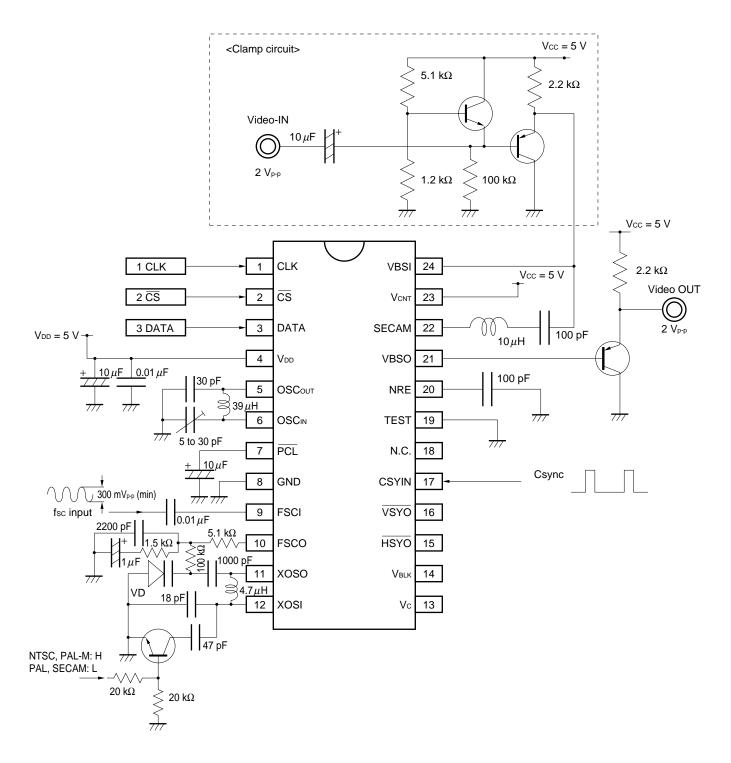

|        | 3.1.1 Sample μPD6464A or μPD6465 application circuits             | 57 |  |  |  |  |

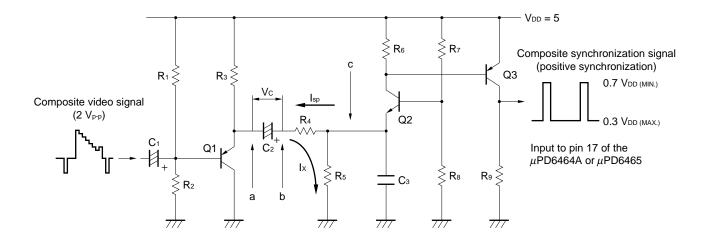

|        | 3.1.2 Composite synchronization signal (Csync) separation circuit | 60 |  |  |  |  |

|        | 3.1.3 Sample application for separate video signal input          | 63 |  |  |  |  |

|        | 3.1.4 Sample application for NTSC direct mode                     | 64 |  |  |  |  |

| 3.2    | RGB-   | System OSD LSI Application Examples                             | 66 |

|--------|--------|-----------------------------------------------------------------|----|

|        | 3.2.1  | Sample $\mu$ PD6461A or $\mu$ PD6462 application circuit        | 66 |

|        | 3.2.2  | Sample µPD6466 application circuit                              | 67 |

| 3.3    | Exter  | nal Clock Forced Input to LC Oscillation Circuit Section        | 68 |

| CHAPTE | R 4 F/ | 4Q                                                              | 69 |

| 4.1    | All O  | SD LSIs                                                         | 69 |

| 4.2    | Video  | o-System OSD LSIs ( $\mu$ PD6464A and $\mu$ PD6465)             | 73 |

|        |        | System OSD LSIs ( $\mu$ PD6461, $\mu$ PD6462, and $\mu$ PD6466) |    |

| CHAPTE | R 5 D  | EVELOPMENT TOOLS                                                | 79 |

| 5.1    | Over   | view of Development Tools                                       | 79 |

| 5.2    | Conc   | erning OSD LSI Mask ROM Ordering                                | 83 |

## LIST OF FIGURES (1/2)

| Figure No. | Title                                                                               | Page |  |  |  |  |

|------------|-------------------------------------------------------------------------------------|------|--|--|--|--|

| 1-1        | Sample Uses of OSD LSIs (RGB-System OSD LSI: Camcorder)                             | 13   |  |  |  |  |

| 1-2        | $\mu$ PD6464A or $\mu$ PD6465 Pin Configuration (Top View)                          | 16   |  |  |  |  |

| 1-3        | $\mu$ PD6461 or $\mu$ PD6462 Pin Configuration (Top View)                           | 18   |  |  |  |  |

| 1-4        | $\mu$ PD6466 Pin Configuration (Top View)                                           | 21   |  |  |  |  |

| 1-5        | $\mu$ PD6464A and $\mu$ PD6465 Block Diagram                                        |      |  |  |  |  |

| 1-6        | $\mu$ PD6461 and $\mu$ PD6462 Block Diagram                                         | 25   |  |  |  |  |

| 1-7        | μPD6466 Block Diagram                                                               | 26   |  |  |  |  |

| 2-1        | OSD LSI Basic Block Diagram                                                         | 27   |  |  |  |  |

| 2-2        | Dot Clock Oscillation Equivalent Circuit                                            | 28   |  |  |  |  |

| 2-3        | Horizontal Control Section                                                          | 29   |  |  |  |  |

| 2-4        | Vertical Control Section                                                            | 30   |  |  |  |  |

| 2-5        | Video RAM Control Section                                                           | 30   |  |  |  |  |

| 2-6        | Quadruple/4fsc Crystal Oscillation Circuit                                          | 33   |  |  |  |  |

| 2-7        | Synchronization Separation Circuit Section                                          | 35   |  |  |  |  |

| 2-8        | Sample Horizontal Synchronization Signal Correction Circuit Timing Charts           | 36   |  |  |  |  |

| 2-9        | Video Signal Output Section Equivalent Circuit                                      | 39   |  |  |  |  |

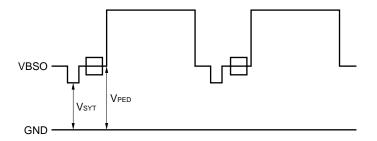

| 2-10       | Vsyt and Vped Levels of Composite Video Signal                                      | 40   |  |  |  |  |

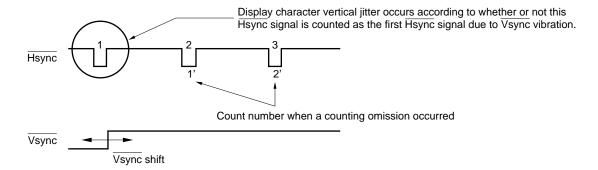

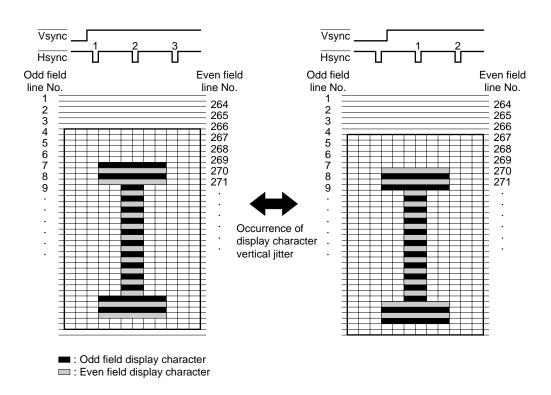

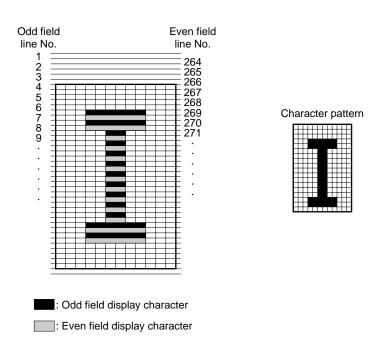

| 2-11       | Display Character Vertical Jitter Generation Mechanism                              |      |  |  |  |  |

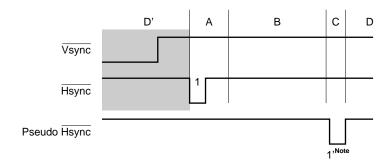

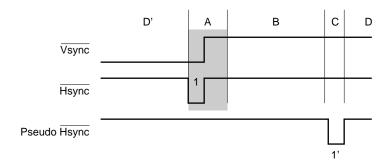

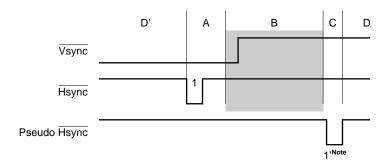

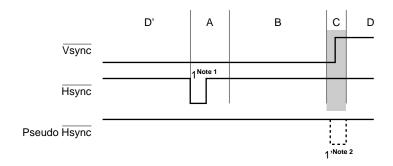

| 2-12       | Synchronization Protection Circuit Operation (Mode 1)                               |      |  |  |  |  |

| 2-13       | Synchronization Protection Circuit Operation (Mode 2)                               |      |  |  |  |  |

| 2-14       | Synchronization Protection Circuit Operation (Mode 3)                               |      |  |  |  |  |

| 2-15       | Synchronization Protection Circuit Operation (Mode 4)                               |      |  |  |  |  |

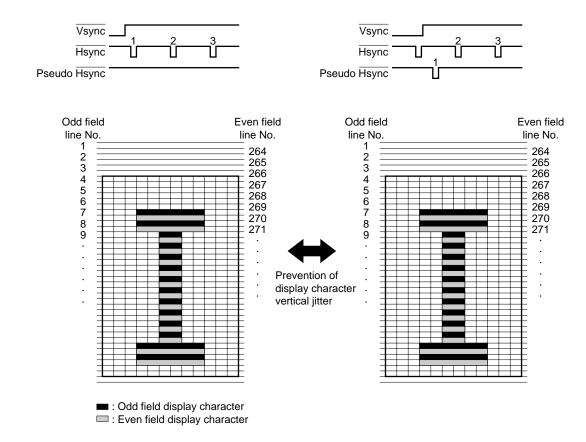

| 2-16       | Display Character Vertical Jitter Prevention Mechanism                              |      |  |  |  |  |

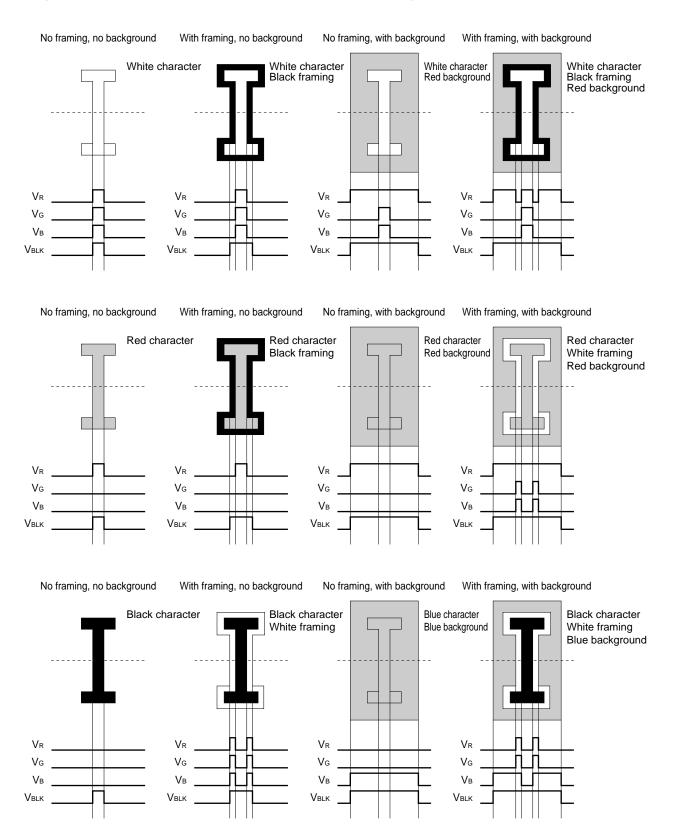

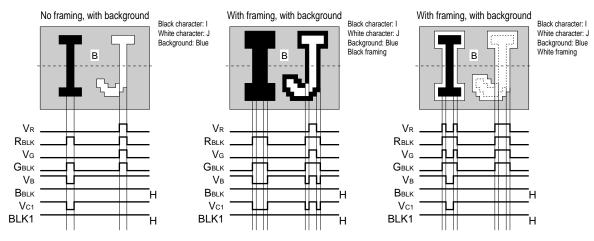

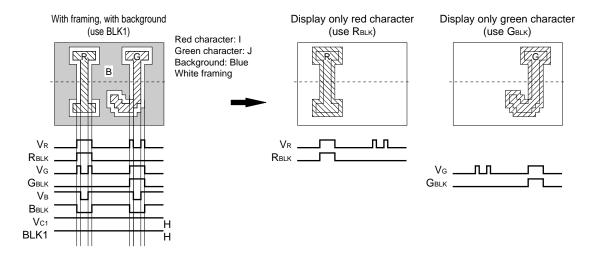

| 2-17       | Output Pins: Sample R, G, B, and BLK Output Images When RGB + Vc1 + Vc2 Is Selected |      |  |  |  |  |

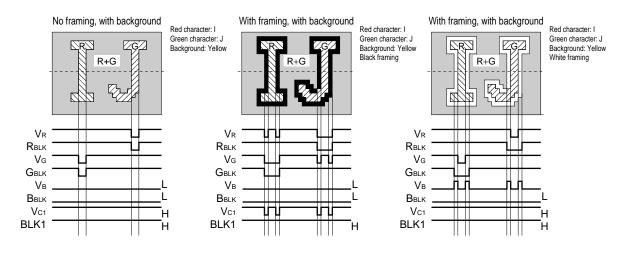

| 2-18       | Sample R, G, B, and BLK Output Images When RGB + 3BLK Is Selected                   | 47   |  |  |  |  |

| 2-19       | Sample Use of Blanking Signals Corresponding to RGB                                 | 48   |  |  |  |  |

| 2-20       | Character Display                                                                   | 49   |  |  |  |  |

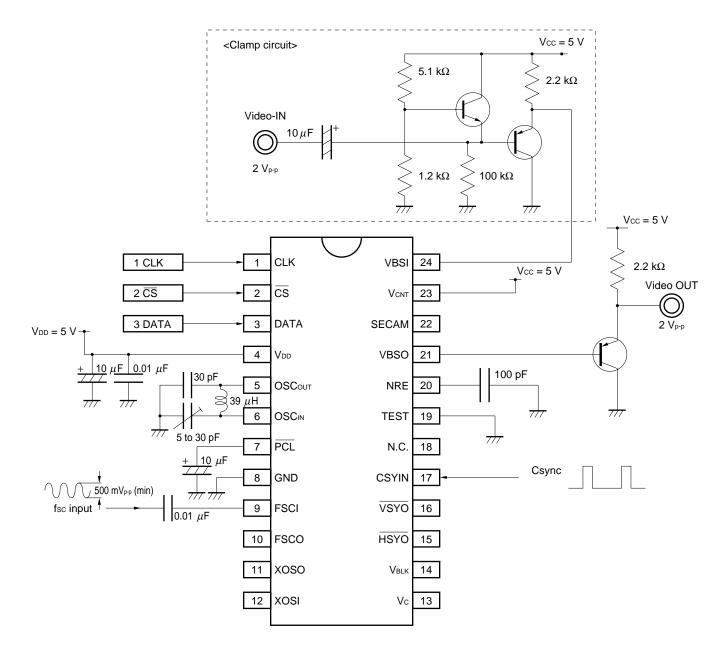

| 3-1        | Sample $\mu$ PD6464A or $\mu$ PD6465 Application Circuit                            |      |  |  |  |  |

|            | (When Quadruple Oscillation Is Selected)                                            | 58   |  |  |  |  |

| 3-2        | Sample $\mu$ PD6464A or $\mu$ PD6465 Application Circuit                            |      |  |  |  |  |

|            | (When 4fsc Crystal Oscillation Is Selected)                                         | 59   |  |  |  |  |

| 3-3        | Composite Synchronization Signal Separation Circuit                                 | 60   |  |  |  |  |

| 3-4        | Sample Application Circuit for Separate Video Signal Input                          | 63   |  |  |  |  |

| 3-5        | Sample Application Circuit for NTSC Direct Mode                                     | 65   |  |  |  |  |

| 3-6        | Sample $\mu$ PD6461 or $\mu$ PD6462 Application Circuit                             |      |  |  |  |  |

| 3-7        | Sample $\mu$ PD6466 Application Circuit                                             | 67   |  |  |  |  |

| 3-8        | Timing Chart for External Clock Forced Input                                        | 68   |  |  |  |  |

## LIST OF FIGURES (2/2)

| Figure No. | Title                                                                |      |  |

|------------|----------------------------------------------------------------------|------|--|

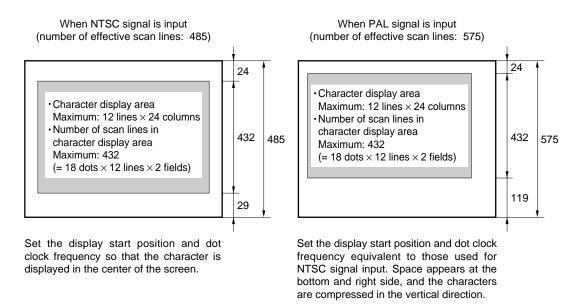

| 4-1        | Character Display Area Image 1 – When NTSC and PAL Signals Are Input |      |  |

|            | (for Equivalent Display Start Position and Dot Clock Frequency)      | . 72 |  |

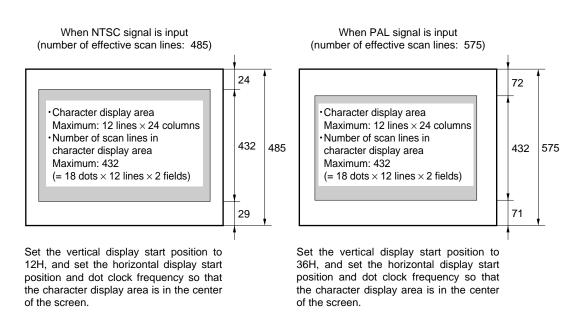

| 4-2        | Character Display Area Image 2 – When NTSC and PAL Signals Are Input |      |  |

|            | (for Center Display)                                                 | . 72 |  |

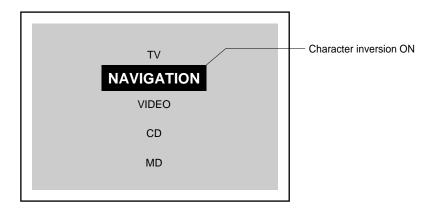

| 4-3        | Sample Display Using Character Inversion                             | . 77 |  |

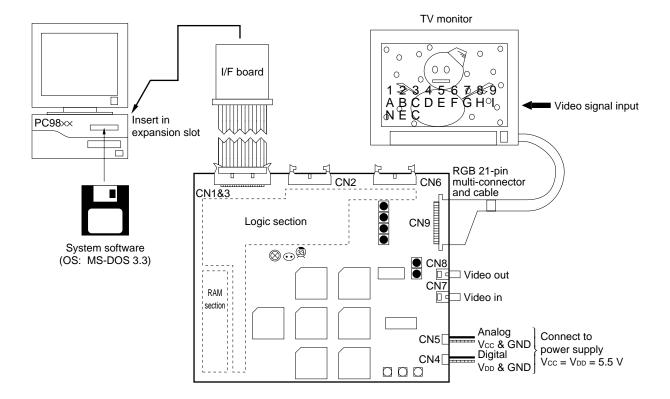

| 5-1        | ROM Verification Board Connection Diagram for RGB Display            | . 80 |  |

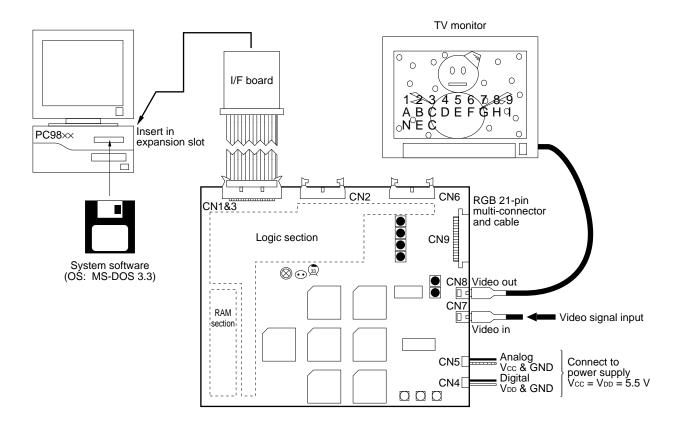

| 5-2        | ROM Verification Board Connection Diagram for VCR Display            | . 81 |  |

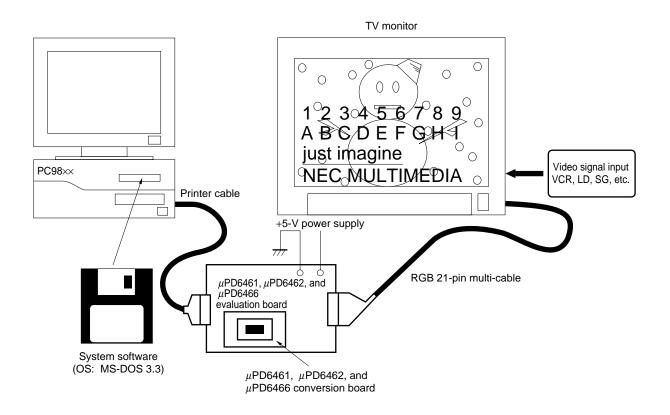

| 5-3        | Video-System OSD LSI Evaluation Board Connection Diagram             | . 82 |  |

| 5-4        | RGB-System OSD LSI Evaluation Board Connection Diagram               | . 82 |  |

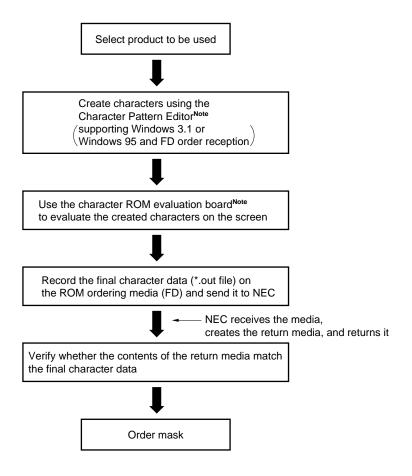

| 5-5        | OSD LSI Mask ROM Code Ordering Procedure (for FD Order Reception)    | . 83 |  |

#### LIST OF TABLES

| Table No. | Title                                                     | Page |

|-----------|-----------------------------------------------------------|------|

| 1-1       | List of OSD LSIs                                          | 14   |

| 1-2       | Ordering Information                                      | 15   |

| 1-3       | List of $\mu$ PD6464A and $\mu$ PD6465 Pin Functions      | 17   |

| 1-4       | List of $\mu$ PD6461 and $\mu$ PD6462 Pin Functions       | 20   |

| 1-5       | List of $\mu$ PD6466 Pin Functions                        | 23   |

| 2-1       | $\mu$ PD6464A or $\mu$ PD6465 Internal Video Signal Level | 40   |

| 2-2       | Command Data Transfer Format                              | 50   |

| 2-3       | $\mu$ PD6464A or $\mu$ PD6465 Command Tables              | 51   |

| 2-4       | $\mu$ PD6461 or $\mu$ PD6462 Command Tables (MSB First)   | 52   |

| 2-5       | $\mu$ PD6461 or $\mu$ PD6462 Command Tables (LSB First)   | 53   |

| 2-6       | $\mu$ PD6466 Command Tables (MSB First)                   | 54   |

| 2-7       | μPD6466 Command Tables (LSB First)                        | 55   |

| 3-1       | NTSC Direct Mode Setting Command                          | 64   |

[MEMO]

#### **CHAPTER 1 OVERVIEW**

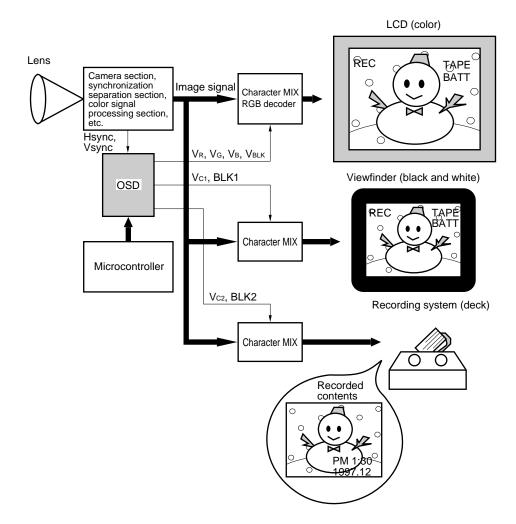

The on-screen character display CMOS LSI (OSD LSI) is used to display character data on various types of monitor screens. The size of one character is 12 (horizontal) by 18 (vertical) dots, and up to 12 lines of 24 columns (288 characters) can be displayed. The character types are determined by the ROM capacity of each product. NEC has 128-character ( $\mu$ PD6462,  $\mu$ PD6464A), 256-character ( $\mu$ PD6465), and 512-character ( $\mu$ PD6466) OSD LSIs.

Also, the NEC OSD LSIs are broadly divided into video-system OSD LSIs ( $\mu$ PD6464A,  $\mu$ PD6465) and RGB-system OSD LSIs ( $\mu$ PD6461,  $\mu$ PD6462,  $\mu$ PD6466) according to their use. By combining it with a microcontroller, a video-system OSD LSI controls not only the program screen of a deck-type VCR or LD player, but also various indicators (such as the tape counter). An RGB-system OSD LSI controls the display of the counter, time, date, and other indicators on the viewfinder of a camcorder, the transcription of the time, date, and other indicators on a video tape, and the display of the channel or other indicators on a TV screen.

This user's manual describes the operation of OSD LSIs and presents several practical examples of their use.

Figure 1-1. Sample Uses of OSD LSIs (RGB-System OSD LSI: Camcorder)

#### 1.1 List of OSD LSIs

Table 1-1. List of OSD LSIs

|                                                          | Video-s                                                                                                                                                               | system                                                      |                                              | RGB-system                                                    |                                                                                                       |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Sample uses                                              | TV, video, video CD                                                                                                                                                   |                                                             | Camcorder, DVD, LCD TV, digital still camera |                                                               | al still camera                                                                                       |

| Product name                                             | μPD6464A                                                                                                                                                              | μPD6465                                                     | μPD6461                                      | μPD6462                                                       | μPD6466                                                                                               |

| Character type                                           | 128                                                                                                                                                                   | 256                                                         | 256                                          | 128                                                           | 512                                                                                                   |

| Number of display characters                             | 12 lines × 24 colum                                                                                                                                                   | nns (288 characters                                         | 3)                                           |                                                               |                                                                                                       |

| Dot matrix                                               | 12 (horizontal) × 18                                                                                                                                                  | 3 (vertical) dots                                           |                                              |                                                               |                                                                                                       |

| Character color                                          | Single color (white) level for the screen                                                                                                                             | · -                                                         |                                              |                                                               |                                                                                                       |

| Character size (unit: lines)                             | 1× and 2×<br>(simultaneous horiz                                                                                                                                      | zontal and vertical s                                       | specification)                               |                                                               | 1x, 2x, 3x, and 4x<br>(independent<br>horizontal and<br>vertical<br>specifications)                   |

| Character color inversion (unit: characters)             | None                                                                                                                                                                  |                                                             | Black characters (no framing)                |                                                               | Black characters<br>(framing control<br>disabled)<br>White characters<br>(framing control<br>enabled) |

| Character left-right inversion (unit: characters)        | None Available (cannot be used when blinking is specified)                                                                                                            |                                                             |                                              | blinking is                                                   |                                                                                                       |

| Blinking (unit: characters)                              | Blinking ratio is 1:1 (blinking frequency can be selected for the entire screen from the three options corresponding to approximately 0.5, 1, and 2 Hz)               |                                                             |                                              |                                                               |                                                                                                       |

| Internal video signal color White, black, blue, or green |                                                                                                                                                                       | None                                                        |                                              | White or blue<br>(effective only for<br>RGB-system<br>output) |                                                                                                       |

| Background (unit: screen)                                | No background, bla                                                                                                                                                    | ack framing, black-o                                        | on-white, black filling                      | ]                                                             |                                                                                                       |

| Background color (unit: screen)                          | Single color (black)                                                                                                                                                  | 1                                                           | 8 colors (RGB-syst                           | tem output) or<br>Vc1 and Vc2 syster                          | m output)                                                                                             |

| Framing color (unit: screen)                             | Single color (black)                                                                                                                                                  | )                                                           | 2 colors (white and                          | l black)                                                      |                                                                                                       |

| Supported video signal method                            |                                                                                                                                                                       | C, PSL, PAL-M, SECAM, — — — — — — — — — — — — — — — — — — — |                                              |                                                               |                                                                                                       |

| Video signal input/output                                | Composite video signal                                                                                                                                                |                                                             | No input/output system                       |                                                               |                                                                                                       |

| Character signal output                                  | Character signal and blanking signal RGB+3BLK or RGB+Vc1+Vc2 (for μPD6461 and μPD6462 select according to mask code option; for μPD6466, select according to command) |                                                             |                                              |                                                               |                                                                                                       |

| Video RAM data clear                                     | Video RAM data can be cleared by the video RAM batch clear command and the power-ON clear function                                                                    |                                                             |                                              |                                                               |                                                                                                       |

| Interface with microcontroller                           | Serial input type of 8-bit variable word length                                                                                                                       |                                                             |                                              |                                                               |                                                                                                       |

| Operation power supply range                             | 4.5 to 5.5 V                                                                                                                                                          |                                                             | 2.7 to 5.5 V                                 |                                                               |                                                                                                       |

| Packages 24-pin SDIP 24-pin SOP                          |                                                                                                                                                                       | 20-pin SSOP<br>24-pin SOP                                   | 20-pin SSOP                                  | 20-pin SSOP<br>24-pin SOP                                     |                                                                                                       |

#### 1.2 Ordering Information

Table 1-2. Ordering Information

|                | Part Number    | Package                              | NEC standard ROM code number                                                                                                                                                          |

|----------------|----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video-         | μPD6464ACS-××× | 24-pin plastic shrink DIP (300 mils) | 001                                                                                                                                                                                   |

| system         | μPD6464AGT-××× | 24-pin plastic SOP (375 mils)        | 101                                                                                                                                                                                   |

|                | μPD6465CS-×××  | 24-pin plastic shrink DIP (300 mils) | 001                                                                                                                                                                                   |

|                | μPD6465GT-×××  | 24-pin plastic SOP (375 mils)        | 101                                                                                                                                                                                   |

| RGB-<br>system | μPD6461GS-xxx  | 20-pin plastic shrink SOP (300 mils) | <ul> <li>101: MSB first, 3-line unit setting, RBG + 3BLK, option B, LC oscillation</li> <li>102: MSB first, 3-line unit setting, RBG + Vc1 + Vc2, option B, LC oscillation</li> </ul> |

|                | μPD6461GT-×××  | 24-pin plastic SOP (375 mils)        | _                                                                                                                                                                                     |

|                | μPD6462GS-×××  | 20-pin plastic shrink SOP (300 mils) | 001: MSB first, 3-line unit setting, RBG + Vc1 + Vc2, option C, LC oscillation                                                                                                        |

|                | μPD6466GS-×××  | 20-pin plastic shrink SOP (300 mils) | 001                                                                                                                                                                                   |

|                | μPD6466GT-×××  | 24-pin plastic SOP (375 mils)        | 201                                                                                                                                                                                   |

#### Remarks 1. xxx indicates ROM code suffix.

2. For the  $\mu$ PD6461 and  $\mu$ PD6462, the following are selected according to the mask code option (for the  $\mu$ PD6466, they can be selected according to the initialization command or the CMDCT pin). For details, refer to the data sheet for each product.

Data transfer

LSB first or MSB first

Vertical display start position : 3-line unit setting or 9-line unit setting

Pin selection : RBG + Vc1 + Vc2 or RGB + 3BLK

Output selection : Option A, option B, or option C

Dot clock : LC oscillation or external clock input

#### 1.3 Pin Configurations

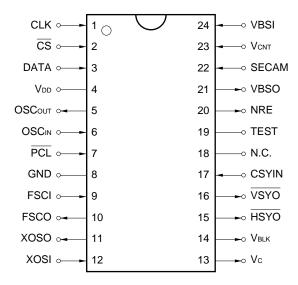

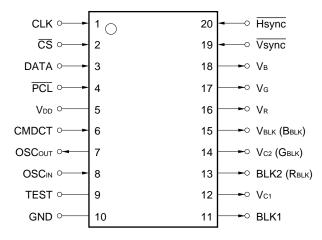

Figure 1-2.  $\mu$ PD6464A or  $\mu$ PD6465 Pin Configuration (Top View)

#### 24-pin plastic shrink DIP (300 mils)

$\mu$ PD6464ACS- $\times\times$  $\mu$ PD6465CS- $\times\times$

#### 24-pin plastic SOP (375 mils)

$\mu$ PD6464AGT- $\times\times$  $\mu$ PD6465GT- $\times\times$

#### Remark xxx indicates ROM code suffix.

CLK : Clock Input PCL : Power-on Clear

CS : Chip Select Input SECAM : SECAM subcarrier Input

CSYIN : Composite Synchronization Signal Input TEST : Test Pin

DATA : Serial Data Input VBLK : Blanking Signal Output

GND : Ground Vc : Character Signal Output

HSYO : Horizontal Synchronization Signal Output VCNT : Video Signal Output Level Adjustment

N.C. : No Connection VDD : Power Supply

OSCIN : LC Oscillation Input XOSI : Quadruple Oscillation Input OSCout : LC Oscillation Output XOSO : Quadruple Oscillation Output

Table 1-3. List of  $\mu$ PD6464A and  $\mu$ PD6465 Pin Functions

| Pin No. | Pin Symbol                              | Pin Name                                    | Function                                                                                                                                                                                    |  |

|---------|-----------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | CLK                                     | Clock Input                                 | Inputs clock for data read. Data input to the DATA pin is read at the rising edge of the clock input to this pin.                                                                           |  |

| 2       | CS                                      | Chip Select Input                           | Serial transfer can be acknowledged by making this $\overline{\text{CS}}$ pin low.                                                                                                          |  |

| 3       | DATA                                    | Serial Data Input                           | Inputs control data. Data is read in synchronization with the clock input to the CLK pin.                                                                                                   |  |

| 4       | V <sub>DD</sub>                         | Power Supply                                | Supplies power to the IC.                                                                                                                                                                   |  |

| 5<br>6  | OSC <sub>OUT</sub><br>OSC <sub>IN</sub> | LC Oscillation Output LC Oscillation Input  | These are input and output pins of an oscillator that generates dot clocks. Connect a coil and a capacitor to these pins for oscillation.                                                   |  |

| 7       | PCL                                     | Power-ON Clear                              | Power-ON clear pin. Make this pin high on power application. It initializes the internal circuitry of the IC.                                                                               |  |

| 8       | GND                                     | Ground                                      | Ground pin of the IC.                                                                                                                                                                       |  |

| 9       | FSCI                                    | fsc Signal Input                            | Inputs color subcarrier signal (fsc) when quadruple oscillation is selected. Connect it to GND or Vcc when 4fsc crystal oscillation is selected.                                            |  |

| 10      | FSCO                                    | Frequency Error Output                      | Frequency error output signal of the $\times 4$ multiplier. Leave it open when 4fsc crystal oscillation is selected.                                                                        |  |

| 11      | xoso                                    | Quadruple Oscillation Output                | The quadruple oscillator LC for internal video signal generation is connected                                                                                                               |  |

| 12      | XOSI                                    | Quadruple Oscillation Input                 | to these pins. A crystal oscillator also can be connected.                                                                                                                                  |  |

| 13      | Vc                                      | Character Signal Output                     | Character signal output pin, which is high active.                                                                                                                                          |  |

| 14      | VBLK                                    | Blanking Signal Output                      | This pin outputs a blanking signal that cuts the video signal. It corresponds to Vc output and is high active.                                                                              |  |

| 15      | HSYO                                    | Horizontal Synchronization<br>Signal Output | Outputs a horizontal synchronization signal separated from the composisynchronization signal.                                                                                               |  |

| 16      | VSYO                                    | Vertical Synchronization<br>Signal Output   | Outputs a vertical synchronization signal separated from the composite synchronization signal.                                                                                              |  |

| 17      | CSYIN                                   | Composite Synchronization<br>Signal Input   | Inputs a composite synchronization signal for synchronization separation. Always input this signal when external video signal mode is used. The input polarity is positive synchronization. |  |

| 18      | N.C.                                    | No Connection                               | Free pin. Leave this pin open.                                                                                                                                                              |  |

| 19      | TEST                                    | Test Pin                                    | Test mode select pin. Generally, connect this pin to GND.                                                                                                                                   |  |

| 20      | NRE                                     | Noise Reduction Constant<br>Append          | Constant append pin for noise reduction.                                                                                                                                                    |  |

| 21      | VBSO                                    | Composite Video Signal Output               | Outputs a composite video signal with which the character signal is mixed.                                                                                                                  |  |

| 22      | SECAM                                   | SECAM subcarrier Input                      | SECAM subcarrier signal mixing pin. When a mode other than SECAM is selected, leave this pin open.                                                                                          |  |

| 23      | VCNT                                    | Video Signal Output Level<br>Adjustment     | Adjusts the output level adjustment of the composite video signal and luminance signal.                                                                                                     |  |

| 24      | VBSI                                    | Composite Video Signal Input                | Inputs a composite video signal. Inputs a signal with the leading edge clamped, consisting of a negative synchronization and positive video signal.                                         |  |

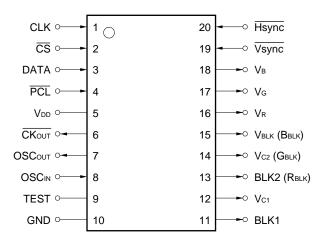

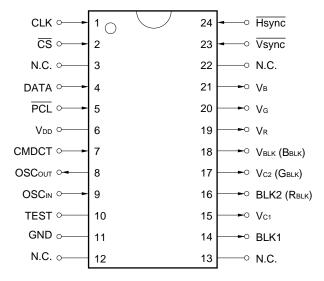

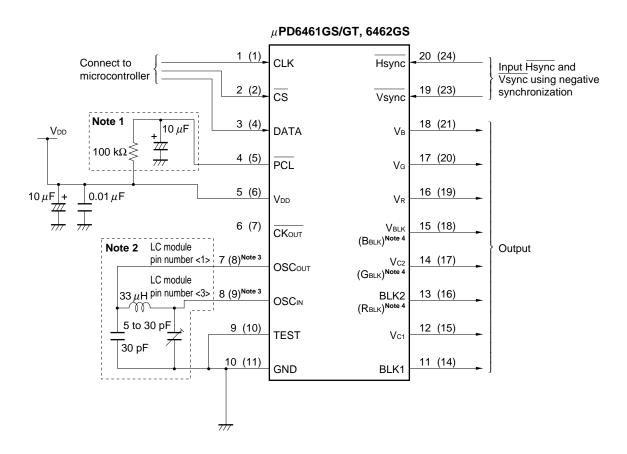

Figure 1-3.  $\mu$ PD6461 or  $\mu$ PD6462 Pin Configuration (Top View)

#### 20-pin plastic shrink SOP (300 mils)

$\begin{array}{l} \mu \text{PD6461GS-} \times \times \times \\ \mu \text{PD6462GS-} \times \times \times \end{array}$

#### 24-pin plastic SOP (375 mils)

$\mu$ PD6461GT- $\times\times$

Remarks 1. xxx indicates ROM code suffix.

2. The symbols enclosed in parentheses are set by the mask code option (RGB + Blanking corresponding to RGB).

BBLK : Blanking B

BLK1, BLK2 : Blanking Output 1, 2

CKOUT : Clock Output

CLK : Clock Input

CS : Chip Select

DATA : Data Input

GBLK : Blanking G

GND : Ground

Hsync : Horizontal Synchronous Signal Input

N.C. : No Connection

OSCIN : Oscillator Input

OSCOUT : Oscillator Output

PCL : Power-on Clear

RBLK : Blanking R

TEST : Test

V<sub>B</sub> : Character Signal Output

VBLK : Blanking Signal Output for VR, VG, and VB

Vc1, Vc2 : Character Signal output 1, 2

V<sub>DD</sub> : Power supply

VG : Character Signal Output VR : Character Signal Output

Vsync : Vertical Synchronous Signal Input

Table 1-4. List of  $\mu \text{PD6461}$  and  $\mu \text{PD6462}$  Pin Functions

| Pin No.Note 1                 | Note 2<br>Pin Symbol        | Pin Name <sup>Note 2</sup>                                | Function                                                                                                                                                                                                                                                                                |

|-------------------------------|-----------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                             | CLK                         | Clock Input                                               | Inputs clock for data read. Data input to the DATA pin is read at the rising edge of the clock input to this pin.                                                                                                                                                                       |

| 2                             | CS                          | Chip Select Input                                         | Serial transfer can be acknowledged by making this $\overline{\text{CS}}$ pin low.                                                                                                                                                                                                      |

| 3 (4)                         | DATA                        | Serial Data Input                                         | Inputs control data. Data is read in synchronization with the clock input to the CLK pin.                                                                                                                                                                                               |

| 4 (5)                         | PCL                         | Power-ON Clear                                            | Power-ON clear pin. Make this pin high on power application. It initializes the internal circuitry of the IC.                                                                                                                                                                           |

| 5 (6)                         | V <sub>DD</sub>             | Power Supply                                              | Supplies power to the IC.                                                                                                                                                                                                                                                               |

| 6 (7)                         | СКоит                       | Clock Output                                              | Checks the oscillation frequency. It uses N-channel open-drain output.                                                                                                                                                                                                                  |

| 7 (8)<br>8 (9)                | OSC <sub>IN</sub>           | LC Oscillation Input/Output (OSCIN: External clock input) | These are input and output pins of an oscillator that generates dot clocks. Connect a coil and a capacitor to these pins for oscillation. (When external clock input is selected by the mask option, the external clock (clock synchronized with Hsync) is input. OSCout is left open.) |

| 9 (10)                        | TEST                        | Test Pin                                                  | IC test pin. Connect this pin to GND.                                                                                                                                                                                                                                                   |

| 10 (11)                       | GND                         | Ground                                                    | Connect this pin to the system GND.                                                                                                                                                                                                                                                     |

| 11 (14)                       | BLK1                        | Blanking Signal Output 1                                  | This pin outputs a blanking signal that cuts the video signal. It corresponds to Vc1 output and is high active.  (When blanking corresponding to RGB is selected by the mask option, the logical sum of RBLK, GBLK, and BBLK is output.)                                                |

| 12 (15)                       | Vc1                         | Character Signal Output 1                                 | Outputs the character signal. It is high active. (When blanking corresponding to RGB is selected by the mask option, the logical sum of V <sub>R</sub> , V <sub>G</sub> , and V <sub>B</sub> is output.)                                                                                |

| 13 (16)                       | BLK2<br>(R <sub>BLK</sub> ) | Blanking Signal Output 2<br>(Blanking R)                  | This pin outputs a blanking signal that cuts the video signal. It corresponds to Vc2 output and is high active.  (The blanking signal corresponding to VR output is output. It is high active.)                                                                                         |

| 14 (17)                       | Vc2<br>(Gblk)               | Character Signal Output 2<br>(Blanking G)                 | Outputs the character signal. It is high active. (The blanking signal corresponding to V <sub>G</sub> output is output. It is high active.)                                                                                                                                             |

| 15 (18)                       | VBLK<br>(BBLK)              | Blanking Signal Output<br>(Blanking B)                    | This pin outputs a blanking signal that cuts the video signal. It corresponds to VR, VG, and VB output and is high active. (The blanking signal corresponding to VB output is output. It is high active.)                                                                               |

| 16 (19)<br>17 (20)<br>18 (21) | VR<br>VG<br>VB              | Character Signal Output                                   | Character signal output pin, which is high active.                                                                                                                                                                                                                                      |

| 19 (23)                       | Vsync                       | Vertical Synchronization<br>Signal Input                  | Inputs the vertical synchronization signal. Input using negative synchronization.                                                                                                                                                                                                       |

| 20 (24)                       | Hsync                       | Horizontal Synchronization<br>Signal Input                | Inputs the horizontal synchronization signal. Input using negative synchronization.                                                                                                                                                                                                     |

| (3,12,13,22)                  | N.C.                        | No Connection                                             | Free pin.                                                                                                                                                                                                                                                                               |

**Notes** 1. The numbers enclosed in parentheses are pin numbers for the  $\mu$ PD6461GT-xxx.

2. The symbols and names enclosed in parentheses are set by the mask code option (RGB + Blanking corresponding to RGB).

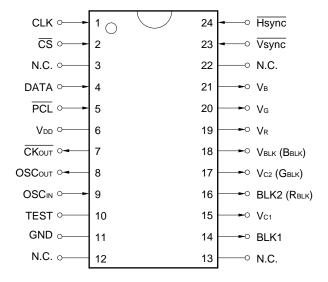

Figure 1-4.  $\mu$ PD6466 Pin Configuration (Top View)

#### 20-pin plastic shrink SOP (300 mils)

$\mu$ PD6466GS-×××

#### 24-pin plastic SOP (375 mils)

$\mu$ PD6466GT- $\times\times$

#### **Remarks 1.** ××× indicates ROM code suffix.

2. The symbols enclosed in parentheses are set by the initialization command (RGB + Blanking corresponding to RGB).

BBLK : Blanking B

BLK1, BLK2: Blanking Output 1, 2

CLK : Clock

CMDCT : Command Control

CS : Chip Select

DATA : Data Input

GBLK : Blanking G

GND : Ground

Hsync : Horizontal Synchronous Signal Input

N.C. : No Connection

OSCIN : Oscillator Input

OSCOUT : Oscillator Output

PCL : Power-on Clear

RBLK : Blanking R

TEST : Test

V<sub>B</sub> : Character Signal Output

VBLK : Blanking Signal Output for VR, VG, and VB

Vc1, Vc2 : Character Signal output 1, 2

VDD : Power supply

VG : Character Signal Output VR : Character Signal Output

Vsync : Vertical Synchronous Signal Input

Table 1-5. List of  $\mu PD6466$  Pin Functions

| Pin No.Note 1                 | Pin Symbol                              | Pin Name <sup>Note 2</sup>                                | Function                                                                                                                                                                                                                                                                                           |

|-------------------------------|-----------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                             | CLK                                     | Clock Input                                               | Inputs clock for data read. Data input to the DATA pin is read at the rising edge of the clock input to this pin.                                                                                                                                                                                  |

| 2                             | CS                                      | Chip Select Input                                         | Serial transfer can be acknowledged by making this $\overline{\text{CS}}$ pin low.                                                                                                                                                                                                                 |

| 3 (4)                         | DATA                                    | Serial Data Input                                         | Inputs control data. Data is read in synchronization with the clock input to the CLK pin.                                                                                                                                                                                                          |

| 4 (5)                         | PCL                                     | Power-ON Clear                                            | Power-ON clear pin. Make this pin high on power application. It initializes the internal circuitry of the IC.                                                                                                                                                                                      |

| 5 (6)                         | V <sub>DD</sub>                         | Power Supply                                              | Supplies power to the IC.                                                                                                                                                                                                                                                                          |

| 6 (7)                         | CMDCT                                   | Command Control                                           | Switches between LSB-first and MSB-first input for commands. When this pin is low, LSB-first input is used. When it is high, MSB-first input is used. When using LSB-first input, this pin can be left open.                                                                                       |

| 7 (8)<br>8 (9)                | OSC <sub>OUT</sub><br>OSC <sub>IN</sub> | LC Oscillation Input/Output (OSCIN: External clock input) | These are input and output pins of an oscillator that generates dot clocks. Connect a coil and a capacitor to these pins for oscillation. (When external clock input is selected by the initialization command, the external clock (clock synchronized with Hsync) is input. OSCout is left open.) |

| 9 (10)                        | TEST                                    | Test                                                      | IC test pin. Connect this pin to GND.                                                                                                                                                                                                                                                              |

| 10 (11)                       | GND                                     | Ground                                                    | Connect this pin to the system GND.                                                                                                                                                                                                                                                                |

| 11 (14)                       | BLK1                                    | Blanking Signal Output 1                                  | This pin outputs a blanking signal that cuts the video signal. It corresponds to Vc1 output and is high active.  (When blanking corresponding to RGB is selected by the command, the logical sum of Rblk, Gblk, and Bblk is output.)                                                               |

| 12 (15)                       | Vc1                                     | Character Signal Output 1                                 | Outputs the character signal. It is high active. (When blanking corresponding to RGB is selected by the command, the logical sum of VR, VG, and VB is output.)                                                                                                                                     |

| 13 (16)                       | BLK2<br>(RBLK)                          | Blanking Signal Output 2<br>(Blanking R)                  | This pin outputs a blanking signal that cuts the video signal. It corresponds to Vc2 output and is high active.  (The blanking signal corresponding to VR output is output. It is high active.)                                                                                                    |

| 14 (17)                       | Vc2<br>(Gblk)                           | Character Signal Output 2<br>(Blanking G)                 | Outputs the character signal. It is high active. (The blanking signal corresponding to Ve output is output. It is high active.)                                                                                                                                                                    |

| 15 (18)                       | VBLK<br>(BBLK)                          | Blanking Signal Output<br>(Blanking B)                    | This pin outputs a blanking signal that cuts the video signal. It corresponds to VR, VG, and VB output and is high active. (The blanking signal corresponding to VB output is output. It is high active.)                                                                                          |

| 16 (19)<br>17 (20)<br>18 (21) | VR<br>VG<br>VB                          | Character Signal Output                                   | Character signal output pin, which is high active.                                                                                                                                                                                                                                                 |

| 19 (23)                       | Vsync                                   | Vertical Synchronization<br>Signal Input                  | Inputs the vertical synchronization signal. Input using negative synchronization.                                                                                                                                                                                                                  |

| 20 (24)                       | Hsync                                   | Horizontal Synchronization<br>Signal Input                | Inputs the horizontal synchronization signal. Input using negative synchronization.                                                                                                                                                                                                                |

| (3,12,13,22)                  | N.C.                                    | No Connection                                             | Free pin.                                                                                                                                                                                                                                                                                          |

**Notes** 1. The numbers enclosed in parentheses are pin numbers for the  $\mu$ PD6466GT-xxx.

2. The names enclosed in parentheses are set by the initialization command (RGB + Blanking corresponding to RGB).

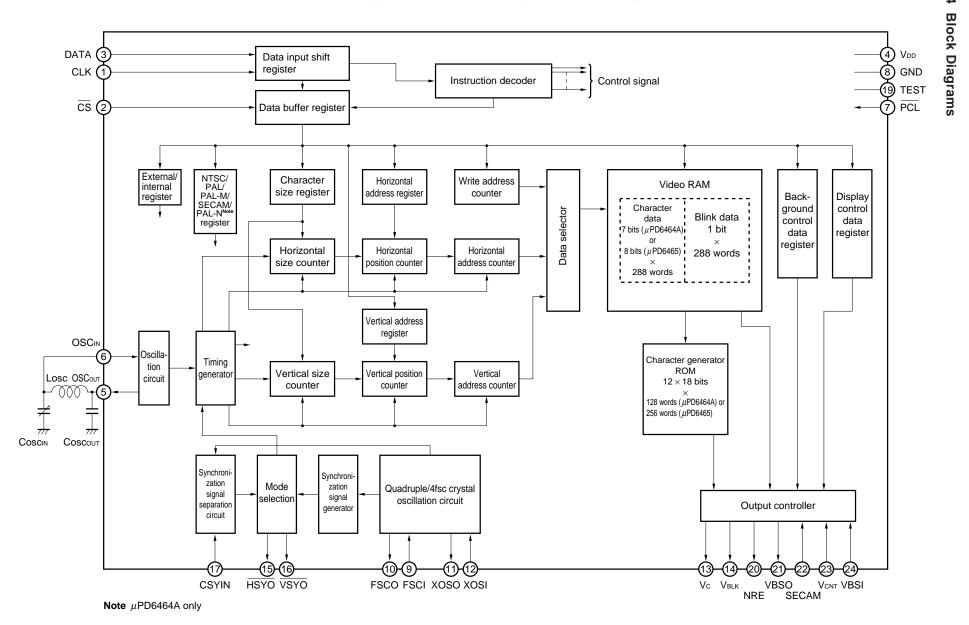

Figure 1-5.  $\mu$ PD6464A and  $\mu$ PD6465 Block Diagram

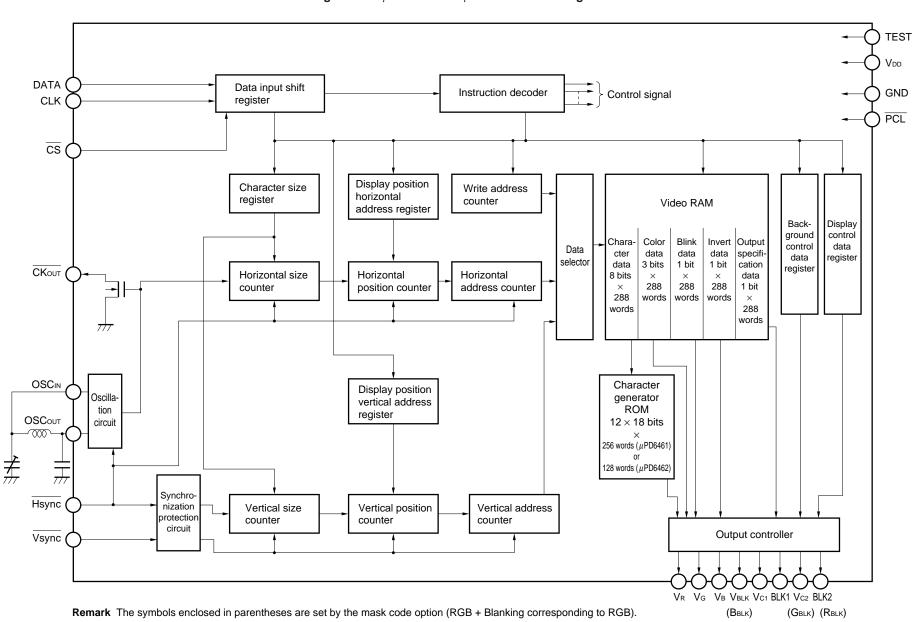

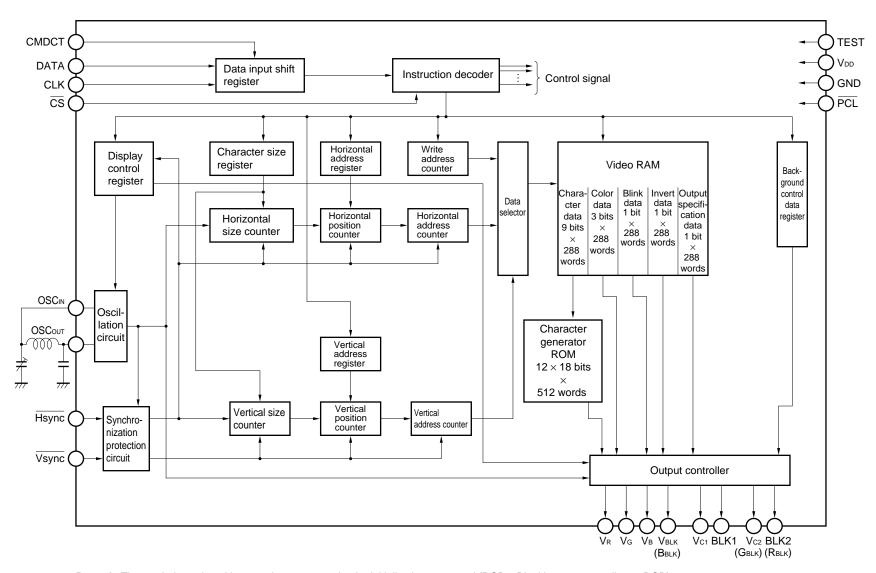

Figure 1-6.  $\mu$ PD6461 and  $\mu$ PD6462 Block Diagram

Figure 1-7. μPD6466 Block Diagram

Remark The symbols enclosed in parentheses are set by the initialization command (RGB + Blanking corresponding to RGB).

#### **CHAPTER 2 BASIC OPERATION**

This chapter describes the basic operation of an OSD LSI.

#### 2.1 OSD LSI Configuration

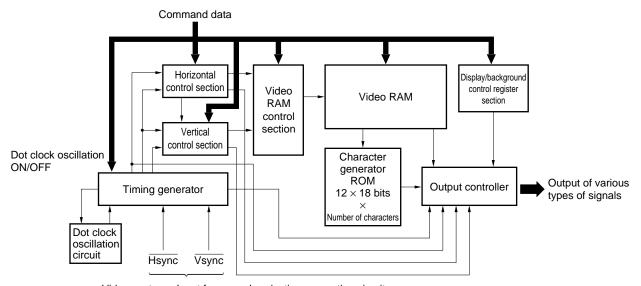

An OSD LSI consists of a dot clock oscillation circuit, timing generator, horizontal control section, vertical control section, video RAM control section, video RAM, character generator ROM, display/background control register section, and output controller.

The OSD LSI, which is controlled by command data sent from a microcontroller, displays the character data stored in the character generator ROM ( $\mu$ PD6462 and  $\mu$ PD6464A: 128 characters;  $\mu$ PD6461 and  $\mu$ PD6465: 256 characters;  $\mu$ PD6466: 512 characters) on the display screen.

Figure 2-1. OSD LSI Basic Block Diagram

Video-system: Input from synchronization separation circuit

RGB-system: Input from synchronization separation protection circuit

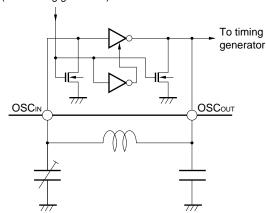

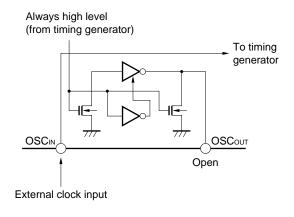

#### 2.1.1 Dot clock oscillation circuit

The dot clock oscillation circuit consists of the OSD LSI and an externally connected LC circuit. With an RGB-system OSD LSI, external clock input can be selected (For the  $\mu$ PD6461 and  $\mu$ PD6462, this is selected by the mask code option; for the  $\mu$ PD6466, it is selected by the initialization command).

Figure 2-2. Dot Clock Oscillation Equivalent Circuit

#### (a) When LC oscillation is selected

# (b) When external clock input is selected ( $\mu$ PD6461, $\mu$ PD6462, or $\mu$ PD6466)

High level when oscillation is OFF (from timing generator)

**Remark** When LC oscillation is ON, the dot clock oscillation circuit is controlled as follows by the timing generator while Hsync is low.

When display is ON : Dot clock oscillation stopped

When display is OFF: Dot clock oscillation

The dot clock frequency (fosc) when LC oscillation is ON can be calculated using the following formulas.

$$fosc = \frac{1}{(2\pi\sqrt{LC})} [Hz]$$

$$C = \frac{C_{in} \cdot C_{out}}{(C_{in} + C_{out})} [F]$$

By setting L = 33  $\mu$ H, C<sub>in</sub> = 5 to 30 pF (trimmer capacitor), and C<sub>out</sub> = 30 pF, the circuit can be used in the LC oscillation frequency range (fosc = 6 to 8 MHz) recommended by NEC for operation.

The actual circuit will have a lower frequency than the calculated value due to effects such as the stray capacitance of the pins or delay within the LSI.

#### 2.1.2 Timing generator

The timing generator generates various types of timing signals according to horizontal/vertical synchronization signals input from the dot clock oscillation circuit, synchronization separation circuit, synchronization signal generator (video-system OSD LSI) or synchronization protection circuit (RGB-system OSD LSI) commands from the microcontroller (such as LC oscillation ON/OFF, crystal oscillation ON/OFF, or display ON/OFF, etc.).

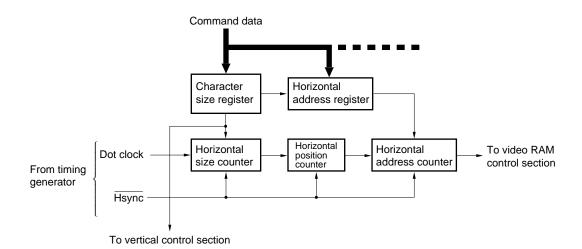

#### 2.1.3 Horizontal control section

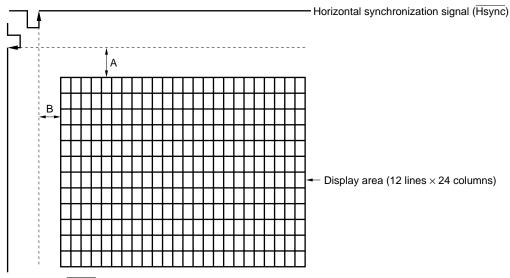

The horizontal display start position of a character is determined by counting dot clocks from the rising edge of the horizontal synchronization signal (Hsync). The character is displayed at the position corresponding to this horizontal display start position and the specified video RAM column address.

Each block reset is synchronized with Hsync. If Hsync is not supplied within the OSD LSI, the character is not displayed correctly, since no reset occurs.

Figure 2-3. Horizontal Control Section

#### 2.1.4 Vertical control section

The vertical display start position of a character is determined by counting rising edges of the horizontal synchronization signal (Hsync) from the rising edge of the vertical synchronization signal (Vsync). The character is displayed at the position corresponding to this vertical display start position and the specified video RAM line address. The character type to be displayed is set by the character generator ROM line address control.

Command data Vertical address From character register size register Vertical Vertical size Vertical address To video RAM Hsync position counter counter control section From timing counter generator Vsync

Figure 2-4. Vertical Control Section

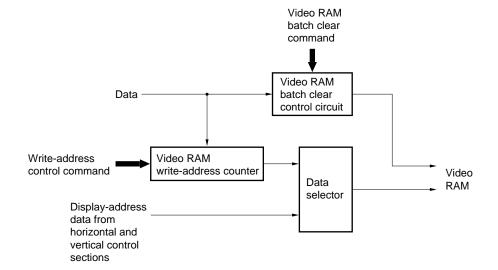

#### 2.1.5 Video RAM control section

The video RAM control section controls video RAM addresses. When a video RAM batch clear command is executed, the Display Off Code is written to all addresses (288 words) of video RAM.

Figure 2-5. Video RAM Control Section

#### 2.1.6 Video RAM

The video RAM maintains data set in character units corresponding to a 12 line by 24 column display area.

#### 2.1.7 Character generator ROM

The character generator ROM stores a character font. The number of characters is determined by the ROM capacity. The character generator ROM for a video-system OSD LSI can have a capacity of 128 characters ( $\mu$ PD6464A) or 256 characters ( $\mu$ PD6465). For an RGB-system OSD LSI, can have a capacity of 128 characters ( $\mu$ PD6462), 256 characters ( $\mu$ PD6461), or 512 characters ( $\mu$ PD6466).

#### 2.1.8 Output controller

The output controller controls the display of characters, backgrounds, and other output.

#### 2.2 Basic Operation of a Video-System OSD LSI

This section describes the basic operation of the circuits of a video-system OSD LSI ( $\mu$ PD6464A or  $\mu$ PD6465).

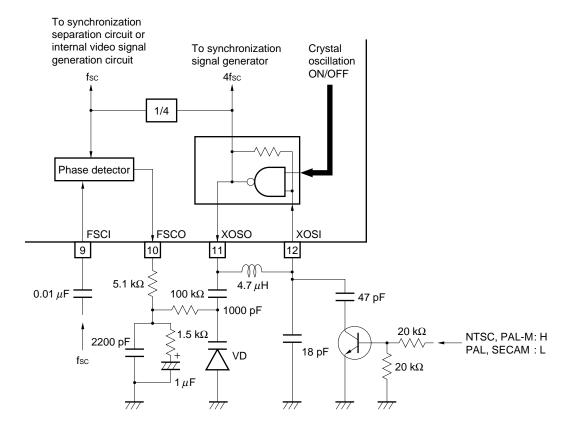

#### 2.2.1 Quadruple/4fsc crystal oscillation circuit

Figure 2-6 shows a block diagram of a quadruple/4fsc crystal oscillation circuit.

With the  $\mu$ PD6464A or  $\mu$ PD6465, quadruple oscillation or 4fsc crystal oscillation is selected according to the externally connected circuit and oscillation mode control command. Since the 4fsc signal generated by the oscillation circuit is used as the reference clock for synchronization signal generation when internal video signal mode is set and the fsc signal is used as the reference clock for internal video signal generation and for synchronization separation in the synchronization separation circuit, a crystal oscillation control command must be used to set crystal oscillation to ON when generating characters.

The operation of this circuit when each mode is selected is explained below.

#### (1) When quadruple oscillation is selected

The fsc signal must be input from the FSCI pin (pin 9) (see **Figure 3-1 Sample**  $\mu$ **PD6464A** or  $\mu$ **PD6465 Application Circuit (When Quadruple Oscillation Is Selected)**). The 4fsc signal is generated by an externally connected LC oscillator and internal circuits of the  $\mu$ PD6464A or  $\mu$ PD6465. Also, the phase of the signal obtained by dividing the 4fsc signal generated by LC oscillation into 4 parts is compared with the phase of the fsc signal input to the FSCI pin, and the phase differential is converted to a voltage value and output from the FSCO pin (pin 10). A 4fsc signal that is synchronized with the external fsc signal is generated by varying the varactor diode capacitance according to this voltage.

Selecting this mode reduces the crystal oscillator and enables the installation area and cost to be reduced.

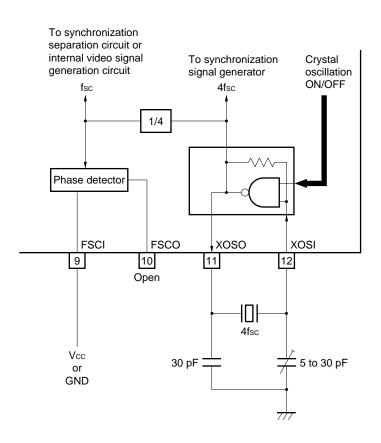

#### (2) When 4fsc crystal oscillation is selected

Connect a crystal resonator (frequency: 4fsc) between the XOSO pin (pin 11) and XOSI pin (pin 12) and connect a capacitor (approx. 30 pF) between the XOSO pin (pin 11) and ground (GND) and connect a trimmer capacitor (5 to 30 pF) between the XOSI pin (pin 12) and ground (GND) (see **Figure 3-2 Sample**  $\mu$ **PD6464A** or  $\mu$ **PD6465 Application Circuit (When 4fsc Crystal Oscillation Is Selected)**).

This crystal oscillator generates the 4fsc signal, and the fsc signal is generated by dividing this 4fsc signal into four parts.

Figure 2-6. Quadruple/4fsc Crystal Oscillation Circuit

#### (a) When quadruple oscillation is selected

#### (b) When 4fsc crystal oscillation is selected

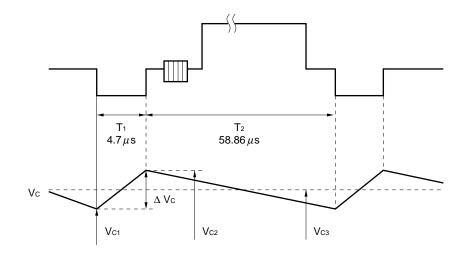

#### 2.2.2 Synchronization separation circuit

When external video signal mode is selected, the synchronization separation circuit uses the fsc signal generated by the quadruple/4fsc crystal oscillation circuit to separate the horizontal synchronization signal (Hsync) and vertical synchronization signal (Vsync) from the composite synchronization signal (Csync).

The vertical synchronization signal sampling circuit uses the fsc signal to sample Vsync from Csync by counting down when Csync is high and counting up when it is low.

Also, the horizontal synchronization signal sampling circuit can prevent synchronization signals from being omitted or noise from being generated due to invalid signals because it contains an on-chip horizontal synchronization signal correction (Hsync autogeneration) circuit.

When internal video signal mode is selected, Vsync and Hsync are generated by the synchronization signal generator by using the 4fsc signal generated by the quadruple/4fsc crystal oscillation circuit section.

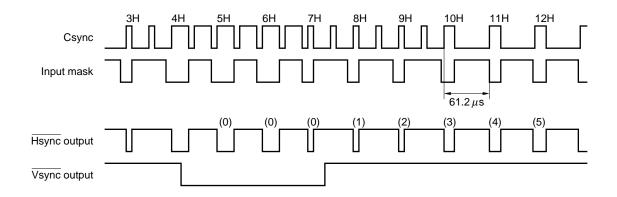

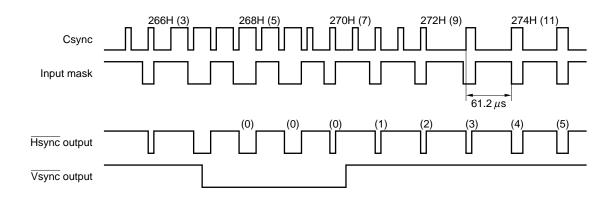

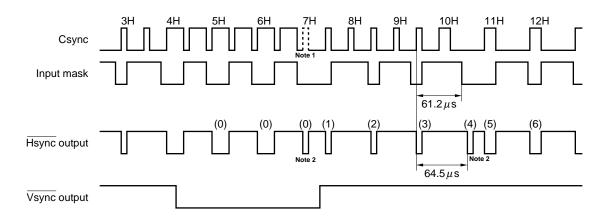

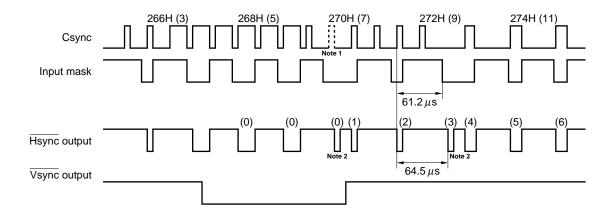

The operation of the horizontal synchronization signal correction (Hsync autogeneration) circuit is outlined below (see **Figure 2-8** for sample timing charts).

#### (1) Hsync width

The  $\mu$ PD6464A recognizes a signal of at least 0.2  $\mu$ sec as  $\overline{\text{Hsync}}$ , and the  $\mu$ PD6465 recognizes a signal of at least 0.8  $\mu$ sec. Signals having smaller widths are ignored.

#### (2) Hsync cycle

No external signal can be sampled for an interval of 61.2  $\mu$ sec after  $\overline{\text{Hsync}}$  is sampled.

#### (3) Hsync autogeneration

The  $\overline{\text{Hsync}}$  cycle is monitored, and if no external  $\overline{\text{Hsync}}$  is input in a 61.2 to 64.5  $\mu$ sec interval after  $\overline{\text{Hsync}}$  is sampled, a pseudo  $\overline{\text{Hsync}}$  is autogenerated and output. The sampling of signals is not inhibited after the autogeneration of the pseudo  $\overline{\text{Hsync}}$ . The external signal that is input next is treated as  $\overline{\text{Hsync}}$  to accelerate the move back to the regular  $\overline{\text{Hsync}}$  (If the sampling of signals were inhibited after the autogeneration of the pseudo  $\overline{\text{Hsync}}$ , the auto-generation interval would continue, resulting in a loss of synchronization between the external  $\overline{\text{Hsync}}$  and the  $\overline{\text{Hsync}}$  used for display inside the OSD LSI).

According to the operation described above, the pseudo Hsync is output even if no external Csync is input. However, no pseudo Vsync is autogenerated.

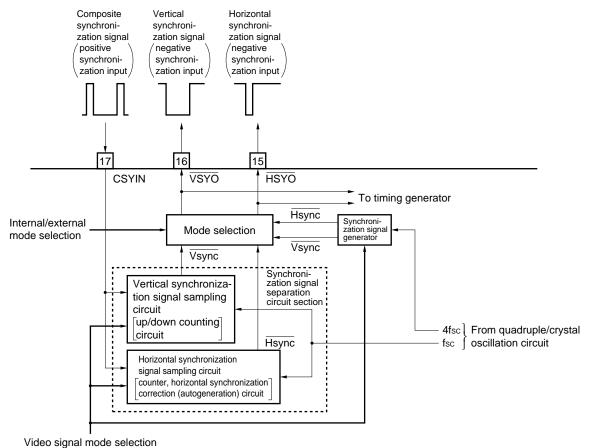

Figure 2-7. Synchronization Separation Circuit Section

Figure 2-8. Sample Horizontal Synchronization Signal Correction Circuit Timing Charts (1/3)

#### (a) When regular signals are input

#### Odd fields

#### Even fields

**Remark** The numbers enclosed in parentheses are vertical display counter values within the  $\mu$ PD6464A or  $\mu$ PD6465.

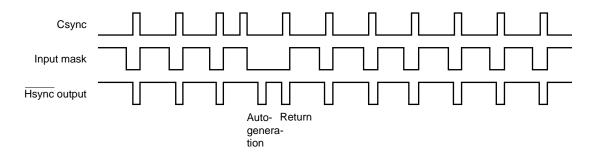

Figure 2-8. Sample Horizontal Synchronization Signal Correction Circuit Timing Charts (2/3)

## (b) Hsync autogeneration example

## Odd fields

#### Even fields

- Notes 1. Indicates that one pulse within the Csync signal is missing.

- 2. This is an autogenerated  $\overline{\text{Hsync}}$  signal within the  $\mu\text{PD6464A}$  or  $\mu\text{PD6465}$ .

**Remark** The numbers enclosed in parentheses are vertical display counter values within the  $\mu$ PD6464A or  $\mu$ PD6465.

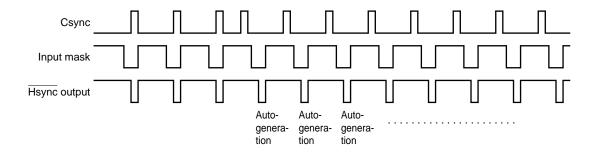

Figure 2-8. Sample Horizontal Synchronization Signal Correction Circuit Timing Charts (3/3)

## (c) Change in Hsync output due to input mask after autogeneration

When no masking is performed after autogeneration

when masking is performed after autogeneration

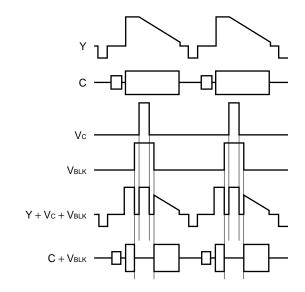

#### 2.2.3 Video signal output section

The video signal output section mixes character information with a video signal input from an external source or with an internally generated video signal and outputs the mixed signal.

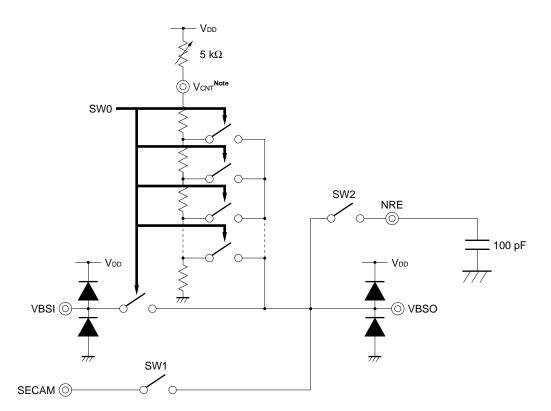

With the  $\mu$ PD6464A or  $\mu$ PD6465, set the VCNT pin voltage to 2.5 V to use the internal/external video signal amplitude level at 1 V<sub>P-P</sub>, and set the VCNT pin voltage to 5 V to use it at 2 V<sub>P-P</sub>. In addition, the corresponding sync-chip level and pedestal level of the composite video signal input from an external source must match the internal video signal level (see **Table 2-1**). If the video signal amplitude level, sync-chip level, and pedestal level are not matched with the internal/external video signal, the character levels will differ in external video signal mode and internal video signal mode.

For details about the adjustment method, refer to the data sheet.

Figure 2-9. Video Signal Output Section Equivalent Circuit

**Note** Set the VCNT pin voltage to 5 V when the internal video signal amplitude level is 2 V<sub>p-p</sub>, and set the voltage to 2.5 V when the amplitude level is 1 V<sub>p-p</sub>.

**Remark** The switch operations are as follows.

SW0: Controlled by the output control section according to the character/background level, color burst/color phase (for internal video signal mode), etc.