S/UNI®-JET Data Sheet Released

# PM7347

# S/UNI®-JET

# SATURN® USER NETWORK INTERFACE for J2/E3/T3

# **Data Sheet**

### Released

Issue 3: June 2001

# Legal Information

### Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

PMC-1990267 (R3)

#### Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

### Trademarks

S/UNI and SATURN are registerd trademarks of PMC-Sierra, Inc. SCI-PHY is a trademark of PMC-Sierra, Inc.

# **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000 Fax: (604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: <u>http://www.pmc-sierra.com</u>

# **Revision History**

| Issue No. | Issue Date | Details of Change                                                                                                                                                                                        |

|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3         | June 2001  | Included Application examples, Description, and Functional Description,<br>Functional Timing, Microprocessor Timing, and A.C. Timing sections.<br>Completed Normal Mode Register and Operation sections. |

|           |            | Changed all read-only "Reserved" bits to "Unused".                                                                                                                                                       |

|           |            | Changed IDDOP values.                                                                                                                                                                                    |

|           |            | Changed Thermal "Case" temperature to "Ambient", Section 11.                                                                                                                                             |

|           |            | Divided Pin Diagram into quadrants for readability.                                                                                                                                                      |

| 2         | March 2000 | Preliminary label removed.                                                                                                                                                                               |

|           |            | S/UNI-JET errata added.                                                                                                                                                                                  |

| 1         | April 1999 | Document created.                                                                                                                                                                                        |

# **Table of Contents**

| 1  | Feat  | ures                                           | . 17 |

|----|-------|------------------------------------------------|------|

| 2  | Appl  | ications                                       | .21  |

| 3  | Refe  | rences                                         | .22  |

| 4  | Defir | nitions                                        | .24  |

| 5  | Appl  | ication Examples                               | .26  |

| 6  | Bloc  | k Diagram                                      | .28  |

| 7  | Desc  | cription                                       | .29  |

| 8  | Pin [ | Diagram                                        | .32  |

| 9  | Pin [ | Description                                    | .34  |

| 10 | Fund  | stional Description                            | .54  |

|    | 10.1  | DS3 Framer                                     | .54  |

|    | 10.2  | E3 Framer                                      | .56  |

|    | 10.3  | J2 Framer                                      | .58  |

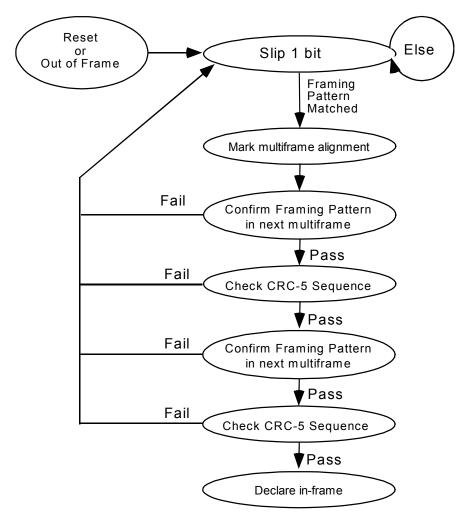

|    |       | 10.3.1 J2 Frame Find Algorithms                | .59  |

|    | 10.4  | RBOC Bit-Oriented Code Detector                | .62  |

|    | 10.5  | RDLC PMDL Receiver                             | .62  |

|    | 10.6  | PMON Performance Monitor Accumulator           | .63  |

|    | 10.7  | SPLR PLCP Layer Receiver                       | .63  |

|    | 10.8  | ATMF ATM Cell Delineator                       | .64  |

|    |       | PRGD Pseudo-Random Sequence Generator/Detector |      |

|    |       | RXCP-50 Receive Cell Processor                 |      |

|    | 10.11 | RXFF Receive FIFO                              | .68  |

|    | 10.12 | CPPM Cell and PLCP Performance Monitor         | .69  |

|    | 10.13 | DS3 Transmitter                                | .69  |

|    | 10.14 | E3 Transmitter                                 | .70  |

|    | 10.15 | J2 Transmitter                                 | .71  |

|    | 10.16 | XBOC Bit Oriented Code Generator               | .72  |

|    | 10.17 | TDPR PMDL Transmitter                          | .72  |

|    | 10.18 | SPLT SMDS PLCP Layer Transmitter               | .73  |

|    |       | TXCP-50 Transmit Cell Processor                |      |

|    | 10.20 | TXFF Transmit FIFO                             | .74  |

|    | 10.21 | TTB Trail Trace Buffer                         | .75  |

|    | 10.22 | JTAG Test Access Port                          | .75  |

|     | 10.23 Microprocessor Interface                       | 76  |  |

|-----|------------------------------------------------------|-----|--|

| 11  | 1 Normal Mode Register Description                   |     |  |

| 12  | 2 Test Features Description                          |     |  |

|     | 12.1 Test Mode 0 Details                             | 251 |  |

|     | 12.2 JTAG Test Port                                  | 255 |  |

| 13  | Operation                                            | 259 |  |

|     | 13.1 Software Initialization Sequence                | 259 |  |

|     | 13.2 Register Settings for Basic Configurations      |     |  |

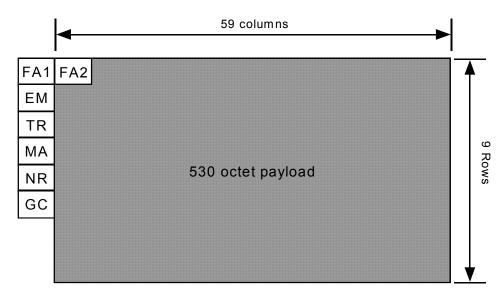

|     | 13.3 PLCP Frame Formats                              | 261 |  |

|     | 13.3.1 PLCP Path Overhead Octet Processing           | 264 |  |

|     | 13.4 DS3 Frame Format                                |     |  |

|     | 13.5 G.751 E3 Frame Format                           | 269 |  |

|     | 13.6 G.832 E3 Frame Format                           | 270 |  |

|     | 13.7 J2 Frame Format                                 | 271 |  |

|     | 13.8 S/UNI-JET Cell Data Structure                   | 273 |  |

|     | 13.9 Resetting the RXFF and TXFF FIFOs               | 277 |  |

|     | 13.10 Servicing Interrupts                           | 277 |  |

|     | 13.11 Using the Performance Monitoring Features      | 277 |  |

|     | 13.12 Using the Internal PMDL Transmitter            | 278 |  |

|     | 13.12.1 Interrupt Driven Mode                        | 279 |  |

|     | 13.12.2 TDPR Interrupt Routine                       |     |  |

|     | 13.13 Using the Internal Data Link Receiver          | 281 |  |

|     | 13.14 PRGD Pattern Generation                        | 285 |  |

|     | 13.14.1 Generating and detecting repetitive patterns | 286 |  |

|     | 13.14.2 Common Test Patterns                         | 286 |  |

|     | 13.15 JTAG Support                                   |     |  |

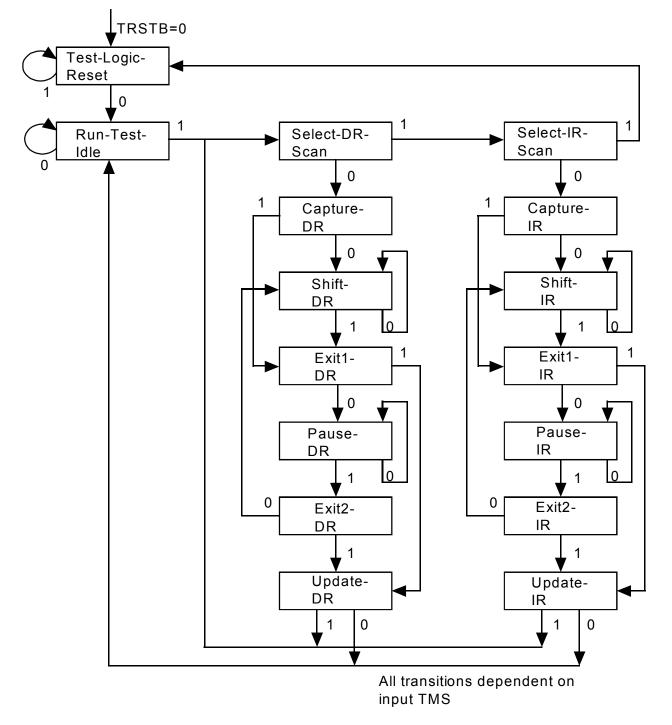

|     | 13.15.1 TAP Controller                               | 289 |  |

| 14  | Functional Timing                                    | 295 |  |

| 15  | Absolute Maximum Ratings                             | 319 |  |

| 16  | D.C. Characteristics                                 | 320 |  |

| 17  | Microprocessor Interface Timing Characteristics      | 322 |  |

| 18  | A.C. Timing Characteristics                          | 325 |  |

| 19  | Ordering and Thermal Information                     |     |  |

| 20  | Mechanical Information                               | 340 |  |

| Not | tes                                                  | 341 |  |

# List of Registers

| Register 300H: S/UNI-JET Configuration 1                                         | 82  |

|----------------------------------------------------------------------------------|-----|

| Register 301H: S/UNI-JET Configuration 2                                         | 85  |

| Register 302H: S/UNI-JET Transmit Configuration                                  | 87  |

| Register 303H: S/UNI-JET Receive Configuration                                   | 89  |

| Register 304H: S/UNI-JET Data Link and FERF/RAI Control                          | 91  |

| Register 305H: S/UNI-JET Interrupt Status                                        | 95  |

| Register 006H: S/UNI-JET Identification, Master Reset, and Global Monitor Update |     |

| Register 307H: S/UNI-JET Clock Activity Monitor and Interrupt Identification     | 97  |

| Register 308H: SPLR Configuration                                                | 98  |

| Register 309H: SPLR Interrupt Enable                                             |     |

| Register 30AH: SPLR Interrupt Status                                             |     |

| Register 30BH: SPLR Status                                                       | 104 |

| Register 30CH: SPLT Configuration                                                |     |

| Register 30DH: SPLT Control                                                      |     |

| Register 30EH: SPLT Diagnostics and G1 Octet                                     | 111 |

| Register 30FH: SPLT F1 Octet                                                     | 113 |

| Register 310H: Change of PMON Performance Meters                                 | 114 |

| Register 311H: PMON Interrupt Enable/Status                                      | 115 |

| Register 314H: PMON LCV Event Count LSB                                          | 116 |

| Register 315H: PMON LCV Event Count MSB                                          | 116 |

| Register 316H: PMON Framing Bit Error Event Count LSB                            | 117 |

| 317H: PMON Framing Bit Error Event Count MSB                                     | 117 |

| Register 318H: PMON Excessive Zero Count LSB                                     | 118 |

| Register 319H: PMON Excessive Zero Count MSB                                     | 118 |

| Register 31AH: PMON Parity Error Event Count LSB                                 | 119 |

| Register 31BH: PMON Parity Error Event Count MSB                                 | 119 |

| Register 31CH: PMON Path Parity Error Event Count LSB                            | 120 |

| Register 31DH: PMON Path Parity Error Event Count MSB                            | 120 |

| Register 31EH: PMON FEBE/J2-EXZS Event Count LSB                                 | 121 |

| Register 31FH: PMON FEBE/J2-EXZS Event Count MSB                                 | 121 |

| Register 321H: CPPM Change of CPPM Performance Meters                            | 122 |

| Register 322H: CPPM B1 Error Count LSB                                           | 123 |

| Register 323H: CPPM B1 Error Count MSB                                           | 123 |

| Register 324H: CPPM Framing Error Event Count LSB              | 124 |

|----------------------------------------------------------------|-----|

| Register 325H: CPPM Framing Error Event Count MSB              | 124 |

| Register 326H: CPPM FEBE Count LSB                             | 125 |

| Register 327H: CPPM FEBE Count MSB                             | 125 |

| Register 330H: DS3 FRMR Configuration                          | 126 |

| Register 331H: DS3 FRMR Interrupt Enable (ACE=0)               | 128 |

| Register 331H: DS3 FRMR Additional Configuration Register      | 130 |

| Register 332H: DS3 FRMR Interrupt Status                       | 133 |

| Register 333H: DS3 FRMR Status                                 | 135 |

| Register 334H: DS3 TRAN Configuration                          | 137 |

| Register 335H: DS3 TRAN Diagnostic                             | 139 |

| Register 338H: E3 FRMR Framing Options                         | 141 |

| Register 339H: E3 FRMR Maintenance Options                     | 143 |

| Register 33AH: E3 FRMR Framing Interrupt Enable                | 145 |

| Register 33BH: E3 FRMR Framing Interrupt Indication and Status | 146 |

| Register 33CH: E3 FRMR Maintenance Event Interrupt Enable      | 148 |

| Register 33DH: E3 FRMR Maintenance Event Interrupt Indication  | 150 |

| Register 33EH: E3 FRMR Maintenance Event Status                | 152 |

| Register 340H: E3 TRAN Framing Options                         | 154 |

| Register 341H: E3 TRAN Status and Diagnostic Options           | 155 |

| Register 342H: E3 TRAN BIP-8 Error Mask                        | 157 |

| Register 343H: E3 TRAN Maintenance and Adaptation Options      | 158 |

| Register 344H: J2-FRMR Configuration                           | 160 |

| Register 345H: J2-FRMR Status                                  | 162 |

| Register 346H: J2-FRMR Alarm Interrupt Enable                  | 163 |

| Register 347H: J2-FRMR Alarm Interrupt Status                  | 165 |

| Register 348H: J2-FRMR Error/Xbit Interrupt Enable             | 167 |

| Register 349H: J2-FRMR Error/Xbit Interrupt Status             | 169 |

| Register 34CH: J2-TRAN Configuration                           | 171 |

| Register 34DH: J2-TRAN Diagnostic                              | 172 |

| Register 34EH: J2-TRAN TS97 Signaling                          | 173 |

| Register 34FH: J2-TRAN TS98 Signaling                          | 174 |

| Register 350H: RDLC Configuration                              | 175 |

| Register 351H: RDLC Interrupt Control                          | 177 |

| Register 352H: RDLC Status                                     | 178 |

|                                                                |     |

| Register 353H: RDLC Data                                    | . 180 |

|-------------------------------------------------------------|-------|

| Register 354H: RDLC Primary Address Match                   | . 181 |

| Register 355H: RDLC Secondary Address Match                 | . 182 |

| Register 358H: TDPR Configuration                           | . 183 |

| Register 359H: TDPR Upper Transmit Threshold                | . 185 |

| Register 35AH: TDPR Lower Interrupt Threshold               | . 186 |

| Register 35BH: TDPR Interrupt Enable                        | . 187 |

| Register 35CH: TDPR Interrupt Status/UDR Clear              | . 188 |

| Register 35DH: TDPR Transmit Data                           | . 190 |

| Register 360H: RXCP-50 Configuration 1                      | . 191 |

| Register 361H: RXCP-50 Configuration 2                      | . 193 |

| Register 362H: RXCP-50 FIFO/UTOPIA Control & Configuration  | . 195 |

| Register 363H: RXCP-50 Interrupt Enables and Counter Status | . 197 |

| Register 364H: RXCP-50 Status/Interrupt Status              | . 199 |

| Register 365H: RXCP-50 LCD Count Threshold (MSB)            | .201  |

| Register 366H: RXCP-50 LCD Count Threshold (LSB)            | .201  |

| Register 367H: RXCP-50 Idle Cell Header Pattern             | .203  |

| Register 368H: RXCP-50 Idle Cell Header Mask                | 204   |

| Register 369H: RXCP-50 Corrected HCS Error Count            | .205  |

| Register 36AH: RXCP-50 Uncorrected HCS Error Count          | . 206 |

| Register 36BH: RXCP-50 Receive Cell Counter (LSB)           | . 207 |

| Register 36CH: RXCP-50 Receive Cell Counter                 | 207   |

| Register 36DH: RXCP-50 Receive Cell Counter (MSB)           | .208  |

| Register 36EH: RXCP-50 Idle Cell Counter (LSB)              | .209  |

| Register 36FH: RXCP-50 Idle Cell Counter                    | .209  |

| Register 370H: RXCP-50 Idle Cell Counter (MSB)              | .210  |

| Register 380H: TXCP-50 Configuration 1                      | . 211 |

| Register 381H: TXCP-50 Configuration 2                      | .213  |

| Register 382H: TXCP-50 Cell Count Status                    | .215  |

| Register 383H: TXCP-50 Interrupt Enable/Status              | .216  |

| Register 384H: TXCP-50 Idle Cell Header Control             | .218  |

| Register 385H: TXCP-50 Idle Cell Payload Control            | 219   |

| Register 386H: TXCP-50 Transmit Cell Count (LSB)            | 220   |

| Register 387H: TXCP-50 Transmit Cell Count                  | 220   |

| Register 388H: TXCP-50 Transmit Cell Count (MSB)            | 221   |

|                                                             |       |

| Register 390H: TTB Control                           | .222 |

|------------------------------------------------------|------|

| Register 391H: TTB Trail Trace Identifier Status     | .224 |

| Register 392H: TTB Indirect Address                  | .225 |

| Register 393H: TTB Indirect Data                     | .226 |

| Register 394H: TTB Expected Payload Type Label       | .227 |

| Register 395H: TTB Payload Type Label Control/Status | .228 |

| Register 398H: RBOC Configuration/Interrupt Enable   | .230 |

| Register 399H: RBOC Interrupt Status                 | .231 |

| Register 39AH: XBOC Code                             |      |

| Register 39BH: S/UNI-JET Miscellaneous               | .233 |

| Register 39CH: S/UNI-JET FRMR LOF Status.            | .235 |

| Register 3A0H: PRGD Control                          | .237 |

| Register 3A1H: PRGD Interrupt Enable/Status          | .239 |

| Register 3A2H: PRGD Length                           |      |

| Register 3A3H: PRGD Tap                              | .242 |

| Register 3A4H: PRGD Error Insertion Register         | .243 |

| Register 3A8H: Pattern Insertion #1                  | .244 |

| Register 3A9H: Pattern Insertion #2                  | .244 |

| Register 3AAH: Pattern Insertion #3                  | .245 |

| Register 3ABH: Pattern Insertion #4                  | .245 |

| Register 3ACH: PRGD Pattern Detector #1              | .246 |

| Register 3ADH: PRGD Pattern Detector #2              | .246 |

| Register 3AEH: PRGD Pattern Detector #3              | .247 |

| Register 3AFH: PRGD Pattern Detector #4              | .247 |

| Register 40CH: S/UNI-JET Identification Register     | .248 |

# List of Figures

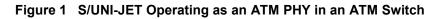

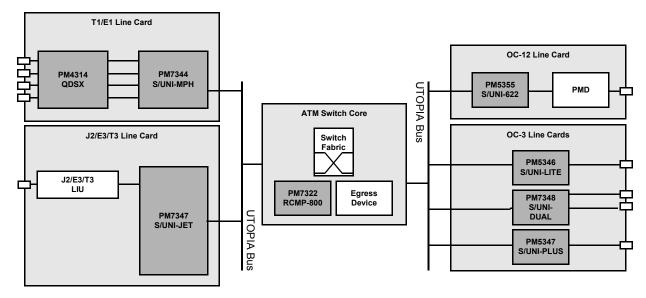

| Figure 1  | S/UNI-JET Operating as an ATM PHY in an ATM Switch              | 26  |

|-----------|-----------------------------------------------------------------|-----|

| Figure 2  | S/UNI-JET Operating as a Framer Device in Frame Relay Equipment | 27  |

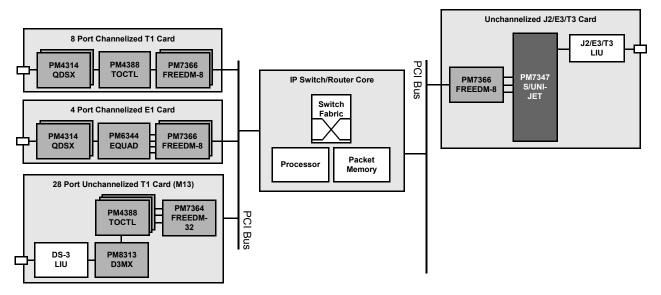

| Figure 3  | Block Diagram                                                   | 28  |

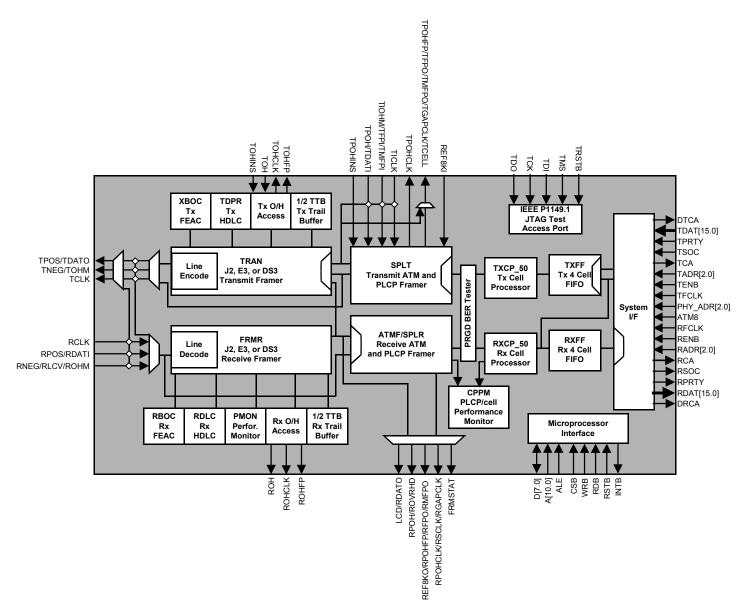

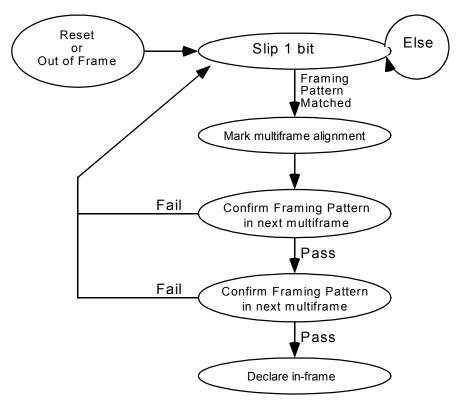

| Figure 4  | Framing algorithm (CRC_REFR = 0)                                | 60  |

| Figure 5  | Framing Algorithm (CRC_REFR = 1)                                | 61  |

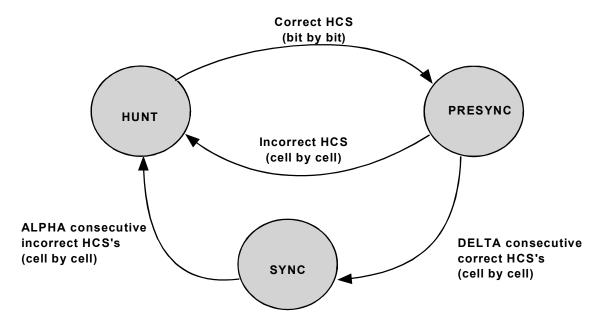

| Figure 6  | Cell delineation State Diagram                                  | 65  |

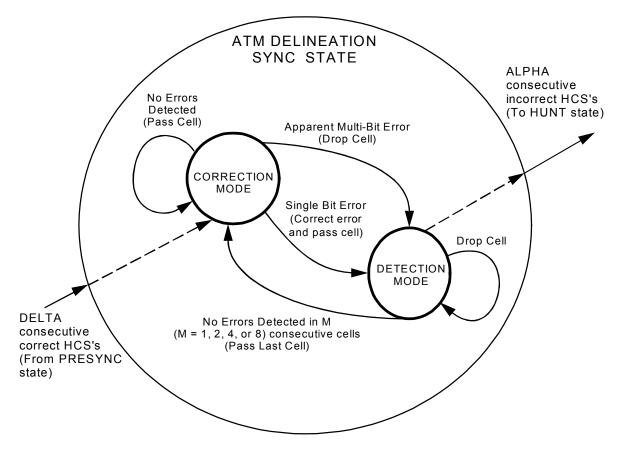

| Figure 7  | HCS Verification State Diagram                                  | 68  |

| Figure 8  | DS3 PLCP Frame Format                                           | 262 |

| Figure 9  | DS1 PLCP Frame Format                                           | 262 |

| Figure 10 | G.751 E3 PLCP Frame Format                                      | 263 |

| Figure 11 | E1 PLCP Frame Format                                            | 264 |

| Figure 12 | DS3 Frame Structure                                             | 267 |

| Figure 13 | G.751 E3 Frame Structure                                        | 269 |

| Figure 14 | G.832 E3 Frame Structure                                        | 270 |

| Figure 15 | J2 Frame Structure                                              | 272 |

| Figure 16 | 16-bit Wide, 26-byte Word Structure                             | 273 |

| Figure 17 | 16-bit Wide, 27-byte Word Structure                             | 274 |

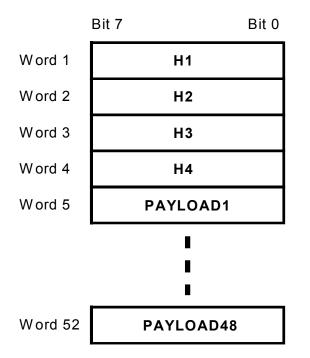

| Figure 18 | 8-bit Wide, 52-byte Word Structure                              | 275 |

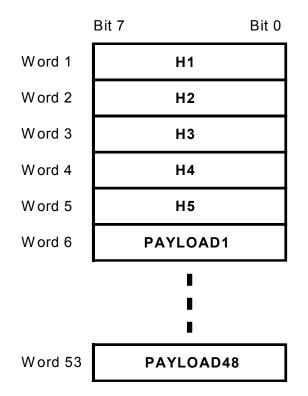

| Figure 19 | 8-bit Wide, 53-byte Word Structure                              | 276 |

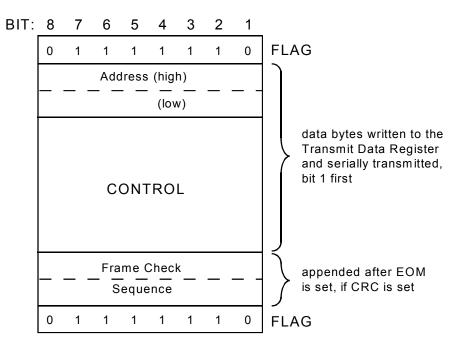

| Figure 20 | Typical Data Frame                                              | 284 |

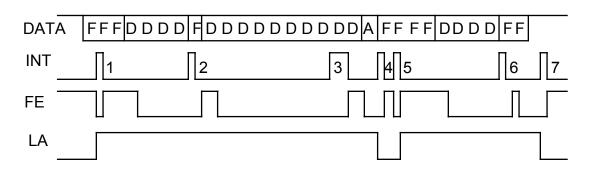

| Figure 21 | Example Multi-Packet Operational Sequence                       | 284 |

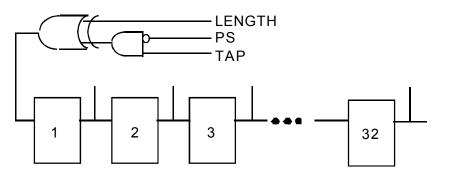

| Figure 22 | PRGD Pattern Generator                                          | 285 |

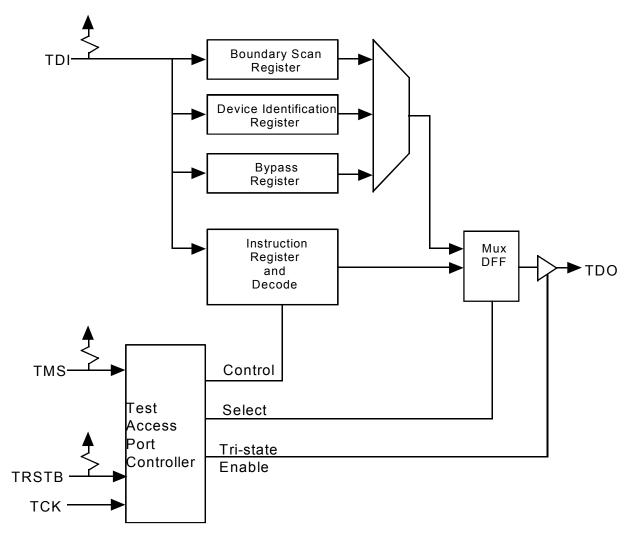

| Figure 23 | Boundary Scan Architecture                                      | 288 |

| Figure 24 | TAP Controller Finite State Machine                             | 290 |

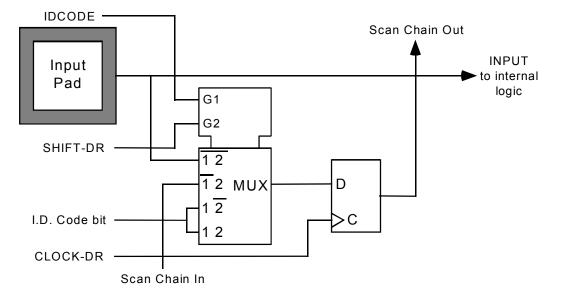

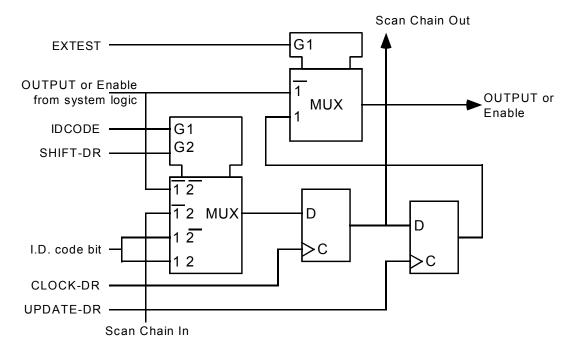

| Figure 25 | Input Observation Cell (IN_CELL)                                | 293 |

| Figure 26 | Output Cell (OUT_CELL)                                          | 293 |

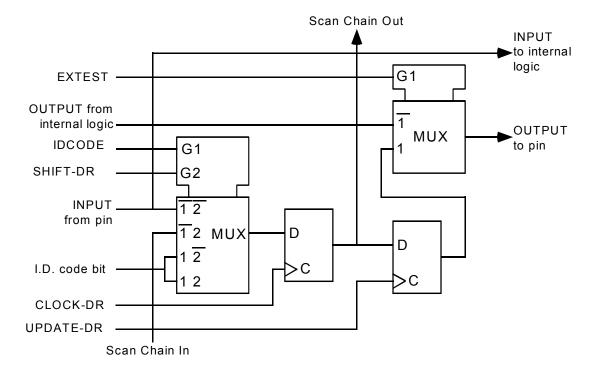

| Figure 27 | Bi-directional Cell (IO_CELL)                                   | 294 |

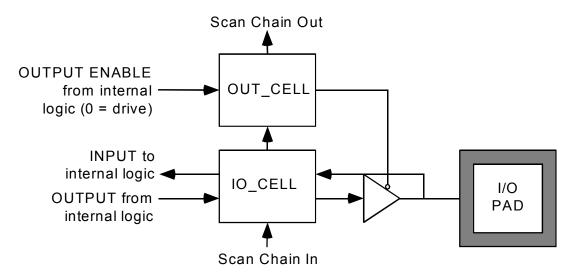

| Figure 28 | Layout of Output Enable and Bi-directional Cells                | 294 |

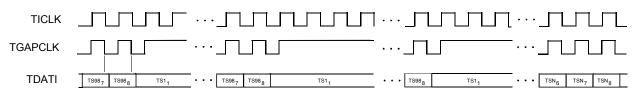

| Figure 29 | Receive DS1 Stream                                              | 295 |

| Figure 30 | Receive E1 Stream                                               | 295 |

| Figure 31 | Receive Bipolar DS3 Stream                                      | 296 |

| Figure 32 | Receive Unipolar DS3 Stream                                     | 296 |

| Figure 33 | Receive Bipolar E3 Stream                                       | 296 |

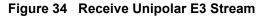

| Figure 34 | Receive Unipolar E3 Stream                              | 297 |

|-----------|---------------------------------------------------------|-----|

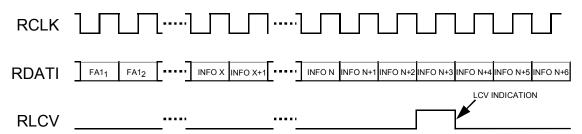

| Figure 35 | Receive Bipolar J2 Stream                               | 297 |

| Figure 36 | Receive Unipolar J2 Stream                              | 298 |

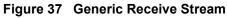

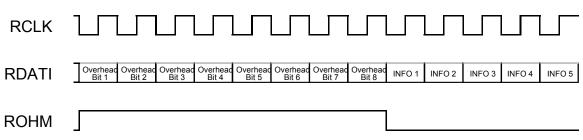

| Figure 37 | Generic Receive Stream                                  | 298 |

| Figure 38 | Receive DS3 Overhead                                    | 299 |

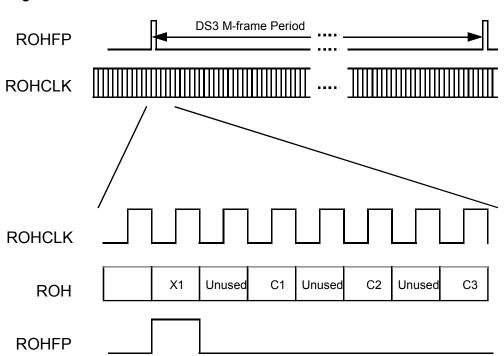

| Figure 39 | Receive G.832 E3 Overhead                               | 300 |

| Figure 40 | Receive G.751 E3 Overhead                               | 300 |

| Figure 41 | Receive J2 Overhead                                     | 301 |

| Figure 42 | Receive PLCP Overhead                                   | 301 |

| Figure 43 | Transmit DS1 Stream                                     | 302 |

| Figure 44 | Transmit E1 Stream                                      | 302 |

| Figure 45 | Transmit Bipolar DS3 Stream                             | 303 |

| Figure 46 | Transmit Unipolar DS3 Stream                            | 303 |

| Figure 47 | Transmit Bipolar E3 Stream                              | 304 |

| Figure 48 | Transmit Unipolar E3 Stream                             | 304 |

| Figure 49 | Transmit Bipolar J2 Stream                              | 305 |

| Figure 50 | Transmit Unipolar J2 Stream                             | 305 |

| Figure 51 | Generic Transmit Stream                                 | 306 |

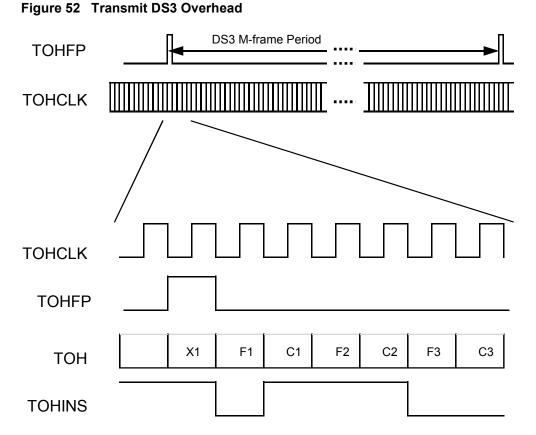

| Figure 52 | Transmit DS3 Overhead                                   | 307 |

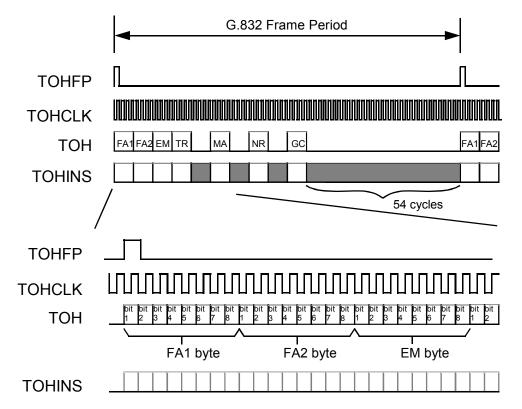

| Figure 53 | Transmit G.832 E3 Overhead                              | 308 |

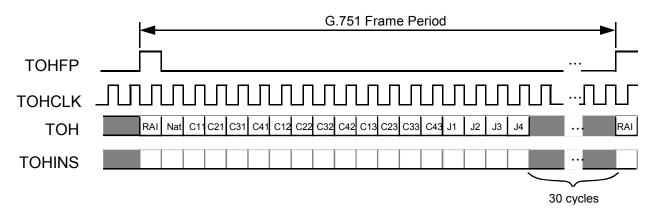

| Figure 54 | Transmit G.751 E3 Overhead                              | 309 |

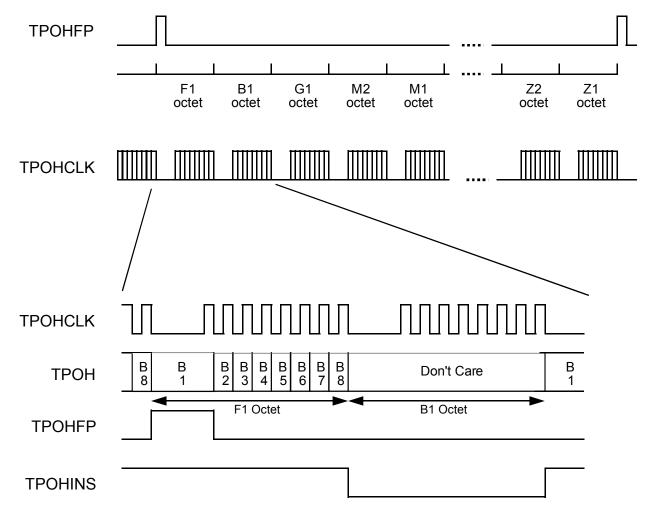

| Figure 55 | Transmit J2 Overhead                                    | 309 |

| Figure 56 | Transmit PLCP Overhead                                  | 310 |

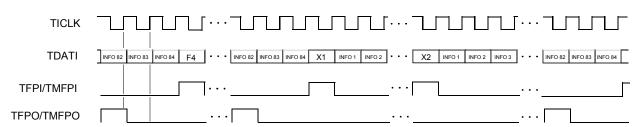

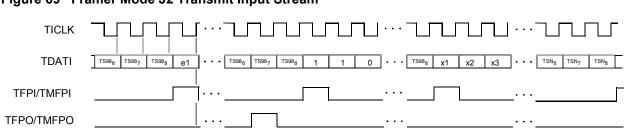

| Figure 57 | Framer Mode DS3 Transmit Input Stream                   | 311 |

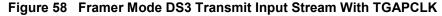

| Figure 58 | Framer Mode DS3 Transmit Input Stream With TGAPCLK      | 311 |

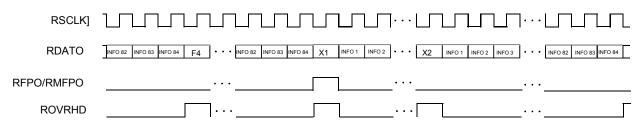

| Figure 59 | Framer Mode DS3 Receive Output Stream                   | 311 |

| Figure 60 | Framer Mode DS3 Receive Output Stream with RGAPCLK      | 312 |

| Figure 61 | Framer Mode G.751 E3 Transmit Input Stream              | 312 |

| Figure 62 | Framer Mode G.751 E3 Transmit Input Stream With TGAPCLK | 312 |

| Figure 63 | Framer Mode G.751 E3 Receive Output Stream              | 313 |

| Figure 64 | Framer Mode G.751 E3 Receive Output Stream with RGAPCLK | 313 |

| Figure 65 | Framer Mode G.832 E3 Transmit Input Stream              | 314 |

| Figure 66 | Framer Mode G.832 E3 Transmit Input Stream With TGAPCLK | 314 |

| Figure 67 | Framer Mode G.832 E3 Receive Output Stream              | 314 |

| Figure 68 | Framer Mode G.832 E3 Receive Output Stream with RGAPCLK | 314 |

|           |                                                         |     |

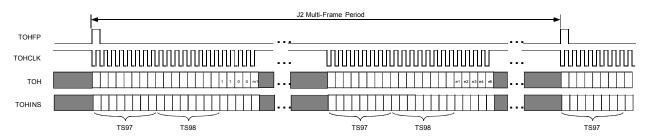

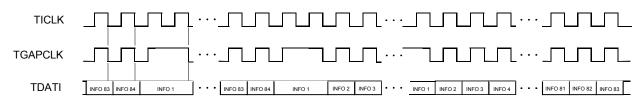

| Figure 69 | Framer Mode J2 Transmit Input Stream                     | 315 |

|-----------|----------------------------------------------------------|-----|

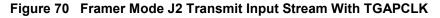

| Figure 70 | Framer Mode J2 Transmit Input Stream With TGAPCLK        | 315 |

| Figure 71 | Framer Mode J2 Receive Output Stream                     | 316 |

| Figure 72 | Framer Mode J2 Receive Output Stream with RGAPCLK        | 316 |

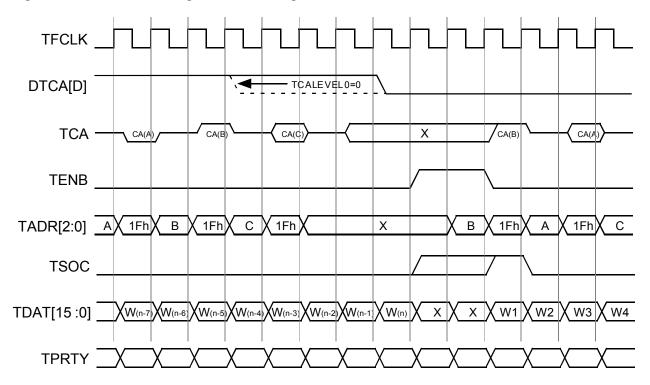

| Figure 73 | Multi-PHY Polling and Addressing Transmit Cell Interface | 317 |

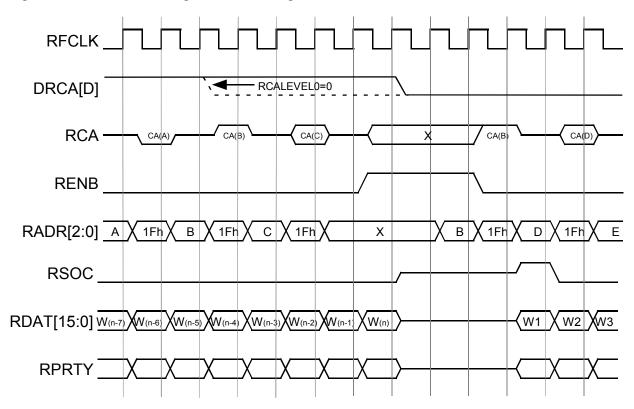

| Figure 74 | Multi-PHY Polling and Addressing Receive Cell Interface  | 318 |

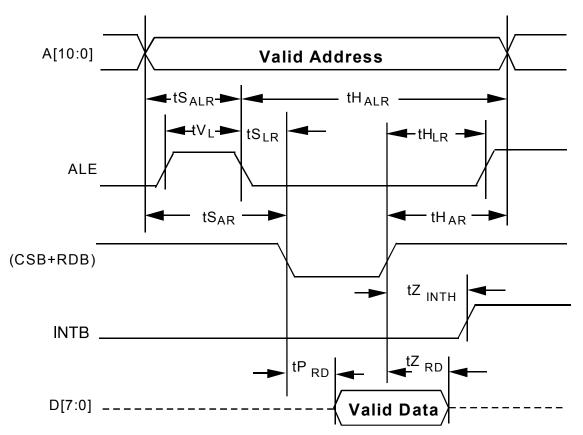

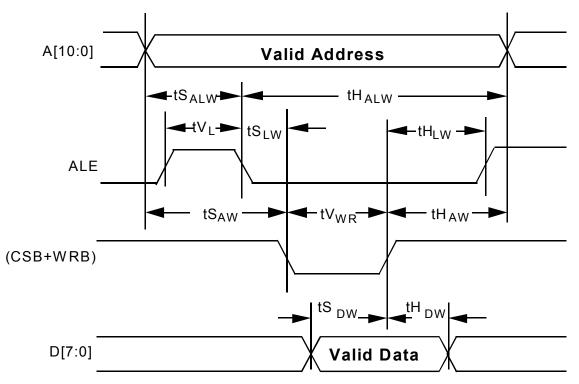

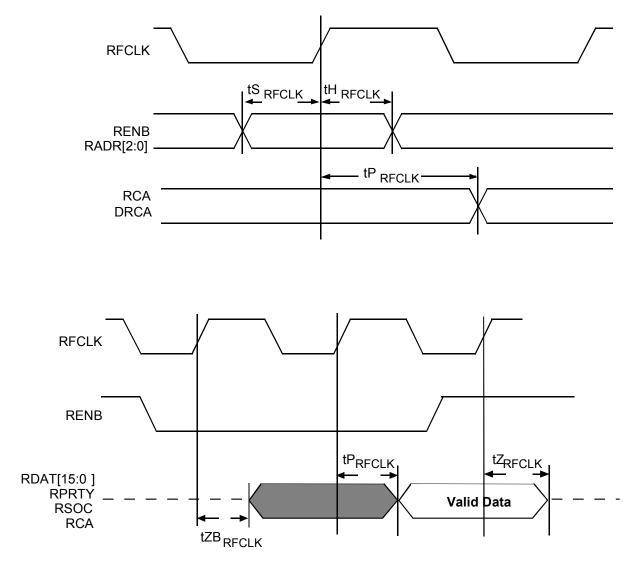

| Figure 75 | Microprocessor Interface Read Timing                     | 322 |

| Figure 76 | Microprocessor Interface Write Timing                    | 324 |

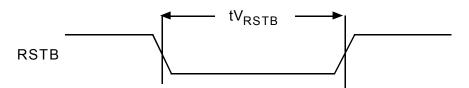

| Figure 77 | RSTB Timing                                              | 325 |

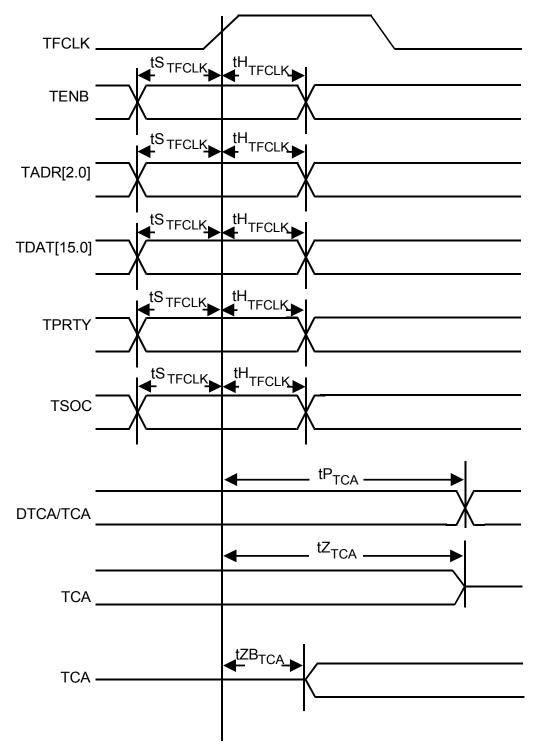

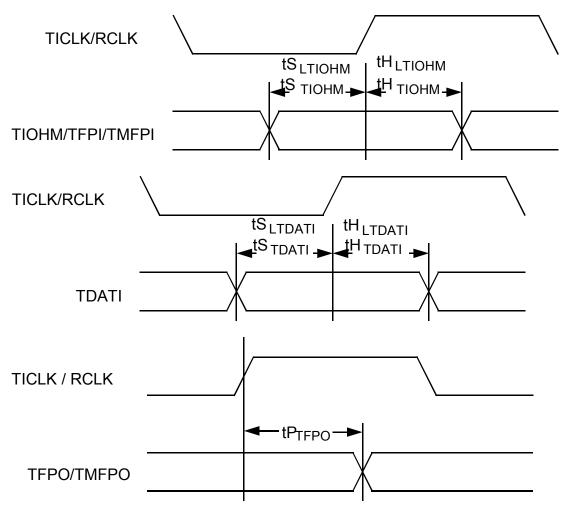

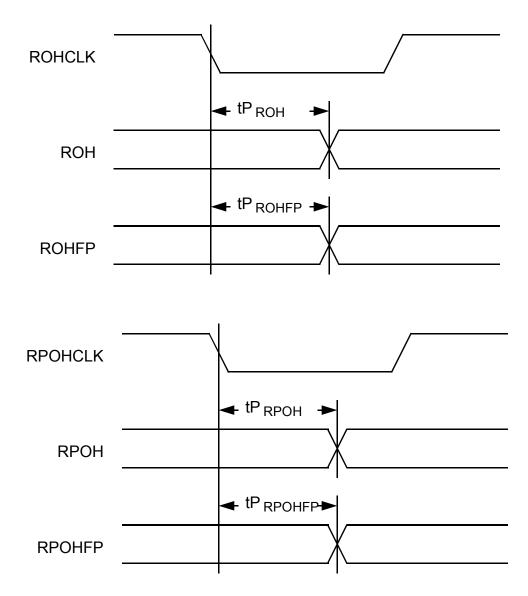

| Figure 78 | Transmit ATM Cell Interface Timing                       | 326 |

| Figure 79 | Receive ATM Cell Interface Timing                        | 328 |

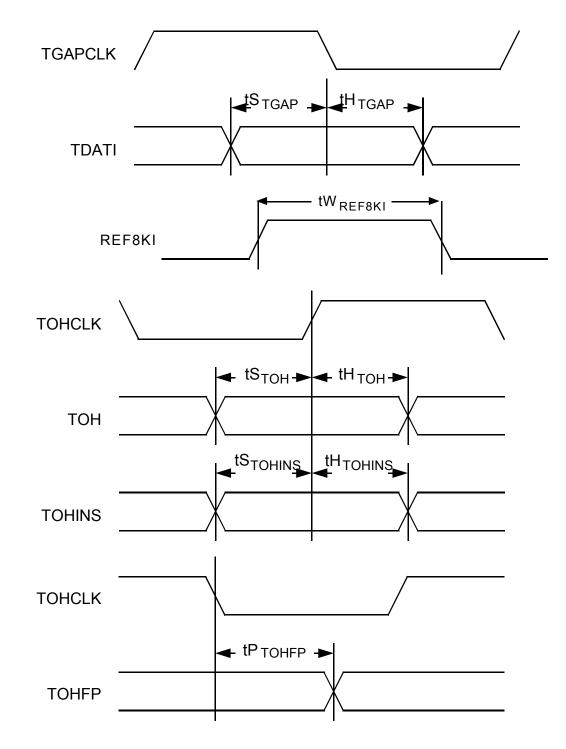

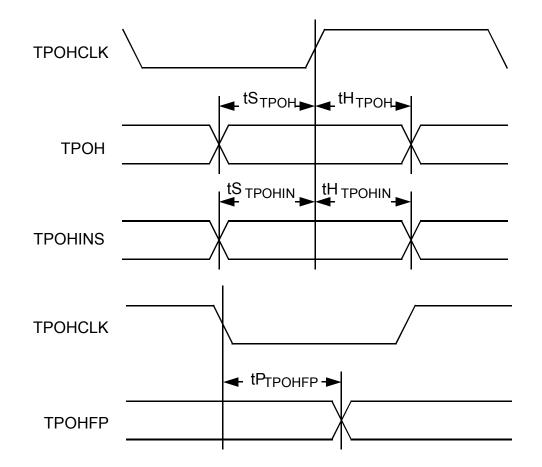

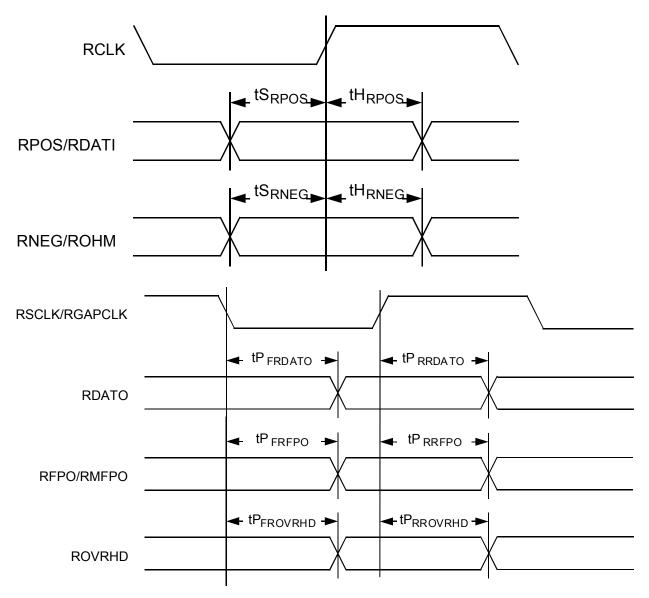

| Figure 80 | Transmit Interface Timing                                | 330 |

| Figure 81 | Receive Interface Timing                                 | 335 |

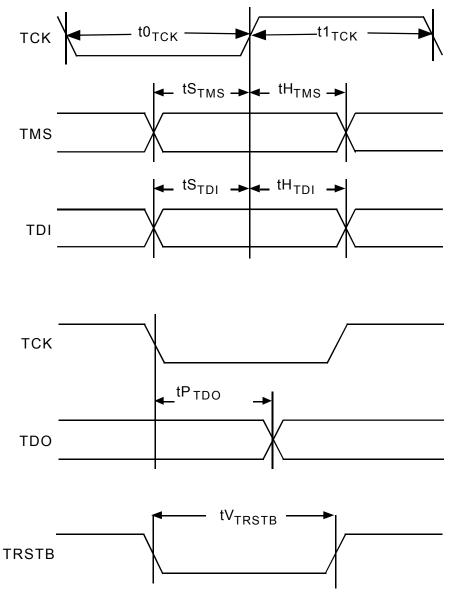

| Figure 82 | JTAG Port Interface Timing                               | 337 |

# **List of Tables**

| Table 1  | Supported Operating Formats                                   | 17  |

|----------|---------------------------------------------------------------|-----|

| Table 2  | Transmission System Sublayer Processing Acceptance and Output | 29  |

| Table 3  | Summary of Receive Detection Features                         | 29  |

| Table 4  | Multiframe Format                                             | 58  |

| Table 5  | C1 Octet Pattern                                              | 74  |

| Table 6  | Register Memory Map                                           | 76  |

| Table 7  | STATSEL[2:0] Options                                          | 86  |

| Table 8  | TFRM[1:0] Transmit Frame Structure Configurations             | 88  |

| Table 9  | LOF[1:0] Integration Period Configuration                     | 90  |

| Table 10 | RFRM[1:0] Receive Frame Structure Configurations              | 90  |

| Table 11 | SPLR FORM[1:0] Configurations                                 | 99  |

| Table 12 | PLCP LOF Declaration/Removal Times                            | 104 |

| Table 13 | SPLT FORM[1:0] Configurations                                 | 107 |

| Table 14 | DS3 FRMR EXZS/LCV Count Configurations                        | 131 |

| Table 15 | DS3 FRMR AIS Configurations                                   | 132 |

| Table 16 | E3 FRMR FORMAT[1:0] Configurations                            | 141 |

| Table 17 | E3 TRAN FORMAT[1:0] Configurations                            | 154 |

| Table 18 | J2 FRMR LOS Threshold Configurations                          | 161 |

| Table 19 | RDLC PBS[2:0] Data Status                                     | 178 |

| Table 20 | RXCP-50 HCS Filtering Configurations                          | 193 |

| Table 21 | RXCP-50 Cell Delineation Algorithm Base                       | 193 |

| Table 22 | RXCP-50 LCD Integration Periods                               | 201 |

| Table 23 | TXCP-50 FIFO Depth Configurations                             | 213 |

| Table 24 | TTB Payload Type Match Configurations                         | 227 |

| Table 25 | PRGD Pattern Detector Register Configuration                  | 237 |

| Table 26 | PRGD Generated Bit Error Rate Configurations                  | 243 |

| Table 27 | Test Mode Register Memory Map                                 | 249 |

| Table 28 | Test Mode 0 Input Read Address Locations                      | 251 |

| Table 29 | Test Mode 0 Output Write Address Locations                    | 253 |

| Table 30 | Instruction Register                                          | 255 |

| Table 31 | Identification Register                                       | 256 |

| Table 32 | Boundary Scan Register                                        | 256 |

| Table 33 | Register Settings for Basic Configurations                    | 260 |

| Table 34 | PLCP Overhead Processing                          | 264 |

|----------|---------------------------------------------------|-----|

| Table 35 | PLCP Path Overhead Identifier Codes               | 266 |

| Table 36 | DS3 PLCP Trailer Length                           | 266 |

| Table 37 | E3 PLCP Trailer Length                            | 267 |

| Table 38 | DS3 Frame Overhead Operation                      | 268 |

| Table 39 | G.751 E3 Frame Overhead Operation                 | 269 |

| Table 40 | G.832 E3 Frame Overhead Operation                 | 270 |

| Table 41 | J2 Frame Overhead Operation                       | 272 |

| Table 42 | Pseudo Random Pattern Generation (PS bit = 0)     | 286 |

| Table 43 | Repetitive Pattern Generation (PS bit = 1)        | 287 |

| Table 44 | DS3 Receive Overhead Bits                         | 299 |

| Table 45 | DS3 Transmit Overhead Bits                        | 307 |

| Table 46 | Absolute Maximum Ratings                          | 319 |

| Table 47 | DC Characteristics                                | 320 |

| Table 48 | Microprocessor Interface Read Access (Figure 75)  | 322 |

| Table 49 | Microprocessor Interface Write Access (Figure 76) | 323 |

| Table 50 | RSTB Timing (Figure 77)                           | 325 |

| Table 51 | Transmit ATM Cell Interface Timing (Figure 78)    | 325 |

| Table 52 | Receive ATM Cell Interface Timing (Figure 79)     | 327 |

| Table 53 | Transmit Interface Timing (Figure 80)             | 329 |

| Table 54 | Receive Interface Timing (Figure 81)              | 334 |

| Table 55 | JTAG Port Interface (Refer to Figure 82)          | 336 |

| Table 56 | Packaging Information                             | 339 |

| Table 57 | Thermal Information                               | 339 |

### 1 Features

The S/UNI®-JET is a single chip Asynchronous Transfer Mode (ATM) User Network Interface (UNI) operating at 44.736 Mbit/s, 34.368 Mbit/s, and 6.312 Mbit/s that:

- Conforms to AF-Physical (PHY)-0054.000, AF-PHY-0034.000 and AF-PHY-0029.000.

- Implements ATM Direct Cell Mapping into DS1, DS3, E1, E3, and J2 transmission systems according to ITU-T Recommendation G.804.

- Provides a UTOPIA Level 2 compatible ATM-PHY Interface.

- Implements the Physical Layer Convergence Protocol (PLCP) for DS1 and DS3 transmission systems according to the ATM Forum User Network Interface Specification and ANSI TA-TSY-000773, TA-TSY-000772, and E1 and E3 transmission systems according to the ETSI 300-269 and ETSI 300-270.

- Supports Switched Multi-megabit Data Service (SMDS) and ATM mappings into various rate transmission systems as shown in Table 1:

| Rate                | Format       | Framer Only | SMDS PLCP<br>Mapping | ATM Direct<br>Mapping |

|---------------------|--------------|-------------|----------------------|-----------------------|

| Т3                  | C-bit Parity | YES         | YES                  | YES                   |

| (44.736 Mbit/s)     | M23          | YES         | YES                  | YES                   |

| E3                  | G.751        | YES         | YES                  | YES                   |

| (34.368 Mbit/s)     | G.832        | YES         | n/a                  | YES                   |

| J2                  | G.704 & NTT  | YES         | n/a                  | YES                   |

| (6.312 Mbit/s)      |              |             |                      |                       |

| E1                  | CRC-4        | external    | YES                  | YES                   |

| (2.048 Mbit/s)      | PCM30        | external    | YES                  | YES                   |

| T1                  | ESF          | external    | YES                  | YES                   |

| (1.544 Mbit/s)      | SF           | external    | YES                  | YES                   |

| Arbitrary Cell Rate |              | bypass      | n/a                  | YES                   |

| (up to 52 Mbit/s)   |              |             |                      |                       |

#### Table 1 Supported Operating Formats

- Implements the ATM physical layer for Broadband ISDN according to ITU-T Recommendation I.432.

- Provides on-chip DS3, E3 (G.751 and G.832), and J2 framers.

- Is configurable for sole DS3, E3, or J2 Framer use.

Note: When configured to operate as a DS3, E3, or J2 Framer, gapped transmit and receive clocks can be optionally generated for interface to devices which only need access to payload data bits.

• Provides support for an arbitrary rate external transmission system interface up to a maximum rate of 52 Mbit/s, which enables the S/UNI-JET to be used as an ATM cell delineator.

- Uses the PMC-Sierra<sup>™</sup> PM4351 COMET, PM4341 T1XC and PM6341 E1XC T1 and E1 framer/line interface chips for DS1 and E1 applications.

- Provides programmable pseudo-random test pattern generation, detection, and analysis features.

- Provides integral transmit and receive HDLC controller with 128-byte FIFO depth.

- Provides performance monitoring counters suitable for accumulation periods of up to 1 second.

- Provides an 8-bit microprocessor interface for configuration, control and status monitoring.

- Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

- Uses low power 3.3V CMOS technology with 5V tolerant inputs.

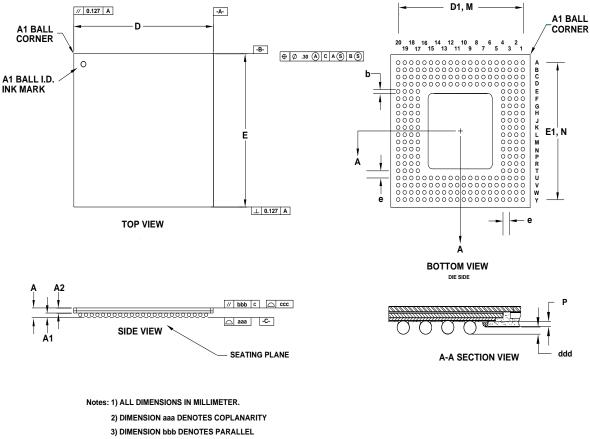

- Is available in a 256-pin SBGA package (27mm x 27mm).

The receiver section of the S/UNI-JET:

- Provides frame synchronization for the M23 or C-bit parity DS3 applications and alarm detection. Also:

- <sup>°</sup> Accumulates line code violations, framing errors, parity errors, path parity errors and FEBE events.

- ° Detects far end alarm channel codes.

- ° Provides an integral HDLC receiver to terminate the path maintenance data link.

- Provides frame synchronization for the G.751 or G.832 E3 applications and alarm detection. Also:

- ° Accumulates line code violations, framing errors, parity errors, and FEBE events.

- <sup>°</sup> Detects the Trail Trace in G.832, the Trail Trace is detected.

- <sup>°</sup> Provides an integral HDLC receiver is provided to terminate either the Network Requirement or the General Purpose data link.

- Provides frame synchronization for G.704 and NTT 6.312 Mbit/s J2 applications and alarm detection. Also:

- ° Accumulates line code violations, framing errors, and CRC parity errors.

- <sup>°</sup> Provides an integral HDLC receiver to terminate the data link.

- Provides frame synchronization, cell delineation and extraction for DS3, G.751 E3, G.832 E3, and G.704 and NTT J2 ATM direct-mapped formats.

- Provides PLCP frame synchronization, path overhead extraction, and cell extraction for DS1 PLCP, DS3 PLCP, E1 PLCP, and G.751 E3 PLCP formatted streams.

- Provides a 50 MHz 8-bit wide or 16-bit wide Utopia FIFO buffer in the receive path with parity support, and multi-PHY (Level 2) control signals.

- Provides ATM framing using cell delineation. Note: ATM cell delineation may optionally be disabled to allow passing of all cell bytes regardless of cell delineation status.

- Provides cell descrambling, header check sequence (HCS) error detection, idle cell filtering, header descrambling (for use with PPP packets), and accumulates the number of received idle cells, the number of received cells written to the FIFO, and the number of HCS errors.

- Provides a four cell FIFO for rate decoupling between the line, and a higher layer processing entity. FIFO latency may be reduced by changing the number of operational cell FIFOs.

- Provides a receive HDLC controller with a 128-byte FIFO to accumulate data link information.

- Provides detection of yellow alarm and loss of frame (LOF), and accumulates BIP-8 errors, framing errors and FEBE events.

- Provides programmable pseudo-random test-sequence detection (up to 2<sup>32</sup>-1 bit length patterns conforming to ITU-T O.151 standards) and analysis features.

The transmitter section of the S/UNI-JET:

- Provides frame insertion for the M23 or C-bit parity DS3 applications, alarm insertion, and diagnostic features. Also:

- ° Optionally inserts far end alarm channel codes.

- Provides an integral HDLC transmitter is provided to insert the path maintenance data link.

- Provides frame insertion for the G.751 or G.832 E3 applications, alarm insertion, and diagnostic features. Also:

- <sup>o</sup> Inserts the Trail Trace for G.832

- Provides an integral HDLC transmitter to insert either the Network Requirement or the General Purpose data link.

- Provides frame insertion for G.704 6.312 Mbit/s J2 applications, alarm insertion, and diagnostic features, and also an integral HDLC transmitter to insert the path maintenance data link.

- Provides frame insertion and path overhead insertion for DS1, DS3, E1 or E3 based PLCP formats, and also alarm insertion and diagnostic features.

- Provides a 50 MHz 8-bit wide or 16-bit wide Utopia FIFO buffer in the transmit path with parity support and multi-PHY (Level 2) control signals.

- Provides optional ATM cell scrambling, header scrambling (for use with PPP packets), HCS generation/insertion, programmable idle cell insertion, diagnostics features and accumulates transmitted cells read from the FIFO.

- Provides a four cell FIFO for rate decoupling between the line and a higher layer processing entity. FIFO latency may be reduced by changing the number of operational cells in the FIFO.

- Provides a transmit HDLC controller with a 128-byte FIFO.

- Provides an 8 kHz reference input for locking the transmit PLCP frame rate to an externally applied frame reference.

• Provides programmable pseudo-random test sequence generation (up to 2<sup>32</sup>-1 bit length sequences conforming to ITU-T O.151 standards). Diagnostic abilities include single bit error insertion or error insertion at bit error rates ranging from 10<sup>-1</sup> to 10<sup>-7</sup>.

The bypass and loopback features of the S/UNI-JET:

- Allow bypassing of the DS3, E3, and J2 framers to enable transmission system sublayer processing by an external device.

- Allow bypassing of the PLCP and ATM functions to enable use of the S/UNI-JET as a DS3, E3, or J2 framer.

- Provide diagnostic loopbacks, line loopbacks, and payload loopbacks.

# 2 Applications

- ATM or SMDS Switches, Multiplexers, and Routers

- SONET/SDH Mux E3/DS3 Tributary Interfaces

- PDH Mux J2/E3/DS3 Line Interfaces

- DS3/E3/J2 Digital Cross Connect Interfaces

- DS3/E3/J2 PPP Internet Access Interfaces

- DS3/E3/J2 Frame Relay Interfaces

- DSLAM Uplinks

### 3 References

- ANSI T1.627 1993, "Broadband ISDN ATM Layer Functionality and Specification".

- ANSI T1.107a 1990, "Digital Hierarchy Supplement to Formats Specifications (DS3 Format Applications)".

- ANSI T1.107 1995, "Digital Hierarchy Formats Specifications".

- ANSI T1.646 1995, "Broadband ISDN Physical Layer Specification for User-Network Interfaces Including DS1/ATM".

- ATM Forum ATM User-Network Interface Specification, V3.1, October, 1995.

- ATM Forum "UTOPIA, An ATM PHY Interface Specification, Level 2, Version 1", June, 1995.

- ATM Forum, af-PHY-0034.000, "E3 (34,368 kbps) Physical Layer Interface", August, 1995.

- ATM Forum, af-PHY-0054.000, "DS3 Physical Layer Interface Specification", January, 1996.

- ATM Forum, af-PHY-0029.000, "6,312 Kbps UNI Specification, Version 1.0", June 1995.

- Bell Communications Research, TA-TSY-000773 "Local Access System Generic Requirements, Objectives, and Interface in Support of Switched Multi-megabit Data Service" Issue 2, March 1990 and Supplement 1, December 1990.

- ETS 300 269 Draft Standard T/NA(91)17 "Metropolitan Area Network Physical Layer Convergence Procedure for 2.048 Mbit/s", April 1994.

- ETS 300 270 Draft Standard T/NA(91)18 "Metropolitan Area Network Physical Layer Convergence Procedure for 34.368 Mbit/s", April 1994.

- ITU-T Recommendation 0.151 "Error Performance Measuring Equipment Operating at the Primary Rate and Above", October, 1992.

- ITU-T Recommendation I.432 "B-ISDN User-Network Interface Physical Layer Specification", 1993

- ITU-T Recommendation G.703 "Physical/Electrical Characteristics of Hierarchical Digital Interfaces", 1991.

- ITU-T Recommendation G.704 "General Aspects of Digital Transmission Systems; Terminal Equipment - Synchronous Frame Structures Used At 1544, 6312, 2048, 8488 and 44 736 kbit/s Hierarchical Levels", July, 1995.

- ITU-T Recommendation G.751 CCITT Blue Book Fasc. III.4, "Digital Multiplex Equipment Operating at the Third Order Bit Rate of 34,368 kbit/s and the Fourth Order Bit Rate of 139,264 kbit/s and Using Positive Justification", 1988.

- ITU-T Draft Recommendation G.775 "Loss of Signal (LOS) and Alarm Indication Signal (AIS) Defect Detection and Clearance Criteria", October 1993.

- ITU-T Recommendation G.804 "ATM Cell Mapping into Plesiochronous Digital Hierarchy (PDH)", 1993.

- ITU-T Recommendation G.832 "Transport of SDH Elements on PDH Networks: Frame and Multiplexing Structures", 1993.

- ITU-T Recommendation Q.921 "ISDN User-Network Interface Data Link Layer Specification", March, 1993.

- NTT Technical Reference, "NTT Technical Reference for High-Speed Digital Leased Circuit Services", 1991.

## 4 Definitions

The following table defines the abbreviations for the S/UNI-JET.

| AIC   | Application Identification Channel      |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

| AIS   | Alarm Indication Signal                 |  |  |  |  |  |  |

| ATM   | Asynchronous Transfer Mode              |  |  |  |  |  |  |

| BIP   | Bit Interleaved Parity                  |  |  |  |  |  |  |

| CMOS  | Complementary Metal Oxide Semiconductor |  |  |  |  |  |  |

| COFA  | Change of Frame Alignment               |  |  |  |  |  |  |

| CPERR | Path Parity Error                       |  |  |  |  |  |  |

| CRC   | Cyclic Redundancy Check                 |  |  |  |  |  |  |

| DSLAM | DSL Access Multiplexer                  |  |  |  |  |  |  |

| DS1   | Digital Signal Level 1                  |  |  |  |  |  |  |

| DS3   | Digital Signal Level 3                  |  |  |  |  |  |  |

| EXZS  | Excess Zeros                            |  |  |  |  |  |  |

| F-bit | Framing Bit                             |  |  |  |  |  |  |

| FAS   | Framing Alignment Signal                |  |  |  |  |  |  |

| FEAC  | Far-End Alarm Control                   |  |  |  |  |  |  |

| FEBE  | Far-End Block Error                     |  |  |  |  |  |  |

| FERF  | Far End Receive Failure                 |  |  |  |  |  |  |

| FERR  | Framing Bit Error                       |  |  |  |  |  |  |

| FIFO  | First-In First-Out                      |  |  |  |  |  |  |

| HCS   | Header Check Sequence                   |  |  |  |  |  |  |

| HDLC  | High-level Data Link Control            |  |  |  |  |  |  |

| ISDN  | Integrated Services Digital network     |  |  |  |  |  |  |

| ITU   | International Telecommunications Union  |  |  |  |  |  |  |

| JTAG  | Joint Test Action Group                 |  |  |  |  |  |  |

| LCD   | Loss of Cell Delineation                |  |  |  |  |  |  |

| LCV   | Line Code Violation                     |  |  |  |  |  |  |

| LOF   | Loss of Frame                           |  |  |  |  |  |  |

| LOS   | Loss of Signal                          |  |  |  |  |  |  |

| NRZ   | Non Return to Zero                      |  |  |  |  |  |  |

| OOF   | Out of Frame                            |  |  |  |  |  |  |

| PERR  | Parity Error                            |  |  |  |  |  |  |

| PHY   | Physical Layer                          |  |  |  |  |  |  |

| PLCP  | Physical Layer Convergence Procedure    |  |  |  |  |  |  |

| PMDL  | Path Maintenance Data Link              |  |  |  |  |  |  |

| PMON  | Performance Monitor                     |  |  |  |  |  |  |

| POS   | Packet Over SONET                       |  |  |  |  |  |  |

| PPP   | Point-to-Point Protocol                 |  |  |  |  |  |  |

| RAI     | Receive Alarm Indication                                                 |  |  |  |  |

|---------|--------------------------------------------------------------------------|--|--|--|--|

| RBOC    | Bit Oriented Code Detector                                               |  |  |  |  |

| RDLC    | Data Link Receiver                                                       |  |  |  |  |

| RED     | Receive Error Detection                                                  |  |  |  |  |

| SBGA    | Super Ball Grid Array                                                    |  |  |  |  |

| SCI-PHY | SATURN® Compatible Interface Specification for PHY and ATM layer devices |  |  |  |  |

| SMDS    | Switched Multi-Megabit Data Service                                      |  |  |  |  |

| SONET   | Synchronous Optical Network                                              |  |  |  |  |

| TAP     | Test Access Port                                                         |  |  |  |  |

| TSB     | Telecom System Block                                                     |  |  |  |  |

| ТТВ     | Trail Trace Buffer                                                       |  |  |  |  |

# 5 Application Examples

The S/UNI-JET is configurable as:

- An ATM device

- A J2/E3/T3 framer

- A cell processor

As an ATM-PHY layer device, the S/UNI-JET connects on the line side to one J2/E3/T3 line interface unit and on the system side, it interfaces with an ATM layer device, such as the PM7322 RCMP-800, over an 8- or 16-bit wide UTOPIA Level 2 interface. Refer to Figure 1.

As a J2/E3/T3 framer, the S/UNI-JET can be used in router, frame relay switch, and multiplexer applications. Refer to Figure 2.

#### Figure 2 S/UNI-JET Operating as a Framer Device in Frame Relay Equipment

Access Side

Uplink Side

In an unchannelized J2/E3/T3 line card, the S/UNI-JET directly connects to one PM7366 FREEDM-8 HDLC controller. Each FREEDM-8 can process two high-speed links such as T3 and E3, or can process up to eight lower speed links such as J2. The S/UNI-JET gaps all the overhead bits so that only the payload data is passed to and from FREEDM-8. On the line side, the S/UNI-JET is connected to one J2/E3/T3 line interface unit. On the system side, the S/UNI-JET interfaces with a data link device over a serial bit interface.

### 6 Block Diagram

## 7 Description

The PM7346 S/UNI-JET is an ATM physical layer processor with integrated DS3, E3, and J2 framers. It supports PLCP sublayer DS1, DS3, E1, and E3 processing and ATM cell delineation.

The S/UNI-JET contains:

- An Integral DS3 framer that provides DS3 framing and error accumulation in accordance with ANSI T1.107, and T1.107a.

- An Integral E3 framer that provide E3 framing in accordance with ITU-T Recommendations G.832 and G.751.

- An Integral J2 framer that provide J2 framing in accordance with ITU-T Recommendation G.704 and I.432.

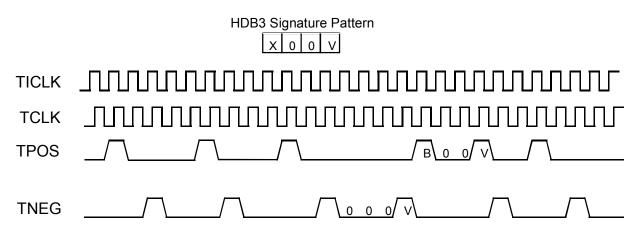

When configured for various transmission system sublayer processing, the S/UNI-JET accepts and outputs the appropriate type of bipolar and unipolar signals as described in Table 2:

| Transmission System<br>Sublayer Processing | Acceptance and Output                                                                                                         |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| DS3                                        | Accepts and outputs both digital B3ZS-encoded bipolar and unipolar signals compatible with M23 and C-bit parity applications. |

| E3                                         | Accepts and outputs both HDB3-encoded bipolar and unipolar signals compatible with G.751 and G.832 applications.              |

| J2                                         | Accepts and outputs both B8ZS-encoded bipolar and unipolar signals compliant with G.704 and NTT 6.312 Mbit/s applications.    |

| DS1, or E1                                 | Accepts and outputs outputs unipolar signals with appropriate clock and frame pulse signals for physical sublayer processing. |

| Other transmission systems                 | Provides a generic interface for physical sublayer processing.                                                                |

Table 2 Transmission System Sublayer Processing Acceptance and Output

In the DS3 receive direction, the S/UNI-JET frames to DS3 signals with a maximum average reframe time of 1.5 ms and detects line code violations (LCV), loss of signal (LOS), framing bit errors, parity errors, path parity errors, alarm indication signals (AIS), far end receive failure (FERF), and idle code. The DS3 overhead bits are extracted and presented on serial outputs. When in C-bit parity mode, the Path Maintenance Data Link (PMDL) and the Far End Alarm and Control (FEAC) channels are extracted. HDLC receivers are provided for PMDL support. Valid bit-oriented codes in the FEAC channels are also detected and are available through the microprocessor port.

| Table 3 | Summary of Receive Detection Features |

|---------|---------------------------------------|

|---------|---------------------------------------|

| Transmission System<br>Sublayer Processing | Transmit or<br>Receive | Detected Features                                                                         |

|--------------------------------------------|------------------------|-------------------------------------------------------------------------------------------|

| DS3                                        | Receive                | LCV, LOS, framing bit errors, parity errors, path parity errors, AIS, FERF, and idle code |

| E3                                         | Receive                | LCV, LOS, framing bit errors, AIS, and RAI                                                |

|    | Transmit or<br>Receive | Detected Features                                                                                           |

|----|------------------------|-------------------------------------------------------------------------------------------------------------|

| J2 |                        | LCV, LOS, LOF, framing bit errors, physical layer AIS, payload AIS, CRC-5 errors, Remote End Alarm, and RAI |

In the E3 receive direction, the S/UNI-JET frames to G.751 and G.832 E3 signals with a maximum average reframe times of 135 µs for G.751 frames and 250 µs for G.832 frames. LCVs, LOS, framing bit errors, AIS, and remote alarm indication (RAI) are detected. Further, when processing G.832 formatted data, parity errors, far end receive failure, and far end block errors are also detected; and the Trail Trace message can be extracted and made available through the microprocessor port. HDLC receivers are provided for either the G.832 Network Requirement or the G.832 General Purpose Data Link support.

In the J2 receive direction, the S/UNI-JET frames to G.704 6.312 MHz signals with a maximum average reframe time of 5.07 ms. An alternate framing algorithm that uses the CRC-5 bits to rule out 99.9% of all static mimic framing patterns is available with a maximum average reframe time of 10.22 ms when operating with a  $10^{-4}$  bit error rate. The alternate framing algorithm can be selected by the CRC\_REFR bit in the J2-FRMR Configuration Register. LCV, LOS, loss of frame (LOF), framing bit errors, physical layer AIS, payload AIS, CRC-5 errors, Remote End Alarm, and RAI are detected. HDLC receivers are provided for Data Link support.

Error event accumulation is also provided by the S/UNI-JET. Framing bit errors, LCV, parity errors, path parity errors, and far end block errors (FEBE) are accumulated, when appropriate, in saturating counters for DS3, E3, and J2 frames. LOF detection for DS3, E3, and J2 is provided as recommended by ITU-T G.783 with integration times of 1ms, 2ms, and 3ms.

In the DS3 transmit direction, the S/UNI-JET inserts DS3 framing, X and P bits. When enabled for C-bit parity operation, bit-oriented code transmitters and HDLC transmitters are provided for the insertion of FEAC channels and the PMDL in the appropriate overhead bits. AIS can be inserted by using internal register bits and other status signals such as the idle signal can be inserted when enabled by internal register bits. When M23 operation is selected, the C-bit Parity ID bit (the first C-bit of the first M sub-frame) is forced to toggle so that downstream equipment will not confuse an M23-formatted stream with stuck-at 1 C-bits for C-bit parity application.

In the E3 transmit direction, the S/UNI-JET inserts E3 framing in either G.832 or G.751 format. When enabled for G.832 operation, an HDLC transmitter is provided so that the Network Requirement or General Purpose Data Link is inserted into the appropriate overhead bits. The AIS and other status signals can be inserted by internal register bits.

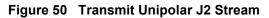

In the J2 transmit direction, the S/UNI-JET inserts J2 6.312 Mbit/s G.704 framing. HDLC transmitters are provided the Data Links are inserted. CRC-5 check bits are calculated and inserted into the J2 multiframe. External pins are provided so that any of the overhead bits within the J2 frame can be overwritten.

The S/UNI-JET also supports diagnostic options that allow it to insert, when appropriate, the transmit framing format, parity or path parity errors, F-bit framing errors, M-bit framing errors, invalid X or P-bits, LCV, all-zeros, AIS, RAIs, and Remote End Alarms.

The S/UNI-JET provides cell delineation for ATM cells using the PLCP framing format, or by using the header check sequence octet in the ATM cell header as specified by ITU-T Recommendation I.432. DS1, DS3, E1, and E3-based PLCP frame formats can be processed. Non-PLCP-based cell delineation is done with either bit, nibble, or byte-wide search algorithms depending on the line interface used. An interface consistent with the generic physical interface defined by ITU-T Recommendation I.432 is provided for arbitrary rates up to 52 Mbit/s. This interface is used for PHY layer support for transmission systems that do not have an associated PLCP sublayer, or to provide an efficient means of directly mapping ATM cells to existing transmission system formats (such as DS3 and DS1).

In the PLCP receive direction, framing, path overhead extraction, and cell extraction is provided. BIP-8 error events, frame octet error events, and FEBE events are accumulated.

In the PLCP transmit direction, the S/UNI-JET provides overhead insertion using inputs or internal registers, DS3 nibble and E3 byte stuffing, automatic BIP-8 octet generation and insertion, and automatic FEBE insertion. Diagnostic features for BIP-8 error, framing error and FEBE insertion are also supported.

In the cell receive path, idle cells may be dropped according to a programmable filter. By default, incoming cells with single bit HCS errors are corrected and written to the FIFO buffer. Optionally, cells can be dropped upon detection of a HCS error. Cell delineation may optionally be disabled to allow all cells to pass, regardless of cell delineation status. The ATM cell payloads are optionally descrambled. ATM cell headers may optionally be descrambled (for use with PPP packets). Assigned cells containing no detectable HCS errors are written to a FIFO buffer. Cell data is read from the FIFO using a synchronous 50 MHz 8-bit wide or 16-bit wide SCI-PHY<sup>TM</sup> and Utopia Level 2-compatible interface. Cell data parity is also provided. Counts of error-free assigned cells, and cells containing HCS errors are accumulated independently for performance monitoring purposes.

In the cell transmit path, cell data is written to a FIFO buffer using a synchronous 50 MHz 8-bit wide or 16-bit wide SCI-PHY<sup>TM</sup> compatible interface. Cell data parity is also examined for errors. Idle cells are automatically inserted when the FIFO contains less than one full cell. HCS generation, cell payload scrambling, and cell header scrambling (for use with PPP packets) are optionally provided. Counts of transmitted cells are accumulated for performance monitoring purposes.

Both receive and transmit cell FIFOs provide buffering for four cells. The FIFOs provide the rate matching interface between the higher layer ATM entity and the S/UNI-JET.

The S/UNI-JET is configured, controlled, and monitored by a generic 8-bit microprocessor bus through which all internal registers are accessed. All sources of interrupts can be identified, acknowledged, or masked with this interface.

The S/UNI-JET requires a software initialization sequence in order to guarantee proper device operation and long term reliability. Please refer to Section 13.1 of this document for the details on how to program this sequence.

## 8 Pin Diagram

The S/UNI-JET is packaged in a 256-pin SBGA package with a body size of 27 mm by 27 mm and a pin pitch of 1.27 mm.

# Quadrant A11/A20 to K11/K20

|   | 20      | 19      | 18         | 17        | 16          | 15        | 14    | 13   | 12   | 11   |   |

|---|---------|---------|------------|-----------|-------------|-----------|-------|------|------|------|---|

| A | VSS     | VSS     | VSS        | TDATI[10] | TDATI[14]   | D[1]      | D[5]  | VSS  | A[3] | A[7] | А |

| В | VSS     | VDD     | VDD        | TDATI[9]  | TDATI[13]   | D[0]      | D[4]  | A[0] | A[2] | A[6] | в |

| С | VSS     | VDD     | VDD        | TDATI[7]  | TDATI[11]   | TDATI[15] | D[2]  | D[6] | A[1] | A[5] | С |

| D | TDAT[3] | TDAT[4] | TDAT[6]    | NC        | TDAT[8]     | TDAT[12]  | VDD   | D[3] | D[7] | A[4] | D |

| Е | TFCLK   | TDAT[0] | TDAT[2]    | TDAT[5]   |             |           |       |      |      |      | Е |

| F | TADR[0] | TADR[1] | TADR[2]    | TDAT[1]   | Bottom View |           |       |      |      |      |   |

| G | TSOC    | TPRTY   | VDD        | VDD       |             |           | Top L | -    |      |      | G |

| Н | BIAS    | TCA     | TENB       | VDD       |             |           |       | .eny |      |      | н |

| J | VSS     | NC      | NC         | DTCA      |             |           |       |      |      |      | J |

| K | VSS     | NC      | PHY_ADR[2] | VDD       | 1           |           |       |      |      |      | к |

|   | 20      | 19      | 18         | 17        | 16          | 15        | 14    | 13   | 12   | 11   | - |

### Quadrant A1/A10 to K1/K10

|   | 10   | 9     | 8     | 7        | 6              | 5                      | 4      | 3     | 2      | 1     |   |

|---|------|-------|-------|----------|----------------|------------------------|--------|-------|--------|-------|---|

| A | VSS  | VSS   | ALE   | INTB     | TRSTB          | TOHM/<br>TNEG          | RCLK   | VSS   | VSS    | VSS   | A |

| В | A[9] | A[10] | WRB   | TDO      | тск            | TCLK                   | NC     | VDD   | VDD    | VSS   | В |

| С | A[8] | CSB   | RSTB  | TMS      | TPOS/<br>TDATO | RLCV/<br>RNEG/<br>ROHM | NC     | VDD   | VDD    | VSS   | С |

| D | VDD  | RDB   | TDI   | VDD      | RPOS/<br>RDATI | NC                     | BIAS   | NC    | NC     | VSS   | D |

| Е |      |       |       |          |                |                        | NC     | VSS   | VSS    | VSS   | Е |

| F |      |       | Potto | n View   |                |                        | VSS    | VSS   | NC     | NC    | F |

| G |      |       |       | Right)   |                |                        | VDD    | NC    | VSS    | VSS   | G |

| Н |      |       | (iop  | ixigiit) |                |                        | VSS    | тон   | TOHCLK | VSS   | Н |

| J |      |       |       |          |                |                        | TOHINS | TOHFP | ROH    | ROHFP | J |

| ĸ |      |       |       |          |                |                        | ROHCLK | VSS   | VSS    | NC    | к |

|   | 10   | 9     | 8     | 7        | 6              | 5                      | 4      | 3     | 2      | 1     |   |

## Quadrant L11/L20 to Y11/Y20

|   | 20         | 19         | 18       | 17       | 16      | 15                       | 14                                              | 13                            | 12                                   | 11  |   |

|---|------------|------------|----------|----------|---------|--------------------------|-------------------------------------------------|-------------------------------|--------------------------------------|-----|---|

| L | PHY_ADR[1] | PHY_ADR[0] | ATMB     | DRCA     |         |                          | Bottom                                          | View                          |                                      |     | L |

| М | NC         | NC         | NC       | RSOC     |         |                          | (Botton                                         | n Left)                       |                                      |     | М |

| Ν | VSS        | RCA        | RENB     | RADR[1]  |         |                          |                                                 |                               |                                      |     | Ν |

| Ρ | RFCLK      | RADR[2]    | RADR[0]  | VDD      |         |                          |                                                 |                               |                                      |     | Ρ |

| R | VDD        | VDD        | RPRTY    | RDAT[13] |         |                          |                                                 |                               |                                      |     | R |

| Т | RDAT[15]   | RDAT[14]   | RDAT[12] | RDAT[9]  |         |                          |                                                 |                               |                                      |     | т |

| U | RDAT[11]   | RDAT[10]   | RDAT[8]  | BIAS     | RDAT[6] | RDAT[2]                  | VDD                                             | TPOHCLK                       | REF8KO/<br>RPOHFP/<br>RFPO/<br>RMFPO | VDD | U |

| V | VSS        | VDD        | VDD      | RDAT[7]  | RDAT[3] | TICLK                    | TPOHINS                                         | RPOH/<br>ROVRHD               | VSS                                  | NC  | V |

| W | VSS        | VDD        | VDD      | RDAT[5]  | RDAT[1] | TIOHM/<br>TFPI/<br>TMFPI | TPOHFP/<br>TFPO/<br>TMFPO/<br>TGAPCLK/<br>TCELL | RPOHCLK/<br>RSCLK/<br>RGAPCLK | VSS                                  | VSS | w |

| Y | VSS        | VSS        | VSS      | RDAT[4]  | RDAT[0] |                          | LCD/<br>RDATO                                   | VSS                           | VSS                                  | VSS | Y |

|   | 20         | 19         | 18       | 17       | 16      | 15                       | 14                                              | 13                            | 12                                   | 11  | _ |

### Quadrant L1/L10 to Y1/Y10

|   | 10      | 9        | 8   | 7   | 6   | 5   | 4    | 3      | 2   | 1       |   |

|---|---------|----------|-----|-----|-----|-----|------|--------|-----|---------|---|

| L | Bottom  | View     |     |     |     |     | VDD  | NC     | NC  | VSS     | L |

| М | (Bottom | n Right) |     |     |     |     | VSS  | NC     | NC  | VSS     | М |

| Ν |         |          |     |     |     |     | NC   | NC     | NC  | VSS     | N |

| Ρ |         |          |     |     |     |     | VDD  | VSS    | NC  | NC      | Р |

| R |         |          |     |     |     |     | NC   | NC     | NC  | VSS     | R |

| т |         |          |     |     |     |     | NC   | REF8KI | NC  | NC      | т |

| U | NC      | VSS      | NC  | VDD | NC  | NC  | BIAS | NC     | NC  | FRMSTAT | U |

| V | NC      | VSS      | NC  | NC  | VSS | NC  | NC   | VDD    | VDD | VSS     | v |

| W | NC      | VSS      | VSS | NC  | VSS | VSS | NC   | VDD    | VDD | VSS     | w |

| Y | NC      | NC       | VSS | NC  | NC  | VSS | NC   | VSS    | VSS | VSS     | Y |

|   | 10      | 9        | 8   | 7   | 6   | 5   | 4    | 3      | 2   | 1       | 1 |

# 9 Pin Description

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

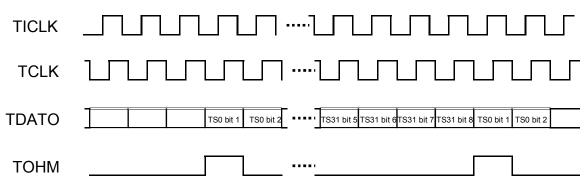

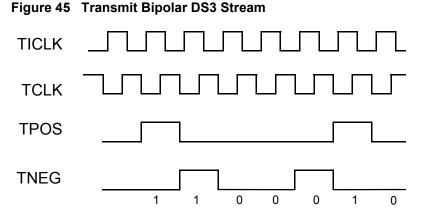

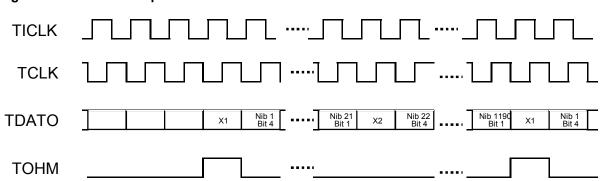

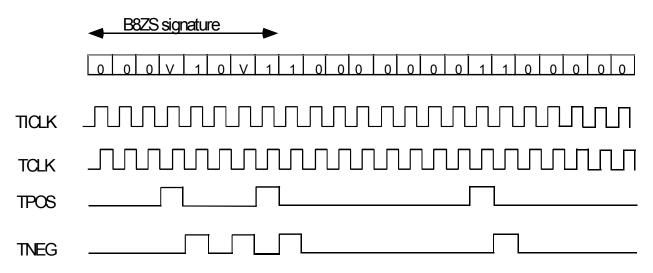

| TPOS     | Output | C6         | The Transmit Digital Positive Pulse (TPOS) contains the positive pulses transmitted on the B3ZS-encoded DS3, HDB3-encoded E3, or B8ZS-encoded J2 transmission system when the dual-rail output format is selected.                                                                                                                                                               |

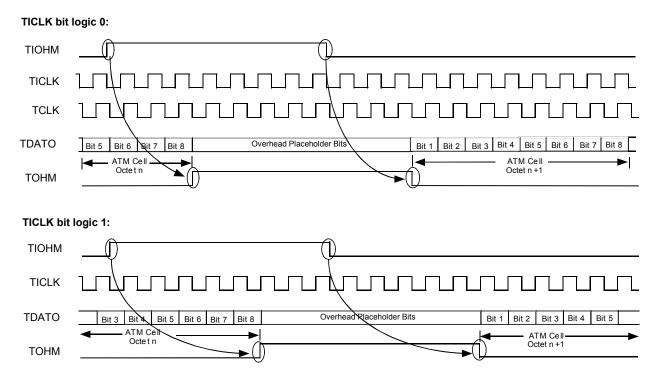

| TDATO    |        |            | The Transmit Data (TDATO) contains the transmit data stream when the single-rail (unipolar) output format is enabled or when a non-DS3/E3/J2 based transmission system is selected.                                                                                                                                                                                              |

|          |        |            | The TPOS/TDATO pin function selection is controlled by<br>the TFRM[1:0] and the TUNI bits in the S/UNI-JET<br>Transmit Configuration Register. Output signal polarity<br>control is provided by the TPOSINV bit in the S/UNI-JET<br>Transmit Configuration Register.                                                                                                             |

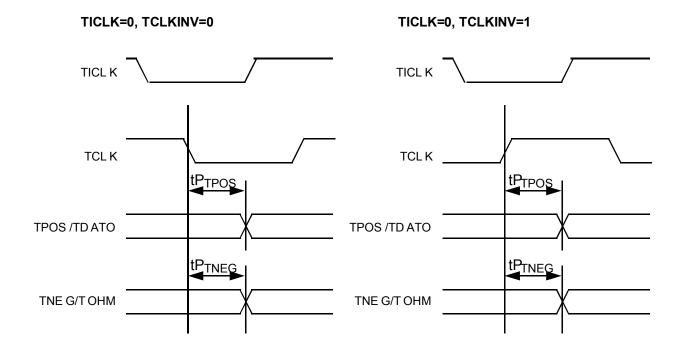

|          |        |            | Both TPOS and TDATO are updated on the falling edge<br>of TCLK by default, and may be configured for update on<br>the rising edge of TCLK through the TCLKINV bit in the<br>S/UNI-JET Transmit Configuration Register. Also, both<br>TPOS and TDATO can be updated on the rising edge of<br>TICLK, enabled by the TICLK bit in the S/UNI-JET<br>Transmit Configuration Register. |

| TNEG     | Output | A5         | The Transmit Digital Negative Pulse (TNEG) contains the negative pulses transmitted on the B3ZS-encoded DS3, HDB3-encoded E3, or B8ZS-encoded J2 transmission system when the dual-rail NRZ output format is selected.                                                                                                                                                           |

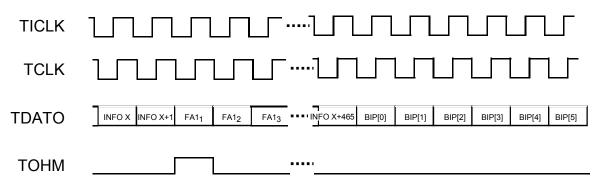

| ТОНМ     |        |            | The Transmit Overhead Mask (TOHM) indicates the position of overhead bits (non-payload bits) in the transmission system stream aligned with TDATO. TOHM indicates the location of the M-frame boundary for DS3, the position of the frame boundary for E3, and the position of the multi-frame boundary for J2 when the single-rail (unipolar) NRZ input format is enabled.      |

|          |        |            | When a PLCP formatted signal is transmitted, TOHM is set to logic one once per transmission frame, and indicates the DS1 or E1 frame alignment.                                                                                                                                                                                                                                  |

|          |        |            | When a non-PLCP, non-DS3, non-E3, or non-J2 based signal is transmitted, TOHM is a delayed version of the TIOHM input, and indicates the position of each overhead bit in the transmission frame. TOHM is updated on the falling edge of TCLK.                                                                                                                                   |

|          |        |            | The TNEG/TOHM pin function selection is controlled by<br>the TFRM[1:0] and the TUNI bits in the S/UNI-JET<br>Transmit Configuration Register. Output signal polarity<br>control is provided by the TNEGINV bit in the S/UNI-JET<br>Transmit Configuration Register.                                                                                                              |

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |        |            | By default, both TNEG and TOHM are updated on the<br>falling edge of TCLK and can be enabled for update on<br>the rising edge of TCLK. This sampling is controlled by<br>the TCLKINV bit in the S/UNI-JET Transmit<br>Configuration Register. Also, both TNEG and TOHM can<br>be updated on the rising edge of TICLK, enabled by the<br>TICLK bit in the S/UNI-JET Transmit Configuration<br>Register. |

| TCLK     | Output | B5         | The Transmit Output Clock (TCLK) provides the transmit direction timing. TCLK is a buffered version of TICLK and can be enabled to update the TPOS/TDATO and TNEG/TOHM outputs on its rising or falling edge.                                                                                                                                                                                          |

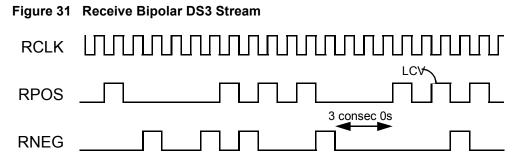

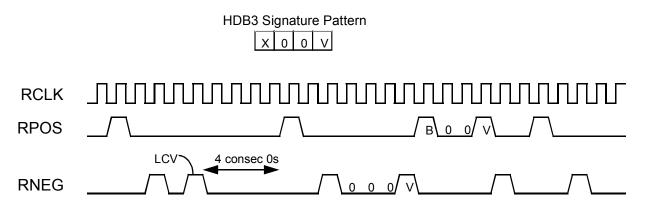

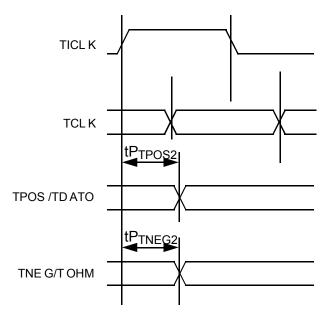

| RPOS     | Input  | D6         | The Receive Digital Positive Pulse (RPOS) contains the positive pulses received on the B3ZS-encoded DS3, the HDB3-encoded E3, or the B8ZS-encoded J2 transmission system when the dual-rail NRZ input format is selected.                                                                                                                                                                              |

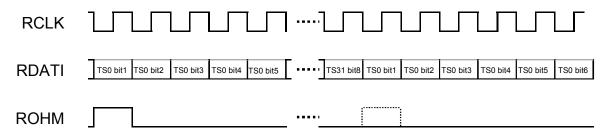

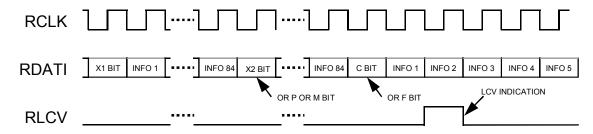

| RDATI    |        |            | The Receive Data (RDATI) contains the data stream<br>when the single-rail (unipolar) NRZ input format is<br>enabled or when a non-DS3/E3/J2 based transmission<br>system is being processed (for example, RDATI may<br>contain a DS1 or E1 stream).                                                                                                                                                    |

|          |        |            | The RPOS/RDATI pin function selection is controlled by<br>the RFRM[1:0] bits in the S/UNI-JET Configuration<br>Register and by the UNI bits in the DS3 FRMR, the E3<br>FRMR, or the J2 FRMR Configuration Register.                                                                                                                                                                                    |

|          |        |            | Both RPOS and RDATI are sampled on the rising edge<br>of RCLK by default, and may be enabled to be sampled<br>on the falling edge of RCLK. This sampling is controlled<br>by the RCLKINV bit in the S/UNI-JET Receive<br>Configuration Register.                                                                                                                                                       |

|          |        |            | Note: Signal polarity control is provided by the RPOSINV bit in the S/UNI-JET Receive Configuration Register.                                                                                                                                                                                                                                                                                          |

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RNEG     | Input | C5         | The Receive Digital Negative Pulse (RNEG) contains the negative pulses received on the B3ZS encoded DS3, the HDB3-encoded E3, or the B8ZS-encoded J2 transmission system when the dual-rail NRZ input format is selected.                                                                                                                                         |

| RLCV     |       |            | The Receive LCV (RLCV) contains LCV indications when<br>the single-rail (unipolar) NRZ input format is enabled for<br>DS3, E3, or J2 applications. Each LCV is represented by<br>an RCLK period-wide pulse.                                                                                                                                                       |

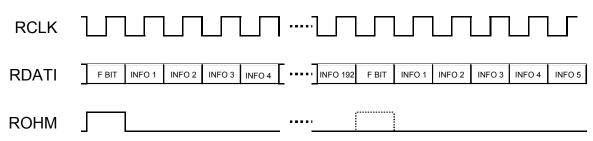

| ROHM     |       |            | When a DS1 or E1 PLCP or ATM direct-mapped signal is<br>received, Receive Overhead Mask (ROHM) is pulsed<br>once per transmission frame, and indicates the DS1 or<br>E1 frame alignment relative to the RDATI data stream.<br>When an alternate frame-based signal is received,<br>ROHM indicates the position of each overhead bit in the<br>transmission frame. |

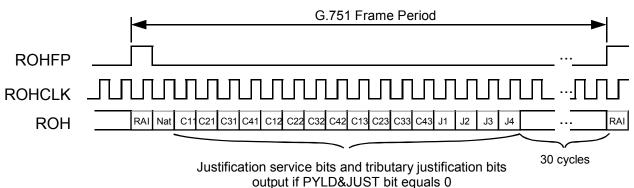

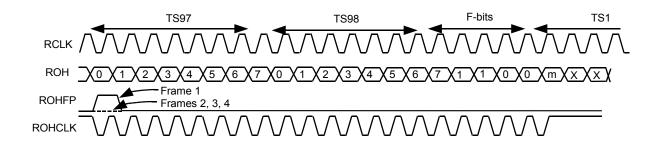

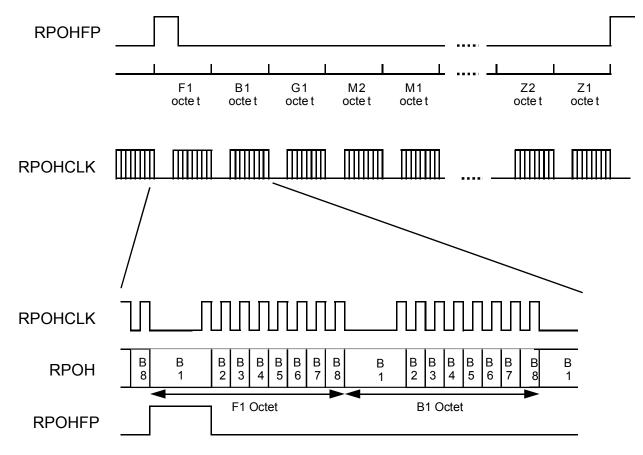

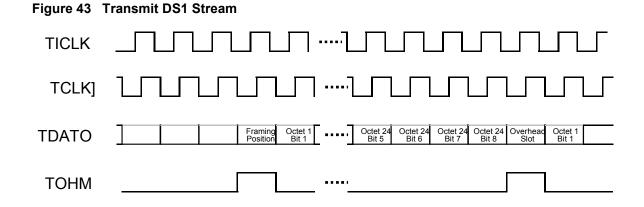

|          |       |            | The RNEG/RLCV/ROHM pin function selection is<br>controlled by the RFRM[1:0] bits in the S/UNI-JET<br>Receive Configuration Register, the UNI bits in the DS3<br>FRMR, E3 FRMR, or J2 FRMR Configuration Register,<br>and the PLCPEN and EXT bits in the SPLR<br>Configuration Register.                                                                           |