ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

## **PM4314**

# **QDSX**

# **QUAD T1/E1 LINE INTERFACE DEVICE**

## **DATA SHEET**

**ISSUE 5: JUNE 1998**

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

### **PUBLIC REVISION HISTORY**

| Issue<br>No. | Issue<br>Date    | Details of Change                                           |

|--------------|------------------|-------------------------------------------------------------|

| 5 June,      |                  | Data Sheet Reformatted — No Change in Technical Content     |

|              | 1998             | Generated R5 data sheet from PMC-950739, R4                 |

| 4            | January,<br>1997 | Eng Doc Issue R3 released                                   |

| 3            | March,<br>1996   | Public release of document: removal of confidential notices |

| 2            | January,<br>1996 | Upgrade to Eng Doc Issue P2                                 |

| 1            | August,<br>1995  | Creation of Document                                        |

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

### **CONTENTS**

| 1 | FEAT  | URES                                               | 1  |

|---|-------|----------------------------------------------------|----|

| 2 | APPL  | ICATIONS                                           | 5  |

| 3 | REFE  | ERENCES                                            | 6  |

| 4 | APPL  | ICATION EXAMPLES                                   | 8  |

| 5 | BLOC  | CK DIAGRAM                                         | 13 |

| 6 | DESC  | CRIPTION                                           | 15 |

| 7 | PIN D | DIAGRAM                                            | 18 |

| 8 | PIN D | DESCRIPTION                                        | 19 |

| 9 | FUNC  | CTIONAL DESCRIPTION                                | 32 |

|   | 9.1   | ANALOG PULSE SLICER (RSLC)                         | 32 |

|   | 9.2   | CLOCK AND DATA RECOVERY (CDRC)                     | 35 |

|   | 9.3   | LINE CODE VIOLATION PERFORMANCE MONITOR (LCV_PMON) | 39 |

|   | 9.4   | INBAND LOOPBACK CODE DETECTOR (IBCD)               | 40 |

|   | 9.5   | PSEUDO-RANDOM BIT SEQUENCE MONITOR (PRSM)          | 40 |

|   | 9.6   | TIMING OPTIONS (TOPS)                              | 42 |

|   | 9.7   | PSEUDO-RANDOM BIT SEQUENCE GENERATOR (PRSG).       | 42 |

|   | 9.8   | INBAND LOOPBACK CODE GENERATOR (XIBC)              | 43 |

|   | 9.9   | B8ZS/HDB3/AMI LINE ENCODER (LCODE)                 | 43 |

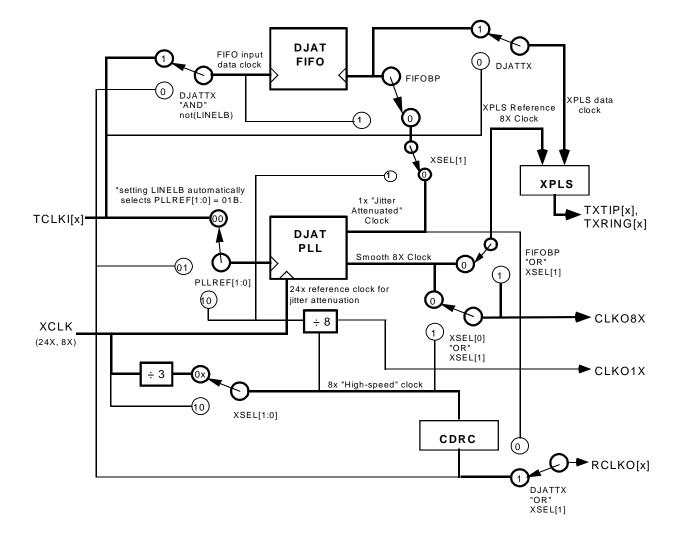

|   | 9.10  | DIGITAL JITTER ATTENUATOR (DJAT)                   | 43 |

|   | 9.11  | ANALOG PULSE GENERATOR (XPLS)                      | 49 |

ISSUE 5

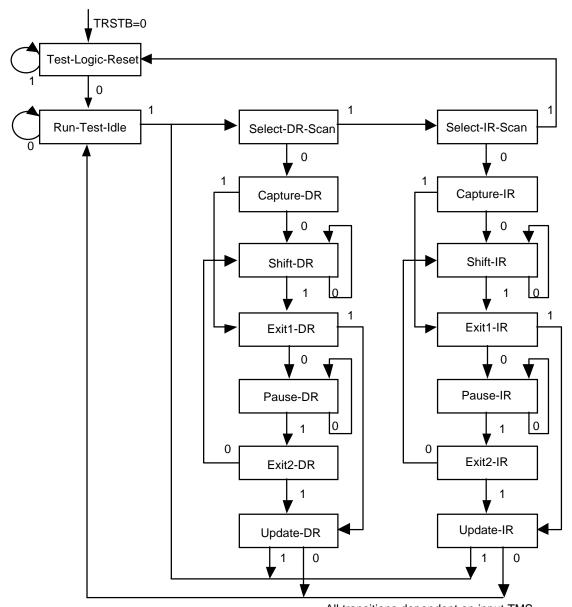

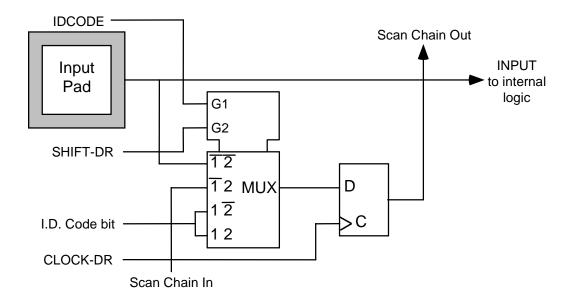

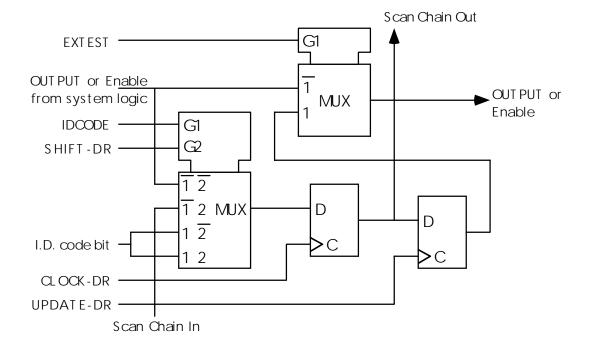

|    | 9.12   | IEEE P1149.1 JTAG TEST ACCESS PORT                   | 52  |

|----|--------|------------------------------------------------------|-----|

|    | 9.13   | MICROPROCESSOR INTERFACE                             | 52  |

|    | 9.14   | REGISTER MEMORY MAP                                  | 53  |

| 10 | NOR    | MAL MODE REGISTER DESCRIPTION                        | 56  |

| 11 | TEST   | FEATURES DESCRIPTION                                 | 113 |

|    | 11.1   | TEST MODE 0 DETAILS                                  | 114 |

|    | 11.2   | JTAG TEST PORT                                       | 116 |

| 12 | OPER   | RATIONS                                              | 119 |

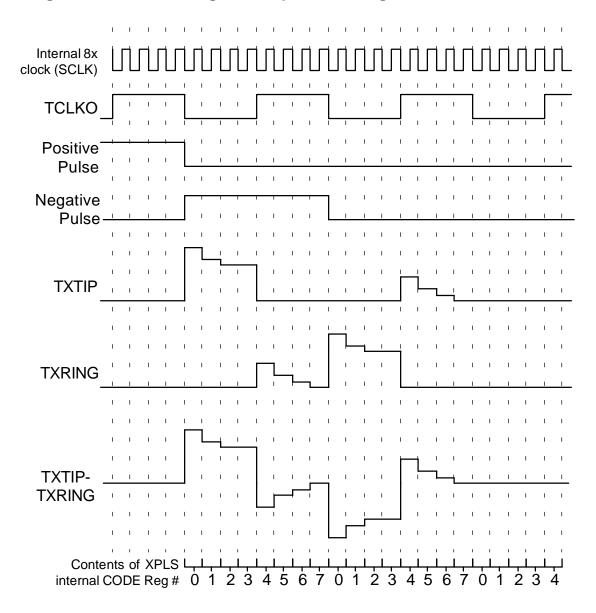

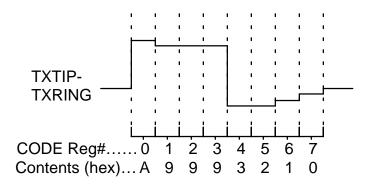

|    | 12.1   | PROGRAMMING THE XPLS WAVEFORM TEMPLATE               | 122 |

|    | 12.2   | USING THE DIGITAL JITTER ATTENUATOR                  | 127 |

|    | 12.3   | USING XPLS WITHOUT DJAT                              | 128 |

|    |        | 12.3.1 FIFO NOT IN TX PATH, XSEL[1] = 0              | 129 |

|    |        | 12.3.2 FIFO NOT IN TX PATH, XSEL[1] = 1, XSEL[0] = 0 | 129 |

|    |        | 12.3.3 FIFO IS IN TX PATH, XSEL[1] = 1, XSEL[0] = 0  | 129 |

|    |        | 12.3.4 FIFO NOT IN TX PATH, XSEL[1] = 1, XSEL[0] = 1 | 129 |

|    |        | 12.3.5 FIFO IS IN TX PATH, XSEL[1] = 1, XSEL[0] = 1  | 130 |

|    | 12.4   | JTAG SUPPORT                                         | 130 |

| 13 | FUNC   | CTIONAL TIMING                                       | 141 |

|    | 13.1   | LINE CODE VIOLATION INSERTION                        | 141 |

| 14 | ABSC   | DLUTE MAXIMUM RATINGS                                | 144 |

| 15 | CAPA   | CITANCE                                              | 145 |

| 16 | D.C. C | CHARACTERISTICS                                      | 146 |

| 17 | MICR   | OPROCESSOR INTERFACE TIMING CHARACTERISTICS          | 149 |

| DATA SHEET<br>PMC-950857 | ISSUE 5                          | QUAD T1/E1 LINE INTERFACE DEVICE |  |

|--------------------------|----------------------------------|----------------------------------|--|

| 18                       | A.C. TIMING CHARACTERISTICS      | 153                              |  |

| 19                       | ORDERING AND THERMAL INFORMATION | 163                              |  |

| 20                       | MECHANICAL INFORMATION           | 164                              |  |

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

### **LIST OF REGISTERS**

| REGISTER 000H, 040H, 080H, AND 0C0H: RECEIVE CONFIGURATION57                          |

|---------------------------------------------------------------------------------------|

| REGISTER 001H, 041H, 081H, AND 0C1H: TRANSMIT CONFIGURATION 60                        |

| REGISTER 002H, 042H, 082H, AND 0C2H: TX/RX BLOCK PLACEMENT62                          |

| REGISTER 003H, 043H, 083H, AND 0C3H: INTERRUPT SOURCE64                               |

| REGISTER 005H, 045H, 085H, AND 0C5H: DIAGNOSTICS65                                    |

| REGISTER 006H OR 106H: MASTER TEST67                                                  |

| REGISTER 007H: REVISION/CHIP ID/GLOBAL MONITORING UPDATE70                            |

| REGISTER 008H: INTERRUPT QUADRANT ID71                                                |

| REGISTER 009H: TOPS MASTER CLOCK CONFIGURATION/CLOCK ACTIVITY MONITOR72               |

| REGISTER 00AH, 04AH, 08AH, AND 0CAH: TOPS CLOCK TIMING OPTIONS                        |

| REGISTER 00BH, 04BH, 08BH, AND 0CBH: LCODE TRANSMIT LINE CODE CONFIGURATION76         |

| REGISTER 010H, 050H, 090H, AND 0D0H: CDRC CONFIGURATION77                             |

| REGISTERS 011H, 051H, 091H AND 0D1H: CDRC INTERRUPT ENABLE79                          |

| REGISTERS 012H, 052H, 092H AND 0D2H: CDRC INTERRUPT STATUS80                          |

| REGISTER 014H, 054H, 094H, AND 0D4H: LCV_PMON INTERRUPT ENABLE/STATUS81               |

| REGISTERS 01AH-01BH, 05AH-05BH, 09AH-09BH, 0DAH-0DBH: LATCHING LCV PERFORMANCE DATA82 |

| REGISTERS 01AH, 05AH, 09AH AND 0DAH: LCV_PMON LINE CODE VIOLATION COUNT LSB           |

ISSUE 5

| REGISTERS 01BH, 05BH, 09BH AND 0DBH: LCV_PMON LINE CODE VIOLATION COUNT MSB84   |

|---------------------------------------------------------------------------------|

| REGISTERS 01CH, 05CH, 09CH AND 0DCH: DJAT INTERRUPT STATUS85                    |

| REGISTER 01DH, 05DH, 09DH AND 0DDH: DJAT REFERENCE CLOCK DIVISOR (N1) CONTROL86 |

| REGISTERS 01EH, 05EH, 09EH AND 0DEH: DJAT OUTPUT CLOCK DIVISOR (N2) CONTROL87   |

| REGISTERS 01FH, 05FH, 09FH AND 0DFH: DJAT CONFIGURATION88                       |

| REGISTERS 020H, 060H, 0A0H AND 0E0H: IBCD CONFIGURATION90                       |

| REGISTERS 021H, 061H, 0A1H AND 0E1H: IBCD INTERRUPT ENABLE/STATUS91             |

| REGISTERS 022H, 062H, 0A2H AND 0E2H: IBCD ACTIVATE CODE93                       |

| REGISTERS 023H, 063H, 0A3H AND 0E3H: IBCD DEACTIVATE CODE94                     |

| REGISTERS 024H, 064H, 0A4H AND 0E4H: XIBC CONTROL95                             |

| REGISTERS 025H, 065H, 0A5H AND 0E5H: XIBC LOOPBACK CODE97                       |

| REGISTER 027H, 067H, 0A7H, 0E7H: PRSG CONFIGURATION98                           |

| REGISTER 029H, 069H, 0A9H, 0E9H: PRSM CONTROL/STATUS99                          |

| REGISTER 02AH, 06AH, 0AAH, 0EAH: PRSM BIT ERROR EVENT COUNT LSB102              |

| REGISTER 02BH, 06BH, 0ABH, 0EBH: PRSM BIT ERROR EVENT COUNT MSB103              |

| REGISTER 02CH, 06CH, 0ACH, 0ECH: XPLS LINE LENGTH CONFIGURATION104              |

| REGISTER 02DH, 06DH, 0ADH, 0EDH: XPLS CONTROL/STATUS106                         |

| REGISTER 02EH, 06EH, 0AEH, 0EEH: XPLS CODE INDIRECT ADDRESS 108                 |

| REGISTER 02FH, 06FH, 0AFH, 0EFH: XPLS CODE INDIRECT DATA110                     |

| ISSUE 5 | QUAD T1/E1 LINE INTERFACE DEVICE |

|---------|----------------------------------|

| REGISTER | 030H, | 070H, | 0B0H, | OFOH: | RSLC | CONFI  | GURA   | ΓΙΟN  |         | 111   |

|----------|-------|-------|-------|-------|------|--------|--------|-------|---------|-------|

| REGISTER | 031H, | 071H, | 0B1H, | 0F1H: | RSLC | INTERF | RUPT I | ENABL | E/STATU | JS112 |

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

### **LIST OF FIGURES**

| FIGURE 1 - EXAMPLE 1. IT OR ET ATM INTERFACES                             |

|---------------------------------------------------------------------------|

| FIGURE 2 - EXAMPLE 2. DSX-1 DIGITAL ACCESS CROSS CONNECTS (DACS)          |

| FIGURE 3 - EXAMPLE 3. MULTIPLEXERS (M13)12                                |

| FIGURE 4 - NORMAL OPERATING MODE13                                        |

| FIGURE 5 - LOOPBACK MODES14                                               |

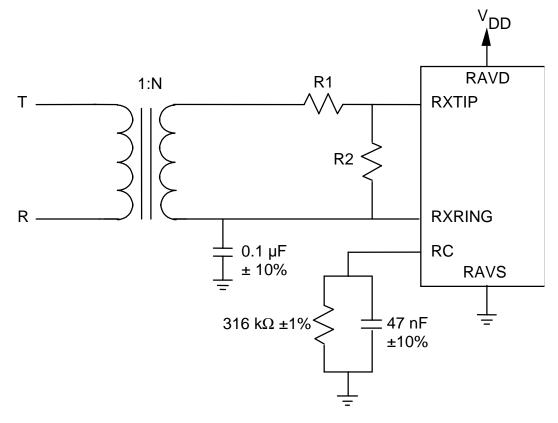

| FIGURE 6 - EXTERNAL ANALOG RECEIVE INTERFACE CIRCUIT34                    |

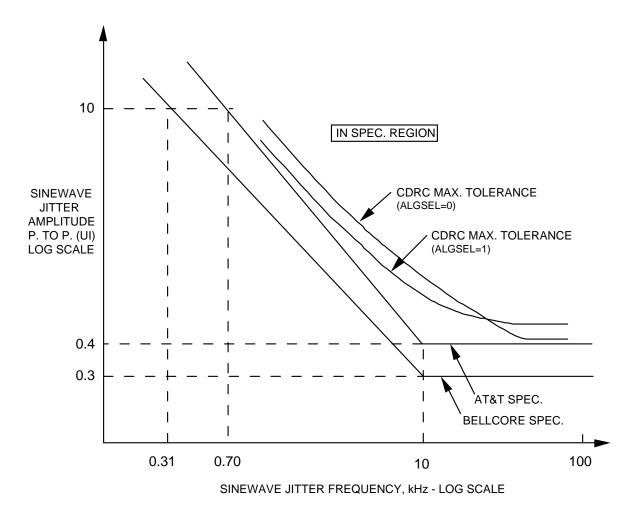

| FIGURE 7 - DSX-1 JITTER TOLERANCE                                         |

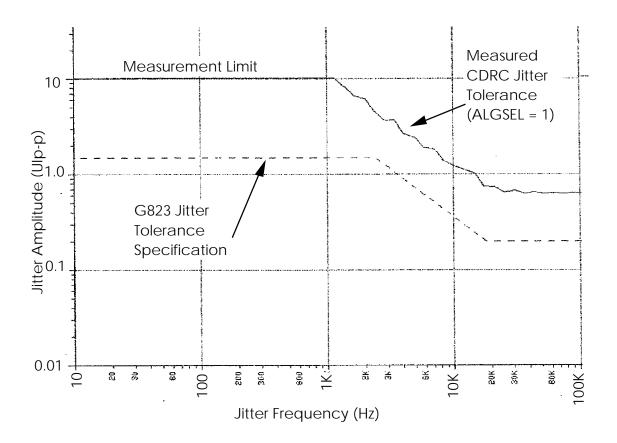

| FIGURE 8 - E1 JITTER TOLERANCE WITH ALGSEL = 138                          |

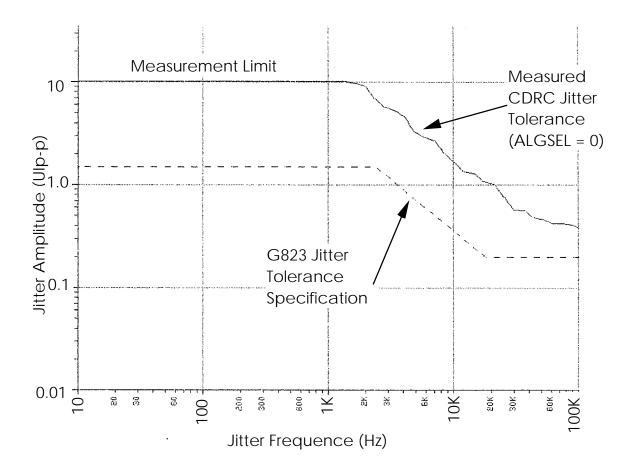

| FIGURE 9 - E1 JITTER TOLERANCE WITH ALGSEL = 039                          |

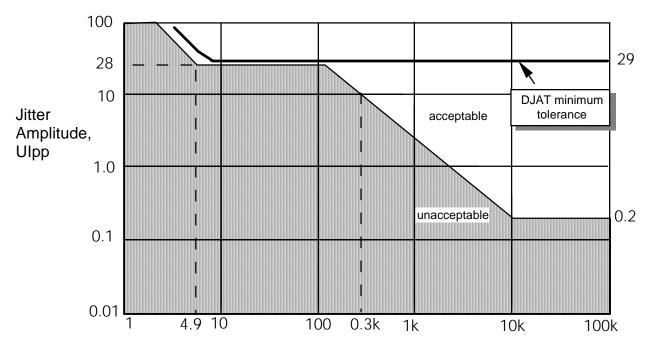

| FIGURE 10- DSX-1 JITTER TOLERANCE45                                       |

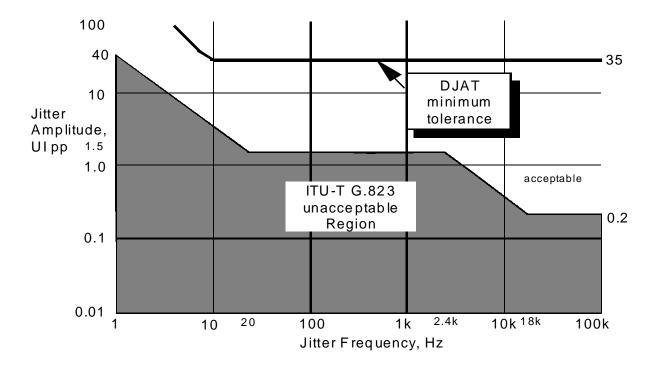

| FIGURE 11- E1 JITTER TOLERANCE46                                          |

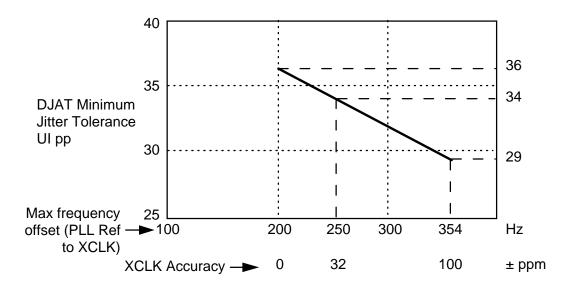

| FIGURE 12- DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY (DSX-1 CASE)47 |

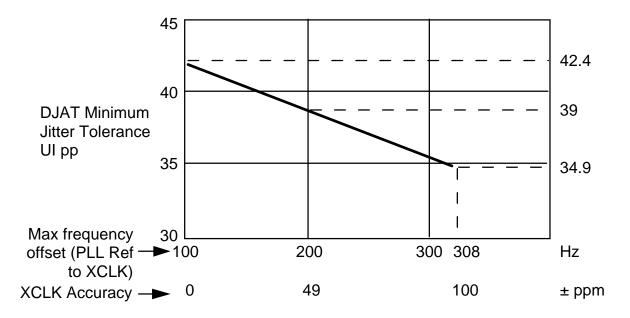

| FIGURE 13- DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY (E1 CASE)47    |

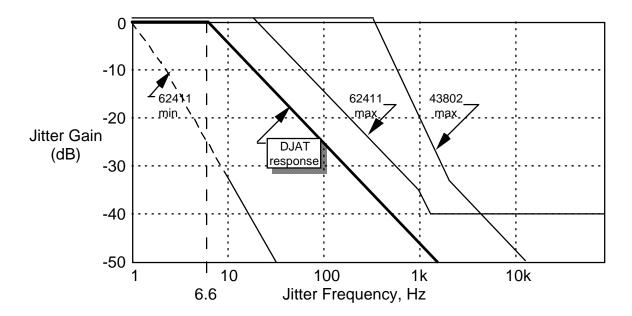

| FIGURE 14- DSX-1 JITTER TRANSFER48                                        |

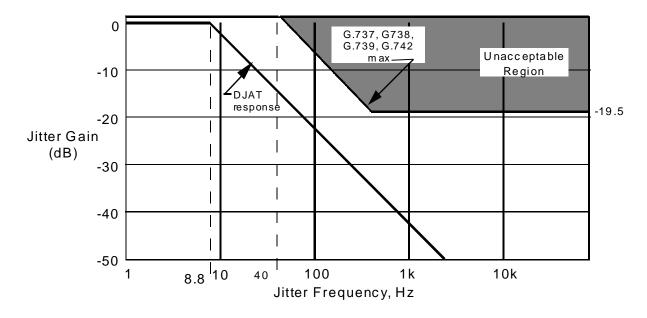

| FIGURE 15- E1 JITTER TRANSFER49                                           |

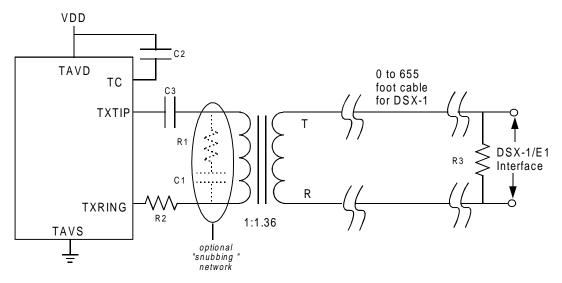

| FIGURE 16- EXTERNAL ANALOG TRANSMIT INTERFACE CIRCUIT57                   |

| FIGURE 17- TIMING OPTIONS75                                               |

| FIGURE 18- CODE REGISTER SEQUENCE DURING PULSE GENERATION125              |

| FIGURE 19- CODE REGISTER SEQUENCE FOR 0-110 FEET BUILD-OUT 126            |

ISSUE 5

| FIGURE 20- BOUNDARY SCAN ARCHITECTURE13                          |

|------------------------------------------------------------------|

| FIGURE 21- TAP CONTROLLER FINITE STATE MACHINE13                 |

| FIGURE 22- INPUT OBSERVATION CELL (IN_CELL)13                    |

| FIGURE 23- OUTPUT CELL (OUT_CELL)13                              |

| FIGURE 24- BIDIRECTIONAL CELL (IO_CELL)14                        |

| FIGURE 25- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS 14    |

| FIGURE 26- B8ZS LINE CODE VIOLATION INSERTION14                  |

| FIGURE 27- HDB3 LINE CODE VIOLATION INSERTION14                  |

| FIGURE 28- AMI LINE CODE VIOLATION INSERTION14                   |

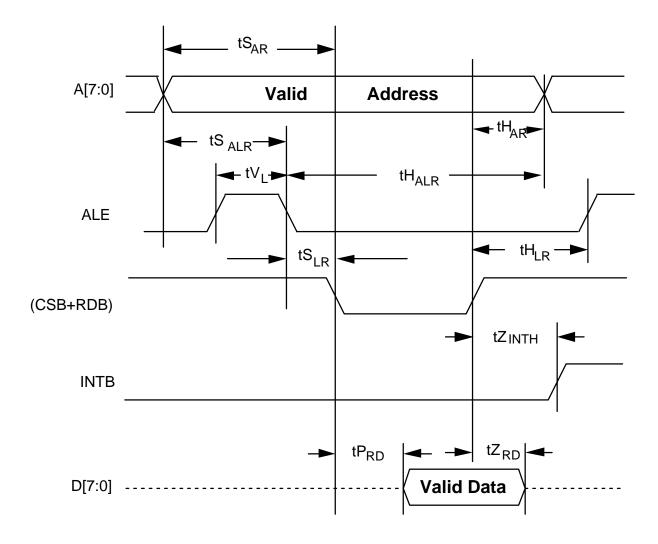

| FIGURE 29- MICROPROCESSOR INTERFACE READ TIMING150               |

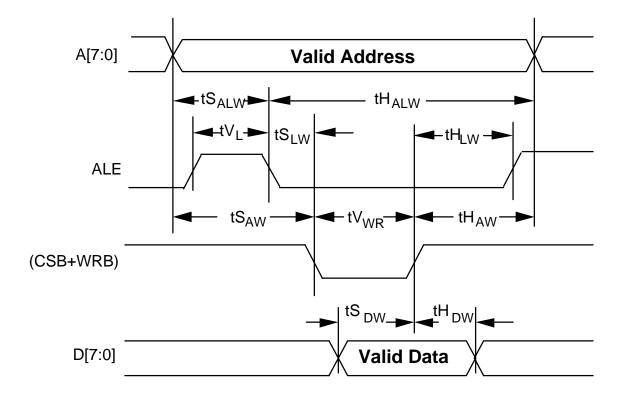

| FIGURE 30- MICROPROCESSOR INTERFACE WRITE TIMING152              |

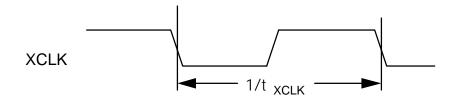

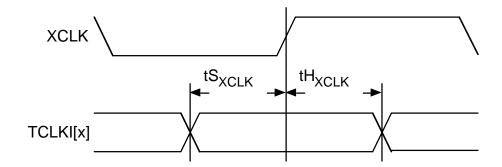

| FIGURE 31 - XCLK INPUT TIMING FOR JITTER ATTENUATION15           |

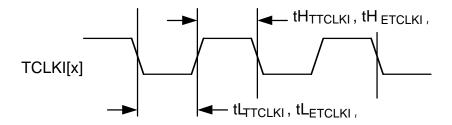

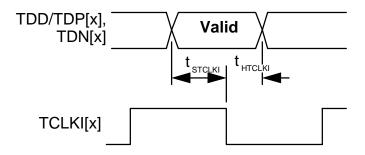

| FIGURE 32-TCLKI INPUT TIMING15                                   |

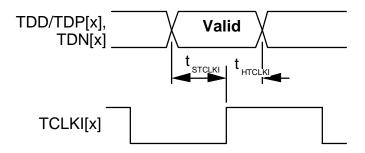

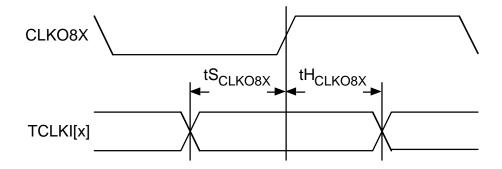

| FIGURE 33- CLKO8X INPUT TIMING DIAGRAM (FIFO NOT IN TX PATH) 150 |

| FIGURE 34- XCLK INPUT TIMING DIAGRAM (FIFO NOT IN TX PATH) 15    |

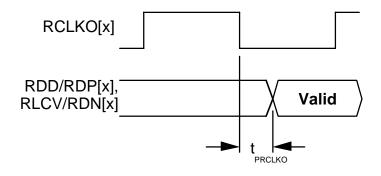

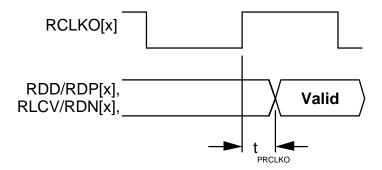

| FIGURE 35- RCLKO OUTPUT TIMING DIAGRAM15                         |

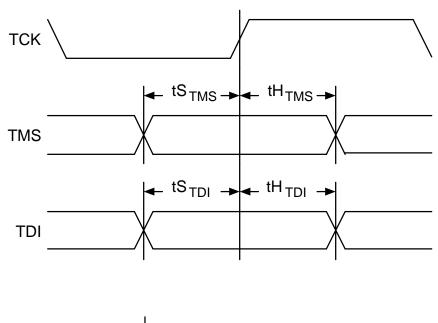

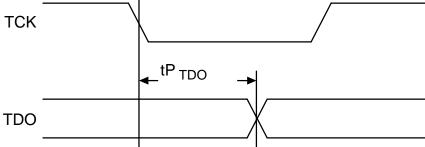

| FIGURE 36- JTAG PORT INTERFACE TIMING160                         |

| FIGURE 37- ANALOG RECEIVE DATA INPUT TIMING DIAGRAM16            |

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

### **LIST OF TABLES**

| TABLE 1  | 3                                                  | 3  |

|----------|----------------------------------------------------|----|

| TABLE 2  | 3                                                  | 5  |

| TABLE 3  | 5                                                  | 1  |

| TABLE 4  | 9                                                  | 0  |

| TABLE 5  | - TEST MODE REGISTER MEMORY MAP11                  | 3  |

| TABLE 6  | 11                                                 | 5  |

| TABLE 7  | 11                                                 | 5  |

| TABLE 8  | - INSTRUCTION REGISTER11                           | 6  |

| TABLE 9  | - BOUNDARY SCAN REGISTER11                         | 7  |

| TABLE 10 |                                                    | 2  |

| TABLE 11 |                                                    | 3  |

| TABLE 12 |                                                    | 4  |

| TABLE 13 |                                                    | 6  |

| TABLE 14 | QDSX ABSOLUTE MAXIMUM RATINGS14                    | 4  |

| TABLE 15 | - QDSX CAPACITANCE                                 | 5  |

| TABLE 16 | - QDSX D.C. CHARACTERISTICS14                      | -6 |

| TABLE 17 | - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 29) |    |

| TABLE 18 | - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 30 |    |

| TABLE 19 | - XCLK INPUT FOR JITTER ATTENUATION (FIGURE 31)15  | 3  |

| TABLE 20 | - TCLKI INPUT TIMING (FIGURE 32)15                 | 4  |

ISSUE 5

| TABLE 21 | - CLKO8X INPUT TIMING (FIFO NOT IN TX PATH) (FIGURE 33) | 156 |

|----------|---------------------------------------------------------|-----|

| TABLE 22 | - XCLK INPUT TIMING (FIFO NOT IN TX PATH) (FIGURE 34)   | 157 |

| TABLE 23 | - RCLKO OUTPUT TIMING (FIGURE 35)                       | 158 |

| TABLE 24 | - JTAG PORT INTERFACE TIMING (FIGURE 36)                | 159 |

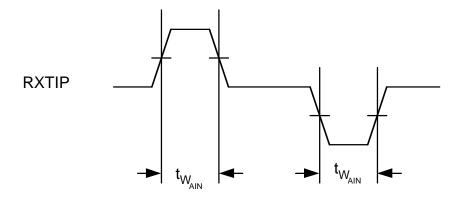

| TABLE 25 | - ANALOG RECEIVE DATA INPUT TIMING (FIGURE 37)          | 161 |

| TABLE 26 | - QDSX ORDERING INFORMATION                             | 163 |

| TABLE 27 | - QDSX THERMAL INFORMATION                              | 163 |

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

#### 1 FEATURES

- Integrates four duplex DSX-1 or CEPT E1 compatible line interface circuits in a single monolithic device. Line format is selected on a per-device basis.

- Provides clock recovery and line performance monitoring in the receivers.

- Provides jitter attenuation and programmable line build out in the transmitters.

- Utilizes digital phase-locked loops for receive and transmit clock derivation without the use of tuned circuits.

- Provides an integrated 8X clock multiplier for generation of required highspeed clocks in applications not requiring jitter attenuation.

- Optionally inserts Alarm Indication Signal (AIS) when loopback modes are enabled. AIS insertion may also be directly controlled via the microprocessor interface.

- Provides a generic microprocessor interface for initial configuration, ongoing control, and status monitoring.

- Generates an interrupt upon detection of any of various alarms, events, or changes in status. Identification of interrupt sources, masking of interrupt sources, and acknowledgment of interrupts is provided via internal registers.

- Provides optional hardware programmed mode which provides external configuration pins when microprocessor access is not available to the device.

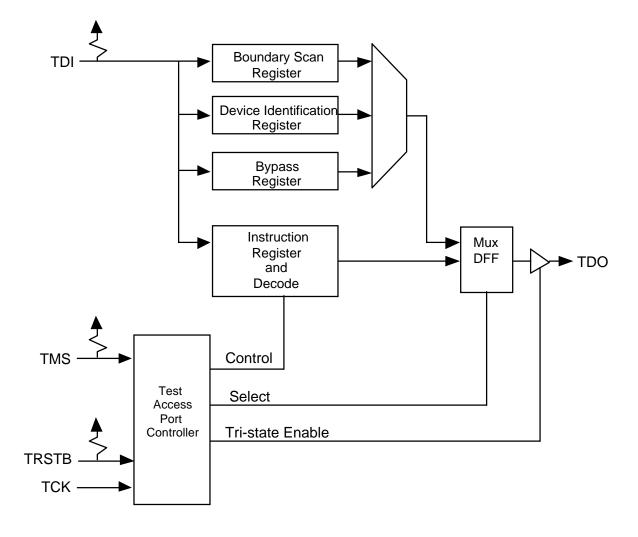

- Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

- Provides seamless interface to PM4344 TQUAD, PM6344 EQUAD, PM8313 D3MX, and PM7344 S/UNI-MPH.

- Low power CMOS technology, 1500 mW power dissipation processing all ones signals on all four quadrants.

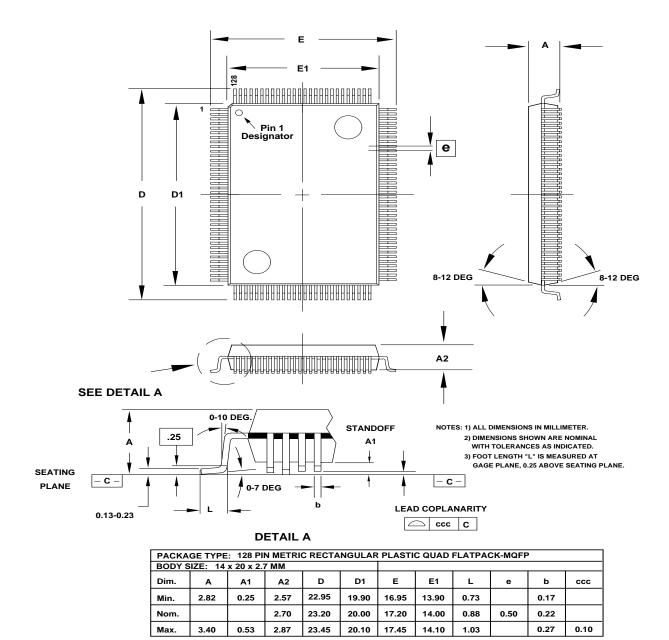

- 128-pin (14mm x 20mm) PQFP package.

#### Each receiver section

- Slices incoming G.703 DSX-1 and CEPT E1 bipolar line signals into digital return-to-zero (RZ) pulses.

- Selectable slicer levels (DSX-1/CEPT E1) to provide improved SNR.

ISSUE 5

- Squelches RZ signals with pulse amplitudes below 140mV and 105mV for CEPT and T1, respectively.

- Typical minimum sensitivity of 50 mV at transformer primary with a 1:2 turns ratio transformer allows for terminating or bridged performance monitoring applications.

- Recovers a 1.544 MHz clock and DS-1 data or a 2.048 MHz clock and E1 data using a digital phase-locked loop to achieve high jitter accommodation.

- Accommodates up to 0.4 UI peak-to-peak, high frequency jitter to satisfy AT&T TR 62411 and ITU-T G.823.

- Optionally outputs either dual rail recovered line pulses or a single rail DS-1/E1 signal.

- Performs B8ZS or AMI decoding when processing a bipolar DS-1 signal and HDB3 or AMI decoding when processing a bipolar E1 signal.

- Detects line code violations (LCVs), B8ZS/HDB3 line code signatures, and 16, 8, or 4 successive zeros.

- Accumulates up to 4095 line code violations (LCVs), for performance monitoring purposes, over accumulation intervals defined by the period between software write accesses to the LCV register.

- Detects loss of signal (LOS), which is defined as 10, 15, 31, 63, or 175 successive zeros.

- Detects both programmable inband loopback activate and deactivate code sequences received in the DS-1 data stream when they are present for 5 seconds. Optionally, enters loopback mode automatically on detection of an inband loopback code.

- Detects any pair of arbitrary inband codes from three to eight bits in length.

- The inband code detection algorithm operates in the presence of a 10-2 bit error rate.

- Programmable to detect CSU (Channel Service Unit), network, and far-end loopback codes.

- Optionally allows jitter attenuation of recovered clock and data, using a 2 X 48 bit FIFO.

- Optionally inserts unframed inband code sequences in place of recovered data.

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

- Detects unframed 2<sup>15</sup>-1 test sequences as defined in ITU-T 0.151 and accumulates bit errors detected using this pseudo-random pattern.

- Optionally inserts unframed 2<sup>15</sup>-1 test sequences in place of recovered data.

#### **Each transmitter section**

- Generates DSX-1 and CEPT E1 compatible pulses with programmable pulse shape using an external 1:1.36 turns ratio transformer.

- Accommodates standard cable types such as ABAM, PIC, and Coaxial.

- Provides an integrated analog pulse driver performance monitor which can provide an interrupt upon detection of failure.

- Allows bipolar violation (BPV) transparent operation for error restoring regenerator applications.

- Allows bipolar violation (BPV) insertion for diagnostic testing purposes.

- Supports all ones transmission for alarm indication signal (AIS) generation.

- Provides a digital phase-locked loop for generation of jitter reduced transmit output timing. The DPLL utilizes a 37.056 MHz master clock for DSX-1 or a 49.152 MHz master clock for CEPT E1 applications.

- Digital phase-locked loop locks 1.544 MHz or 2.048 MHz output timing to the average frequency of the 1.544 MHz or 2.048 MHz jittered transmit input clock.

- Provides a 2 x 48 bit FIFO for jitter attenuation in the transmit path.

- Provides up to 55 dB of jitter attenuation to satisfy AT&T TR 62411, ITU-T G.737, G.738, G.739, and G.742.

- Provides FIFO overrun and underrun indicators.

- Inhibits FIFO overrun and underrun for excessive jitter amplitudes.

- Supports transmission of a programmable unframed inband loopback code sequence.

- Programmable to transmit repetitions of any arbitrary code from three to eight bits in length.

- Accepts either dual rail or single rail DS-1/E1 signals.

- Performs B8ZS or AMI encoding when processing a single rail DS-1 signal and HDB3 or AMI encoding when processing a single rail E1 signal.

ISSUE 5

- Optionally detects inband code sequences in DS-1 transmit streams.

- Optionally inserts unframed 2<sup>15</sup>-1 test sequences in place of input transmit data.

- Optionally detects unframed 2<sup>15</sup>-1 test sequences in the input transmit data.

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

#### **APPLICATIONS**

- T1 or E1 ATM interfaces

- Electronic DSX-1/CEPT E1 Cross-connects

- Digital Access and Cross-connect Systems (DACS)

- Multiplexers

- Channel Service Units (CSUs)

- DSX-1/CEPT E1 Repeaters

- Test Equipment

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

#### 3 **REFERENCES**

- American National Standard for Telecommunications, ANSI T1.102-1992 -"Digital Hierarchy - Electrical Interfaces".

- American National Standard for Telecommunications, ANSI T1.107-1991 -"Digital Hierarchy - Formats Specifications".

- American National Standard for Telecommunications, ANSI T1.403-1989 -"Carrier to Customer Installation - DS1 Metallic Interface Specification".

- American National Standard for Telecommunications. ANSI T1.408-1990 -"Integrated Services Digital Network (ISDN) Primary Rate - Customer Installation Metallic Interfaces Layer 1 Specification".

- 5. Bell Communications Research, TR-TSY-000009 "Asynchronous Digital" Multiplexes Requirements and Objectives", Issue 1, May, 1986.

- Bell Communications Research, TA-TSY-000147 "DS1 Rate Digital Service Monitoring Unit Functional Specification", Issue 1, October, 1987.

- 7. Bell Communications Research, TR-TSY-000170 "Digital Cross-Connect System (DCS) - Requirements and Objectives", Issue 1, November, 1985.

- 8. Bell Communications Research, TR-TSY-000191 "Alarm Indication Signal Requirements and Objectives" Issue 1, May 1986.

- 9. Bell Communications Research, TR-TSY-000303 "Integrated Digital Loop Carrier System Generic Requirements, Objectives, and Interface", Issue 1, Rev. 1, December, 1987.

- 10. Bell Communications Research, TR-TSY-000312 "Functional Criteria for the DS1 Interface Connector", Issue 1, March, 1988.

- 11. Bell Communications Research, TR-TSY-000499 "Transport Systems Generic Requirements (TSGR): Common Requirement", Issue 3, December, 1989.

- 12. AT&T, TR 43801 "Digital Channel Bank Requirements and Objectives", November, 1982.

ISSUE 5

- 13. AT&T, TR 43802 "Digital Multiplexers Requirements and Objectives", July, 1982.

- 14. AT&T, TR 62411 Accunet T1.5 "Service Description and Interface Specification", December, 1990.

- 15. CCITT Red Book, Recommendation Q.516, "Operations and maintenance functions", Vol. VI, Fasc. VI.5, 1984.

- 16. ITU-T Recommendation 0.150, "Digital Test Patterns for Performance Measurements on Digital Transmission Equipment", Oct. 1992.

- 17. ITU-T Recommendation O.151, "Error Performance Measuring Equipment Operating at the Primary Rate and Above", Rev.1, 1992.

- 18. ITU-T Recommendation G.703, "Physical/Electrical Characteristics of Hierarchical Digital Interfaces", Rev.1, 1991.

- 19. ITU-T Recommendation G.704, "Synchronous Frame Structures Used at Primary and Secondary Hierarchical Levels", Rev.1, 1991.

- 20. ITU-T Recommendation G.821, "Error Performance of an International Digital Connection Forming Part of an Integrated Services Digital Network", Blue Book Fasc. III.5, 1988.

- 21. ITU-T Recommendation G.823, "The Control of Jitter and Wander Within Digital Networks Which are Based on the 2048 kbit/s Hierarchy", 1993.

- 22. ITU-T Recommendation O.151, "Error Performance Measuring Equipment Operating at the Primary Rate and Above", Rev. 1, Oct. 1992.

- 23. ITU-T Recommendation 0.162, "Equipment to Perform in Service" Monitoring on 2048, 8448, 34368, and 139264 kbit/s Signals", Rev.1, Oct. 1992.

- 24.ITU-T, Recommendation I.432 "B-ISDN User-Network Interface Physical Layer Specification", August 1992.

ISSUE 5

QUAD T1/E1 LINE INTERFACE DEVICE

#### 4 APPLICATION EXAMPLES

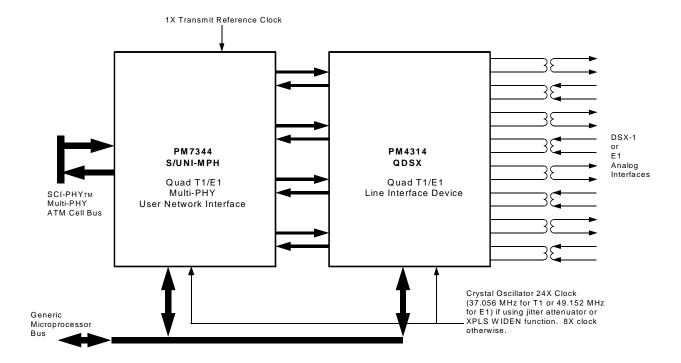

Figure 1 - Example 1. T1 or E1 ATM Interfaces

Example 1 shows the PM4314 QDSX used with the PM7344 S/UNI-MPH to implement a quad T1/E1 UNI where the DS1 or E1 signals are presented on DSX-1 or E1 electrical interfaces.

In this example, the DSX-1 or E1 line interface functions are provided by the QDSX and the DS-1 or E1 framing functions are provided by the S/UNI-MPH. The S/UNI-MPH also provides the ATM cell processing functions associated with the PHY layer, including the implementation of a SCI-PHY multi-PHY interface to the ATM layer device(s). The combination of the QDSX device with the S/UNI-MPH allows both ANSI/ITU compliant DSX-1/E1 analog signals and ATM Forum UNI 3.1 and ITU G.804 compliant DS1/E1 digital signals to be processed.

Jitter attenuation by both the QDSX and the S/UNI-MPH can be performed by supplying a 24X reference clock to the devices. If jitter attenuation is to be executed by the S/UNI-MPH only, then an 8X reference clock is required by the QDSX and a 24X reference clock is required by the S/UNI-MPH. If jitter attenuation is to be executed by the QDSX, then a 24X reference clock must be

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

supplied to it and an 8X reference clock may be supplied to the S/UNI-MPH. If jitter attenuation is not required by either device, then an 8X reference clock may be supplied to both devices.

ISSUE 5

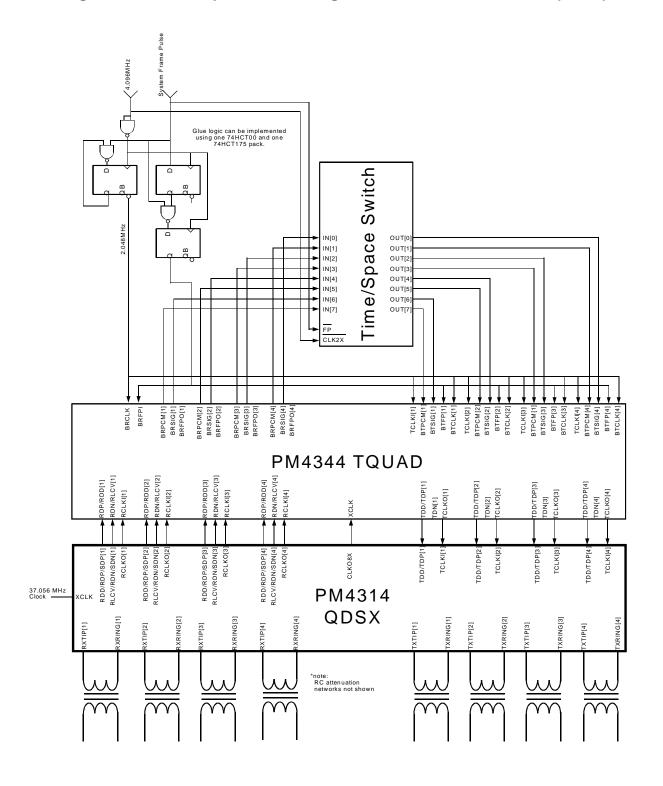

Figure 2 - Example 2. DSX-1 Digital Access Cross Connects (DACs)

**ISSUE 5**

QUAD T1/E1 LINE INTERFACE DEVICE

Example 2 shows a DSX 1/0 Cross-Connect using a PM4314 QDSX, a PM4344 TQUAD, and a Digital Time/Space Switch to implement a simple 1/0 cross-connect. An alternate architecture could use two Digital Time/Space Switches, one as a voice switch and the other as a signaling switch, and 2 TQUADs to cross-connect eight T1s. (Note: a true implementation would require redundancy in the switch core.)

In this example, the TQUAD is programmed to receive and generate the same framing format, using the 2.048 MHz backplane data rate. The "system frame pulse" signal is stretched through the two D-FF into a pulse of 488ns duration, which is used to frame align the data out of each framer through the elastic store and to provide frame alignment indication to the transmitters. The raw system frame pulse signal is used to indicate frame alignment synchronization to the Digital Time/Space Switch. Another D-FF is configured as a toggle to generate a 2.048MHz clock from the system 4.096MHz clock source, synchronized to the system frame pulse. The TQUAD is configured to accept and source unipolar signal from and to the QDSX. As shown, the jitter attenuation is performed in the QDSX and is disabled in the TQUAD.

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

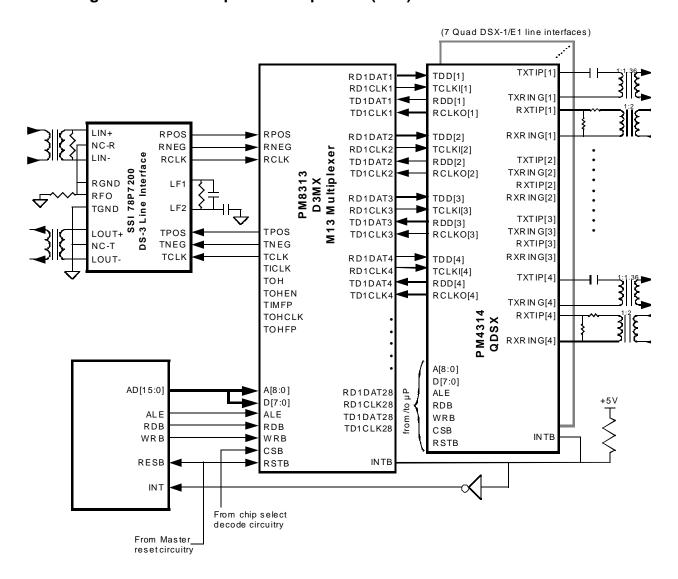

Figure 3 - Example 3. Multiplexers (M13)

Example 3 shows the use of the PM4314 QDSX with the PM8313 D3MX in an M13 Multiplexer/Demultiplexer application. Use of the SSI LIU as illustrated requires that TICLK of the D3MX has a duty cycle of 45% min., 55% max. or better (e.g., using a Connor Winfield S65T3 reference oscillator).

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

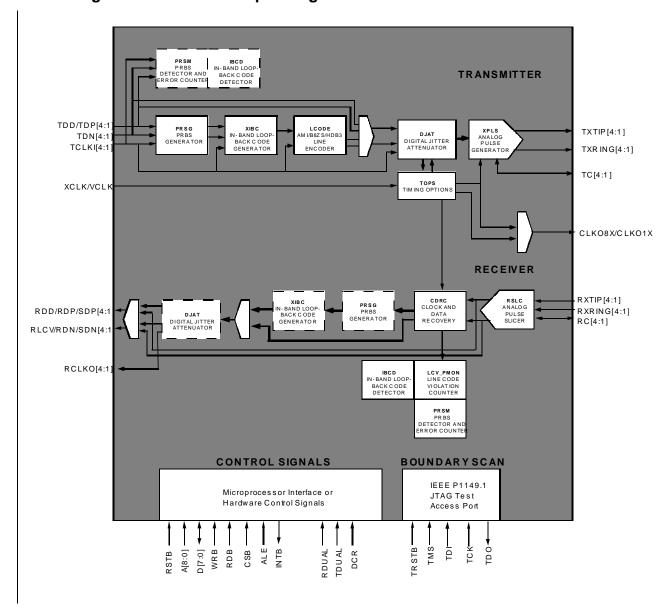

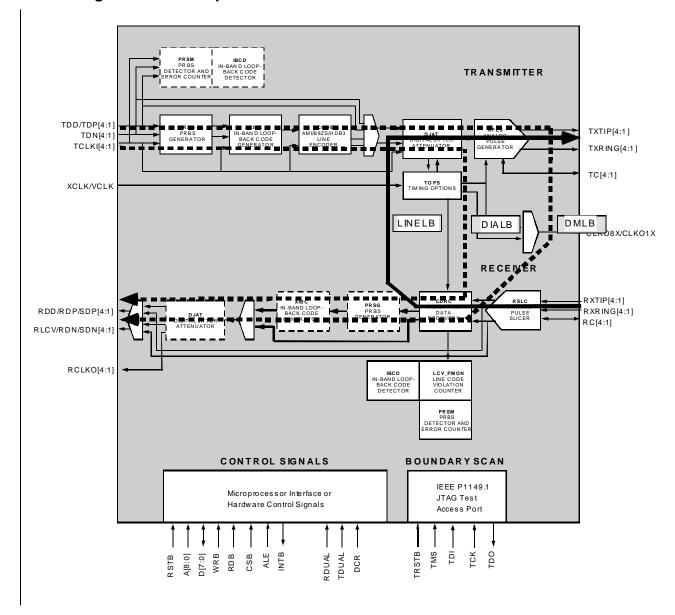

#### 5 BLOCK DIAGRAM

Figure 4 - Normal Operating Mode

#### Note:

Dashed boxes show optional placement of blocks. Default placement of the block is shown in solid boxes.

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

Figure 5 - Loopback Modes

#### Note:

Dashed boxes show optional placement of blocks. Default placement of the block is shown in solid boxes.

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

#### 6 DESCRIPTION

The PM4314 QDSX Quad T1/E1 Line Interface Device is a monolithic integrated circuit that supports DSX-1 and CEPT E1 compatible transmit and receive interfaces for four 1.544 Mbit/s or 2.048 Mbit/s data streams.

In the incoming direction, the DSX-1/E1 signals for each quadrant of the QDSX are first processed by a receive data slicer. The receive data slicer converts the line signal received via a coupling transformer to dual rail RZ digital pulses. Adaptation for attenuation is achieved using an integral peak detector that sets the slicing levels. Through use of passive external attenuation circuitry, either terminated or bridge monitored DSX-1/E1 signal levels can be accommodated. The low signal level condition or signal squelch may be enabled to generate interrupts. Clock and data are recovered from the dual rail RZ digital pulses using a digital phase-locked loop that provides excellent high frequency jitter accommodation. The recovered data is decoded using B8ZS, HDB3, or AMI line code rules and is presented either as a DS-1/E1 stream or presented in an undecoded dual rail NRZ format. Loss of signal and line code violations are detected as well as 8 successive zeros/4 successive zeros, and the B8ZS/HDB3 signature. The presence of programmable inband loopback codes is also detected. These various events or changes in status may be enabled to generate interrupts. Additionally, line code violations are indicated on outputs.

In the outgoing direction, each quadrant of the QDSX may accept either a DS-1/E1 stream to be encoded using B8ZS, HDB3, or AMI line code rules, or it may accept pre-encoded data in dual rail NRZ format. Jitter attenuation is provided by passing outgoing data through a FIFO. A low jitter clock is generated by an integral digital phase-locked loop and is used to read data from the FIFO. FIFO overrun or underrun may be enabled to generate interrupts. Alarm indication signal (all ones) may be substituted for the FIFO data. The digital data is converted to high drive, dual rail RZ pulses that drive the DSX-1/E1 interface through a coupling transformer. The shape of the pulses is user programmable to ensure that the DSX-1/E1 pulse template is met after the signal is passed through different cable lengths or types. Driver performance monitoring is provided and may be enabled to generate interrupts upon driver failure.

The jitter attenuation function can optionally be moved to the receive side. The recovered clock and data is passed through the jitter attenuator before being presented at the digital receive outputs.

**ISSUE 5**

**QUAD T1/E1 LINE INTERFACE DEVICE**

Internal high speed timing for all quadrants of the QDSX is provided by a common 37.056 MHz or 49.152 MHz master clock. This master clock rate is required for applications where QDSX provides jitter attenuation. For applications where QDSX is not required to attenuate jitter, a 12.352 MHz or 16.384 MHz clock may be used as the master clock and used directly as the internal 8X high speed clock.

Diagnostic loopback is provided and the loopback may be invoked past the analog transmit outputs using the driver performance monitors or invoked prior to the conversion to analog. Line loopback with jitter attenuation is provided and may be enabled for automatic operation based on detected inband loopback codes.

The QDSX detects framed or unframed inband loopback code sequences from the received input pulses. Any arbitrary code from three to eight bits in length can be declared to be the activate and deactivate codes by writing to configuration registers. The inband loopback code detector can optionally be moved to the transmit side where it detects inband loopback codes in the unipolar input transmit data stream. For framed inband loopback code sequences, it is expected that the framing bit overwrites the inband loopback code bit.

The QDSX may insert unframed inband loopback code sequences into the transmitted PCM data stream. These codes consist of continuous repetitions of specific bit sequences. Any arbitrary code from three to eight bits in length is programmable by writing to configuration registers. This unframed inband loopback code insertion may optionally be switched to the receive side where it overwrites the data from the slicer.

The QDSX may insert an unframed 2<sup>15</sup>-1 O.151 compatible pseudo-random bit sequence into the transmitted PCM data stream. Optionally, the PRBS insertion may be switched to the receive side where it overwrites the data from the slicer.

The QDSX detects an unframed 2<sup>15</sup>-1 O.151 compatible pseudo-random bit sequence input to the receive slicer. This PRBS detector can operate in the presence of a 10<sup>-2</sup> bit error rate. Bit errors are detected and recorded. The PRBS detector can optionally be switched to the transmit side where it can detect unframed PRBS data from the unipolar input transmit data stream.

The QDSX operates in conjunction with external line coupling transformers, resistors, and capacitors. An external crystal may be used for high speed timing

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

generation. The QDSX is configured, controlled, and monitored using registers that are accessed via a generic microprocessor interface.

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

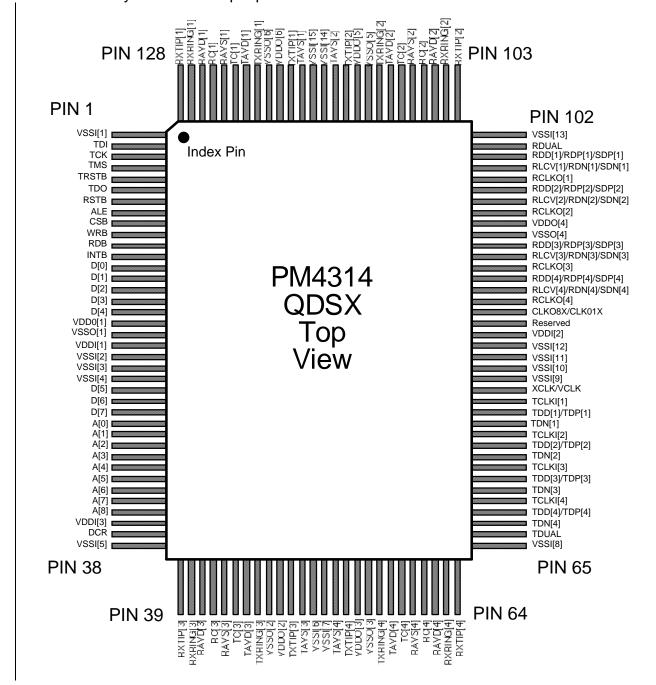

#### 7 PIN DIAGRAM

The QDSX is packaged in a 128-pin plastic QFP package having a body size of 1mm by 20mm and a pin pitch of 0.5 mm.

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

#### **PIN DESCRIPTION** 8

| Pin Name                                | Туре   | Pin<br>No.             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------|--------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXTIP[4] TXTIP[3] TXTIP[2] TXTIP[1]     | Output | 54<br>49<br>113<br>118 | Transmit Bipolar Tip (TXTIP[4:1]). The TXTIP[4:1] outputs are the transmit analog positive pulses. These analog outputs drive an AC signal through an external matching transformer. They must be connected to the positive lead of the transformer primary.  An analog Transmit Monitor Positive point is internally bonded to each of these outputs and is used to monitor the positive pulses on each                                   |

| TXRING[4] TXRING[3] TXRING[2] TXRING[1] | Output | 57<br>46<br>110<br>121 | transmit line.  Transmit Bipolar Ring (TXRING[4:1]). The TXRING[4:1] outputs are the transmit analog negative pulses. These analog outputs drive an AC signal through an external matching transformer. They must be connected to the negative lead of the transformer primary.  An analog Transmit Monitor Negative point is internally bonded to each of these outputs and is used to monitor the negative pulses on each transmit line. |

| TC[4]<br>TC[3]<br>TC[2]<br>TC[1]        | I/O    | 59<br>44<br>108<br>123 | Transmit Reference Decoupling Capacitor (TC[4:1]). These analog bidirectionals provide decoupling for an internal reference generator. They must be connected to an external decoupling capacitor to the corresponding TAVD[4:1].                                                                                                                                                                                                          |

ISSUE 5

| Pin Name  | Туре  | Pin<br>No. | Function                                                                                                                                          |

|-----------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| TDD[4]    | Input | 68         | Transmit Data (TDD[4:1]). When in single-rail                                                                                                     |

| TDD[3]    |       | 71         | mode, these inputs are the NRZ data signals to be transmitted. These inputs can be configured                                                     |

| TDD[2]    |       | 74         | to be active high or active low. These inputs can                                                                                                 |

| TDD[1]    |       | 77         | be sampled on either the rising or falling edges of the corresponding TCLKI[4:1].                                                                 |

| TDP[4]    | Input |            | Transmit Positive Data (TDP[4:1]). When in dual-                                                                                                  |

| TDP[3]    |       |            | rail mode, these inputs are the NRZ positive data signals to be transmitted. These inputs can be                                                  |

| TDP[2]    |       |            | sampled on either the rising or falling edges of                                                                                                  |

| TDP[1]    |       |            | the corresponding TCLKI[4:1].                                                                                                                     |

| TDN[4]    | Input | 67         | Transmit Negative Data (TDN[4:1]). When in                                                                                                        |

| TDN[3]    |       | 70         | dual-rail mode, these inputs are the NRZ negative data signals to be transmitted. These                                                           |

| TDN[2]    |       | 73         | inputs can be sampled on either the rising or                                                                                                     |

| TDN[1]    |       | 76         | falling edges of the corresponding TCLKI[4:1]. These input pins are ignored if the device is configured for single-rail (unipolar) transmit mode. |

| TCLKI[4]  | Input | 69         | Transmit Clock (TCLKI[4:1]). This clock should be                                                                                                 |

| TCLKI[3]  |       | 72         | 1.544 MHz for DS1 or 2.048 MHz for E1 data streams and is used to sample the corresponding                                                        |

| TCLKI[2]  |       | 75         | TDP/TDD[4:1] and TDN[4:1] signals.                                                                                                                |

| TCLKI[1]  |       | 78         |                                                                                                                                                   |

| RXTIP[4]  | Input | 64         | Receive Bipolar Tip (RXTIP[4:1]). The                                                                                                             |

| RXTIP[3]  |       | 39         | RXTIP[4:1] inputs are the receive analog positive pulses. They must be connected to the positive                                                  |

| RXTIP[2]  |       | 103        | lead of the transformer secondary through a                                                                                                       |

| RXTIP[1]  |       | 128        | passive attenuation network.                                                                                                                      |

| RXRING[4] | I/O   | 63         | Receive Bipolar Ring (RXRING[4:1]). The                                                                                                           |

| RXRING[3] |       | 40         | RXRING[4:1] bidirectional pins provide DC bias to an external isolation transformer. They must                                                    |

| RXRING[2] |       | 104        | be connected to the negative lead of the                                                                                                          |

| RXRING[1] |       | 127        | transformer secondary and to a decoupling capacitor to RAVS[4:1].                                                                                 |

ISSUE 5

| Pin Name                                                                             | Туре                 | Pin<br>No.             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------|----------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RC[4]<br>RC[3]<br>RC[2]<br>RC[1]                                                     | I/O                  | 61<br>42<br>106<br>125 | Receive Peak Hold R-C Network (RC[4:1]). The RC[4:1] analog bidirectional pins must be connected to an external parallel resistor/capacitor network to RAVS[4:1]. This network is necessary to the operation of the internal peak detector that tracks the incoming signal level.                                                                                                                                                                                                                                                                                                                                                                                                    |

| RDD[4] RDD[3] RDD[2] RDD[1]  RDP[4] RDP[3] RDP[2] RDP[1] SDP[4] SDP[3] SDP[2] SDP[1] | Output Output Output | 89<br>92<br>97<br>100  | Receive Digital Data (RDD[4:1]). When configured for unipolar outputs, the RDD[4:1] NRZ outputs contain the sampled DS-1 or E1 data which has been decoded by AMI, B8ZS, or HDB3 line code rules. RDD[4:1] outputs can be updated on either the falling or rising RCLKO[4:1] edge.  Receive Digital Positive Pulse (RDP[4:1]). When configured for bipolar outputs, the RDP[4:1] NRZ outputs contain sampled bipolar positive pulses. RDP[4:1] outputs can be updated on either the falling or rising RCLKO[4:1] edge.  Sliced Positive Line Pulse (SDP[4:1]). A positive pulse on the SDP[4:1] outputs corresponds to the sampled positive pulse excursion on the RXTIP[4:1] input. |

ISSUE 5

| Pin Name                                     | Туре   | Pin<br>No.           | Function                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|--------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLCV[4]<br>RLCV[3]<br>RLCV[2]<br>RLCV[1]     | Output | 88<br>91<br>96<br>99 | Receive Line Code Violation Indication (RLCV[4:1]). When configured for unipolar outputs, the RLCV[4:1] NRZ outputs pulse whenever a line code violation or excess zeroes condition is detected. RDP[4:1] outputs can be updated on either the falling or rising RCLKO[4:1] edge.                                                                                    |

| RDN[4]<br>RDN[3]<br>RDN[2]<br>RDN[1]         | Output |                      | Receive Digital Positive Pulse (RDN[4:1]). When configured for bipolar outputs, the RDN[4:1] NRZ outputs contain sampled bipolar negative pulses. RDN[4:1] outputs can be updated on either the falling or rising RCLKO[4:1] edge.                                                                                                                                   |

| SDN[4]<br>SDN[3]<br>SDN[2]<br>SDN[1]         | Output |                      | Sliced Negative Line Pulse (SDN[4:1]). A positive pulse on the SDN[4:1] outputs corresponds to the sampled negative pulse excursion on the RXTIP[4:1] input.                                                                                                                                                                                                         |

| RCLKO[4]<br>RCLKO[3]<br>RCLKO[2]<br>RCLKO[1] | Output | 87<br>90<br>95<br>98 | Recovered Clock Output (RCLKO[4:1]). RCLKO[4:1] is the clock recovered from the RXTIP[4:1] and RXRING[4:1] input signals. RCLKO[4:1] are 2mA output pads. Care must be taken in board layouts to guarantee the integrity of the clock signals.                                                                                                                       |

| XCLK/                                        | Input  | 79                   | Crystal Clock Input (XCLK). This signal supplies the timing reference for the high-speed clocks required by many portions of the QDSX. When jitter attenuation is required, XCLK is nominally a 24X clock (37.056 MHz for T1, 49.152 MHz for E1). When jitter attenuation is not required, XCLK can be driven by an 8X clock (12.352 MHz for T1, 16.384 MHz for E1). |

| VCLK                                         |        |                      | Vector Clock (VCLK). The VCLK signal is used during QDSX production test to verify internal functionality.                                                                                                                                                                                                                                                           |

ISSUE 5

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKO8X/  | Output | 86         | 8X Clock Output (CLKO8X).                                                                                                                                                                                                                                                                                                                                                                                         |

|          |        |            | This output is the internal 8X high-speed clock derived from the digital jitter attenuator, or derived by dividing down the 24X XCLK input. It is used as the reference clock to generate the transmit analog pulse template. The CLKO8X signal is generated from Quadrant 1.                                                                                                                                     |

|          |        |            | 1X Clock Output (CLKO1X).                                                                                                                                                                                                                                                                                                                                                                                         |

| CLKO1X   | Output |            | When an 8X clock is provided on XCLK, this is the internal 8X clock divided by 8. This output can be used to synchronously clock in data on TDP[4:1]/TDD[4:1] and TDN[4:1] by connecting it to TCLKI[4:1].                                                                                                                                                                                                        |

| DCR      | Input  | 37         | Disable Clock Recovery Input (DCR). When set high, the DCR input will disable clock recovery in the QDSX and enable the SDP[4:1] and SDN[4:1] sliced line pulse outputs. This input is logically "ORed" with the DCR register bits.                                                                                                                                                                               |

| TDUAL    | Input  | 66         | Transmit Dual-Rail Input Select (TDUAL). This input selects whether the QDSX expects single-rail or dual-rail input transmit data. The TDUAL input is logically "ORed" with the TDUAL register bits. When TDUAL is set high, the TDP[4:1] and TDN[4:1] inputs are enabled. When both the TDUAL input pin and register bits are set low, then the TDD[4:1] inputs are enabled and the TDN[4:1] inputs are ignored. |

ISSUE 5

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDUAL    | Input | 101        | Receive Dual-Rail Output Select (RDUAL). This input selects whether the QDSX generates single-rail or dual-rail outputs from its receiver section. The RDUAL input is logically "ORed" with the RDUAL register bits. When RDUAL is set high, the RDP[4:1] and RDN[4:1] outputs are enabled. When both the RDUAL input pin and register bits are set low, then line decoding is performed on the receive slicer outputs and the RDD[4:1] and RLCV[4:1] outputs are enabled. The state of the DCR input pin or the DCR register bits takes precedence over the RDUAL state. |

| CSB      | Input | 9          | Active low Chip Select (CSB). This signal must be low to enable QDSX register accesses. CSB must go high at least once after a powerup to clear internal test modes. If CSB is not used, then it should be tied to an inverted version of RSTB, in which case RDB and WRB determine register access.                                                                                                                                                                                                                                                                      |

| WRB      | Input | 10         | Active low Write Strobe (WRB). This signal is pulsed low to enable a QDSX register write access. The D[7:0] bus is clocked into the addressed register on the rising edge of WRB while CSB is low.                                                                                                                                                                                                                                                                                                                                                                        |

| RDB      | Input |            | Active low Read Enable (RDB). This signal is pulsed low to enable a QDSX register read access. The QDSX drives the D[7:0] bus with the contents of the addressed register while RDB and CSB are both low.                                                                                                                                                                                                                                                                                                                                                                 |

ISSUE 5

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                         |

|----------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[8]     | Input  | 35         | Address Bus (A[8:0]). This bus selects specific                                                                                                                                                                                                                  |

| A[7]     |        | 34         | registers during QDSX register accesses.                                                                                                                                                                                                                         |

| A[6]     |        | 33         |                                                                                                                                                                                                                                                                  |

| A[5]     |        | 32         |                                                                                                                                                                                                                                                                  |

| A[4]     |        | 31         |                                                                                                                                                                                                                                                                  |

| A[3]     |        | 30         |                                                                                                                                                                                                                                                                  |

| A[2]     |        | 29         |                                                                                                                                                                                                                                                                  |

| A[1]     |        | 28         |                                                                                                                                                                                                                                                                  |

| A[0]     |        | 27         |                                                                                                                                                                                                                                                                  |

|          |        |            |                                                                                                                                                                                                                                                                  |

| ALE      | Input  | 8          | Address Latch Enable (ALE). This signal latches the address bus contents, A[8:0], when low, allowing the QDSX to be interfaced to a multiplexed address/data bus. When ALE is high, the address latches are transparent. ALE has an integral pull-up resistor.   |

| INTB     | Output | 12         | Active low Open-Drain Interrupt (INTB). This signal goes low when an unmasked interrupt event is detected on any of the internal interrupt sources. Note that INTB will remain low until all active unmasked interrupt sources are acknowledged at their source. |

ISSUE 5

| Pin Name | Туре               | Pin<br>No. | Function                                                                                                                                                                                                                                        |

|----------|--------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7]     | I/O                | 26         | Bidirectional Data Bus (D[7:0]). This bus is used                                                                                                                                                                                               |

| D[6]     |                    | 25         | during QDSX read and write accesses.                                                                                                                                                                                                            |

| D[5]     |                    | 24         |                                                                                                                                                                                                                                                 |

| D[4]     |                    | 17         |                                                                                                                                                                                                                                                 |

| D[3]     |                    | 16         |                                                                                                                                                                                                                                                 |

| D[2]     |                    | 15         |                                                                                                                                                                                                                                                 |

| D[1]     |                    | 14         |                                                                                                                                                                                                                                                 |

| D[0]     |                    | 13         |                                                                                                                                                                                                                                                 |

|          |                    |            |                                                                                                                                                                                                                                                 |

| RSTB     | Input              | 7          | Active low Reset (RSTB). This signal is set low to asynchronously reset the QDSX. RSTB is a Schmitt-trigger input with an integral pull-up resistor.                                                                                            |

| TCK      | Input              | 3          | Test Clock (TCK). This signal provides timing for test operations that can be carried out using the IEEE P1149.1 test access port.                                                                                                              |

| TMS      | Input              | 4          | Test Mode Select (TMS). This signal controls the test operations that can be carried out using the IEEE P1149.1 test access port. TMS is sampled on the rising edge of TCK. TMS has an integral pull up resistor.                               |

| TDI      | Input              | 2          | Test Data Input (TDI). This signal carries test data into the QDSX via the IEEE P1149.1 test access port. TDI is sampled on the rising edge of TCK. TDI has an integral pull up resistor.                                                       |

| TDO      | Tristate<br>Output | 6          | Test Data Output (TDO). This signal carries test data out of the QDSX via the IEEE P1149.1 test access port. TDO is updated on the falling edge of TCK. TDO is a tristate output which is inactive except when scanning of data is in progress. |

ISSUE 5

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                        |

|----------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRSTB    | Input  | 5          | Active low Test Reset (TRSTB). This signal provides an asynchronous QDSX test access port reset via the IEEE P1149.1 test access port. TRSTB is a Schmitt triggered input with an integral pull up resistor. When not being used, TRSTB should be tied to RSTB. |

| VDDO[6]  | Power  | 119        | Pad Ring Power Pins (VDDO[6:1]). These pins                                                                                                                                                                                                                     |

| VDDO[5]  |        | 112        | must be connected to a common well decoupled +5V DC power supply together with the                                                                                                                                                                              |

| VDDO[4]  |        | 94         | VDDI[3:1], TAVD[4:1], and RAVD[4:1] pins. Care                                                                                                                                                                                                                  |

| VDDO[3]  |        | 55         | must be taken to avoid coupling noise between these pins.                                                                                                                                                                                                       |

| VDDO[2]  |        | 48         | triese piris.                                                                                                                                                                                                                                                   |

| VDDO[1]  |        | 18         |                                                                                                                                                                                                                                                                 |

| VDDI[3]  | Power  | 36         | Core Power Pins (VDDI[3:1]). These pins must be                                                                                                                                                                                                                 |

| VDDI[2]  |        | 84         | connected to a common well decoupled +5V DC power supply together with the VDDO[6:1],                                                                                                                                                                           |

| VDDI[1]  |        | 20         | TAVD[4:1], and RAVD[4:1] pins. Care must be taken to avoid coupling noise between these pins.                                                                                                                                                                   |

| VSSO[6]  | Ground | 120        | Pad Ring Ground Pins (VSSO[6:1]). These pins                                                                                                                                                                                                                    |

| VSSO[5]  |        | 111        | must be connected to a common ground together with the VSSI[15:1], TAVS[4:1], and RAVS[4:1]                                                                                                                                                                     |

| VSSO[4]  |        | 93         | pins. Care must be taken to avoid coupling noise                                                                                                                                                                                                                |

| VSSO[3]  |        | 56         | between these pins.                                                                                                                                                                                                                                             |

| VSSO[2]  |        | 47         |                                                                                                                                                                                                                                                                 |

| VSSO[1]  |        | 19         |                                                                                                                                                                                                                                                                 |

ISSUE 5

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                |  |  |  |

|----------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VSSI[15] | Ground | 116        | Core Ground Pins (VSSI[15:1]). These pins must                                                                                                                                                                                          |  |  |  |

| VSSI[14] |        | 115        | be connected to a common ground together wit the VSSO[6:1], TAVS[4:1], and RAVS[4:1]pins.                                                                                                                                               |  |  |  |

| VSSI[13] |        | 102        | Care must be taken to avoid coupling noise                                                                                                                                                                                              |  |  |  |

| VSSI[12] |        | 83         | between these pins. These pins also act as                                                                                                                                                                                              |  |  |  |

| VSSI[11] |        | 82         | thermal-dissipation grounds, and as such should be thermally well-connected to a ground plane.                                                                                                                                          |  |  |  |

| VSSI[10] |        | 81         | , g .                                                                                                                                                                                                                                   |  |  |  |

| VSSI[9]  |        | 80         |                                                                                                                                                                                                                                         |  |  |  |

| VSSI[8]  |        | 65         |                                                                                                                                                                                                                                         |  |  |  |

| VSSI[7]  |        | 52         |                                                                                                                                                                                                                                         |  |  |  |

| VSSI[6]  |        | 51         |                                                                                                                                                                                                                                         |  |  |  |

| VSSI[5]  |        | 38         |                                                                                                                                                                                                                                         |  |  |  |

| VSSI[4]  |        | 23         |                                                                                                                                                                                                                                         |  |  |  |

| VSSI[3]  |        | 22         |                                                                                                                                                                                                                                         |  |  |  |

| VSSI[2]  |        | 21         |                                                                                                                                                                                                                                         |  |  |  |

| VSSI[1]  |        | 1          |                                                                                                                                                                                                                                         |  |  |  |

| TAVD[4]  | TX     | 58         | Transmit Analog Power Pins (TAVD[4:1]). These                                                                                                                                                                                           |  |  |  |

| TAVD[3]  | Analog | 45         | pins provide the +5 V supply to the transmit analog line interfaces. The transmit analog line                                                                                                                                           |  |  |  |

| TAVD[2]  | Power  | 109        | interface remains in a low power consumption                                                                                                                                                                                            |  |  |  |

| TAVD[1]  |        | 122        | state after reset until enabled. TAVD[4:1] must be connected to a common well decoupled +5 V DC power supply together with the VDDO[6:1], VDDI[3:1], and RAVD[4:1] pins. Care must be taken to avoid coupling noise between these pins. |  |  |  |

| TAVS[4]  | TX     | 53         | Transmit Analog Ground Pins (TAVS[4:1]). These                                                                                                                                                                                          |  |  |  |

| TAVS[3]  | Analog | 50         | pins provide the ground supply to the transmit analog line interface. TAVS[4:1] must be                                                                                                                                                 |  |  |  |

| TAVS[2]  | Ground | 114        | connected to a common ground together with the                                                                                                                                                                                          |  |  |  |

| TAVS[1]  |        | 117        | VSSO[6:1], VSSI[15:1], and RAVS[4:1] pins. Care must be taken to avoid coupling noise between these pins.                                                                                                                               |  |  |  |

ISSUE 5

**QUAD T1/E1 LINE INTERFACE DEVICE**

| Pin Name                                 | Туре                   | Pin<br>No.             | Function                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAVD[4]<br>RAVD[3]<br>RAVD[2]<br>RAVD[1] | RX<br>Analog<br>Power  | 62<br>41<br>105<br>126 | Receive Analog Power Pins (RAVD[4:1]). These pins provide the +5 V DC power supply to the receive analog line interface. RAVD[4:1] must be connected to a common well decoupled +5 V DC power supply together with the VDDO[6:1], VDDI[3:1], and TAVD[4:1] pins. Care must be taken to avoid coupling noise between these pins. |

| RAVS[4]<br>RAVS[3]<br>RAVS[2]<br>RAVS[1] | RX<br>Analog<br>Ground | 60<br>43<br>107<br>124 | Receive Analog Ground Pins (RAVS[4:1]). These pins provide the ground supply to the receive analog line interface. RAVS[4:1] must be connected to a common ground together with the VSSO[6:1], VSSI[15:1], and TAVS[4:1] pins. Care must be taken to avoid coupling noise between these pins.                                   |

# **Notes on Pin Description:**

- VDDI[3:1] and VSSI[15:1] are the +5 V and ground connections, respectively, for the core circuitry of the device. VDDO[6:1] and VSSO[6:1] are the +5 V and ground connections, respectively, for the pad ring circuitry of the device. TAVD[4:1] and TAVS[4:1] are the +5 V and ground connections, respectively, for the transmit analog circuitry of the device. RAVD[4:1] and RAVS[4:1] are the

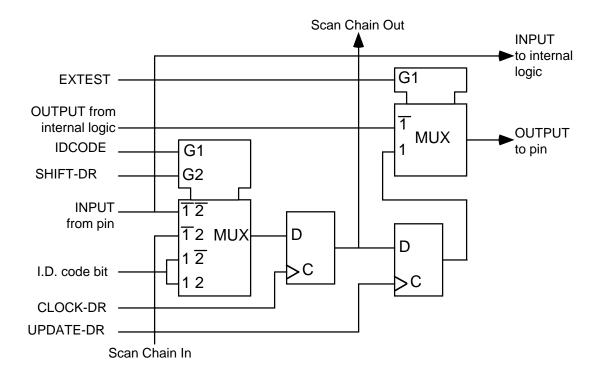

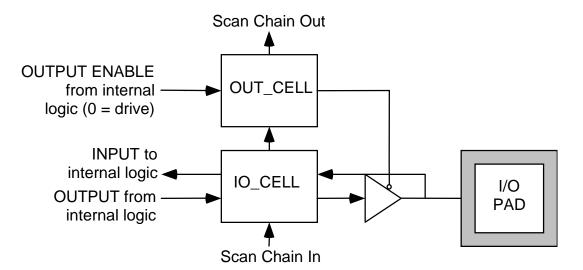

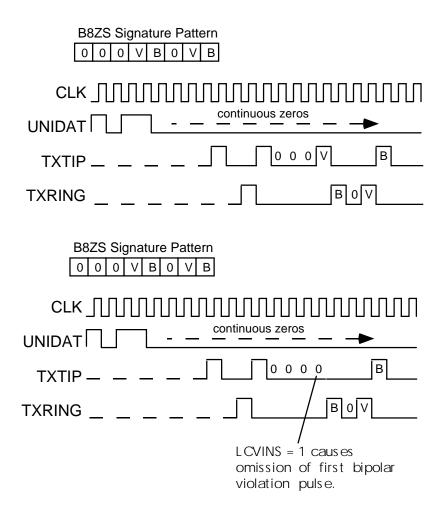

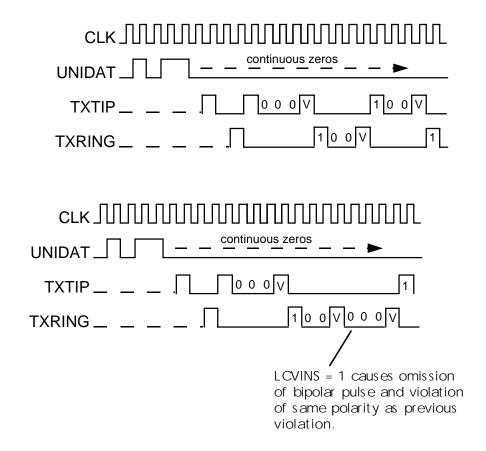

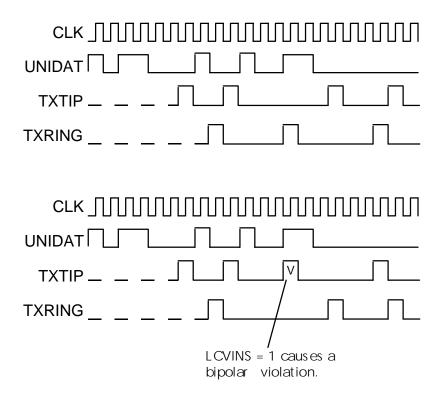

- +5 V and ground connections, respectively, for the receive analog circuitry of the device. These power supply connections must all be utilized and must all connect to a common +5 V or ground rail, as appropriate. There is no low impedance connection within the PM4314 QDSX between the core, pad ring, transmit analog, and receive analog supply rails. Failure to properly make these connections may result in improper operation or damage to the device. Care must be taken to avoid coupling of noise into the transmit and receive analog supply rails.