# HT9580 Character Pager Controller

### **Features**

- Operating voltage: 2.4V~3.5V

- Temperature range: -30°C to +85°C

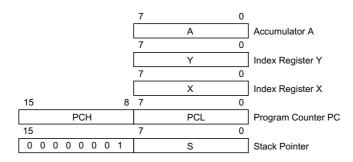

- low power, high performance M6502 core

- low power crystal oscillator control

512/1200/2400 bps data rate operation

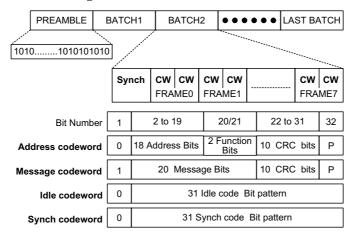

- "CCIR Radio Paging Code No.1" (POCSAG) compatible

- 76.8kHz crystal for all available data rates

- · High/low system clock switching capability

- 44 Kbytes program ROM

- 848 bytes global data RAM

- Internal 2 Mbits Character ROM

- 256 Kbits internal SRAM

- External option up to 2 Mbits Character ROM or 2 Mbits SRAM

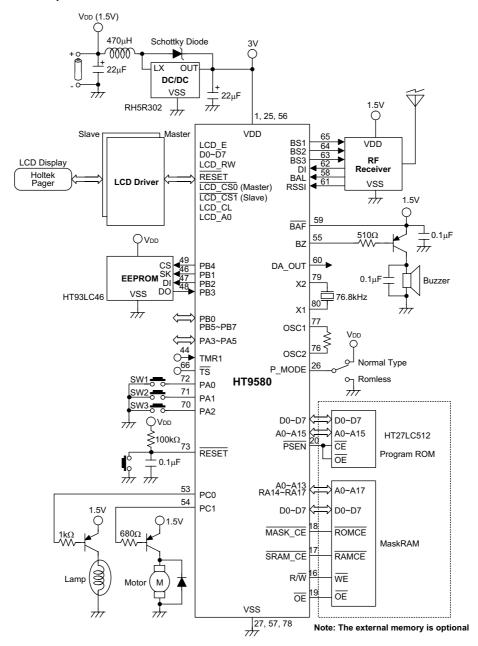

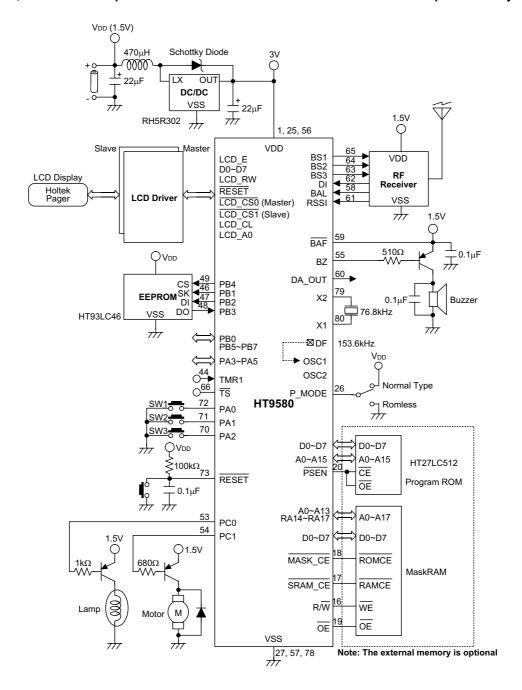

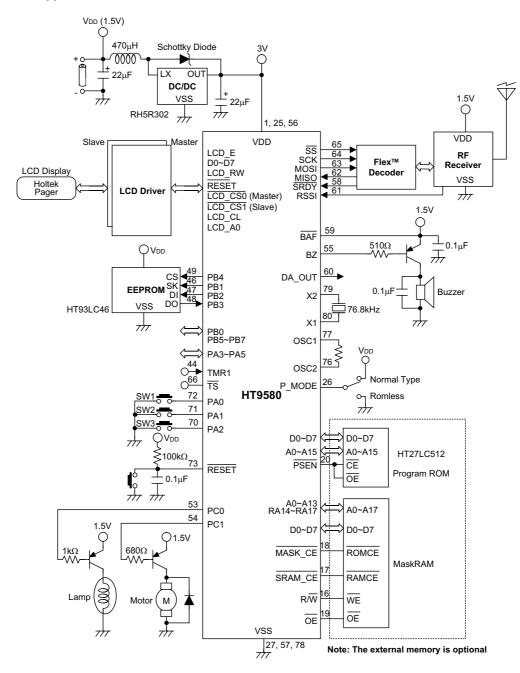

- SED15X(KSX), MC141X and HD66410 series LCD driver compatible interface option

- 46 bytes message buffer

- One 16-bit timer and one 8-bit timer

- Internal 2Hz or 1Hz RTC or Real Time Clock option

- Single buzzer generator output (BZ) with duty cycle control

- low current HALT mode operation

- 16-bit watchdog timer

- Built-in data filter (16-times over-sampling) and bit clock recovery

- Advanced synchronization algorithm

- 2-bit random and (optional) 4-bit burst error correction for address and message

- Up to 6 user addresses and 6 user frames, independently programmable

- 3 RF power-on timing control pins and Received data inversion (optional)

- Built in SPI circuit

- Out-of-range condition indicator

- One internal 8-bit D/A converter

- · Battery fail and battery low detection

- 80-pin LQFP package

### **General Description**

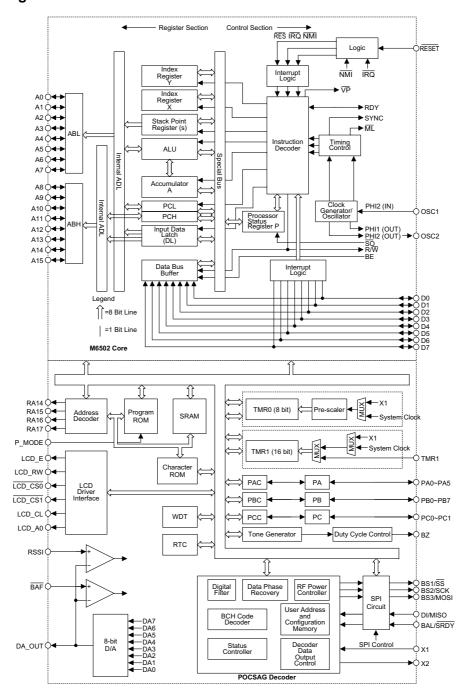

The HT9580 is a high performance pager controller which can be used for Chinese Pager system applications. The HT9580 4-in-1 Character Pager Controller combines a POCSAG decoder with a M6502 microprocessor core, 2 Mbits Character ROM and 256 Kbits SRAM to provide both high decoder performance and excellent system flexibility. The decoder utilizes a 2-bit random error correction algorithm and

therefore provides excellent decoder sensitivity. The controller contains a full function pager decoder at a 512, 1200, 2400 bps data rates. Using an M6502 core takes advantage of a flexible external control interface, LCD driver chips and abundant programming resources from worldwide providers. The internal SPI would communicate with SPI of FLEX  $^{\rm TM}$  high speed pager decoder.

### **Block Diagram**

2

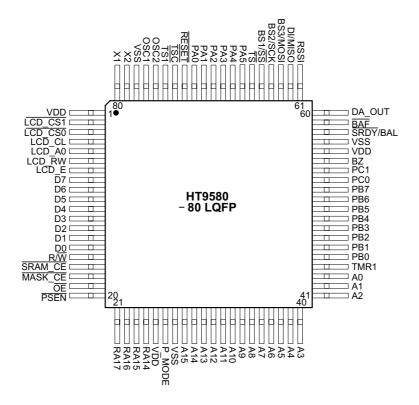

### **Pin Assignment**

3

# **Pin Description**

| Pin No.    | Pin Name                 | I/O | Description                                                                                                                                                                                                                                           |

|------------|--------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 25, 56  | VDD                      | _   | Positive power supply                                                                                                                                                                                                                                 |

| 2          | LCD_CS1                  | О   | LCD driver chip select control (for slave LCD driver)                                                                                                                                                                                                 |

| 3          | LCD_CS0                  | О   | LCD driver chip select control (for master LCD driver)                                                                                                                                                                                                |

| 4          | LCD_CL                   | О   | LCD driver clock output                                                                                                                                                                                                                               |

| 5          | LCD_A0                   | О   | LCD driver data/command select control                                                                                                                                                                                                                |

| 6          | LCD_RW                   | O   | LCD Driver Read/Write signal output                                                                                                                                                                                                                   |

| 7          | LCD_E                    | O   | LCD driver enable clock control                                                                                                                                                                                                                       |

| 15~8       | D0~D7                    | I/O | 8-bit, tristate, bidirectional I/O data bus.                                                                                                                                                                                                          |

| 16         | $R/\overline{W}$         | О   | Read/Write signal output                                                                                                                                                                                                                              |

| 17         | SRAM_CE                  | О   | SRAM chip Enable. This signal is generated from the HT9580 to provide read or write timing for external SRAM devices. (See Application Circuit)                                                                                                       |

| 18         | MASK_CE                  | О   | Mask ROM Chip Enable. This signal is generated from the HT9580 to provide read timing for external Mask ROM devices. (See Application Circuit)                                                                                                        |

| 19         | $\overline{\mathrm{OE}}$ | O   | Mask ROM or SRAM Output Enable. This signal is generated from the HT9580 to provide read timing for external Mask ROM and SRAM devices. (See Application Circuit)                                                                                     |

| 20         | PSEN                     | О   | Program Store Enable. This pin is used to connect the $\overline{OE}$ and $\overline{CE}$ pins of the external 44 Kbytes program ROM when the "MODE_P" internal pad is connected to VSS. (See note)                                                   |

| 21~24      | RA17~RA14                | О   | Extended address bus pins                                                                                                                                                                                                                             |

| 26         | P_MODE                   | I   | Internal or external program ROM selection without pull-high resistor. If the pin connects to VDD, the internal program ROM will be fetched (normal type), otherwise the external program ROM will be fetched when the pin connects to VSS (Romless). |

| 27, 57, 78 | VSS                      | _   | Negative power supply                                                                                                                                                                                                                                 |

| 43~28      | A0~A15                   | O   | Address bus pins. This is used for memory and I/O exchanges on the data bus.                                                                                                                                                                          |

| 44         | TMR1                     | I   | Schmitt trigger input for timer1 counter with pull-high resisor.                                                                                                                                                                                      |

| 45~52      | PB0~PB7                  | I/O | General Input/Output Port B. The input cell structures can be selected as CMOS or CMOS with pull-high resistors.                                                                                                                                      |

| 53~54      | PC0~PC1                  | I/O | General Input/Output Port C. The input cell structures can be selected as CMOS or CMOS with pull-high resistors.                                                                                                                                      |

| 55         | BZ                       | O   | Buzzer non-inverting BZ output                                                                                                                                                                                                                        |

| Pin No.                 | Pin Name                  | I/O    | Description                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------------------|---------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                         | BAL                       | I      | Battery voltage detector input with pull-high resistor.                                                                                                                                                                                                                                               |  |  |  |  |

| 58                      | SRDY                      | I      | SPI slave ready — This slave ready pin is a Schmitt trigger input with pull-high resistor. When the slave initiates the SPI transfer, a high to low transition activates an interrupt. When the master initiates the SPI transfer, a high to low transition trigger the master to start the transfer. |  |  |  |  |

| 59                      | $\overline{\mathrm{BAF}}$ | I      | Battery fail indication input, active low.                                                                                                                                                                                                                                                            |  |  |  |  |

| 60                      | DA_OUT                    | О      | D/A converter output. This pin is an 8-bit D/A analog output                                                                                                                                                                                                                                          |  |  |  |  |

| 61                      | RSSI                      | I      | RSSI output from IF circuit. This pin should be pulled high or low externally when this pin is not used.                                                                                                                                                                                              |  |  |  |  |

| CO                      | DI                        | I      | POCSAG code input serial data. CMOS input with pull-high resistor.                                                                                                                                                                                                                                    |  |  |  |  |

| 62                      | MISO                      | I      | SPI master-in-slave-out — this is the data input with pull-high resistor for SPI communications.                                                                                                                                                                                                      |  |  |  |  |

|                         | BS3                       | О      | PLL power control enable, CMOS output                                                                                                                                                                                                                                                                 |  |  |  |  |

| 63                      | MOSI                      | О      | SPI master-out-slave-in — this is the data output for SPI communications.                                                                                                                                                                                                                             |  |  |  |  |

|                         | BS2                       | О      | RF quick charge control enable, CMOS output                                                                                                                                                                                                                                                           |  |  |  |  |

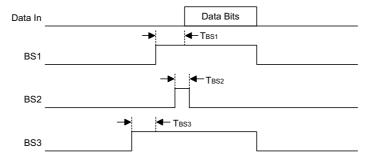

| MOSI  BS2  64  SCK  BS1 |                           | I/O    | SPI serial clock — the SCK signal is used to synchronize the datransfer. If HT9580 is in the master mode, the SCK is outp clock. Otherwise, SCK is input clock if HT9580 is in the slamode.                                                                                                           |  |  |  |  |

|                         | BS1                       | О      | Pager receiver power control enable output, CMOS output                                                                                                                                                                                                                                               |  |  |  |  |

| 65                      | $\overline{	ext{SS}}$     | О      | SPI slave select — this signal is used to enable the SPI slave for transfer.                                                                                                                                                                                                                          |  |  |  |  |

| 66                      | $\overline{	ext{TS}}$     | I      | Decoder test mode input pin, active low with pull-high resistor.                                                                                                                                                                                                                                      |  |  |  |  |

| 72~67                   | PA0~PA5                   | I/O    | General Input/Output Port A. These ports can be programmed to have a wake-up capability for applications in keyboard operations or as normal I/O. Also the input cell structures are all Schmitt trigger types and can be selected between CMOS or CMOS with pull-high resistors.                     |  |  |  |  |

| 73                      | $\overline{	ext{RESET}}$  | I      | Schmitt trigger reset input, active low.                                                                                                                                                                                                                                                              |  |  |  |  |

| 74                      | TSC                       | I      | $\mu C$ test mode input pin, active low with internal pull-high resistor. The test circuit will be activated when this pin pulls low.                                                                                                                                                                 |  |  |  |  |

| 75                      | TS1                       | I      | Decoder test mode input pin, active low with pull-high resistor. The internal test mode will be activated when this pin pulls low.                                                                                                                                                                    |  |  |  |  |

| 77                      | OSC1                      | I      | OSC1 and OSC2 are connected to an RC network to form a main                                                                                                                                                                                                                                           |  |  |  |  |

| 76                      | OSC2                      | О      | clock oscillator                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 80<br>79                | X1<br>X2                  | I<br>O | X1 and X2 are connected to a crystal to form an internal low power clock oscillator (32.768kHz, 76.8kHz, or 153.6kHz)                                                                                                                                                                                 |  |  |  |  |

5

### **Absolute Maximum Ratings**

| Supply Voltage0.3V to 3.6V                                          | Storage Temperature $-55^{\circ}$ C to $150^{\circ}$ C                  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------|

| Input VoltageV $_{\rm SS}$ –0.5V to $V_{\rm DD}$ +0.5V              | Operating Temperature $-30^{\circ}\mathrm{C}$ to $85^{\circ}\mathrm{C}$ |

| Current Drain Per Pin Excluding V <sub>DD</sub> and V <sub>SS</sub> | 10mA                                                                    |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

### **D.C. Characteristics**

Ta=25°C

| G 1.1              | D 4                              | ,        | Test Conditions                                | 3.41                | T.   | D/F                 | TT *4 |

|--------------------|----------------------------------|----------|------------------------------------------------|---------------------|------|---------------------|-------|

| Symbol             | Parameter                        | $V_{DD}$ | Conditions                                     | Min.                | Тур. | Max.                | Unit  |

| $V_{\mathrm{DD}}$  | Operating Voltage                |          | 3V application                                 | 2.4                 | 3.0  | 3.5                 | V     |

| $I_{DD}$           | Operating Current                | 3V       | No load,<br>OSC1=1MHz<br>$f_{X1}=76.8kHz$      |                     | 300  |                     | μΑ    |

| $I_{STP}$          | HALT Mode Current                | 3V       | No load, $\mu C$ clock stop, $f_{X1}$ =76.8kHz |                     | _    | 100                 | μΑ    |

| $V_{\mathrm{IL}}$  | Input low Voltage for I/O Port   | 3V       |                                                |                     | _    | $0.3 \times V_{DD}$ | V     |

| V <sub>IH</sub>    | Input High Voltage for I/O Port  | 3V       | 3V                                             |                     | _    | 3                   | v     |

| $V_{\rm IL1}$      | Input low Voltage                | 3V       | _                                              | 0                   | _    | $0.3 \times V_{DD}$ | V     |

| $V_{\mathrm{IH}1}$ | Input High Voltage               | 3V       | _                                              | $0.7 \times V_{DD}$ | _    | 3                   | V     |

| $V_{\rm IL2}$      | Input low Voltage (BAF)          | 3V       | _                                              | 0                   | _    | 0.9                 | V     |

| $V_{\mathrm{IH}2}$ | Input High Voltage (BAF)         | 3V       | _                                              | 1.0                 | _    | 3                   | V     |

| $V_{\mathrm{OL}}$  | Output low Voltage               | 3V       | _                                              | _                   | _    | 0.4                 | V     |

| $V_{OH}$           | Output High Voltage              | 3V       | _                                              | 2.3                 | _    | _                   | V     |

| $I_{OL}$           | I/O Port Sink Current            | 3V       | $V_{\rm OL}$ =0.3 $V$                          | 2.0                 | 3.6  | _                   | mA    |

| $I_{OH}$           | I/O Port Source Current          | 3V       | $V_{\mathrm{OH}}$ =2.7 $V$                     | -1.2                | -2.2 |                     | mA    |

| $I_{\mathrm{OL1}}$ | BZ, PC0~PC1 Sink Current         | 3V       | $V_{\rm OL}$ =0.3 $V$                          | 2                   | 4.5  | _                   | mA    |

| $I_{\mathrm{OH1}}$ | BZ, PC0~PC1 Source Current       | 3V       | $V_{\mathrm{OH}}$ =2.7 $V$                     | -1.5                | -2.5 | _                   | mA    |

| $I_{\mathrm{OL2}}$ | BS1, BS2, BS3 Sink Current       | 3V       | $V_{\rm OL}$ =0.3 $V$                          | 350                 | _    | _                   | μΑ    |

| $I_{ m OH2}$       | BS1, BS2, BS3 Source Current     | 3V       | $V_{\mathrm{OH}}$ =2.7 $V$                     | -1.0                | _    | _                   | mA    |

| R <sub>OSC</sub>   | RC Oscillator Resistor           | 3V       | f <sub>OSC</sub> =1MHz                         |                     | 51   | _                   | kΩ    |

| $R_{\mathrm{PH}}$  | I/O Port Pull-high<br>Resistance | 3V       | _                                              | 100                 | 250  |                     | kΩ    |

### A.C. Characteristics

| т |   |   | 0  | _ | _ | _ |

|---|---|---|----|---|---|---|

| 1 | я | = | 7. | n | ~ | ı |

| G11               | D                               | Test     | Conditions | ъл:    | Т    | М     | Unit |  |

|-------------------|---------------------------------|----------|------------|--------|------|-------|------|--|

| Symbol            | Parameter                       | $V_{DD}$ | Conditions | Min.   | Тур. | Max.  | Unit |  |

| $f_{OSC1}$        | Main Clock (RC OSC)             | 3V       |            | 76.8   | 1000 | 2000  | kHz  |  |

| D <sub>OSC1</sub> | Main Clock Duty Cycle           | 3V       | _          | 40     | 50   | 60    | %    |  |

| $f_{X1}$          | Pager Clock Input (Crystal OSC) | 3V       | _          | 32.768 | 76.8 | 153.6 | kHz  |  |

| $t_{ m RESET}$    | RESET Input Pulse Width         | _        | _          | 1      | _    | _     | ms   |  |

### **Functional Description**

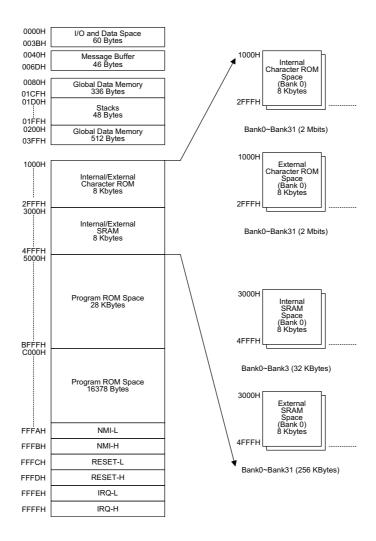

### **Memory map**

## HT9580 memory mapping table (I/O and data space)

| Address         | Register<br>Name                   | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | State on<br>POR |

|-----------------|------------------------------------|-----------|-----------|----------|----------|---------|---------|---------|---------|-----------------|

| 0000H           | Config.                            | HALT      | CLK SEL   | OSC MOD  | LPM      | RTC     | BZ CLK  | MDUT    | MGEN    | 0001 0000       |

| 0001H           | WDT-TMR                            | X         | X         | TMR0_PR1 | TMR0_PR0 | WDTEN   | WS2     | WS1     | WS0     | 0000 0111       |

| 0002H           | CLR WDT                            | X         | X         | X        | X        | X       | X       | X       | X       | uuuu uuuu       |

| 0003H           | BZ-L                               | BZL7      | BZL6      | BZL5     | BZL4     | BZL3    | BZL2    | BZL1    | BZL0    | 0000 0000       |

| 0004H           | BZ-H                               | BZH7      | BZH6      | BZH5     | BZH4     | BZH3    | BZH2    | BZH1    | BZH0    | 0000 0000       |

| 0005H           | INT ctrl                           | 0         | 0         | 0        | RTCEN    | ORMSK   | RTCMSK  | TM1IMSK | TM0IMSK | 0000 1111       |

| 0006H           | INT flag                           | 0         | RTC FG    | DR FG    | BF FG    | WDTOVFG | OR FG   | TM10VFG | TM0OVFG | 0000 0000       |

| 0007H           | TMRC                               | TMR1MOD   | X         | TMR1CLK  | TMR0CLK  | TMR1EDG | TMR0EDG | TMR1EN  | TMR0EN  | 0000 0000       |

| 0008H           | TMR1L                              | TM1D7     | TM1D6     | TM1D5    | TM1D4    | TM1D3   | TM1D2   | TM1D1   | TM1D0   | uuuu uuuu       |

| 0009H           | TMR1H                              | TM1D15    | TM1D14    | TM1D13   | TM1D12   | TM1D11  | TM1D10  | TM1D9   | TM1D8   | uuuu uuuu       |

| 000AH           | TMR0                               | TM0D7     | TM0D6     | TM0D5    | TM0D4    | TM0D3   | TM0D2   | TM0D1   | TM0D0   | uuuu uuuu       |

| 000BH           | PA data                            | X         | X         | PA5      | PA4      | PA3     | PA2     | PA1     | PA0     | uu11 1111       |

| 000CH           | PB data                            | PB7       | PB6       | PB5      | PB4      | PB3     | PB2     | PB1     | PB0     | 1111 1111       |

| 000DH           | PC data                            | X         | X         | X        | X        | X       | X       | PC1     | PC0     | uuuu uu11       |

| 000EH           | PAC                                | X         | X         | PAC5     | PAC4     | PAC3    | PAC2    | PAC1    | PAC0    | uu11 1111       |

| 000FH           | PBC                                | PBC7      | PBC6      | PBC5     | PBC4     | PBC3    | PBC3    | PBC1    | PBC0    | 1111 1111       |

| 0010H           | PCC                                | X         | X         | X        | X        | X       | X       | PCC1    | PCC0    | uuuu uu11       |

| 0011H           | PA WUE                             | X         | X         | PAWUE5   | PAWUE4   | PAWUE3  | PAWUE2  | PAWUE1  | PAWUE0  | uu00 0000       |

| 0012H           | PA IM                              | X         | X         | PAIM5    | PAIM4    | PAIM3   | PAIM2   | PAIM1   | PAIM0   | uu11 1111       |

| 0013H           | PB IM                              | PBIM7     | PBIM6     | PBIM5    | PBIM4    | PBIM3   | PBIM2   | PBIM1   | PBIM0   | 1111 1111       |

| 0014H           | PC IM                              | X         | X         | X        | X        | X       | X       | PCIM1   | PCIM0   | uuuu uu11       |

| 0015H           | MROM-BP                            | BP_MODM1  | BP_MODM0  | M_BP5    | M_BP4    | M_BP3   | M_BP2   | M_BP1   | M_BP0   | 0000 0000       |

| 0016H           | SRAM-BP                            | BP_MODS1  | BP_MODS0  | S_BP5    | S_BP4    | S_BP3   | S_BP2   | S_BP1   | S_BP0   | 0000 0000       |

| 0017H           | LCD_CTRL                           | LCD-CHIP1 | LCD-CHIP0 | LCD-CLK  | CLK-MOD  | LCD-CS1 | LCD-CS0 | LCD-A0  | LCD-WRB | 0000 1101       |

| 0018H           | LCD_CMD                            | LCD_D7    | LCD_D6    | LCD_D5   | LCD_D4   | LCD_D3  | LCD_D2  | LCD_D1  | LCD_D0  | uuuu uuuu       |

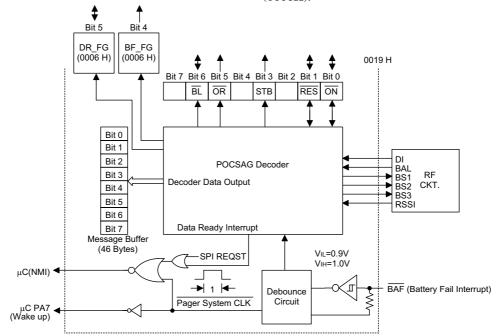

| 0019H           | Decoder<br>Control/<br>flag        | X         | BL        | OR       | X        | STB     | X       | RES     | ON      | uu0u uu01       |

| 001AH~<br>002EH | Decoder<br>Configuration<br>Memory |           |           |          |          |         |         |         |         | uuuu uuuu       |

| 002FH           | D/A-L                              | DA7       | DA6       | DA5      | DA4      | DA3     | DA2     | DA1     | DA0     | 0000 0000       |

| 0030H           | D/A-H                              | X         | X         | X        | X        | X       | D/A_PD  | RSSI    | BAT     | uuuu u1uu       |

| 0031H           | Buffer<br>Status                   | MSG_END   | X         | count_5  | count_4  | count_3 | count_2 | count_1 | count_0 | 0uuu uuuu       |

| 0032H           | SPI-CONFIG                         | S/M       | LEN1      | LEN0     | REQST    | SPIFG   | CLK_EDG | SPI_EN  | START   | 0111 1000       |

| 0033H           | SPI-SPEED                          | SP7       | SP6       | SP5      | SP4      | SP3     | SP2     | SP1     | SP0     | 0000 0000       |

| 0034H           | SPI-OUT3                           | D7        | D6        | D5       | D4       | D3      | D2      | D1      | D0      | 0000 0000       |

| 0035H           | SPI-OUT2                           | D7        | D6        | D5       | D4       | D3      | D2      | D1      | D0      | 0000 0000       |

| 0036H           | SPI-OUT1                           | D7        | D6        | D5       | D4       | D3      | D2      | D1      | D0      | 0000 0000       |

| 0037H           | SPI-OUT0                           | D7        | D6        | D5       | D4       | D3      | D2      | D1      | D0      | 0000 0000       |

| 0038H           | SPI-IN3                            | D7        | D6        | D5       | D4       | D3      | D2      | D1      | D0      | 0000 0000       |

| 0039H           | SPI-IN2                            | D7        | D6        | D5       | D4       | D3      | D2      | D1      | D0      | 0000 0000       |

| 003AH           | SPI-IN1                            | D7        | D6        | D5       | D4       | D3      | D2      | D1      | D0      | 0000 0000       |

| 003BH           | SPI-IN0                            | D7        | D6        | D5       | D4       | D3      | D2      | D1      | D0      | 0000 0000       |

## HT9580 memory attribute table (I/O and data space)

| Address         | Register<br>Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | State on<br>POR |

|-----------------|------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|

| 0000H           | Config.                            | R/W   | 0001 0000       |

| 0001H           | WDT-TMR                            | X     | X     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | 0000 0111       |

| 0002H           | CLR WDT                            | W     | W     | W     | W     | W     | W     | W     | W     | uuuu uuuu       |

| 0003H           | BZ-L                               | R/W   | 0000 0000       |

| 0004H           | BZ-H                               | R/W   | 0000 0000       |

| 0005H           | INT ctrl                           | 0     | 0     | 0     | R/W   | R/W   | R/W   | R/W   | R/W   | 0000 1111       |

| 0006H           | INT flag                           | 0     | R/W   | R/W   | R     | R/W   | R/W   | R/W   | R/W   | 0000 0000       |

| 0007H           | TMRC                               | R/W   | X     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | 0000 0000       |

| 0008H           | TMR1L                              | R/W   | uuuu uuuu       |

| 0009H           | TMR1H                              | R/W   | uuuu uuuu       |

| 000AH           | TMR0                               | R/W   | uuuu uuuu       |

| 000BH           | PA data                            | X     | X     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | uuuu uuuu       |

| 000CH           | PB data                            | R/W   | uuuu uuuu       |

| 000DH           | PC data                            | X     | X     | X     | X     | X     | X     | R/W   | R/W   | uuuu uuuu       |

| 000EH           | PAC                                | X     | X     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | uu11 1111       |

| 000FH           | PBC                                | R/W   | 1111 1111       |

| 0010H           | PCC                                | X     | X     | X     | X     | X     | X     | R/W   | R/W   | uuuu uu11       |

| 0011H           | PA WUE                             | X     | X     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | uu00 0000       |

| 0012H           | PA IM                              | X     | X     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | uu00 0000       |

| 0013H           | PB IM                              | R/W   | 0000 0000       |

| 0014H           | PC IM                              | X     | X     | X     | X     | X     | X     | R/W   | R/W   | uuuu uu00       |

| 0015H           | MROM-BP                            | R/W   | 0000 0000       |

| 0016H           | SRAM-BP                            | R/W   | 0000 0000       |

| 0017H           | LCD_CTRL                           | R/W   | 0000 1101       |

| 0018H           | LCD_CMD                            | R/W   | uuuu uuuu       |

| 0019H           | Decoder<br>Control/<br>flag        | X     | R/W   | R     | X     | R     | X     | R/W   | R/W   | uu0u uu01       |

| 001AH~<br>002EH | Decoder<br>Configuration<br>Memory | R/W   | uuuu uuuu       |

| 002FH           | D/A-L                              | R/W   | 0000 0000       |

| 0030H           | D/A-H                              | X     | X     | X     | X     | X     | R/W   | R     | R     | uuuu u1uu       |

| 0031H           | Buffer<br>Status                   | R     | X     | R     | R     | R     | R     | R     | R     | 0uuu uuuu       |

| 0032H           | SPI-CONFIG                         | R/W   | R/W   | R/W   | R     | R     | R/W   | R/W   | R/W   | 0111 1000       |

| 0033H           | SPI-SPEED                          | R/W   | 0000 0000       |

| 0034H           | SPI-OUT3                           | R/W   | 0000 0000       |

| 0035H           | SPI-OUT2                           | R/W   | 0000 0000       |

| 0036H           | SPI-OUT1                           | R/W   | 0000 0000       |

| 0037H           | SPI-OUT0                           | R/W   | 0000 0000       |

| 0038H           | SPI-IN3                            | R     | R     | R     | R     | R     | R     | R     | R     | 0000 0000       |

| 0039H           | SPI-IN2                            | R     | R     | R     | R     | R     | R     | R     | R     | 0000 0000       |

| 003AH           | SPI-IN1                            | R     | R     | R     | R     | R     | R     | R     | R     | 0000 0000       |

| 003BH           | SPI-IN0                            | R     | R     | R     | R     | R     | R     | R     | R     | 0000 0000       |

Note: "R" Read Only

"W" Write Only

"R/W" Read or Write

"X" N/A

### Configuration register

| A | Address | Register<br>Name | Bit 7 | Bit 6   | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | State on<br>POR |

|---|---------|------------------|-------|---------|---------|-------|-------|--------|-------|-------|-----------------|

|   | H0000   | Config.          | HALT  | CLK_SEL | OSC_MOD | LPM   | RTC   | BZ_CLK | MDUT  | MGEN  | 0001 0000       |

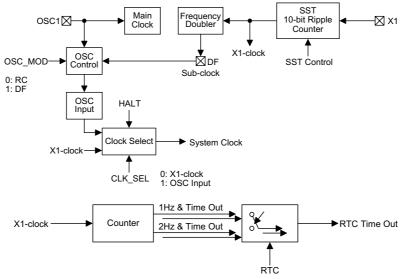

### Oscillator configuration

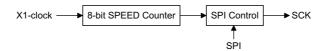

There are two clock source input pins on the chip, the main clock and the pager decoder input clock. The main clock is generated by an RC network. The system clock may be the OSC input or the X1-clock depending on bit "CLK\_SEL". The pager decoder input clock comes from two external pins, X1 and X2. The frequency of the sub-clock will be double that of the X1, X2 input clock. The OSC1 main clock will be generated from an RC network that needs an external resistor (see Application Circuit). The system clock may be X1-clock, DF or RC clock. If no higher frequency (RC) is needed, the external resistor between OSC1 and OSC2 can be removed. The system clock can be switched by bit "CLK\_SEL". If "CLK\_SEL"=0 (POR State), the system clock will be X1-clock. In other cases, with "CLK\_SEL"=1, the OSC input clock will be the system clock. The clock switching function will assist software programmers to change the  $\mu C$  system clock within an adequate time if necessary. The "OSC\_MOD" bit selects the OSC input clock to be either RC or DF. If "OSC\_MOD" is set to "low" then the RC configuration is selected, otherwise the DF application is selected. The programmer should note that the condition of "CLK\_SEL", "HALT" and "OSC\_MOD" assures that the system clock is working properly. It is recommended that the OSC clock source is either DF or RC. If DF and RC are necessary, it is required to switch the system clock to X1-clock before switching between DF and RC. Then switch the system clock back to the OSC input by using bit CLK\_SEL if the switching action of DF and RC is complete. Before enter HALT mode, the system clock must select X1-clock.

The HT9580 will generate two RTC frequencies, 1Hz and 2Hz respectively, determined by bit RTC. If the bit is logic low, the 1Hz RTC frequency will be selected, otherwise the 2Hz RTC frequency will be selected. The RTC counter is enabled/disabled by bit RTCEN and can be masked or not masked as determined by the bit RTCMSK of the interrupt control register

RTC block diagram

10

(0005H). If the RTC counter is enabled, the RTC counter will start to count. The RTC counter source clock is the X1-clock, so the X1 clock setting via by SPF12, SPF13 and SPF14 should be correct.

In order to guarantee that the system clock has started and stabilized, the SST (System Start-up Timer) provides an extra delay of 1024 system clock pulse when the system is powered up.

|     | 1                     | 0                     |

|-----|-----------------------|-----------------------|

| RTC | Select 2Hz as the RTC | Select 1Hz as the RTC |

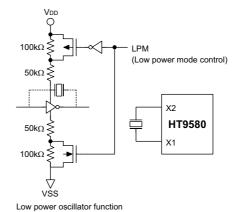

The low power oscillator of the pager decoder input clock should be crystal type. The decoder subsystem low power oscillator, on the other hand, is of a crystal type which is designed with a power on start-up function to reduce the stabilization time of the oscillator. This start-up function is enabled by bit "LPM" which is initially set high at power on reset, and should be cleared to low so as to enable the low-power oscillator function. The oscillator configuration is running in the low power mode.

The system clock oscillator can be enabled/disabled by the register bit, "HALT". The system clock circuit is powered down, when the bit is set to high. On the other hand, the system clock

low power oscillator

circuit is powered up, when the bit is low. When this bit is set high, the CPU is also stopped. When this bit is cleared low, the CPU core returns to its normal operation. After this is set HIGH by the software, it may also be cleared low when reset, interrupt  $(\overline{IRQ} \text{ or } \overline{NMI})$ , RTC timeout, and port wake-up conditions are met.

|      | 0                      | 1                            |

|------|------------------------|------------------------------|

| HALT | System clock<br>enable | System clock<br>powered down |

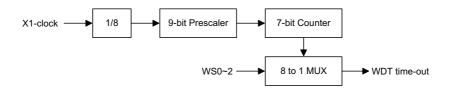

The WDT is a 16-bit counter and sourced by the

### WDT-TMR (Watchdog timer) register

| Address | Register<br>Name | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | State on<br>POR |

|---------|------------------|-------|-------|----------|----------|-------|-------|-------|-------|-----------------|

| 0001H   | WDT-TMR          | X     | X     | TMR0_PR1 | TMR0_PR0 | WDTEN | WS2   | WS1   | WS0   | 0000 0011       |

| 0002H   | CLR WDT          | X     | X     | X        | X        | X     | X     | X     | X     | uuuu uuuu       |

sub-clock divided by 8. The counter is segmented as a 9-bit prescaler and a 7-bit user programmable counter. The input clock is first divided by 512 (9-stage) to get the nominal time-out period. The output of the 9-bit pre-scaler can then be divided by a 7-bit programmable counter to generate the longer watchdog time-out depending on the user's requirements. The 7-bit programmable counter is controlled by 3 register bits, WS0~2. The watchdog timer is enabled/disabled by a control bit WDTEN. To prevent the overflow of this watchdog timer, a clear-WDT operation should

be executed before the timer overflows. The clear-WDT operation is to write any number to the register, CLRWDT (0002H). When the watchdog timer overflows (checked by bit 3 of 0006H "WDTOVFG"), the program counter is set to FFFC H and FFFD H to read the program start vector. The definitions of the control bits are listed below.

|       | 1                         | 0                          |

|-------|---------------------------|----------------------------|

| WDTEN | Enable the watchdog timer | Disable the watchdog timer |

The WDT 7-bit counter is programmed by bits WS0~WS2. The division ratio for the counter is listed in the table.

| WS2 | WS1 | WS0 | Division<br>Ratio |

|-----|-----|-----|-------------------|

| 0   | 0   | 0   | 1:1               |

| 0   | 0   | 1   | 1:2               |

| 0   | 1   | 0   | 1:4               |

| 0   | 1   | 1   | 1:8               |

| 1   | 0   | 0   | 1:16              |

| 1   | 0   | 1   | 1:32              |

| 1   | 1   | 0   | 1:64              |

| 1   | 1   | 1   | 1:128             |

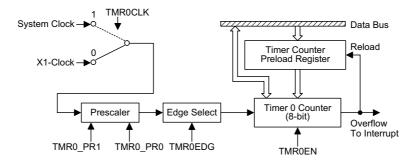

The other pair "TMR0\_PR0" and "TMR0\_PR1" are used to select the prescaler ratio for timer0. The definition is shown in the table.

| TMR0_PR1 | TMR0_PR0 | TMR0<br>Prescaler<br>Ratio |

|----------|----------|----------------------------|

| 0        | 0        | 1/4                        |

| 0        | 1        | 1/8                        |

| 1        | 0        | 1/16                       |

| 1        | 1        | 1/32                       |

### **Buzzer generator registers**

| Address | Register<br>Name | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | State on<br>POR |

|---------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|

| 0003H   | BZ-L             | BZL7  | BZL6  | BZL5  | BZL4  | BZL3  | BZL2  | BZL1  | BZL0  | 0000 0000       |

| 0004H   | BZ-H             | BZH7  | BZH6  | BZH5  | BZH4  | BZH3  | BZH2  | BZH1  | BZH0  | 0000 0000       |

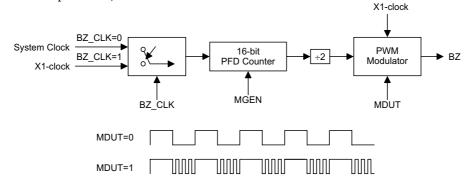

The buzzer generator is composed of a 16-bit PFD counter and a duty cycle control. The counter value is set by two registers, namely BZ-H and BZ-L. The source for this generator may be the system clock or the X1-clock. The buzzer generator is enabled/disabled by the register bit "MGEN" in the configuration register(0000H). When this bit is set high, the buzzer generator is activated. There is another bit in the configuration register(0000H) which controls the buzzer output volume, bit "MDUT". If the bit is logic high, the output of the BZ will be modulated by the X1-clock. The

clock source of the buzzer is selected by bit "BZ\_CLK". When BZ\_CLK=0, the clock source is the system clock. On the other hand, when BZ\_CLK=1, the value of the selector will be the X1-clock.

The truth table for enabling/disabling the buzzer generator is shown in the table.

|      | 1 | 0                            |

|------|---|------------------------------|

| MGEN |   | Disable the buzzer generator |

When BZ-L and BZ-H are all 00H, the tone generator is disabled and BZ is high. The value of the frequency divider, ranges from 2 (BZ-L=01H, BZ-H=00H)~65536 (BZ-L=FFH, BZ-H=FFH). Writing to BZ-L only writes the data into a low byte buffer, while writing to BZ-H will write the high byte data and the contents of the low byte buffer into the PFD counter

When the buzzer generator is disabled by clearing the "MGEN" bit in the configuration register (0000H), the BZ pin remains at its last state. If the BZ pin is low, the BZ transistor in

the application circuits is always active. Therefore it is recommended that both BZ-L and BZ-H be cleared and that the "MGEN" bit in the configuration register (0000H) also be cleared, when it is desired to disable or stop the buzzer.

The output of the 16-bit PFD counter is divided by 2 to generate a BZ output with or without modulation. For example, if the desired output of BZ is 1.6kHz with modulation and the frequency source is X1-clock (76.8kHz), then the value of 16-bit PFD counter is set to BZ-L=17H, BZ-H=00H and "MDUT" is set high.

### Interrupt registers

| Address | Register<br>Name | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1   | Bit 0   | State on<br>POR |

|---------|------------------|-------|--------|-------|-------|---------|--------|---------|---------|-----------------|

| 0005H   | INT ctrl         | 0     | 0      | 0     | RTCEN | ORMSK   | RTCMSK | TM1IMSK | TM0IMSK | 0000 1111       |

| 0006H   | INT flag         | 0     | RTC_FG | DR_FG | BF_FG | WDTOVFG | OR_FG  | TM10VFG | TM0OVFG | 0000 0000       |

13

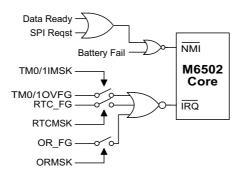

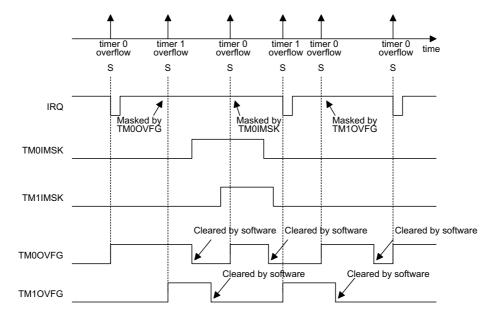

There are two interrupts for the HT9580: a Non-Mask Interrupt (NMI) and a generic interrupt request (IRQ). The data ready interrupt and battery fail interrupt share the NMI call location. Which interrupt occurred can be determined by checking bit BF\_FG and the data ready interrupt bit DR\_FG or SPI complete flag SPIFG (in SPI-CONFIG register). DR\_FG is the data ready interrupt indication bit. When a valid call is detected, data begins to transfer. Either one call is terminated or a message buffer is full or one batch is over but the message is not terminated, the data ready interrupt will occur and DR\_FG is set high. The DR\_FG bit should be cleared low by the µC software after a data ready condition has occurred. A battery fail condition is triggered by a high to low transition on pin BAF and will set the battery fail interrupt request flag BF\_FG to logic high. For details, refer to the POCSAG Decoder section. The sources for the IRQ are timer 0 overflow, timer 1 overflow, out-of-range status changes and RTC time out. The four interrupt sources all could be masked, but the four corresponding interrupt flags will still be set when the interrupt conditions are met. All the four flags are readable/writeable. When an interrupt condition is met, a flag will be set. If an interrupt routine is performed, the software should check which flag is set to high then determine what kind of interrupt source occurred. The WDTOVFG is the flag for the watchdog

timer overflow and RTC\_FG is an indicator for the RTC time out interrupt request flag. The OR\_FG will be set high when an out-of-range status from low to high or high to low transition occurrs. Those flags such as TM0OVFG, TM1OVFG, BF\_FG, DR\_FG, OR\_FG and RTC\_FG should be cleared by the software after they are activated.

|         | 1                                             | 0                                                 |

|---------|-----------------------------------------------|---------------------------------------------------|

| RTCEN   | RTC counter is enabled                        | RTC counter is disabled                           |

| RTCMSK  | RTC interrupt is masked                       | RTC interrupt is not masked                       |

| TM0IMSK | Timer 0 overflow<br>interrupt is<br>masked    | Timer0overflow interruptisnot masked              |

| TM1IMSK | Timer 1<br>overflow<br>interrupt is<br>masked | Timer 1<br>overflow<br>interrupt is not<br>masked |

| ORMSK   | Out-of-range<br>interrupt is<br>masked        | Out-of-range interrupt is not masked              |

|         | 1                                  | 0                             |

|---------|------------------------------------|-------------------------------|

| TM0OVFG | Timer 0 overflows                  | No timer 0 overflow           |

| TM10VFG | Timer 1<br>overflows               | No timer 1 overflow           |

| WDTOVFG | Watchdog<br>timer has<br>overflown | No watchdog<br>timer overflow |

| BF_FG   | Battery fail request               | No battery fail request       |

| DR_FG   | Data ready request                 | No data ready request         |

| OR_FG   | Out-of-range<br>request            | No out-of-range request       |

| RTC_FG  | RTC interrupt request              | No RTC interrupt request      |

Block diagram of NMI and IRQ

Timer0 and Timer1 timing diagram

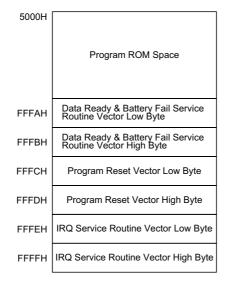

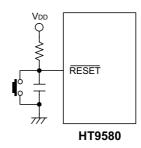

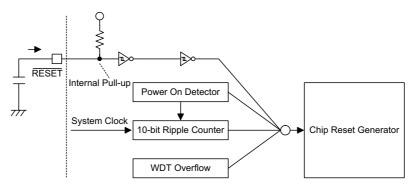

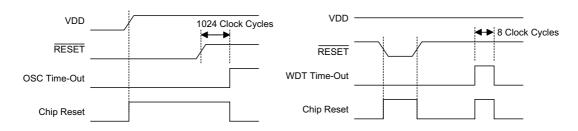

### **Reset conditions**

The HT9580 will reset the whole chip when the following conditions are met:

- Power On

- $\bullet$  The external  $\overline{RESET}$  pin is held low for at least 1 ms

- The WDT overflows

The input is used to reset the  $\mu C$ . Reset must be held low at least 1 ms after VDD reaches operating voltage from a power down. A positive

transition on the chip reset will then cause an initialization sequence to begin. After the system is operating, a low on this line of at least 1 ms in duration will cause  $\mu C$  activity. When a positive edge is detected, there is an initialization sequence lasting 8-clock cycles. Then the interrupt mask flag is set, the decimal mode is cleared and the program counter is loaded with the restart vector from locations FFFC (low byte) and FFFD (high byte). This is the start location for program control. This input should be high during normal operation.

Power on reset timing

RESET active and WDT time-out  $% \left\{ \mathbf{R}^{\prime}\right\} =\left\{ \mathbf{R}^{\prime}\right\} =\left\{$

### **Timer registers**

| Address | Register<br>Name | Bit 7   | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | State on<br>POR |

|---------|------------------|---------|--------|---------|---------|---------|---------|--------|--------|-----------------|

| 0007H   | TMRC             | TMR1MOD | X      | TMR1CLK | TMR0CLK | TMR1EDG | TMR0EDG | TMR1EN | TMR0EN | 0u00 0000       |

| 0008H   | TMR1L            | TM1D7   | TM1D6  | TM1D5   | TM1D4   | TM1D3   | TM1D2   | TM1D1  | TM1D0  | uuuu uuuu       |

| 0009H   | TMR1H            | TM1D15  | TM1D14 | TM1D13  | TM1D12  | TM1D11  | TM1D10  | TM1D9  | TM1D8  | uuuu uuuu       |

| 000AH   | TMR0             | TM0D7   | TM0D6  | TM0D5   | TM0D4   | TM0D3   | TM0D2   | TM0D1  | TM0D0  | uuuu uuuu       |

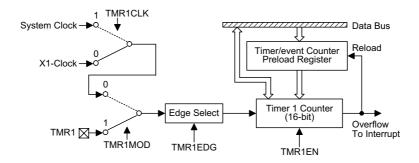

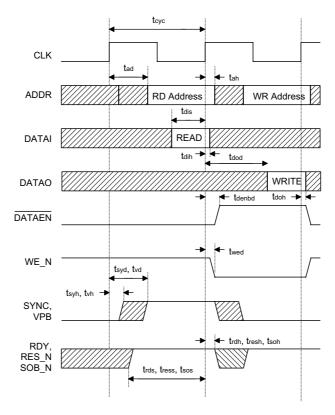

In addition to the watchdog timer, the HT9580 provides two timers: an 8-bit timer (timer 0) and one 16-bit timer (timer 1). Those two timers are controlled and configured by the register TMRC. Both timers are programmable up-count counters whose clocks may be derived from the X1-clock (32.768kHz, 76.8kHz or 153.6kHz). To program the timers, TMR0, TMR1L, and TMR1H should be written with a start value. When the timers are enabled, they will count-up from the start value. If the timers overflow, corresponding interrupts will be generated. When the timers are disabled, the counter contents will not be reset. To reset the counter contents, the software should write the start value again. Since timer1 is a 16-bit counter, it is important to note the method of writing data to both TMR1L and TMR1H. Writing to TMR1L only writes the data into a low byte buffer, while writing to TMR1H will simultaneously write the high byte data and the contents of the low byte buffer into the Timer Counter preload register (16-bit). Note that the Timer counter preload register contents are changed by a TMR1H write operation while writing to TMR1L does not change the contents of the preload register. Reading TMR1H will also latch the contents of TMR1L into the byte buffer to avoid false timing problem. Reading TMR1L returns the contents of the low byte buffer. In other words, the low byte of the timer counter cannot be read directly. It must first read TMR1H to latch the low byte contents of the timer counter into the buffer. TMRC is the timer counter control register, which defines the timer counter options. The timer1 clock source can be selected from either the internal clock or an external input clock by bit TMR1MOD of the TMRC register. The timer0/timer1 can also select its clock source by bits TMR0CLK/TMR1CLK. TMRC as shown in the table.

| Labels (TMRC0 and TMRC1) | Bits   | Function                                                                                                   |

|--------------------------|--------|------------------------------------------------------------------------------------------------------------|

| TMR0EN,<br>TMR1EN        | 0<br>1 | Enable/disable timer counting (0=disable; 1=enable)                                                        |

| TMR0EDG,<br>TMR1EDG      | 2<br>3 | Define the TMR0 and TMR1 active edge (0=active on low to high; 1=active on high to low)                    |

| TMR0CLK                  | 4      | Select TMR0 clock source<br>(0=X1-clock; 1=OSC1 input clock/system clock)                                  |

| TMR1CLK                  | 5      | Select TMR1 clock source if internal clock input is selected (0=X1-clock; 1=OSC1 input clock/system clock) |

| TMR1MOD                  | 7      | Define the TMR1 operation mode<br>(0=internal clock input; 1=external clock input)                         |

Timer 0 block diagram

Timer 1 block diagram

### I/O port configuration registers

| Address | Register<br>Name | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | State on<br>POR |

|---------|------------------|-------|-------|--------|--------|--------|--------|--------|--------|-----------------|

| 000BH   | PA data          | X     | X     | PA5    | PA4    | PA3    | PA2    | PA1    | PA0    | uu11 1111       |

| 000CH   | PB data          | PB7   | PB6   | PB5    | PB4    | PB3    | PB2    | PB1    | PB0    | 1111 1111       |

| 000DH   | PC data          | X     | X     | X      | X      | X      | X      | PC1    | PC0    | uuuu uu11       |

| 000EH   | PAC              | X     | X     | PAC5   | PAC4   | PAC3   | PAC2   | PAC1   | PAC0   | uu11 1111       |

| 000FH   | PBC              | PBC7  | PBC6  | PBC5   | PBC4   | PBC3   | PBC2   | PBC1   | PBC0   | 1111 1111       |

| 0010H   | PCC              | X     | X     | X      | X      | X      | X      | PCC1   | PCC0   | uuuu uu11       |

| 0011H   | PA WUE           | X     | X     | PAWUE5 | PAWUE4 | PAWUE3 | PAWUE2 | PAWUE1 | PAWUE0 | uu00 0000       |

| 0012H   | PA IM            | X     | X     | PAIM5  | PAIM4  | PAIM3  | PAIM2  | PAIM1  | PAIM0  | uu11 1111       |

| 0013H   | PB IM            | PBIM7 | PBIM6 | PBIM5  | PBIM4  | PBIM3  | PBIM2  | PBIM1  | PBIM0  | 1111 1111       |

| 0014H   | PC IM            | X     | X     | X      | X      | X      | X      | PCIM1  | PCIM0  | uuuu uu11       |

The HT9580 has three general purpose I/O ports. The I/O cell structures are configurable. Details are shown in the table.

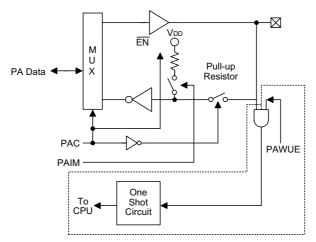

#### Port A

Port A is a general-purpose I/O port. The PAC register controls the data directions for port A. When set as input data type, this port has wake-up capability and the input cell structures are schmitt trigger types. While in a "HALT" condition, a falling edge signal on Port A can wake-up the  $\mu C.$  In addition, the input cell structures can be configured as pull-high or non-pull-high. When set as an output data type, the output structures are CMOS outputs.

|       | 1                                                     | 0                                                          |

|-------|-------------------------------------------------------|------------------------------------------------------------|

| PA    | The pin output logic high                             | The pin output logic low                                   |

| PAC   | As input pin                                          | As output pin                                              |

| PAWUE | The pin has wake-up capability                        | The pin has no<br>wake-up<br>capability                    |

| PAIM  | CMOS input<br>structure<br>with pull-high<br>resistor | CMOS input<br>structure with-<br>out pull-high<br>resistor |

### Port B

Port B is a general-purpose I/O port controlled by the PBC register. The PBIM register controls the input cell structures: normal CMOS inputs or CMOS inputs with pull-high resistors.

|      | 1                                                     | 0                                                     |

|------|-------------------------------------------------------|-------------------------------------------------------|

| PB   | Pin output logic high                                 | Pin output logic low                                  |

| PBC  | Input pin                                             | Output pin                                            |

| PBIM | CMOS input<br>structure with<br>pull-high<br>resistor | CMOS input<br>structure without<br>pull-high resistor |

### Port C

This is a general-purpose I/O port contolled by the PCC register. The PCIM register controls the input cell structures: normal CMOS inputs or CMOS inputs with pull-high resistors.

|      | 1                                                     | 0                                                        |

|------|-------------------------------------------------------|----------------------------------------------------------|

| PC   | The pin output logic high                             | The pin output logic low                                 |

| PCC  | As input pin                                          | As output pin                                            |

| PCIM | CMOS input<br>structure<br>with pull-high<br>resistor | CMOS input<br>structure<br>without pull-high<br>resistor |

I/O structure of port A

### Mask ROM (Character ROM) bank point register

| Address | Register<br>Name | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | State on<br>POR |

|---------|------------------|----------|----------|-------|-------|-------|-------|-------|-------|-----------------|

| 0015H   | MROM-BP          | BP_MODM1 | BP_MODM0 | M_BP5 | M_BP4 | M_BP3 | M_BP2 | M_BP1 | M_BP0 | 0000 0000       |

The Mask ROM bank point register can switch between the internal 2 Mbits Mask ROM or an external up to 2 Mbits Mask ROM space. The selection table is based on the following table. The space size of each Mask ROM bank is 8 Kbytes. The bits BP\_MODM1 and BP\_MODM0 define whether internal or external Mask ROM devices are used. (BP\_MODM1, BP\_MODM0)=(0,1), selects the internal Mask ROM device.

(BP\_MODM1, BP\_MODM0)=(1, 0), selects the external Mask ROM device. The internal Mask ROM can switch from bank 0 to bank 31 and the external Mask ROM can switch from bank 0 to bnak 31 by software programming. In addition, the address range of the internal/external Mask ROM will all range from 1000H to 2FFFH.

The Mask ROM bank point register selection table is shown in the table.

| BP_MODM1 | BP_MODM0 | M_BP5 | M_BP4 | M_BP3 | M_BP2 | M_BP1 | M_BP0 | BP Value | Memory Area                               |

|----------|----------|-------|-------|-------|-------|-------|-------|----------|-------------------------------------------|

| 0        | 0        | X     | X     | X     | X     | X     | X     | X        | Reserved                                  |

| 0        | 1        | 0     | 0     | 0     | 0     | 0     | 0     | 0        | Internal 2 Mbits Mask ROM (low 8 Kbytes)  |

| 0        | 1        |       |       | 1     | l     |       |       | ↓        | ↓                                         |

| 0        | 1        | 0     | 1     | 1     | 1     | 1     | 1     | 31       | Internal 2 Mbits Mask ROM (High 8 Kbytes) |

| 0        | 1        | 1     | 0     | 0     | 0     | 0     | 0     | 32       | Reserved                                  |

| 0        | 1        |       |       | 1     | l     |       |       | ↓        | Reserved                                  |

| 0        | 1        | 1     | 1     | 1     | 1     | 1     | 1     | 63       | Reserved                                  |

| 1        | 0        | 0     | 0     | 0     | 0     | 0     | 0     | 0        | External 2 Mbits Mask ROM (low 8 Kbytes)  |

| 1        | 0        |       |       |       | Į.    |       |       | <b>↓</b> | <b>↓</b>                                  |

| 1        | 0        | 0     | 1     | 1     | 1     | 1     | 1     | 31       | External 2 Mbits Mask ROM (High 8 Kbytes) |

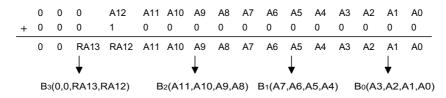

If the internal 2 Mbits mask ROM is placed as shown in the figure and the software programmer obtains a start address from CNS (Taiwan) code or a GB (China) code, A0~A17. The following steps will map from the start address to the bank point register, then the hardware address decode circuit will point to the real 2 Mbits space. (If the internal mask ROM is selected.)

### • Step 1

The formula obtains A0~A18 from the received GB or CNS code. If it is in the lower 2 Mbits space, A18=0. Otherwise, A18=1 if it is in reserved space.

• Step 2

Set  $(BP\_MODM1, BP\_MODM0)=(0, 1)$

• Step 3

Assign correct "M\_BP0"~"M\_BP5" as shown:

- A13→M\_BP0

- A14→M\_BP1

- A15→M\_BP2

- A16→M\_BP3

- A17→M\_BP4

- A18→M\_BP5 (the bit will be 0 at this condition)

- Step 4

Adding \$1000 H to A12~A0 to get new HEX value  $\$B_3B_2B_1B_0$  H.

### • Step 5

The following example will load 32 bytes continuous (one Chinese word) pattern from the internal mask ROM and store them to the start address  $C_3C_2C_1C_0H$  (if absolute index addressing mode is used).

$\begin{array}{lll} LDX & \#00H \\ LDY & \#00H \\ READ: \\ LDA & \$B_3B_2B_1B_0, X \\ STA & \$C_3C_2C_1C_0, Y \\ INX & \\ INY & \\ CPX & \#20H \\ BNZ & READ \\ \end{array}$

### SRAM bank point register

| Address | Register<br>Name | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | State on<br>POR |

|---------|------------------|----------|----------|-------|-------|-------|-------|-------|-------|-----------------|

| 0016H   | SRAM-BP          | BP_MODS1 | BP_MODS0 | S_BP5 | S_BP4 | S_BP3 | S_BP2 | S_BP1 | S_BP0 | 0000 0000       |

The SRAM bank point register can switch to either external 256 Kbytes or internal 32 Kbytes SRAM space. The selection table is based on the following table. The space size of each SRAM bank is 8 Kbytes. Bits BP\_MODS1 and BP\_MODS0 define whether internal or external SRAM devices are used. (BP\_MODS1, BP\_MODS0)=(0, 1), is for internal SRAM de-

vices. (BP\_MODS1, BP\_MODS0)=(1, 0), is for external SRAM devices. The internal SRAM would switch from bank 0 to bank 3 and the external SRAM would switch from bank 0 to bank 31 by software programming. In addition, the address range of the internal/external SRAM will all range from 3000H to 4FFFH.

| BP_MODS1 | BP_MODS0 | S_BP5 | S_BP4 | S_BP3 | S_BP2 | S_BP1 | S_BP0 | BP Value | Memory Area                             |  |  |

|----------|----------|-------|-------|-------|-------|-------|-------|----------|-----------------------------------------|--|--|

| 0        | 0        | X     | X     | X     | X     | X     | X     | X        | Reserved                                |  |  |

| 0        | 1        | 0     | 0     | 0     | 0     | 0     | 0     | 0        | Internal 32 Kbits SRAM (Low 8 Kbytes)   |  |  |

| 0        | 1        |       |       | 1     | ,     | •     |       | <b>↓</b> | <b>↓</b>                                |  |  |

| 0        | 1        | 0     | 0     | 0     | 0     | 1     | 1     | 3        | Internal 32 Kbits SRAM (High 8 Kbytes)  |  |  |

| 0        | 1        | 0     | 0     | 0     | 1     | 0     | 0     | 4        | Reserved                                |  |  |

| 0        | 1        |       |       | 1     | ,     | •     |       | <b>\</b> | Reserved                                |  |  |

| 0        | 1        | 1     | 1     | 1     | 1     | 1     | 1     | 63       | Reserved                                |  |  |

| 1        | 0        | 0     | 0     | 0     | 0     | 0     | 0     | 0        | External 256 Kbits SRAM (Low 8 Kbytes)  |  |  |

| 1        | 0        |       |       | 1     | ,     |       |       | <b>↓</b> | <b>\</b>                                |  |  |

| 1        | 0        | 0     | 1     | 1     | 1     | 1     | 1     | 31       | External 256 Kbits SRAM (High 8 Kbytes) |  |  |

### LCD control and data register

| Address | Register<br>Name | Bit 7     | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0   | State on<br>POR |

|---------|------------------|-----------|-----------|---------|---------|---------|---------|--------|---------|-----------------|

| 0017H   | LCD_CTRL         | LCD-CHIP1 | LCD-CHIP0 | LCD-CLK | CLK-MOD | LCD-CS1 | LCD-CS0 | LCD-A0 | LCD-WRB | 0000 1101       |

| 0018H   | LCD_CMD          | LCD_D7    | LCD_D6    | LCD_D5  | LCD_D4  | LCD_D3  | LCD_D2  | LCD_D1 | LCD_D0  | uuuu uuuu       |

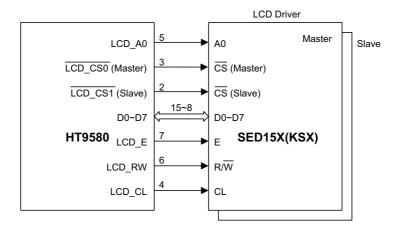

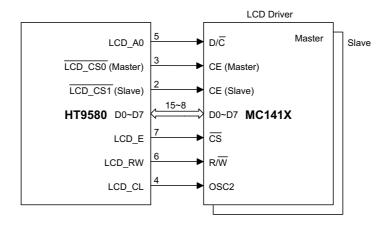

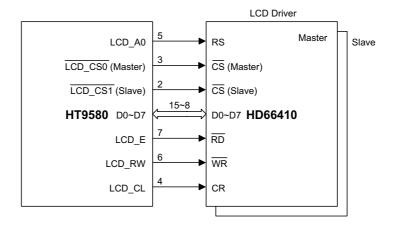

The LCD control and command registers are used for LCD driver interface. There are three kinds of LCD driver chips available for the HT9580. These LCD drivers are SED15X(KSX) series, Motorola LCD driver chip MC141X series and HD66410 respectively according to the following "LCD-CHIP0" and "LCD-CHIP1" bit table settings. The combination of the LCD\_CMD and LCD-CTRL registers can control the SED15X(KSX), MC141X series or HD66410 LCD drivers. Bits LCD-CS0/1 of the

LCD-CTRL register corresponds to the chip select pin of the LCD driver. The bit "LCD-CS0" is used to control the master LCD driver chip while "LCD-CS1" is for the slave LCD driver chip. Both bits are active low. The bit "CLK\_MOD" is used to enable or disable the pin out of LCD\_CL. If the bit is set low, the clock output of pin LCD\_CL will be disabled, otherwise the LCD\_CL clock will be set according to the following Truth Table.

### "LCD-CHIP1" and "LCD-CHIP1" Truth Table

|               | LCD-CHIP0="0"                             | LCD-CHIP0="1"                        |

|---------------|-------------------------------------------|--------------------------------------|

| LCD-CHIP1="0" | SED15X(KSX) series LCD driver is selected | MC141X series LCD driver is selected |

| LCD-CHIP1="1" | HD66410 LCD driver is selected            | N/A                                  |

### "LCD\_CL" Truth Table

|               | LCD-CHIP0="0"          | LCD-CHIP0="1"                                                         |

|---------------|------------------------|-----------------------------------------------------------------------|

| LCD-CHIP1="0" |                        | LCD_CL: If "LCD-CLK"=0, 32 kHz output If "LCD-CLK"=1, X1-clock output |

| LCD-CHIP1="1" | LCD_CL: 10.9kHz output | N/A                                                                   |

The following is a comparison table of the HT9580 pin description between the SED15X (KSX) series and the MC141X series LCD driver.

| HT9580<br>(Pin) | S           | ED15X(KSX) Series                                                                          | M                | IC141X Series                                                                                                                  |

|-----------------|-------------|--------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| LCD_A0          | A0          | Data/command select input. A0=0: Display control data on D0~D7 A0=1: Display data on D0~D7 | D/C              | This input pin acknowledges valid data on D0~D7. If high then D0~D7 contains display data, if low D0~D7 contains command data. |

| LCD_CS0         | CS (Master) | Active low chip select input. (Master)                                                     | CE (Master)      | When high, enables the control pins on the driver. (Master)                                                                    |

| LCD_CS1         | CS (Slave)  | Active low chip select input. (Slave)                                                      | CE (Slave)       | When high, enables the control pins on the driver. (Slave)                                                                     |

| D0~D7           | D0~D7       | 8-bit, tristate, bidirectional I/O bus.                                                    | D0~D7            | Bidirectional bus for data/command transfer.                                                                                   |

| LCD_E           | E           | Enable clock input                                                                         | <del>CS</del>    | This pin is normal low clock input. Data on D0~D7 is latched at the falling edge of CS.                                        |

| LCD_RW          | R/W         | Read/write input                                                                           | $R/\overline{W}$ | To read the display data RAM or the internal status, pull this pin high. The pin low indicates a write operation.              |

| LCD_CL          | CL          | External clock input.<br>(2kHz output from HT9580)                                         | OSC2             | Oscillator input for external clock is used. (32kHz or X1-clock output from HT9580 as determined by the "LCD-CLK").            |

The application circuit when bit "LCD-CHIP1" = 0 and "LCD-CHIP0" = 0

The application circuit when bit "LCD-CHIP1" = 0 and "LCD-CHIP0" = 1

The application circuit when bit "LCD-CHIP1" = 1 and "LCD-CHIP0" = 0

| LCD Driver Chip Selection      | Application                                                       | Note                                               |

|--------------------------------|-------------------------------------------------------------------|----------------------------------------------------|

| LCD-CHIP0="0"                  | SEDX(EPSON) series LCD driver at 68 family MPU application mode.  |                                                    |

| LCD-CHIP1="0"                  | KSX(SAMSUNG) series LCD driver at 68 family MPU application mode. | Pin options set as 68 family MPU application mode. |

| LCD-CHIP0="1"<br>LCD-CHIP1="0" | MC14X(MOTOROLA) series LCD driver.                                |                                                    |

|                                | HD66410(HITACHI) series LCD driver.                               |                                                    |

| LCD-CHIP0="0"<br>LCD-CHIP1="1" | SEDX(EPSON) series LCD driver at 80 family MPU application mode.  | RESET is high active                               |

|                                | KSX(SAMSUNG) series LCD driver at 80 family MPU application.      | Pin options set as 80 family MPU application mode. |

| LCD-CHIP0="1"<br>LCD-CHIP1="1" | N/A                                                               |                                                    |

25

### Power down operation - HALT

The HALT mode is initiated by setting the configuration register bit HALT high and results in the following  $\dots$

The system clock turns off, the low power pager sub-clock, LCD driver, pager decoder and RTC all keep running.

The contents of the on-chip RAM and of the register remain unchanged.

As the WDT and the WDT prescaler depend on software control, the WDT will continue to count when the "HALT" bit is set high.

All the I/O ports remain in their original status.

### D/A registers

| Address | Register<br>Name | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | State on<br>POR |

|---------|------------------|-------|-------|-------|-------|-------|--------|-------|-------|-----------------|

| 002FH   | D/A-L            | DA7   | DA6   | DA5   | DA4   | DA3   | DA2    | DA1   | DA0   | 0000 0000       |

| 0030H   | D/A-H            | X     | X     | X     | X     | X     | D/A_PD | RSSI  | BAT   | uuuu u1uu       |

The system can quit the HALT mode by an external reset, an interrupt, an external falling edge signal on port A or an RTC time out.

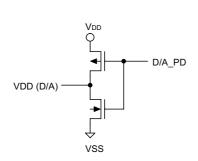

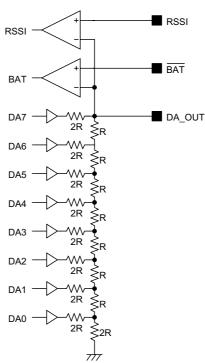

The HT9580 has one internal 8-bit D/A converter which can measure the battery voltage and the RSSI input signal from the IF of the RF circuit. The DA0~DA7 is the digital input of the D/A converter and the analog outputs to the pin named DA\_OUT. Bit BAT of the DA-H register (0030H) is the output of the comparator. Its input at the "-" terminal is from the D/A output and the "+" terminal comes from the input pin

BAF. The bit RSSI of DA-H register (0030H) is the output of another comparator. Its input at "-" terminal is from the D/A output and "+" terminal comes from the input pin RSSI. The software can detect the battery voltage and the RSSI signal by writing to the bits DA0 ~DA7 (002FH) and reading the bits BAT, RSSI (0030H).

Bit "D/A\_PD" is used for the D/A power down control. If this bit is logic high, the D/A will be in the power down mode. Otherwise, the D/A is in the normal condition. For details see the following figure.

The configuration of the 8-bit D/A converter and power down control

### **Buffer status register**

| Address | Register<br>Name | Bit 7   | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | State on<br>POR |

|---------|------------------|---------|-------|---------|---------|---------|---------|---------|---------|-----------------|

| 0031H   | Buffer<br>Status | MSG_END | X     | count_5 | count_4 | count_3 | count_2 | count_1 | count_0 | 0uuu uuuu       |

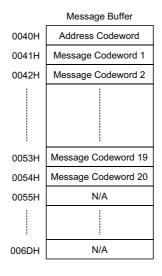

The buffer status register will relay to the  $\mu C$  the status of the message buffer when the data ready request interrupt occurred. The "MSG\_END" bit will be set high when the data (including address codeword and message codeword) is at the end of this data ready interrupt call. The valid data length of the message buffer is determined by bit count\_0 to count\_5. If "MSG\_END" is low, the data length is more

than 46 or data is not at the end, the  $\mu C$  should wait for the next data ready interrupt until the bit "MSG\_END" is set high. Example 1: if the data read from 0031H is "95H" when a new data ready interrupt occurred, it means the total data length is 21 including the address codeword in this call and the message is terminated (bit "MSG\_END" =1). The figure below illustrates example 1.

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

1 0 0 1 0 1 0 1 001 0031H

Example 1

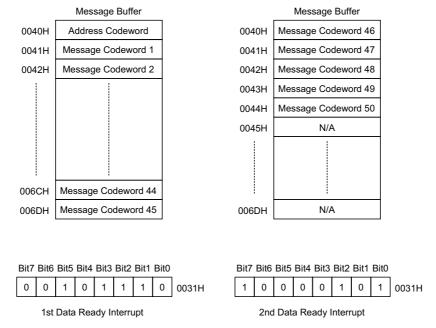

Example 2: if the data read from 0031H is "2EH" when a new data ready interrupt occurred, that means the data length of this call is more than 46 and the next data ready interrupt will occur. If the next interrupt occurs and the contents of 0031H is "85H", the result are

shown in the following figure. The programmer should note that the information on the message buffer must be read out before the next continuous codeword arrives. Otherwise the data on the message will be overwritten.

Example 2

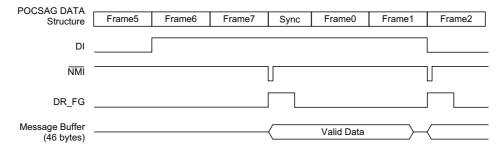

The data ready interrupt will generate when message is terminated, synchronization code

word is received or buffer is full. The following figure will show the typical operation.

The timing chart of message buffer

### SPI configure register

| Address | Register<br>Name | Bit7 | Bit6 | Bit5 | Bit4  | Bit3  | Bit2    | Bit1   | Bit0  | State on<br>POR |

|---------|------------------|------|------|------|-------|-------|---------|--------|-------|-----------------|

| 0032H   | SPI-CONFIG       | S/M  | LEN1 | LEN0 | REQST | SPIFG | CLK_EDG | SPI_EN | START | 0111 1000       |

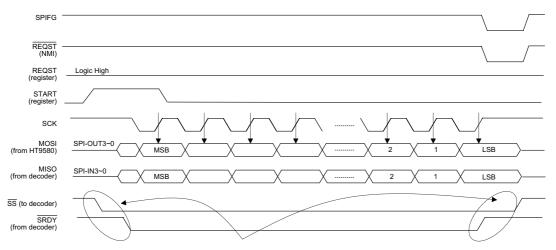

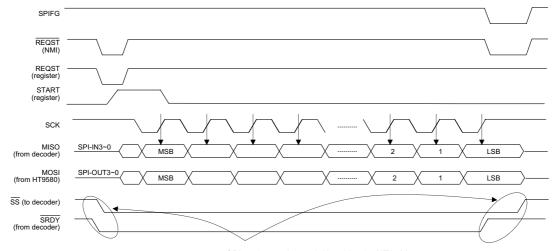

• S/M: Slave/master mode selection When S/M is "0", HT9580 is in the master mode. Otherwise, HT9580 is in the slave mode.

|     | 0                              | 1                            |

|-----|--------------------------------|------------------------------|

| S/M | Master mode<br>(SCK is output) | Slave mode<br>(SCK is input) |

• LEN0, LEN1: Data length

The LEN0 and LEN1 will determine the data length between exchange.

| LEN1 | LEN0 | Data Length (Bit) |

|------|------|-------------------|

| 0    | 0    | 4                 |

| 0    | 1    | 8                 |

| 1    | 0    | 16                |

| 1    | 1    | 32                |

- REQST: SPI request (read only)

When FLEX<sup>TM</sup> decoder wants to exchange data with HT9580, the REQST will have low pulse.

- SPIFG: SPI complete flag 0 (clear): Data transfer to external device has been completed.

- 1 (set): No valid completion of data transfer.

The bit is cleared by hardware and set by software.

• CLK\_EDG: Data sampling edge

The CLK\_EDG will determine the valid

MISO and MOSI sampling edge of SCK clock.

|         | 0           | 1            |

|---------|-------------|--------------|

| CLK_EDG | Rising edge | Falling edge |

• SPI\_EN: The SPI enable

|        | 0                                                                             | 1            |

|--------|-------------------------------------------------------------------------------|--------------|

| SPI_EN | When the SPI circuit is disabled, the POCSAG decoder I/O pins will be enabled | cuit and SPI |