S2061

#### **FEATURES**

- Transmitter incorporates phase-locked loop (PLL) providing clock synthesis from low-speed reference

- Receiver PLL configured for clock and data recovery

- 1.0 1.25 Gbps operation

- · 8-bit parallel TTL compatible interface

- 1.6W typical power dissipation

- +3.3V power supply

- Low-jitter serial PECL compatible interface

- Lock detect

- · Local loopback

- 64 PQFP/TEP package

- · Framing performed by receiver

- Continuous downstream clocking from receiver

- Drives 30m of Twinax cable directly

#### **APPLICATIONS**

High-speed data communications

- Workstation

- Frame buffer

- Switched networks

- · Data broadcast environments

- Proprietary extended backplanes

- · RAID drives

- Mass storage devices

#### **GENERAL DESCRIPTION**

The S2061 transmitter and receiver chip is designed to perform high-speed serial data transmission over fiber optic or coaxial cable interfaces. The chip runs at data rates from 1.0 to 1.25 Gbps with associated 10-bit data word.

The chip performs parallel-to-serial and serial-to-parallel conversion, 8B/10B coding, and framing for block-encoded data. The transmitter's on-chip PLL synthesizes the high-speed clock from a low-speed reference. The receiver's on-chip PLL synchronizes directly to incoming digital signal to receive the data stream. The transmitter and receiver each support differential PECL-compatible I/O for fiber optic component interfaces, to minimize crosstalk and maximize data integrity. Local loopback mode is provided for system diagnostics.

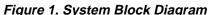

Figure 1 shows a typical configuration incorporating the chip, which is compatible with AMCC's Crosspoint switch products.

#### **S2061 OVERVIEW**

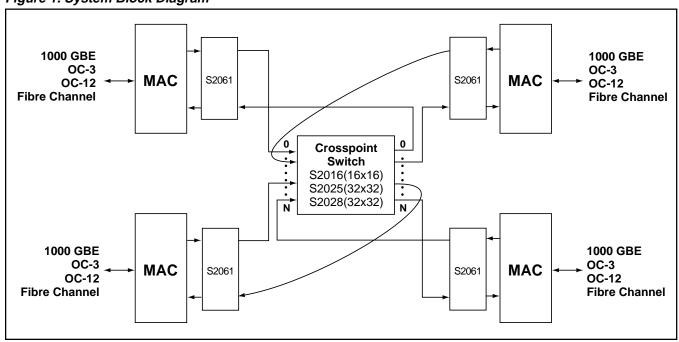

The S2061 transceiver performs encoding/decoding parallel-to-serial and serial-to-parallel conversion and framing functions to implement a Serial Backplane interface. Operation of the S2061 chip is straightforward, as depicted in Figure 2. The sequence of operations is as follows:

#### Transmitter

- 1. 8-bit parallel input

- 2. 8B/10B encoding

- 3. Parallel-to-serial conversion

- 4. Serial output

#### Receiver

- 1. Clock and data recovery from serial input

- 2. Serial-to-parallel conversion

- 3. Frame detection

- 4. 10B/8B decoding

- 5. 8-bit parallel output

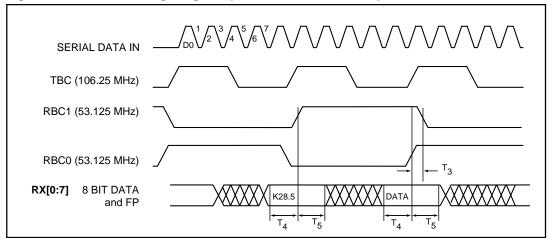

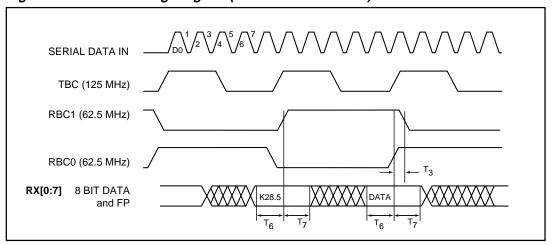

Internal clocking and control functions are transparent to the user. Details of data timing can be seen in Figures 6, 7, 8.

A lock detect feature is provided for the receive PLL. The LOCKDET output indicates that the PLL is locked to the data stream.

#### **Loopback Modes**

Local loopback mode is supported by the chip. Local loopback provides capability for performing offline testing of the interface to ensure the integrity of the serial channel before enabling the transmission medium. It also allows for system diagnostics. (See the section Other Operating Modes.)

Figure 2. Functional Block Diagram

#### **S2061 TRANSMITTER DESCRIPTION**

The S2061 accepts 8-bit parallel input data, performs 8-bit to 10-bit conversion, and serializes the data for transmission over copper or fiber optic media. The transmitter can operate in the range of 1.0 GHz to 1.25 GHz, determined by the TBC frequency.

#### **Data Input**

Data is input to the S2061 as an 8-bit LVTTL (5V tolerant) word. Data is latched into an input register on the rising edge of the input reference clock. The 8-bit data is 8B/10B coded, and the resultant 10-bit word is passed to a shift register where it is converted to serial data.

#### Parallel/Serial Conversion

The parallel-to-serial converter takes 10-bit wide data from the 8B/10B converter and converts it into a serial bit stream. Data is clocked into the serial output shift register at a rate that is synchronous to the clock synthesis unit serial clock. The shift register is clocked by the internally generated bit clock (10x the TBC input frequency).

#### **Transmit Byte Clock**

The Transmit Byte Clock (TBC) input must be supplied from a clock source with ≤100 ppm variation. The internal serial clock is frequency locked to TBC. To set transmitter operating rate (in the range of 1.0 GHz to 1.25 GHz), the TBC input frequency must be selected at 1/10 of the desired operating rate (100 MHz to 125 MHz).

#### 8B/10B Coding

The 8B/10B transmission code includes serial encoding and decoding rules, special characters and error control. Information is encoded, 8 bits at a time, into a 10-bit transmission character. The characters defined by this code ensure that the short run lengths and enough transitions are present in the serial bit stream to make clock recovery possible at the receiver. The encoding also greatly increases the likelihood of detecting any single or multiple errors that might occur during the transmission and reception of data. Refer to reference <sup>1</sup> for a complete description of the transmission code.

The 8B/10B transmission code includes D-characters, used for data transmission, and K-characters, used for control or protocol functions. Each D-character and K-character has a positive and a negative parity version. The parity of each codeword is selected by the encoder to control the running disparity of the data stream.

In addition to the 8-bit data input, there are four control inputs which are used to produce K characters: FRAME, TK0, TK1, and KGEN. Table 1 shows character generation based on input states.

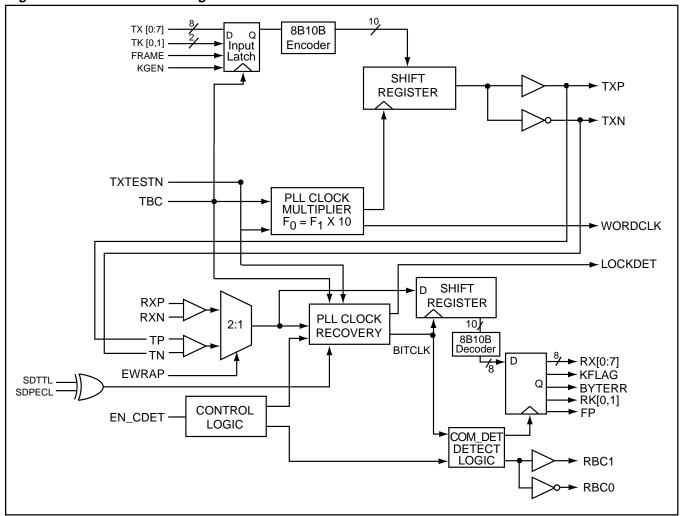

K-character generation is controlled using the KGEN input. When KGEN is asserted, the data on the parallel input is mapped into the corresponding control character. The parity of the K-character is selected to minimize running disparity in the serial data stream. Table 2 lists the K-characters supported by the S2061 and identifies the mapping of the TX[0:7] bits to each character. Figure 3 shows functional waveforms of the S2061.

Table 1. Character Generation

| FRAME | TK1 | TK0 | KGEN | TX[7:0]                 | STATE                                                       |  |  |

|-------|-----|-----|------|-------------------------|-------------------------------------------------------------|--|--|

| 1     | 0   | 0   | 0    | Х                       | K28.5 Running disparity generated.                          |  |  |

| 0     | 0   | 0   | 1    | K<br>Character<br>Value | K character of running disparity generated value on D[0:7]. |  |  |

| 0     | 0   | 1   | 1    | X                       | K28.1 of running disp arity generated.                      |  |  |

| 0     | 1   | 0   | 1    | Х                       | K28.3 of running disparity generated.                       |  |  |

| 0     | 1   | 1   | 1    | Х                       | K28.7 of running disparity generated.                       |  |  |

| 0     | Х   | Х   | 0    | Data                    | D character generated.                                      |  |  |

<sup>1.</sup> A.X. Widner and P.A. Franaszek, "A Byte-Oriented DC Balanced (0,4) 8B/10B Transmission Code," IBM Research Report RC9391, May 1982.

Table 2. K Character Generation

| K         | Υ TX[0:7] |      | Current RD+ | Current RD- | Comments       |  |

|-----------|-----------|------|-------------|-------------|----------------|--|

| Character | 1 1 [0.7] | KGEN | abcdei fghj | abcdei fghj | Comments       |  |

| K28.0     | 000 11100 | 1    | 110000 1011 | 001111 0100 |                |  |

| K28.1     | 001 11100 | 1    | 110000 0110 | 001111 1001 |                |  |

| K28.2     | 010 11100 | 1    | 110000 1010 | 001111 0101 |                |  |

| K28.3     | 011 11100 | 1    | 110000 1100 | 001111 0011 |                |  |

| K28.4     | 100 11100 | 1    | 110000 1101 | 001111 0010 |                |  |

| K28.5     | 101 11100 | 1    | 110000 0101 | 001111 1010 | Sync Character |  |

| K28.6     | 110 11100 | 1    | 110000 1001 | 001111 0110 |                |  |

| K28.7     | 111 11100 | 1    | 110000 0111 | 001111 1000 |                |  |

| K23.7     | 111 10111 | 1    | 111010 1000 | 000101 0111 |                |  |

| K27.5     | 111 11011 | 1    | 110110 1000 | 001001 0111 |                |  |

| K29.7     | 111 11101 | 1    | 101110 1000 | 010001 0111 |                |  |

| K30.7     | 111 11110 | 1    | 011110 1000 | 100001 0111 |                |  |

Table 3. 8B/10B Alphabetic Representation

|                                    |   |   |   | [ | Data | Byte | Э |   | 8 9 |   |  |  |  |

|------------------------------------|---|---|---|---|------|------|---|---|-----|---|--|--|--|

| TX[0:9] or RX[0:9]                 | 0 | 1 | 2 | 3 | 4    | 5    | 6 | 7 | 8   | 9 |  |  |  |

| 8B/10B Alphanumeric Representation | а | b | С | d | е    | i    | f | g | h   | j |  |  |  |

Figure 3. Functional Waveform (1250 and 1062.5 Mbit/sec)

#### RECEIVER DESCRIPTION

The receiver is designed to implement a Serial Backplane receiver function through the physical layer. A block diagram showing the basic function is provided in Figure 2.

The receiver accepts serial encoded data from a fiber optic or coaxial interface. Clock recovery is performed on-chip, with the output data presented as 8-bit parallel data.

Whenever a signal is present, the receiver attempts to achieve synchronization on both bit and transmission-word boundaries of the received encoded bit stream. When bit synchronization is achieved, it is indicated by the LOCKDET signal. Word synchronization is achieved by monitoring the incoming serial data stream for the comma character with negative disparity (0011111XXX). All K28.5 characters, with the correct byte alignment, of either disparity will be indicated by FP. Additional K characters are also decoded per Table 4. When word synchronization is achieved, the receiver provides the valid decoded data on its parallel outputs.

#### **Decoder**

The decoder accepts a serial bit stream, does serial to byte-wide parallel conversion, and performs the 10B/8B decoding function. The framer recognizes the negative disparity comma to correctly frame the data.

#### Byte Synchronization and Framing

The Receiver section performs byte synchronization on the incoming data stream. Byte synchronization is performed on only the negative disparity Fibre Channel comma character (0011111XXX). Thus, in order to ensure byte synchronization, it is necessary to send two comma characters in a row to ensure that one of them is negative disparity. The FP signal will be active whenever a K28.5 character of either disparity is detected. This allows the FRAME input of the transmitter and the FP output on the receiver to be used to 'envelope' the data packet.

Table 4. Character Detection<sup>1</sup>

| FP | RK1 | RK0 | KFLAG | STATE                                   |

|----|-----|-----|-------|-----------------------------------------|

| 1  | 0   | 0   | 1     | K28.5 detected.                         |

| 0  | 0   | 0   | 1     | K character detected, value on TX[0:7]. |

| 0  | 0   | 1   | 1     | K28.1 detected.                         |

| 0  | 1   | 0   | 1     | K28.3 detected.                         |

| 0  | 1   | 1   | 1     | K28.7 detected.                         |

| 0  | 0   | 0   | 0     | D character.                            |

<sup>1.</sup> K characters are detected with either positive or negative disparity.

#### **Lock Detect**

The S2061 contains a lock detect circuit which monitors the integrity of the serial data inputs. If the received serial data fails the run length or frequency test, the PLL will be forced to lock to the local reference clock. This will maintain the correct frequency of the RBC1/0 output under loss of signal or loss of lock conditions. If the serial data inputs have a run length of 80 bit times with no transitions, the PLL will be declared out of lock. In addition, if the recovered clock frequency deviates from the local reference clock frequency by more than approximately 600 ppm, the PLL will also be declared out of lock. The lock detect circuit will poll the input data stream in an attempt to reacquire lock to data. If the recovered clock frequency is determined to be within approximately 300 ppm and the run length check indicates valid data, the PLL will be declared in lock and the lock detect output will go active.

In any transfer of PLL control from the serial data to the reference clock, the RBC1/0 output remains phase continuous and glitch free assuring the integrity of downstream clocking.

#### Reference Clock Input

The reference clock input must be supplied with a crystal clock source with 100 PPM tolerance.

#### OTHER OPERATING MODES

#### Loopback

When local loopback is enabled, serial data from the transmitter is internally routed to the receiver, where the clock is extracted and the data is deserialized. The parallel data is then sent to the subsystem for verification. This loopback mode provides the capability to perform offline testing of the interface to guarantee the integrity of the serial channel before enabling the transmission medium. It also allows system diagnostics.

#### **Operating Frequency Range**

The S2061 is optimized for operation at 1250 and 1062 Mbit/s. Operation at other rates is possible if the rate falls between the nominal rates. TBC must be selected to be within 100 ppm of the desired byte or word clock rate.

Table 5. S2061 Transmitter Pin Assignment and Descriptions

| Pin Name                                             | Level         | I/O | Pin #                                        | Description                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------|---------------|-----|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX7<br>TX6<br>TX5<br>TX4<br>TX3<br>TX2<br>TX1<br>TX0 | TTL           | I   | 38<br>40<br>41<br>42<br>43<br>45<br>46<br>47 | Transmit data. Parallel data on this bus is clocked in on the rising edge of TBC. TX0 is transmitted first.                                                                                                                                                                                                        |

| TBC                                                  | TTL           | I   | 27                                           | Reference clock and transmit byte clock, a crystal-controlled reference clock for the PLL clock multiplier. The frequency of TBC is the bit rate divided by 10.                                                                                                                                                    |

| TXTESTN                                              | TTL           | I   | 39                                           | When toggled 0V/1.5V, TXTESTN replaces internal test input. Tie High for normal operation.                                                                                                                                                                                                                         |

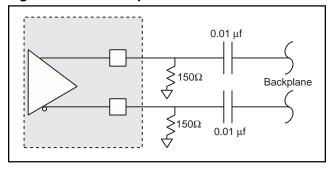

| TXP<br>TXN                                           | Diff.<br>PECL | 0   | 51<br>52                                     | Differential PECL outputs that send out the serial transmitter data and drive $75\Omega$ or $50\Omega$ termination to Vcc–2V. TXP is the positive output, and TXN is the negative output.                                                                                                                          |

| TK0<br>TK1                                           | LVTTL         | I   | 37<br>36                                     | Transmit K character. Active High. These inputs allow additional K characters to be automatically generated by the encoder. (See Table 1.)                                                                                                                                                                         |

| KGEN                                                 | LVTTL         | I   | 33                                           | K Char Gen. Used to specify data (D) or control (K) for parallel data bits 0-7.                                                                                                                                                                                                                                    |

| FRAME                                                | LVTTL         | I   | 32                                           | Active High. If KGEN is 0, the FRAME input controls the transmission of data or K28.5 characters. When active, a K28.5 character with correct running disparity will be generated by the transmit encoder. When inactive, the data byte present on DATAIN<7:0> will be encoded with the correct running disparity. |

| WORDCLK                                              | LVTTL         | 0   | 44                                           | Word clock for encoder. The encoder operates synchronously to this clock. The frequency of the WORDCLK is the bit rate divided by 20.                                                                                                                                                                              |

## Table 6. S2061 Receiver Pin Assignment and Descriptions

| Pin Name                                             | Level     | I/O | Pin #                              | Description                                                                                                                                                                                                                      |

|------------------------------------------------------|-----------|-----|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX7<br>RX6<br>RX5<br>RX4<br>RX3<br>RX2<br>RX1<br>RX0 | TTL       | 0   | 13<br>11<br>10<br>9<br>8<br>6<br>5 | Receive data outputs. Parallel data on this bus is valid on the rising edge of RBC0 and RBC1. RX0 is the first bit received.                                                                                                     |

| RBC1<br>RBC0                                         | Diff. TTL | 0   | 19<br>18                           | Receive clock. Parallel data is valid on the rising edge of RBC0 and RBC1 (see timing diagram in Figure 8). After a sync word is detected, the period of the current RBC1 and RBC0 is stretched to align with the word boundary. |

Table 6. S2061 Receiver Pin Assignment and Descriptions (Continued)

| Table 6. 02007 Rederver 7 III Addignment and Decomptions (Gentinaea) |                 |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------------------------------------------------------------------|-----------------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                                             | Level           | I/O | Pin #    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| EN_CDET                                                              | TTL             | I   | 25       | Enable comma detect. When High, enables sync detection.  Detection of the 7-bit comma + character sync pattern, RX(0-9)  = (K28.5:0011111XXX), will enable the word boundary for the data to follow. When Low, data is treated as unframed data.                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| RXP<br>RXN                                                           | Diff.<br>LVPECL | I   | 59<br>61 | (Externally capacitively coupled.) Differential LVPECL received serial data inputs. RXP is the positive input, and RXN is the negative input. Internally biased.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| FP                                                                   | TTL             | 0   | 2        | Frame Pulse. Active High. When active FP indicates that a K28.5 character of either disparity has been detected and is present on RX<0:7>. Note: Byte alignment is performed on the 7 bit comma character with negative disparity (0011111XXX), not the full K28.5.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| LOCKDET                                                              | LVTTL           | 0   | 64       | Lock Detect. Active High. Indicates that the receiver has achieved bit synchronization (PLL lock).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| KFLAG                                                                | LVTTL           | 0   | 16       | K Character Flag. Active High. Indicates the decoded data byte is a special character (K byte). Control information is indicated whenever KFLAG is high; a low indicates data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| BYTERR                                                               | LVTTL           | 0   | 1        | Byte Error Flag. Active High. Indicates the received byte contained a character or disparity error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| SDTTL                                                                | LVTTL           |     | 22       | Signal Detect. Active High when SDPECL is unconnected (logic 0). Active Low when SDPECL is held at logic 1. A single-ended LVTTL input to be driven by the external optical receiver module to indicate a loss of received optical power. When SDTTL is inactive, the data on the RXP/N pins will be internally forced to a constant zero. When SDTTL is active, data on the RXP/N pins will be processed normally.                                                                                                                                                                                                                                    |  |

| SDPECL                                                               | LVPECL          | ı   | 21       | Signal Detect. LVPECL with internal 1 k pull-down. Active High when SDTTL is held at logic 0. A single-ended 10K LVPECL input to be driven by the external optical receiver module to indicate a loss of received optical power. When SDPECL is inactive, the data on the Serial Data In (RXP/N) pins will be internally forced to a constant zero. When SDPECL is active, data on the RXP/N pins will be processed normally. When SDTTL is to be connected to the optical receiver module instead of SDPECL, then SDPECL should be tied High to implement an active low Signal Detect, or left unconnected to implement an active high Signal Detect. |  |

| RK0<br>RK1                                                           | LVTTL           | 0   | 14<br>15 | Receive K Character. Active High. These outputs indicate reception of the K28.1, K28.3, and K28.7 K characters. (See Table 4.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

# Table 5. S2061 Common Pin Assignment and Descriptions

| Pin Name | Level | I/O | Pin #                      | Description                                                                                                                                                                                      |

|----------|-------|-----|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EWRAP    | TTL   | I   | 30                         | Enable Wrap input. When High, selects the transmitter serial output data to be routed to the receiver. When Low, selects RXP and RXN (normal operation). TXP, TXN are static when EWRAP is High. |

| RST      | TTL   | I   | 23                         | Active Low. Used to initialize the chip for factory test.                                                                                                                                        |

| RATESEL  | TTL   | I   | 56                         | Used for factory test. Tie High for normal operation.                                                                                                                                            |

| ECLVCC   | _     | -   | 29<br>26<br>53<br>58       | Core +3.3V                                                                                                                                                                                       |

| ECLVEE   | -     | -   | 24<br>28<br>35<br>48<br>57 | Core Ground                                                                                                                                                                                      |

| TTLGND   |       |     | 3<br>17                    | TTL Ground                                                                                                                                                                                       |

| TTLVCC   |       |     | 7<br>12                    | TTL +3.3V                                                                                                                                                                                        |

| ECLIOVCC |       |     | 50                         | PECL I/O +3.3V                                                                                                                                                                                   |

| ECLIOVEE |       |     | 55<br>49                   | PECL I/O Ground                                                                                                                                                                                  |

| AVCC     |       |     | 31<br>63                   | Analog +3.3V                                                                                                                                                                                     |

| AVEE     |       |     | 34<br>62                   | Analog Ground                                                                                                                                                                                    |

| NC       | _     | -   | 20<br>54<br>60             | No Connection                                                                                                                                                                                    |

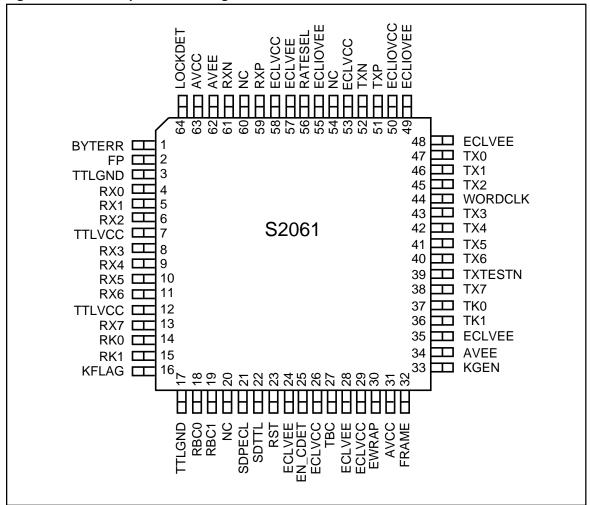

Figure 4. Pin Description and Assignment

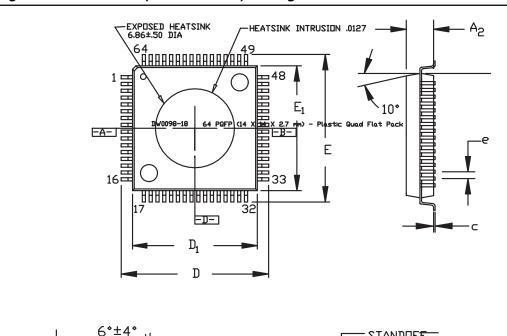

Figure 5. 64 PQFP/TEP (14mm x 14mm) Package

#### DIMENSIONS (are in millimeters)

| UNIT | Α    | A <sub>1</sub> | A2   | D     | $D_1$ | Ε     | E <sub>1</sub> | L    | b    | υ            | C    |

|------|------|----------------|------|-------|-------|-------|----------------|------|------|--------------|------|

| MIN  |      |                | 1.95 | 16.95 | 13.90 | 16.95 | 13.90          | 0.78 | 0.30 |              |      |

| NDM  |      |                | 2.00 | 17.20 | 14.00 | 17.20 | 14.00          | 0.88 | 0.35 | 0.80<br>0.80 |      |

| MAX  | 2.35 | 0.25           | 2.10 | 17.45 | 14.10 | 17.45 | 14.10          | 1.03 | 0.40 |              | 0.17 |

#### Thermal Management

| Device | Power    | ⊝ja    | ⊝jc     |

|--------|----------|--------|---------|

| S2061  | 2.0W Max | 30°C/W | 2.5°C/W |

Table 8. Absolute Maximum Ratings

| PARAMETER                                    | MIN  | TYP | MAX  | UNIT |

|----------------------------------------------|------|-----|------|------|

| Case Temperature under Bias                  | -55  |     | 125  | °C   |

| Junction Temperature under Bias              | -55  |     | 150  | °C   |

| Storage Temperature                          | -65  |     | 150  | °C   |

| Voltage on VCC with Respect to GND           | -0.5 |     | +7.0 | V    |

| Voltage on any TTL Input Pin except Tx [0:7] | -0.5 |     | 3.47 | V    |

| Voltage on TTL input pin TX [0:7]            |      |     | +5.5 | V    |

| Voltage on any PECL Input Pin                | 0    |     | VCC  | V    |

| TTL Output Sink Current                      |      |     | 8    | mA   |

| TTL Output Source Current                    |      |     | 8    | mA   |

| High Speed PECL Output Source<br>Current     |      |     | 50   | mA   |

| Static Discharge Voltage                     |      | 500 |      | V    |

Table 9. Recommended Operating Conditions

| PARAMETER                                                                   | MIN         | TYP | MAX  | UNIT |

|-----------------------------------------------------------------------------|-------------|-----|------|------|

| Ambient Temperature under Bias                                              | 0           |     | 70   | °C   |

| Junction Temperature under Bias                                             |             |     | 130  | °C   |

| Voltage on TTLVCC, ECLVCC,<br>ECLIOVCC, and AVCC with respect to<br>GND/VEE | 3.13        | 3.3 | 3.47 | V    |

| Voltage on TTL Input Pin except TX [0:7]                                    | 0           |     | 3.47 | V    |

| Voltage on any PECL Input Pin                                               | VCC<br>-2.0 |     | VCC  | V    |

| Voltage on TTL data TX [0:7]                                                | 0           |     | 5.0  |      |

Table 10. Reference Clock Requirements

| Parameters                          | Description               | Min  | Max  | Units | Conditions            |

|-------------------------------------|---------------------------|------|------|-------|-----------------------|

| FT                                  | Frequency Tolerance       | -100 | +100 | ppm   | _                     |

| TD <sub>1-2</sub>                   | Symmetry                  | 40   | 60   | %     | Duty Cycle at 50% pt. |

| T <sub>RCR</sub> , T <sub>RCF</sub> | REFCLK Rise and Fall Time | _    | 2    | ns    | 20 – 80%              |

| _                                   | Random Jitter             |      | 100  | ps    | Peak-to-Peak          |

Table 11. S2061 DC Characteristics

| Parameters      | Description                                                        | Min | Тур  | Max  | Units | Conditions                                                     |

|-----------------|--------------------------------------------------------------------|-----|------|------|-------|----------------------------------------------------------------|

| VOH             | Output HIGH Voltage (TTL)                                          | 2.2 | 2.5  | VCC  | V     | V <sub>CC</sub> = min, I <sub>OH</sub> = -400 μA               |

| V <sub>OL</sub> | Output LOW Voltage (TTL)                                           | GND | .025 | 0.5  | V     | V <sub>CC</sub> = max, I <sub>OL</sub> = 1 mA                  |

| V <sub>IH</sub> | Input HIGH Voltage (TTL)                                           | 2.0 | _    | _    | V     | I <sub>H</sub> ≤ 1mA at V <sub>IH</sub> = 5.5V                 |

| V <sub>IL</sub> | Input LOW Voltage (TTL)                                            | GND | _    | 0.8  | V     | _                                                              |

| I <sub>IH</sub> | Input HIGH Current (TTL)                                           | _   | _    | 40   | μΑ    | V <sub>IN</sub> = 2.4V, V <sub>CC</sub> = max                  |

| I <sub>IL</sub> | Input LOW Current (TTL)                                            | _   | _    | 600  | μΑ    | V <sub>IN</sub> = 0.4V, V <sub>CC</sub> = max                  |

| Icc             | Supply Current                                                     |     | 485  | 577  | mA    | Outputs open, V <sub>CC</sub> = V <sub>CC</sub> max SQ pattern |

| P <sub>D</sub>  | Power Dissipation                                                  |     | 1.6  | 2.0  | W     | Outputs open, V <sub>CC</sub> = V <sub>CC</sub> max SQ pattern |

| VDIFF           | Min. differential input voltage swing for differential PECL inputs | 100 |      | 1300 | mV    |                                                                |

| ΔVOUT           | Serial Output Voltage Swing                                        | 600 | _    | 1600 | mV    | 50Ω to V <sub>CC</sub> -2.0V                                   |

| C <sub>in</sub> | Input capacitance                                                  | _   |      | 4    | PF    |                                                                |

Table 12. S2061 Performance Summary

| Parameter             | S20   | Units  |        |

|-----------------------|-------|--------|--------|

| Operating Frequency * | 1250  | 1062.5 | Mbit/s |

| Serial clock period   | .800  | .941   | ns     |

| Byte clock period     | 8.00  | 9.41   | ns     |

| Acquisition Time      | 250   | 250    | ns     |

| Reference clock       | 125.0 | 106.25 | MHz    |

| Word width            | 10    | 10     | Bits   |

$<sup>^{*}</sup>$  ±10% lock range, nominal frequency is per FC-PH standard.

Table 13. S2061 Transmitter Timing

| Parameters                           | Description                                   | Min | Max | Units | Conditions                                                                          |

|--------------------------------------|-----------------------------------------------|-----|-----|-------|-------------------------------------------------------------------------------------|

| T <sub>1</sub>                       | Data setup w.r.t. REFCLK                      | 2   | _   | ns    | See note.                                                                           |

| T <sub>2</sub>                       | Data hold w.r.t. REFCLK                       | 1.0 | _   | ns    | _                                                                                   |

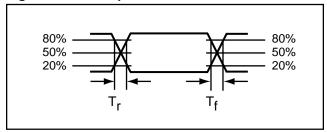

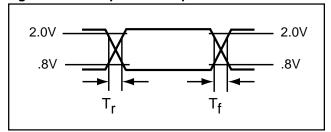

| T <sub>SDR</sub> , T <sub>SDF</sub>  | Serial data rise and fall                     | _   | 300 | ps    | 20% to 80%, tested on a sample basis.                                               |

| Transmitter Output Jitter Allocation |                                               |     |     |       |                                                                                     |

| T <sub>J</sub> RMS                   | Serial data output random jitter (RMS)        | _   | 20  | ps    | RMS, tested on a sample basis.<br>Measured with 1010 pattern.                       |

| T <sub>DJ</sub>                      | Serial data output deterministic jitter (p-p) | _   | 80  | ps    | Peak-to-peak, tested on a sample basis.<br>Measured with K28.5± @ 1.25 GHz pattern. |

Note: All AC measurements are made from the reference voltage level of the clock (1.4V) to the valid input or output data levels (.8V or 2.0V).

Table 14. S2061 Receiver Timing

| Parameters                          | Description                                                              | Min | Max | Units    | Conditions                                                            |

|-------------------------------------|--------------------------------------------------------------------------|-----|-----|----------|-----------------------------------------------------------------------|

| Т3                                  | RBC0 to RBC1 skew                                                        | _   | 1   | ns       | Tested on a sample basis.                                             |

| T <sub>4</sub>                      | Data setup w.r.t. RBC0, RBC1                                             | 3.0 |     | ns       | 1.0625 GHz Mode                                                       |

| T <sub>5</sub>                      | Data hold w.r.t. RBC0, RBC1                                              | 1.5 |     | ns       | 1.0625 GHz Mode                                                       |

| Т <sub>6</sub>                      | Data setup w.r.t. RBC0, RBC1                                             | 2.5 |     | ns       | 1.250 GHz Mode                                                        |

| T <sub>7</sub>                      | Data hold w.r.t. RBC0, RBC1                                              | 1.5 |     | ns       | 1.250 GHz Mode                                                        |

| T <sub>RCR</sub> , T <sub>RCF</sub> | RBC0, RBC1 rise and fall time                                            | _   | 3.0 | ns       | Measured from .8V to 2.0V.                                            |

| T <sub>DR</sub> , T <sub>DF</sub>   | Data Output rise and fall time                                           | _   | 3.0 | ns       | Measured from .8V to 2.0V.                                            |

| T <sub>SDR</sub> , T <sub>SDF</sub> | Serial data input rise and fall                                          | _   | 300 | ps       | 20% to 80%. (See Figure 10.)                                          |

| T <sub>LOCK</sub>                   | Data acquisition lock time @ <1.0625Gb/s                                 | _   | 2.4 | μs       | 8B/10B IDLE pattern sample basis                                      |

| Duty Cycle                          | RBC0/RBC1 Duty Cycle                                                     | 40% | 60% |          |                                                                       |

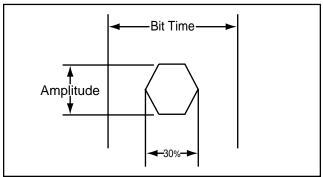

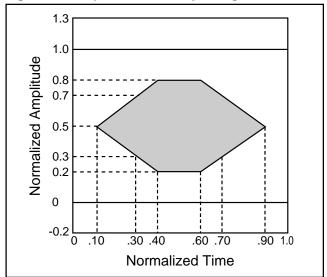

| Input Jitter<br>Tolerance           | Input data eye opening<br>allocation at receiver input<br>for BER ≤1E–12 | 30% | _   | bit time | As specified in Fibre Channel FC–PH standard eye diagram jitter mask. |

Note: All TTL/CMOS AC measurements are assumed to have the output load of 10pF.

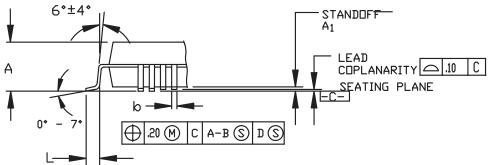

Figure 6. Transmitter Timing Diagram

Figure 7. Receiver Timing Diagram (1062.5 Mbits/sec mode)

Figure 8. Receiver Timing Diagram (1250 Mbits/sec mode)

Figure 9. Serial Input Rise and Fall Time

Figure 10. Serial Output Load

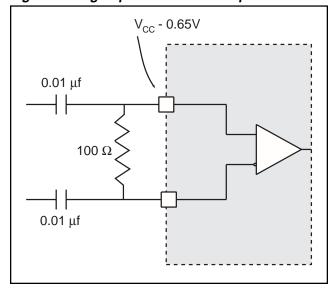

Figure 11. High Speed Differential Inputs

Figure 12. TTL Input and Output Rise and Fall Time

Figure 13. Receiver Input Eye Diagram Jitter Mask

#### **ACQUISITION TIME**

With the input eye diagram shown in Figure 13, the S2061 will recover data with a  $10^{-9}$  BER within 50 bit times after an instantaneous phase shift of the incoming data.

Figure 14. Acquisition Time Eye Diagram

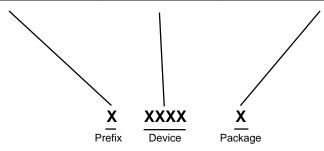

#### **Ordering Information**

| PREFIX                | DEVICE | PACKAGE          |

|-----------------------|--------|------------------|

| S- Integrated Circuit | 2061   | B – 64 PQFP 10mm |

# Applied Micro Circuits Corporation • 6290 Sequence Dr., San Diego, CA 92121 Phone: (619) 450-9333 • (800)755-2622 • Fax: (619) 450-9885

#### http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation.

Copyright ® 1999 Applied Micro Circuits Corporation