# μPD9513AD/9514AD CMOS SERIAL INTERFACE CODEC-FILTER COMBINATION

**April 1987**

#### **Description**

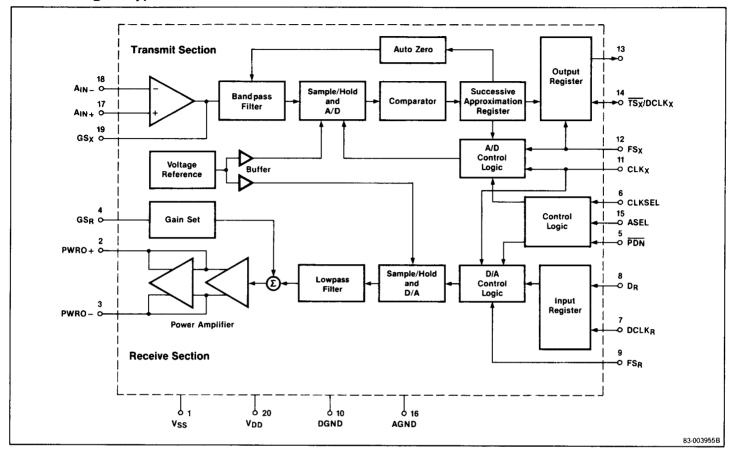

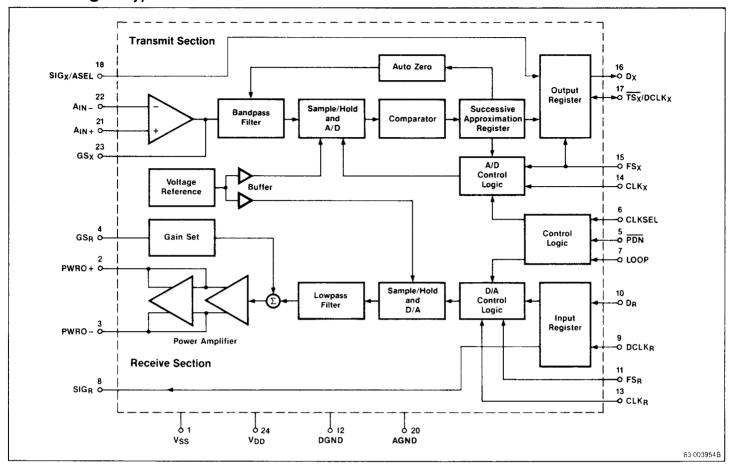

The  $\mu$ PD9513AD and  $\mu$ PD9514AD are monolithic PCM codecs with integrated filters. These devices provide transmit A/D and receive D/A conversions of vf signals using companded  $\mu$ -law or A-law format. They interface the PCM highway through serial ports.

At the vf input, the transmit section includes an adjustable-gain operational amplifier, a lowpass antialiasing filter, and a 200-3400 Hz bandpass filter. The filtered signal is sampled and encoded using a very accurate dc reference voltage. An autozero circuit corrects for dc offset.

The receive section reconstructs an analog signal from the companded digital signal and passes the signal through a 3400-Hz lowpass filter that corrects for the  $(\sin x)/x$  response of the decoder output. A balanced power amplifier at the analog vf receive port allows maximum flexibility in output configurations.

The  $\mu$ PD9513AD and 9514AD can operate in fixed or variable data rate mode. In the fixed data rate mode, the master receive clock and the PCM data clock are selected as 1.536, 1.544, or 2.048 MHz. In the variable data rate mode, the PCM data clock can vary from 64 kHz to 2.048 MHz. The  $\mu$ PD9514AD allows asynchronous master transmit and receive clocks; the  $\mu$ PD9513AD uses one master clock for both transmit and receive sections. The  $\mu$ PD9514AD also has analog loopback and signaling capabilities.

The  $\mu$ PD9513AD and 9514AD are most suited to tele-communications applications. They are ideal for D3/D4 type channel banks and subscriber carrier systems, digital PBXs and central office switching systems, and digital telephone handsets. Their wide dynamic range makes them attractive for any application requiring digital processing of vf signals.

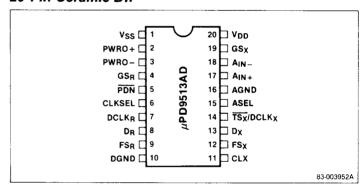

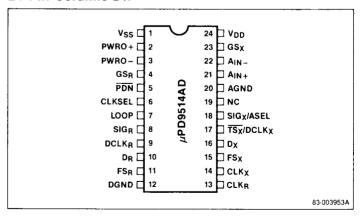

Packaged in a 24-pin DIP, the  $\mu$ PD9514AD offers more capability and flexibility. The  $\mu$ PD9513AD in a 20-pin DIP offers higher-density packaging.

#### **Ordering Information**

| Part No.  | Package Type                 | Signaling |  |  |

|-----------|------------------------------|-----------|--|--|

| μPD9513AD | 20-pin ceramic DIP (300 mil) | No        |  |  |

| μPD9514AD | 24-pin ceramic DIP (600 mil) | Yes       |  |  |

#### **Features**

- ☐ Complete codec and filtering in a single chip

- Transmit highpass and lowpass filters

- Transmit op amp for gain adjustment

- Receive lowpass filter with (sin x)/x correction

- Receive output power amplifier

- Autozero circuit

- Highly-accurate reference voltage

- $\mu$ -law or A-law selectable by pin connection

- Serial digital I/O interface

- ☐ Two timing modes

- Fixed data rate mode (1.536, 1.544, or 2.048 MHz)

- Variable data rate mode (64 kHz to 2.048 MHz)

- ☐ Meets or exceeds D3/D4 and CCITT specifications

- ☐ Low power consumption

- 80 mW in normal operation

- 8 mW in power-down mode

#### **Pin Configurations**

#### 20-Pin Ceramic DIP

#### 24-Pin Ceramic DIP

#### Pin Identification

| Pin N             | lo. |                   |                                                                             |

|-------------------|-----|-------------------|-----------------------------------------------------------------------------|

| 9513AD 9514AD Sym |     | Symbol            | Function                                                                    |

| 1                 | 1   | V <sub>SS</sub>   | Negative supply voltage, —5 V                                               |

| 2                 | 2   | PWR0+             | Receive power amplifier, noninverting output                                |

| 3                 | 3   | PWR0-             | Receive power amplifier, inverting output                                   |

| 4                 | 4   | GS <sub>R</sub>   | Receive power amplifier, gain set resistor                                  |

| 5                 | 5   | PDN               | Power-down select input                                                     |

| 6                 | 6   | CLKSEL            | Master clock select (by strapping)                                          |

|                   | 7   | L00P              | Analog loopback control input                                               |

|                   | 8   | SIGR              | Receive signaling output                                                    |

| 7                 | 9   | DCLK <sub>R</sub> | Receive PCM data clock input; or fixed data rate mode select (by strapping) |

| 8                 | 10  | D <sub>R</sub>    | Receive PCM input                                                           |

| 9                 | 11  | FSR               | Receive 8-kHz frame sync clock input                                        |

| 10                | 12  | DGND              | Digital ground; not tied to analog ground internally                        |

|                   | 13  | CLKR              | Receive master clock input                                                  |

| 11                |     | CLK               | Master clock input                                                          |

|                   | 14  | CLKX              | Transmit master clock input                                                 |

| 12                | 15  | FS <sub>X</sub>   | Transmit 8-kHz frame sync clock input                                       |

| 13                | 16  | DX                | Transmit PCM output                                                         |

| 14                | 17  | TS <sub>X</sub>   | Transmit channel time slot strobe output (fixed rate mode)                  |

|                   |     | DCLKX             | Transmit PCM data clock input (variable data rate mode)                     |

| 15                |     | ASEL              | A-law select (by strapping)                                                 |

|                   | 18  | ASEL              | A-law select (by strapping)                                                 |

|                   |     | SIGX              | Transmit signaling input when A-law is not selected                         |

|                   | 19  | NC                | No connection                                                               |

| 16                | 20  | AGND              | Analog ground; not tied to digital ground internally                        |

| 17                | 21  | A <sub>IN+</sub>  | Transmit op amp analog input, noninverting                                  |

| 18                | 22  | A <sub>IN</sub>   | Transmit op amp analog input, inverting                                     |

| 19                | 23  | GS <sub>X</sub>   | Transmit op amp, gain set resistor                                          |

| 20                | 24  | V <sub>DD</sub>   | Positive supply voltage, +5 V                                               |

#### **Pin Functions**

The information that follows adds to the brief descriptions in the pin identification table.

#### Receive Output [PWRO+ and PWRO-]

The balanced 600-ohm output of the receive power amplifier is between PWRO+ and PWRO-. Either PWRO+ or PWRO- can be used as an unbalanced 300-ohm output.

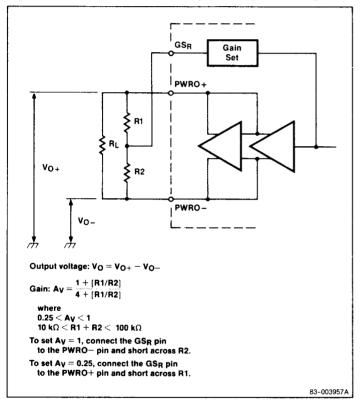

#### Receive Gain Set [GS<sub>R</sub>]

External resistors connecting PWRO+, PWRO-, and  $GS_R$  set the receive power amplifier gain between 0 and -12 dB.

#### Power-Down Select [PDN]

Low logic level on PDN selects the power-down mode.

#### **Master Clock Select [CLKSEL]**

Strap CLKSEL (pin 6) according to the master clock frequency (CLK or CLK<sub>X</sub> and CLK<sub>B</sub>).

| Frequency | Strap Pin 6 to  |

|-----------|-----------------|

| 2.048 MHz | V <sub>SS</sub> |

| 1.544 MHz | DGND            |

| 1.536 MHz | $V_{DD}$        |

#### **Analog Loopback Control [LOOP]**

Applying high logic level to the LOOP pin activates analog loopback. Internally, the receive output is looped back to the transmit input; connections are PWRO+ to  $A_{IN+}$ , PWRO- to  $GS_R$ , and  $GS_X$  to  $A_{IN-}$ .

#### Receive Signaling [SIG<sub>R</sub>]

In the receive section, bit 8 of the channel word in each signaling frame is extracted and held latched until updated in the next signaling frame. The signaling state is output continuously on the  $SIG_{\rm R}$  pin.

#### Data Rate Mode Select [DCLK<sub>R</sub>].

Strapping DCLK<sub>R</sub> to  $V_{SS}$  selects the fixed data rate mode. Omitting the strap selects the variable data rate mode and the DCLK<sub>R</sub> pin becomes the input for the receive PCM data clock, which is 64 kHz to 2.048 MHz.

#### Receive PCM Input [DR]

During the proper channel time slot defined by receive frame sync clock  $FS_R$ , the eight-bit channel word is clocked in from the PCM highway at the PCM data clock rate. The PCM data clock is DCLK<sub>R</sub> in the variable data rate mode and CLK (9513AD) or CLK<sub>R</sub> (9514AD) in the fixed data rate mode.

#### Receive Frame Sync Clock [FS<sub>R</sub>]

This 8-kHz clock defines the time slot of a particular channel in the frame. In the fixed data rate mode, the clock pulse is double width in signaling frames. In the variable data rate mode, the clock remains high during the entire time slot.

If the  $FS_R$  pin is held low for 300 ms, the receive section enters the standby mode.

#### Receive Master Clock [CLK<sub>R</sub>]

The receive master clock input to the  $\mu$ PD9514AD may be 2.048, 1.544, or 1.536 MHz. (The CLKSEL pin is strapped accordingly.) This clock controls the decoder and filter in the receive section. If the data rate is fixed, it also clocks in data from the PCM highway.

#### Master Clock [CLK]

In the  $\mu$ PD9513AD, the CLK input serves as master clock to the transmit and receive sections.

#### Transmit Master Clock [CLK<sub>X</sub>]

The transmit master clock input to the  $\mu$ PD9514AD may be 2.048, 1.544, or 1.536 MHz. It controls the coder and filter in the transmit section and, if the data rate is fixed, clocks data out to the PCM highway.

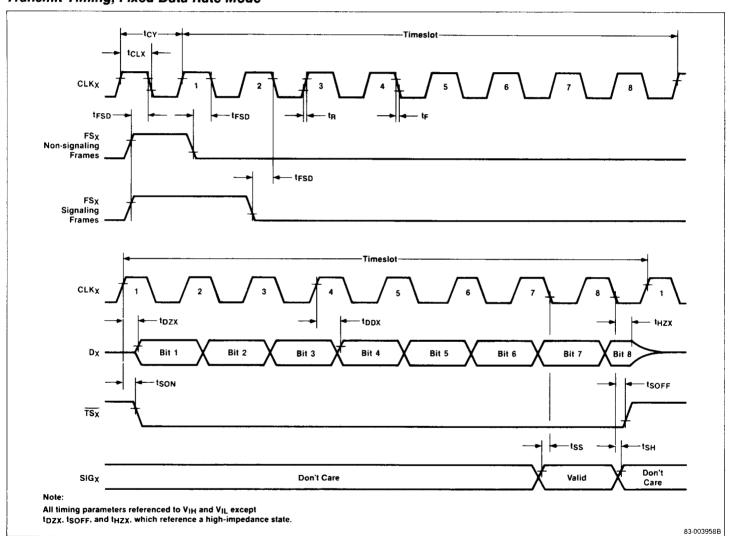

#### Transmit Frame Sync Clock [FSx]

This 8-kHz clock functions in the transmit section the same as FS<sub>R</sub> in the receive section.

#### Transmit PCM Output [Dx]

During the proper channel time slot as defined by the 8-kHz frame sync clock  $FS_X$ , the eight-bit channel word is clocked onto the PCM highway by eight consecutive rising edges of CLK or  $CLK_X$  (fixed data rate mode) or  $DCLK_X$  (variable data rate mode).

#### Transmit Timeslot Strobe [TSX]

In the fixed data rate mode, the  $\overline{TS_X}$  pin is an open-drain output that goes low during the output of the channel word at  $D_X$ .

#### Transmit Data Clock [DCLK<sub>X</sub>]

In the variable data rate mode, DCLK $_{\rm X}$  is the transmit PCM data clock, variable from 64 kHz to 2.048 MHz.

#### Transmit Signaling [SIG<sub>X</sub>]

The logic state of  $SIG_X$  is transmitted as bit 8 of the channel word in signaling frames.

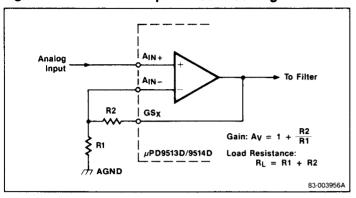

#### Transmit Analog Input [A<sub>IN+</sub> and A<sub>IN-</sub>]

The vf analog signal enters the unbalanced noninverting input  $A_{IN+}$  of the transmit operational amplifier. The gain is set by external resistors connected between the op amp's inverting input pin  $A_{IN-}$  and the transmit gain set pin  $GS_x$ .

## Block Diagram, µPD9513AD

#### Block Diagram, µPD9514AD

#### **Operational Description**

#### Power-Up

The  $\mu$ PD9513AD and 9514AD reset on power-up to maintain the integrity of the PCM highway during the power-up sequence. For approximately four frames (500  $\mu$ s) after power is applied, digital outputs D<sub>X</sub> and  $\overline{\text{TS}_X}$  are held in a high-impedance state and digital output SIG<sub>R</sub> is held low. After this initial delay, the transmit digital outputs become functional and occur in the proper time slot. The SIG<sub>R</sub> output remains low until it is updated during a signaling frame.

Because of the autozero circuit settling time, analog circuits, such as filters, sample-and-hold, and D/A converters, require about 60 ms to reach equilibrium. Thus, signaling information is available almost immediately, whereas valid voice information is delayed.

#### **Power-Down and Standby Modes**

Power-down and standby modes reduce power consumption from 80 mW to 8 mW.

Holding PDN low establishes the power-down mode, disabling most internal circuits. Only circuits that are required for power-up, such as the power-down controller, data clock, and frame sync buffers, stay

enabled. Within 10  $\mu$ s after  $\overline{PDN}$  is held low, digital outputs  $D_X$  and  $\overline{TS}_X$  go to high impedance and  $SIG_R$  goes low. Pulling PDN up to high restores the power-up mode.

The standby mode allows the user to selectively power down the transmit and receive sections by holding low the frame sync clock inputs  $FS_X$  and  $FS_R$ , respectively.

#### **Fixed Data Rate Mode**

Connecting the DCLK<sub>R</sub> pin to V<sub>SS</sub> selects the fixed data rate mode. In this mode, transmit and receive clocks CLK<sub>X</sub> and CLK<sub>R</sub> serve as master clocks to operate the codec and filter circuits and also as PCM data clocks to clock bits to and from the PCM highway. By strapping at the CLKSEL pin, CLK<sub>X</sub> and CLK<sub>R</sub> are selected to be 2.048, 1.544, or 1.536 MHz. Only these three frequencies are possible in the fixed data rate mode.

Frame synchronization clock  $FS_X$  controls data transfer from  $D_X$  to the PCM highway. The clock sets the channel sampling frequency at 8 kHz. After  $FS_X$  is detected high on the falling edge of  $CLK_X$ , data is clocked out serially on the next eight rising edges of  $CLK_X$ . In the following falling edge, the three-state output at  $D_X$  returns to the floating state.

www.DataSheet4U.com

The timeslot strobe enable output  $\overline{TS_X}$  is low during data transfer out of  $D_X$ . This signal can be used to gate the 8-bit word onto the PCM highway when an external buffer is driving the output line.

Receive data is clocked in from the PCM highway after  $FS_R$  is detected high on the falling edge of  $CLK_R$ . The next eight falling edges of  $CLK_R$  latch the receive data.

#### Variable Data Rate Mode

Connecting the DCLK<sub>R</sub> pin to the external PCM data clock (instead of to  $V_{SS}$ ) selects the variable data rate mode. The clock frequency can vary from 64 kHz to 2.048 MHz. Master clock inputs CLK<sub>R</sub> and CLK<sub>X</sub> are still restricted to 2.048, 1.544, or 1.536 MHz as selected by strapping at the CLKSEL pin.

Operation in this mode is similar to the fixed data rate mode except the PCM data clocks are DCLK $_{\rm X}$  and DCLK $_{\rm R}$  instead of CLK $_{\rm X}$  and CLK $_{\rm R}$ . Because signaling is not supported, the frame sync pulses are single width.

#### Signaling

The signaling function is available only with the  $\mu$ PD9514AD in the fixed data rate mode. The width of the pulse on FS<sub>X</sub> and FS<sub>R</sub> distinguishes between a signaling and nonsignaling frame. A single-width pulse (one master clock period) designates a nonsignaling frame; a double-width pulse designates a signaling frame.

When data is transferred onto  $D_X$  in a transmit signaling frame, the least significant bit (LSB) of the encoded PCM data is replaced with the signaling state present on  $SIG_X$ . In a receive signaling frame, the seven most significant bits of the PCM data are routed to the decoder and the least significant bit is latched at the  $SIG_R$  output until updated in the next signaling frame. The D/A converter compensates for the lost LSB and minimizes deterioration in SD and GT characteristics.

#### **Asynchronous Operation**

The  $\mu$ PD9514AD transmit and receive sections can operate asynchronously. Therefore, in either fixed or variable data rate mode, master clocks CLK<sub>R</sub> and CLK<sub>X</sub> can be independent of each other.

#### **Analog Loopback**

The  $\mu$ PD9514AD offers an internal loopback test capability. Setting the LOOP input pin high connects the vf receive port to the vf transmit port internally: PWRO+ to A<sub>IN+</sub>, GS<sub>R</sub> to PWRO-, and A<sub>IN-</sub> to GS<sub>X</sub>. This feature allows the user to remotely test the line circuit by comparing the digital codes sent to digital receive port D<sub>R</sub> with the resulting codes output at digital transmit port D<sub>X</sub>. Because of the difference in transmission levels, a 0-dBm0 digital tone input at D<sub>R</sub> returns to D<sub>X</sub> as a +3-dBm0 digital tone output. Therefore, the maximum input level that can be tested with analog loopback is +3 dBm0.

#### **VF Transmit**

At the vf transmit input, an uncommitted operational amplifier is provided for gain adjustment in the passband. The op amp input leads are  $A_{IN-}$  and  $A_{IN+}$  and the output is  $GS_X.$  For normal operation as a noninverting amplifier, the device functions best with gain settings of 0 to 20 dB, load resistance (including the gain-setting resistance) greater than 10  $k\Omega,$  and load capacitance less than 50 pF. See figure 1.

The op amp output goes through a bandpass filter that fulfills the flatness and frequency response specified by CCITT G.712. The filter includes an antialiasing section that has 35 dB attenuation at the 8-kHz sampling frequency and a notch section that rejects 50- and 60-Hz power line frequencies.

The filtered signal continues to the encoder sample-and-hold circuit. With the on-chip autozero circuit, which corrects for dc offset, and the precision voltage reference, the encoder performs the A/D conversion with  $\mu$ -law or A-law companding as selected by strapping at the ASEL pin. The encoded PCM data is stored in the output register waiting for FS<sub>X</sub> to initiate data transfer to the PCM highway.

#### **VF Receive**

Digital data entering at  $D_R$  is decoded through the D/A converter according to the selected companding law. A lowpass filter corrects for the  $(\sin x)/x$  response of the decoder. At the vf receive output port, a differential power amplifier can drive balanced loads as low as 600 ohms. Two external resistors set the amplifier gain between 0 and -12 dB. See figure 2.

Either of the power amp outputs can drive an unbalanced load as low as 300 ohms.

Figure 1. Transmit Amplifier Gain Setting

Figure 2. Receive Power Amplifier Gain Setting

#### **Absolute Maximum Ratings**

$T_A = +25\,^{\circ}C$

| Parameter                             | Symbol            | Rating                             | Conditions                                                                         |

|---------------------------------------|-------------------|------------------------------------|------------------------------------------------------------------------------------|

| Supply voltage                        | $V_{DD}$          | -0.3 to +7.0 V                     |                                                                                    |

|                                       | $V_{SS}$          | -7.0 to +0.3 V                     |                                                                                    |

| Analog input voltage                  | V <sub>AIN</sub>  | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ V | Pins A <sub>IN+</sub> ,<br>A <sub>IN-</sub> , GS <sub>X</sub> ,<br>GS <sub>R</sub> |

| Digital input<br>voltage              | V <sub>DIN1</sub> | $-0.3$ to $V_{DD} + 0.3 V$         | For pins other than CLKSEL                                                         |

|                                       | V <sub>DIN2</sub> | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ V | Pins CLKSEL,<br>DCLK <sub>R</sub>                                                  |

| Voltage applied to digital output pin | V <sub>DOUT</sub> | 0.3 to V <sub>DD</sub> + 0.3 V     | For all digital output pins                                                        |

| Analog ground pin voltage             | V <sub>AG</sub>   | ±0.1 V                             | $V_{DG} = 0$                                                                       |

| Analog output pin short-circuit time  | t <sub>S</sub>    | Unlimited                          | Pins PWR0+,<br>PWR-                                                                |

| Power dissipation                     | PD                | 500 mW                             |                                                                                    |

| Operating temperature                 | T <sub>OPT</sub>  | 0 to +70°C                         |                                                                                    |

| Storage<br>temperature                | T <sub>STG</sub>  | −65 to +150°C                      |                                                                                    |

| Soldering<br>temperature              | T <sub>SOLD</sub> | +260°C                             | Less than 10 seconds                                                               |

#### Note:

- (1) Voltages are based on the condition that  $V_{DG} = V_{AG} = 0$ .

- (2) Connection between AGND and DGND pins should be as short as possible.

Recommended Operating Conditions  $T_A=0 \text{ to } +70\,^{\circ}\text{C}; \, V_{DD}=+5\pm0.25\,\text{V}; \, V_{SS}=-5\pm0.25\,\text{V}; \, V_{DG}=V_{AG}=0$

|                                                                     |                                          | Limits                |             |                                       |      | Test                                  |

|---------------------------------------------------------------------|------------------------------------------|-----------------------|-------------|---------------------------------------|------|---------------------------------------|

| Parameter                                                           | Symbol                                   | Min                   | Тур         | Max                                   | Unit | Conditions                            |

| Power                                                               |                                          |                       |             |                                       |      |                                       |

| Supply voltage                                                      | V <sub>DD</sub>                          | +4.75                 | +5.0        | +5.25                                 | ٧    |                                       |

|                                                                     | V <sub>SS</sub>                          | -5.25                 | -5.0        | -4.75                                 | V    |                                       |

| Analog                                                              |                                          |                       |             |                                       |      |                                       |

| Transmit amplifier                                                  |                                          |                       |             |                                       |      | · · · · · · · · · · · · · · · · · · · |

| Input analog voltage                                                | V <sub>AIN</sub>                         | <b>-2.17</b>          |             | +2.17                                 | ٧    |                                       |

| Gain setting range                                                  | GR <sub>AX</sub>                         | 0                     |             | +20                                   | dB   |                                       |

| Load resistance                                                     | RLAX                                     | 10                    |             |                                       | kΩ   |                                       |

| Load capacitance                                                    | CLAX                                     |                       |             | 50                                    | pF   |                                       |

| Receive amplifier                                                   |                                          |                       |             |                                       |      | <del></del>                           |

| Load resistance                                                     | RLAR                                     | 300                   |             |                                       | Ω    | Unbalanced output                     |

|                                                                     |                                          | 600                   |             |                                       | Ω    | Balanced output                       |

| Load capacitance                                                    | CL <sub>AR</sub>                         |                       |             | 100                                   | pF   | Pins PWR0+, PWR0-                     |

| Digital                                                             |                                          |                       | <del></del> |                                       |      |                                       |

| Input at digital pins<br>other than CLKSEL                          |                                          |                       |             |                                       |      |                                       |

| Low voltage                                                         | $v_{IL}$                                 | 0                     |             | 0.8                                   | ٧    |                                       |

| High voltage                                                        | V <sub>IH</sub>                          | 2.0                   |             | V <sub>DD</sub>                       | ٧    |                                       |

| Input at CLKSEL pin                                                 |                                          |                       |             |                                       |      |                                       |

| Low voltage                                                         | $V_{ILO}$                                | V <sub>SS</sub>       |             | $V_{SS}-0.5$                          | ٧    | $f_{CLK} = 2.048 \text{ MHz}$         |

| Intermediate voltage                                                | V <sub>IIO</sub>                         | $V_{DG}-0.5$          |             | V <sub>DG</sub> + 0.5                 | ٧    | f <sub>CLK</sub> = 1.544 MHz          |

| High voltage                                                        | V <sub>IHO</sub>                         | V <sub>DD</sub> — 0.5 |             | V <sub>DD</sub>                       | ٧    | f <sub>CLK</sub> = 1.536 MHz          |

| Clock                                                               |                                          |                       |             |                                       |      |                                       |

| Master clock frequency                                              | f <sub>CLK</sub><br>(1/t <sub>CY</sub> ) |                       | 1.536       |                                       | MHz  | CLKSEL connected to V <sub>DD</sub>   |

|                                                                     |                                          |                       | 1.544       |                                       | MHz  | CLKSEL connected to DGND              |

|                                                                     |                                          | -                     | 2.048       |                                       | MHz  | CLKSEL connected to V <sub>SS</sub>   |

| Master clock duty cycle                                             | tcdc                                     | 45                    | 50          | 55                                    | %    |                                       |

| Data clock frequency                                                | f <sub>DCLK</sub>                        | 64 kHz                |             | 2.048                                 | MHz  |                                       |

| Master clock pulse width                                            | <sup>t</sup> CLK                         | 220                   |             |                                       | ns   |                                       |

| Frame sync clock freq                                               | f <sub>FS</sub>                          | 7.9996                | 8.0000      | 8.0004                                | kHz  |                                       |

| D <sub>R</sub> setup time                                           | t <sub>DSR</sub>                         | 10                    |             | · · · · · · · · · · · · · · · · · · · | ns   |                                       |

| D <sub>R</sub> hold time                                            | t <sub>DHR</sub>                         | 60                    |             | ···                                   | ns   |                                       |

| - П                                                                 |                                          |                       |             | 30                                    | ns   |                                       |

|                                                                     | t <sub>R</sub>                           |                       |             |                                       |      |                                       |

| Clock rise time                                                     | t <sub>R</sub>                           |                       |             | 30                                    | ns   |                                       |

| Clock rise time<br>Clock fall time                                  | t <sub>F</sub>                           |                       |             |                                       |      |                                       |

| Clock rise time<br>Clock fall time<br><b>Timing in Fixed Data R</b> | t <sub>F</sub><br>ate Mode               | 100                   |             | 30                                    | ns   |                                       |

| Clock rise time<br>Clock fall time                                  | t <sub>F</sub>                           | 100                   |             |                                       |      | μPD9514AD                             |

#### **Recommended Operating Conditions (cont)**

|                                      |                   | •             | Limits |                                        |    | Test                                                |

|--------------------------------------|-------------------|---------------|--------|----------------------------------------|----|-----------------------------------------------------|

| Parameter                            | Symbol            | Min           | Тур    | Тур Мах                                |    | Conditions                                          |

| Timing in Variable Dat               | a Rate Mode       |               |        |                                        |    |                                                     |

| Timeslot delay                       | t <sub>TSD</sub>  | 140           |        | t <sub>DCY</sub> — 140                 | ns | Referenced to DCLK <sub>X</sub> , DCLK <sub>R</sub> |

| Frame sync delay                     | t <sub>FSD</sub>  | 100           |        | t <sub>CY</sub> - 100                  | ns |                                                     |

| Data clock pulse width               | †DCLK             | 220           |        |                                        | ns |                                                     |

| Timing in Variable Dat               | a Rate Mode, 64   | -kb Operation | 7      | ************************************** |    |                                                     |

| Transmit frame sync minimum downtime | t <sub>FSLX</sub> | 488           |        |                                        | ns | $FS_X$ is TTL high for remainder of frame           |

| Receive frame sync minimum downtime  | <sup>†</sup> FSLR | 1952          |        |                                        | ns | $FS_R$ is TTL high for remainder of frame           |

| Data clock pulse width               | <sup>†</sup> DCLK | 0.195         |        | 10                                     | μS |                                                     |

#### **DC Characteristics**

$T_A=0$  to  $+70\,^{\circ}\text{C};\,V_{DD}=+5\,\pm0.25\,\text{V};\,V_{SS}=-5\,\pm0.25\,\text{V};\,V_{DG}=V_{AG}=0$  DCLK  $_R=$  DCLK  $_X=2.048\,\text{MHz}$

All outputs are unloaded unless otherwise specified.

For typical values,  $T_A = +25\,^{\circ}\text{C}$ ,  $V_{DD} = +5\,\text{V}$ , and  $V_{SS} = -5\,\text{V}$ .

|                            |                  | Limits |      |       |      | Test                                                                   |

|----------------------------|------------------|--------|------|-------|------|------------------------------------------------------------------------|

| Parameter                  | Symbol           | Min    | Тур  | Max   | Unit | Conditions                                                             |

| Power                      |                  |        |      |       |      |                                                                        |

| Normal operating current   | lDD              |        | 8    | 13.0  | mA   |                                                                        |

|                            | I <sub>SS</sub>  |        | -8   | -13.0 | mA   |                                                                        |

| Power-down current         | IDDPD            |        | 0.8  | 1.3   | mA   | 10 μs after PDN is set to low.                                         |

|                            | ISSPD            |        | -0.8 | -1.0  | mA   | <del></del>                                                            |

| Standby current            | IDDST            |        | 0.8  | 1.3   | mA   | 300 ms after $FS_X$ and $FS_R$ are set to low.                         |

|                            | ISSST            |        | -0.8 | -1.0  | mA   |                                                                        |

| Power dissipation          |                  |        |      |       | •    |                                                                        |

| Normal                     | $P_{D}$          |        | 80   | 136.5 | mW   |                                                                        |

| Power-down                 | P <sub>DPD</sub> |        | 8    | 12.1  | mW   | 10 µs after PDN is set to low.                                         |

| Standby                    | P <sub>DST</sub> |        | 8    | 12.1  | mW   | 300 ms after $FS_X$ and $FS_R$ are set to low.                         |

| Digital Interface          |                  |        |      |       |      |                                                                        |

| Digital input current      | I <sub>ID1</sub> |        |      | 10    | μΑ   | $V_{	extsf{DIN}} = 0 	ext{ to } V_{	extsf{DD}}$                        |

|                            | I <sub>ID2</sub> |        |      | 10    | μΑ   | Pins CLKSEL, DCLK <sub>R</sub> ; $V_{DIN} = V_{SS}$ to $V_{DD}$        |

| Output low voltage         | V <sub>OL</sub>  |        |      | 0.4   | V    | Pins $D_X$ , $\overline{TS_X}$ , $SIG_R$ ; $I_{0L} \le 3.2 \text{ mA}$ |

| Output high voltage        | V <sub>OH</sub>  | 2.4    |      |       | V    | Pin $D_X$ , $I_{OH} \le 9.6$ mA;<br>Pin $SIG_R$ , $I_{OH} \le 1.2$ mA  |

| Digital output capacitance | C <sub>OD</sub>  |        | 5    |       | pF   |                                                                        |

| Digital input capacitance  | C <sub>ID</sub>  |        |      | 10    | pF   |                                                                        |

#### **DC Characteristics (cont)**

|                              |                  |       | Limits |      |      | Test<br>Conditions                                                          |

|------------------------------|------------------|-------|--------|------|------|-----------------------------------------------------------------------------|

| Parameter                    | Symbol           | Min   | Тур    | Max  | Unit |                                                                             |

| Transmit Amplifier           |                  |       |        |      |      |                                                                             |

| Input leakage current        | IB               |       |        | 100  | nA   | $V_{AIN} = -2.17 \text{ to } 2.17 \text{ V};$<br>Pins $A_{IN+}$ , $A_{IN-}$ |

| Input resistance             | R <sub>IN</sub>  | 10    |        |      | MΩ   |                                                                             |

| Input offset voltage         | ν <sub>ιο</sub>  | -25   |        | 25   | m۷   |                                                                             |

| Common mode rejection        | CMRR             | 55    |        |      | dB   | $V_{AIN} = -2.17 \text{ to } +2.17 \text{ V}$                               |

| Voltage gain                 | A <sub>V</sub>   | 5000  |        |      |      |                                                                             |

| Maximum output voltage swing | V <sub>CM</sub>  | -2.17 |        | 2.17 | ٧    | $R_L \ge 10 \text{ k}\Omega$                                                |

| Receive Power Amplifier      | •                |       |        |      |      |                                                                             |

| Output offset voltage        | V <sub>0S</sub>  | -150  | 75     | 150  | mV   | Unbalanced output connection, pins PWR0+ and PWR0-                          |

| Maximum output voltage swing |                  |       |        |      |      |                                                                             |

| Unbalanced output            | V <sub>CM1</sub> | -3.06 |        | 3.06 | ٧    | $R_L \ge 300 \Omega$                                                        |

| Balanced output              | V <sub>CM2</sub> | 6.12  |        | 6.12 | V    | R <sub>L</sub> ≥ 600 Ω                                                      |

### **Transmission Characteristics**

$T_A = +25$ °C;  $V_{DD} = +5 \pm 0.25$  V;  $V_{SS} = -5 \pm 0.25$  V Analog input signal level  $V_{IN} = 0$  dBm0 (f = 1020 Hz); analog input op amp gain = 1 (noninverting) Digital input signal level = 0 dBm0 (f = 1020 Hz); receive output power amplifier gain = 1; unbalanced output (PWRO+) unless otherwise specified

|                                                           |                   | Limits   |     |       |      | Test                                                                                                                                                              |  |

|-----------------------------------------------------------|-------------------|----------|-----|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                 | Symbol            | Min      | Тур | Max   | Unit | Conditions                                                                                                                                                        |  |

| Gain                                                      |                   | <u> </u> |     |       |      |                                                                                                                                                                   |  |

| Encoder milliwatt response (transmit gain tolerance)      | EmW               | -0.15    |     | +0.15 | dBm0 | μ-law: V <sub>IN</sub> = 1.064 V rms<br>A-law: V <sub>IN</sub> = 1.068 V rms<br>V <sub>DD</sub> = +5 V; V <sub>SS</sub> = -5 V                                    |  |

| EmW variation with temperature and power supply           | EmW <sub>TS</sub> | -0.12    |     | +0.12 | dΒ   | T <sub>A</sub> = 0 to +70 °C                                                                                                                                      |  |

| Digital milliwatt<br>response (receive<br>gain tolerance) | DmW               | -0.15    |     | +0.15 | dBm0 | Measured relative to 0TLP <sub>R</sub> ; signal input per CCITT recommendation G.712; output signal of 1000 Hz; $V_{DD} = +5 \text{ V}$ ; $V_{SS} = -5 \text{ V}$ |  |

| DmW variation with temperature and power supply           | DmW <sub>TS</sub> | -0.08    |     | +0.08 | dB   | T <sub>A</sub> = 0 to +70 °C                                                                                                                                      |  |

| Transmission Characte | ristics ( | (cont) |

|-----------------------|-----------|--------|

|-----------------------|-----------|--------|

|                                                           |                                       | Lir                                            | nits                                                 |                            | Test                                                                                                          |

|-----------------------------------------------------------|---------------------------------------|------------------------------------------------|------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------|

| arameter                                                  | Symbol                                | Min T                                          | yp Max                                               | Unit                       | Conditions                                                                                                    |

| Gain (cont)                                               |                                       |                                                |                                                      |                            |                                                                                                               |

| ero transmission level point,<br>ansmit section           |                                       |                                                |                                                      |                            |                                                                                                               |

| μ-law                                                     | OTLP1 <sub>X</sub>                    | +2                                             | 2.76                                                 | dBm                        | Referenced to 600 Ω                                                                                           |

|                                                           |                                       | +1                                             | 1.00                                                 | dBm                        | Referenced to 900 $\Omega$                                                                                    |

| A-law                                                     | 0TLP2 <sub>X</sub>                    | +2                                             | .79                                                  | dBm                        | Referenced to 600 $\Omega$                                                                                    |

|                                                           |                                       | +1                                             | 1.03                                                 | dBm                        | Referenced to 900 Ω                                                                                           |

| ero transmission level point, eceive section              |                                       |                                                |                                                      |                            |                                                                                                               |

| μ-law                                                     | 0TLP1 <sub>R</sub>                    | +5                                             | 5.76                                                 | dBm                        | Referenced to 600 Ω                                                                                           |

|                                                           |                                       | +4                                             | 1.00                                                 | dBm                        | Referenced to 900 $\Omega$                                                                                    |

| A-law                                                     | 0TLP2 <sub>R</sub>                    | +5                                             | 5.79                                                 | dBm                        | Referenced to 600 $\Omega$                                                                                    |

|                                                           |                                       | +4                                             | .03                                                  | dBm                        | Referenced to 900 Ω                                                                                           |

| $\mu$ -law                                                | GT1 <sub>X</sub>                      | -0.25                                          | +0.25                                                | dB                         | +3 to -40 dBm0                                                                                                |

| ransmit gain tracking error                               |                                       |                                                |                                                      |                            |                                                                                                               |

| μιαν                                                      | u i i X                               | -0.5                                           | +0.5                                                 | dB                         | -40 to -50 dBm0                                                                                               |

|                                                           |                                       | -1.2                                           | +1.2                                                 | dB                         | -50 to -55 dBm0                                                                                               |

| A-law                                                     | GT2 <sub>X</sub>                      | -0.25                                          | +0.25                                                | dB                         | +3 to -40 dBm0                                                                                                |

|                                                           | <b>X</b>                              | -0.5                                           | +0.5                                                 | dB                         | -40 to -50 dBm0                                                                                               |

|                                                           |                                       | -1.2                                           | +1.2                                                 |                            |                                                                                                               |

|                                                           |                                       | -1. <u>Z</u>                                   | 1 1 - 6                                              | dB                         | −50 to −55 dBm0                                                                                               |

| A-law, white noise                                        | GT3 <sub>X</sub>                      |                                                | 0.1                                                  | dB<br>dB                   | -50 to -55 dBm0<br>-10 to -55 dBm0                                                                            |

| A-law, white noise input CCITT G.712                      | GT3 <sub>X</sub>                      |                                                |                                                      |                            | −10 to −55 dBm0                                                                                               |

| input CCITT G.712                                         | GT3 <sub>X</sub>                      |                                                | 0.1                                                  | dB                         | −10 to −55 dBm0                                                                                               |

| input CCITT G.712                                         | GT3 <sub>X</sub>                      |                                                | 0.1                                                  | dB                         | −10 to −55 dBm0                                                                                               |

| input CCITT G.712<br>Receive gain tracking error          | · · · · · · · · · · · · · · · · · · · |                                                | 0.1                                                  | dB<br>dB                   | -10 to -55 dBm0<br>-55 to -60 dBm0                                                                            |

| input CCITT G.712<br>Receive gain tracking error          | · · · · · · · · · · · · · · · · · · · | -0.25                                          | 0.1<br>0.3<br>+0.25                                  | dB<br>dB                   | -10 to -55 dBm0<br>-55 to -60 dBm0<br>+3 to -40 dBm0<br>-40 to -50 dBm0                                       |

| input CCITT G.712<br>Receive gain tracking error          | · · · · · · · · · · · · · · · · · · · | -0.25<br>-0.5                                  | 0.1<br>0.3<br>+0.25<br>+0.5                          | dB<br>dB<br>dB             | -10 to -55 dBm0<br>-55 to -60 dBm0<br>+3 to -40 dBm0<br>-40 to -50 dBm0                                       |

| input CCITT G.712<br>Receive gain tracking error<br>μ-law | GT1 <sub>R</sub>                      | -0.25<br>-0.5<br>-1.2                          | 0.1<br>0.3<br>+0.25<br>+0.5<br>+1.2                  | dB<br>dB<br>dB<br>dB       | -10 to -55 dBm0 -55 to -60 dBm0 +3 to -40 dBm0 -40 to -50 dBm0 -50 to -55 dBm0 +3 to -40 dBm0                 |

| input CCITT G.712<br>Receive gain tracking error<br>μ-law | GT1 <sub>R</sub>                      | -0.25<br>-0.5<br>-1.2<br>-0.25                 | 0.1<br>0.3<br>+0.25<br>+0.5<br>+1.2<br>+0.25         | dB<br>dB<br>dB<br>dB<br>dB | -10 to -55 dBm0 -55 to -60 dBm0 +3 to -40 dBm0 -40 to -50 dBm0 -50 to -55 dBm0 +3 to -40 dBm0 -40 to -50 dBm0 |

| input CCITT G.712<br>Receive gain tracking error<br>μ-law | GT1 <sub>R</sub>                      | -0.25<br>-0.5<br>-1.2<br>-0.25<br>-0.5<br>-1.2 | 0.1<br>0.3<br>+0.25<br>+0.5<br>+1.2<br>+0.25<br>+0.5 | dB dB dB dB dB dB dB       | -10 to -55 dBm0 -55 to -60 dBm0 +3 to -40 dBm0 -40 to -50 dBm0 -50 to -55 dBm0                                |

## **Transmission Characteristics (cont)**

|                                                      |                     |              | Limits    |                 |              | Test                                                                                                        |

|------------------------------------------------------|---------------------|--------------|-----------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------|

| Parameter                                            | Symbol              | Min          | Тур       | Max             | Unit         | Conditions                                                                                                  |

| Frequency Response Analog input operational amplifie | er gain = 1 (no     | ninverting); | receive o | output pow      | er amplifier | gain = 1 (unbalanced, PWRO+)                                                                                |

| Transmit branch; gain relative to                    | G <sub>RX</sub> 1   |              |           | -30             | dB           | 16.67 Hz                                                                                                    |

| gain at 1020 Hz, 0 dBm0                              | G <sub>RX</sub> 2   |              |           | -25             | dB           | 50 Hz                                                                                                       |

|                                                      | G <sub>RX</sub> 3   |              |           | -23             | dB           | 60 Hz                                                                                                       |

|                                                      | G <sub>RX</sub> 4   | -1.8         |           | -0.125          | dB           | 200 Hz                                                                                                      |

|                                                      | G <sub>RX</sub> 5   | -0.125       |           | +0.125          | dB           | 0.3 to 3.0 kHz                                                                                              |

|                                                      | G <sub>RX</sub> 6   | -0.35        |           | +0.03           | dB           | 3.3 kHz                                                                                                     |

|                                                      | G <sub>RX</sub> 7   | -0.7         |           | -0.1            | dB           | 3.4 kHz                                                                                                     |

|                                                      | G <sub>RX</sub> 8   |              |           | -14             | dB           | 4.0 kHz                                                                                                     |

|                                                      | G <sub>RX</sub> 9   |              |           | -32             | dB           | 4.6 kHz and above                                                                                           |

| Receive branch; gain relative to                     | G <sub>RR</sub> 1   |              |           | +0.125          | dB           | Below 200 Hz                                                                                                |

| gain at 1020 Hz, 0 dBm0                              | G <sub>RR</sub> 2   | -0.5         |           | +0.125          | dB           | 200 Hz                                                                                                      |

|                                                      | G <sub>RR</sub> 3   | -0.125       |           | +0.125          | dB           | 0.3 to 3.0 kHz                                                                                              |

|                                                      | G <sub>RR</sub> 4   | -0.35        |           | +0.03           | dB           | 3.3 kHz                                                                                                     |

|                                                      | G <sub>RR</sub> 5   | -0.7         |           | -0.1            | dB           | 3.4 kHz                                                                                                     |

|                                                      | G <sub>RR</sub> 6   |              |           | -14             | dB           | 4.0 kHz                                                                                                     |

|                                                      | G <sub>RR</sub> 7   |              |           | -30             | dB           | 4.6 kHz and above                                                                                           |

| Noise                                                |                     |              |           |                 |              |                                                                                                             |

| Transmit noise                                       | N <sub>XC</sub> 1   |              | ninies a  | 15              | dBrnc0       | A <sub>IN+</sub> is grounded to AGND; input amplifier gain = 1; C-message weighting                         |

|                                                      | N <sub>XC</sub> 2   |              |           | 18              | dBrnc0       | Same as N <sub>XC</sub> 1; signaling data added to frame 6                                                  |

|                                                      | N <sub>XP</sub>     |              |           | <del></del> 75  | dBm0p        | Same as N <sub>XC</sub> 1 except psophometric weighting                                                     |

| Receive noise                                        | N <sub>RC</sub> 1   |              |           | 11              | dBrnc0       | D <sub>R</sub> = 11111111; measure at PWRO+ with C-message weighting                                        |

|                                                      | N <sub>RC</sub> 2   |              |           | 12              | dBrnc0       | Same as N <sub>RC</sub> 1 except D <sub>R</sub> is zero code with sign bit toggled at 1-kHz rate            |

|                                                      | N <sub>RP</sub>     |              |           | <del>-79</del>  | dBm0p        | Same as N <sub>RC</sub> 1 except D <sub>R</sub> is the lowest positive decode level; psophometric weighting |

| Single-frequency noise                               | NSF                 |              |           | 50              | dBm0         | End-to-end measurement; CCITT G.712 4.2                                                                     |

| Crosstalk, transmit to receive                       | CT <sub>TR</sub>    |              |           | <del>-7</del> 1 | dB           | Transmit input at $A_{IN+} = 0$ -dBm0, 1020-Hz analog signal; $D_R = I_{OW}$ level                          |

| Crosstalk, receive to<br>transmit                    | CT <sub>RT</sub>    |              |           | 71              | dB           | $A_{IN+}$ is grounded to AGND; $D_R = 0$ -dBm0, 1020-Hz digital signal                                      |

| Transmit section power                               | PSRR <sub>T</sub> 1 |              | 40        |                 | dB           | +100-mV signal on V <sub>DD</sub>                                                                           |

| supply rejection ratio                               | PSRR <sub>T</sub> 2 |              | 40        |                 | dB           | +100-mV signal on V <sub>SS</sub>                                                                           |

| Receive section power                                | PSRR <sub>R</sub> 3 |              | 30        |                 | ďΒ           | +100 mV signal on V <sub>DD</sub>                                                                           |

| supply rejection ratio                               | PSRR <sub>R</sub> 4 |              | 30        |                 | dB           | +100 mV signal on V <sub>SS</sub>                                                                           |

## **Transmission Characteristics (cont)**

| Parameter                                        | Symbol           | Limits |       |            |           | Test                                              |

|--------------------------------------------------|------------------|--------|-------|------------|-----------|---------------------------------------------------|

|                                                  |                  | Min    | Тур   | Max        | _<br>Unit | Conditions                                        |

| Distortion                                       |                  |        |       |            |           |                                                   |

| Transmit signal-to-distortion ratio              |                  |        |       |            |           |                                                   |

| μ-law, CCITT G.712<br>Method 2                   | SD1 <sub>X</sub> | 36     |       |            | dB        | 0 to -30 dBm0                                     |

|                                                  |                  | 30     |       |            | dB        | -30 to -40 dBm0                                   |

|                                                  |                  | 25     |       |            | dB        | -40 to -45 dBm0                                   |

| A-law, CCITT G.712<br>Method 2                   | SD2 <sub>X</sub> | 36     |       |            | dB        | 0 to -30 dBm0                                     |

|                                                  |                  | 30     |       |            | dB        | -30 to −40 dBm0                                   |

|                                                  |                  | 25     |       |            | dB        | -40 to -45 dBm0                                   |

| A-ław, CCITT G.712<br>Method 1                   | SD3 <sub>X</sub> |        | 38    |            | dB        | −6 to −27 dBm0                                    |

|                                                  |                  |        | 36    |            | dB        | -34 dBm0                                          |

|                                                  |                  |        | 31    |            | dB        | -40 dBm0                                          |

|                                                  |                  |        | 16    |            | dB        | -55 dBm0                                          |

| Receive signal-to-distortion ratio               |                  |        |       |            |           |                                                   |

| μ-law, CCITT G.712<br>Method 2                   | SD1 <sub>R</sub> | 36     |       |            | dB        | 0 to -30 dBm0                                     |

|                                                  |                  | 30     |       |            | dB        | -30 to -40 dBm0                                   |

|                                                  |                  | 25     | · - · |            | dB        | -40 to -45 dBm0                                   |

| A-law, CCITT G.712<br>Method 2                   | SD2 <sub>R</sub> | 36     |       |            | dB        | 0 to -30 dBm0                                     |

|                                                  |                  | 30     |       |            | dB        | -30 to -40 dBm0                                   |

|                                                  |                  | 25     |       |            | dB        | -40 to -45 dBm0                                   |

| A-law, CCITT G.712<br>Method 1                   | SD3 <sub>R</sub> |        | 38    |            | dB        | -6 to −27 dBm0                                    |

|                                                  |                  |        | 36    |            | dB        | -34 dBm0                                          |

|                                                  |                  |        | 31    |            | dB        | -40 dBm0                                          |

|                                                  |                  |        | 16    |            | dB        | -55 dBm0                                          |

| Transmit single-frequency<br>distortion products | DPX              |        |       | -46        | dBm0      | AT&T Advisory No. 64<br>(3.8) 0-dBm0 input signal |

| Receive single-frequency<br>distortion products  | DPR              |        |       | -46        | dBm0      | AT&T Advisory No. 64<br>(3.8) 0-dBm0 input signal |

| ntermodulation distortion, end-to-end            |                  |        |       |            |           |                                                   |

| CCITT G.712 (7.1)                                | IMD <sub>1</sub> |        |       | -35        | dB        |                                                   |

| CCITT G.712 (7.2)                                | IMD <sub>2</sub> |        |       | <b>–49</b> | dBm0      |                                                   |

| Spurious out-of-band<br>signals, end-to-end      | SOS              |        |       | -25        | dBm0      | CCITT G.712 (6.1)                                 |

| Spurious in-band<br>signals, end-to-end          | SIS              |        |       | -40        | dBm0      | CCITT G.712 (9)                                   |

| Transmit absolute delay                          | D <sub>AX</sub>  | •      | 245   |            | μs        | Fixed data rate, f <sub>CLKX</sub> = 2.048 MHz    |

## **Transmission Characteristics (cont)**

| Parameter                                                           |                   | Limits |     |                                       |      | Test                                           |

|---------------------------------------------------------------------|-------------------|--------|-----|---------------------------------------|------|------------------------------------------------|

|                                                                     | Symbol            | Min    | Тур | Max                                   | Unit | Conditions                                     |

| Distortion (cont)                                                   |                   |        |     |                                       |      |                                                |

| Transmit differential<br>envelope delay relative to D <sub>AX</sub> | D <sub>DX</sub>   |        |     |                                       |      |                                                |

| 500 to 600 Hz                                                       |                   |        | 170 |                                       | μS   |                                                |

| 600 to 1000 Hz                                                      |                   |        | 95  |                                       | μS   |                                                |

| 1000 to 2500 Hz                                                     |                   |        | 45  |                                       | μS   |                                                |

| 2600 to 2800 Hz                                                     |                   |        | 105 |                                       | μS   |                                                |

| Receive absolute delay                                              | D <sub>AR</sub>   |        | 190 |                                       | μS   | Fixed data rate. f <sub>CLKR</sub> = 2.048 MHz |

| Receive differential<br>envelope delay relative to D <sub>AR</sub>  | D <sub>DR</sub>   |        |     |                                       |      |                                                |

| 500 to 600 Hz                                                       |                   |        | 45  |                                       | μS   |                                                |

| 600 to 1000 Hz                                                      |                   | _      | 35  |                                       | μs   |                                                |

| 1000 to 2500 Hz                                                     |                   |        | 85  |                                       | μS   |                                                |

| 2600 to 2800 Hz                                                     |                   |        | 110 |                                       | μS   |                                                |

| Timing Parameters in Fixed D                                        | ata Rate Mode     |        |     |                                       |      |                                                |

| Data enable delay                                                   | t <sub>DZX</sub>  | 0      |     | 145                                   | ns   | C <sub>L</sub> < 100 pF                        |

| Data delay                                                          | t <sub>DDX</sub>  | 0      |     | 145                                   | ns   | C <sub>L</sub> < 100 pF                        |

| Data hold time                                                      | t <sub>HZX</sub>  | 60     |     | 220                                   | ns   | $C_L = 0$                                      |

| TS <sub>X</sub> enable delay                                        | t <sub>SON</sub>  | 0      |     | 145                                   | ns   | C <sub>L</sub> < 100 pF                        |

| TS <sub>X</sub> disable delay                                       | t <sub>SOFF</sub> | 50     |     | 210                                   | ns   | $C_L = 0$                                      |

| SIG <sub>R</sub> update time                                        | tsigr             | 0      |     | 2                                     | μS   |                                                |

| Timing Parameters in Variable                                       | e Data Rate Mode  | 8      |     | · · · · · · · · · · · · · · · · · · · |      |                                                |

| D <sub>X</sub> active delay                                         | t <sub>DON</sub>  | 0      |     | 65                                    | ns   | C <sub>L</sub> < 100 pF                        |

| D <sub>X</sub> inactive delay                                       | t <sub>DOFF</sub> | 0      |     | 90                                    | ns   | C <sub>L</sub> < 100 pF                        |

| Data delay                                                          | t <sub>DFSX</sub> | 0      |     | 140                                   | ns   |                                                |

| Data delay                                                          | t <sub>DDX</sub>  | 0      |     | 100                                   | ns   | C <sub>1</sub> < 100 pF                        |

#### **Timing Waveforms**

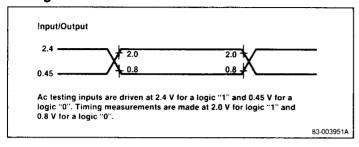

#### **Timing Measurement Points**

#### Transmit Timing, Fixed Data Rate Mode

## **Timing Waveforms (cont)**

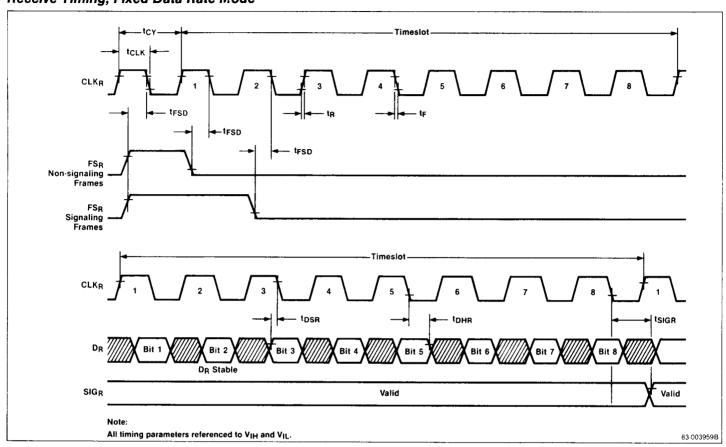

#### Receive Timing, Fixed Data Rate Mode

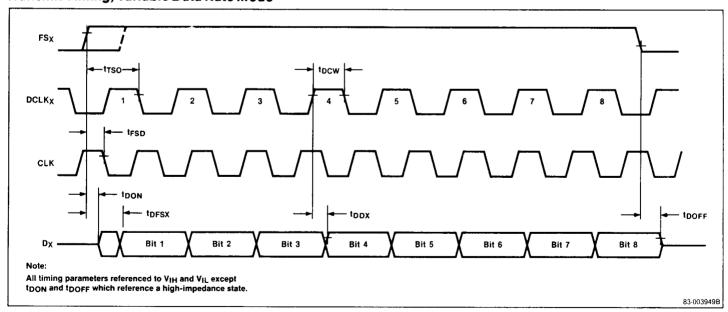

#### Transmit Timing, Variable Data Rate Mode

## **Timing Waveforms (cont)**

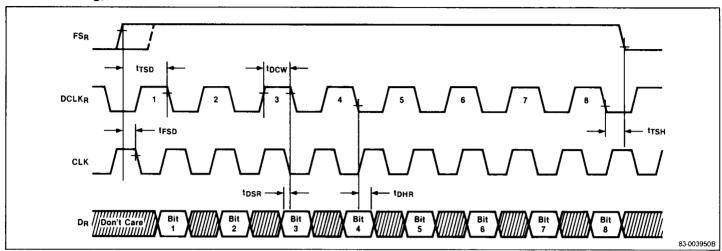

#### Receive Timing, Variable Data Rate Mode

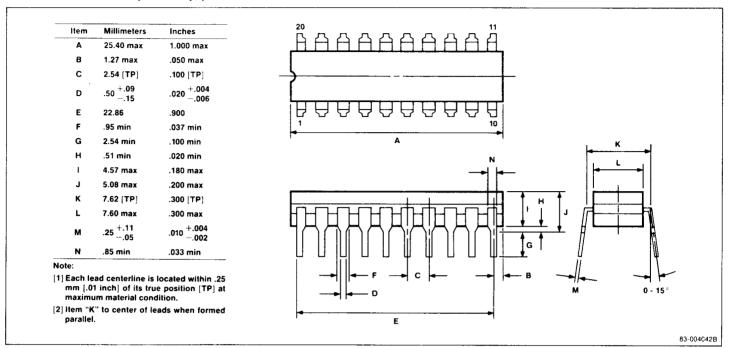

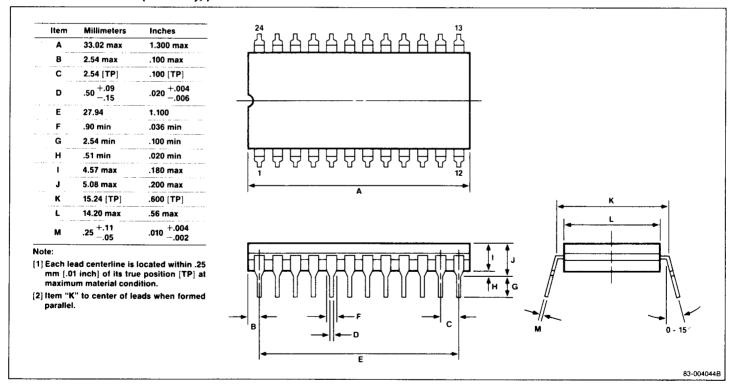

#### **Packaging Information (cont)**

#### 20-Pin Ceramic DIP (300-mil), µPD9513AD

#### 24-Pin Ceramic DIP (600-mil), µPD9514AD

401 Ellis Street P.O. Box 7241 Mountain View, CA 94039 TEL 415-960-6000 TWX 910-379-6985

@1987 NEC Electronics Inc./Printed in U.S.A.

For Literature Call Toll Free: 1-800-632-3531

1-800-632-3532 (In California)

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update on to keep surrent the minformation contained in this document.

008681 ZXB

NECEL-000354 STOCK NO. 220200