**√RoHS**

## Dual Output DC-DC & Linear Regulator IC

The 34710 is a dual-output power regulator IC integrating switching regulator, linear regulator, supervisory and power supply sequencing circuitry. With a wide operating input voltage range of 13 V to 32 V, the 34710 is applicable to many commercial and industrial applications using embedded MCUs.

A mode-selected 5.0 Vor 3.3 V DC-DC switching regulator is provided for board-level I/O and user circuitry up to 700 mA. A linear regulator provides mode-selected core supply voltages of either 3.3V, 2.5V, 1.8V, or 1.5V at currents up to 500 mA.

The supervisor circuitry ensures that the regulator outputs follow a predetermined power-up and power-down sequence.

#### Features

- · Efficient 5.0 V/3.3 V Buck Regulator

- Low Noise LDO Regulator (mode-selected 3.3V, 2.5V,1.8V, or 1.5V)

- · On-Chip Thermal Shutdown Circuitry

- Supervisory Functions (Power-ON Reset and Error Reset Circuitry)

- Sequenced I/O and Core Voltages

- · Pb-Free Packaging Designated by Suffix Code EW

## DUAL OUTPUT DC-DC & LINEAR REGULATOR

| ORDERING INFORMATION                               |               |             |  |

|----------------------------------------------------|---------------|-------------|--|

| Device Temperature Range (T <sub>A</sub> ) Package |               |             |  |

| *PC33710EW/R2                                      | -40°C to 105° | 32 SOICW-EP |  |

| MC34710EW/R2                                       | 0°C to 85°C   | 32 SOICW-EP |  |

\*Device in development.

Electrical parameters being defined.

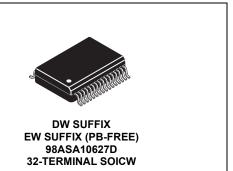

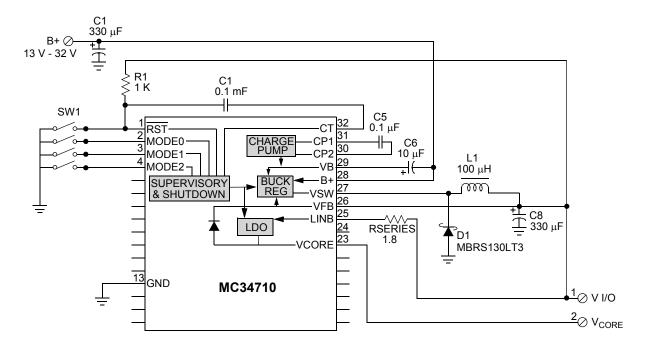

Figure 1. 34710 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

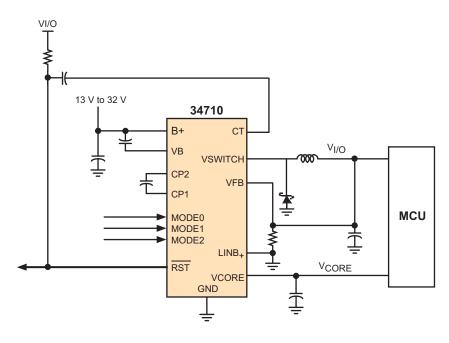

### INTERNAL BLOCK DIAGRAM

Figure 2. 34710 Simplified Internal Block Diagram

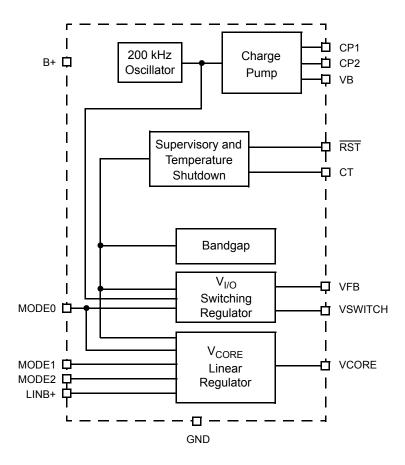

### **TERMINAL CONNECTIONS**

Figure 3. 34710 Terminal Connections

**Table 1. 34710 Terminal Definitions**

| Terminal<br>Number | Terminal<br>Name        | Terminal<br>Function | Formal Name                                              | Definition                                                                                                   |

|--------------------|-------------------------|----------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 1                  | RST                     | Reset                | Reset                                                    | Reset is an open drain output only.                                                                          |

| 2<br>3<br>4        | Mode0<br>Mode1<br>Mode2 | Input                | Mode Control                                             | These input terminals control $V_{\mbox{\scriptsize FB}}$ and $V_{\mbox{\scriptsize CORE}}$ output voltages. |

| 5–12,<br>14–22, 24 | NC                      | NC                   | No Connects                                              | No internal connection to this terminal.                                                                     |

| 13                 | GND                     | Ground               | Ground                                                   | Ground.                                                                                                      |

| 23                 | VCORE                   | Output               | Core Voltage<br>Regulator Output                         | Core regulator output voltage.                                                                               |

| 25                 | LINB+                   | Input                | Core Voltage<br>Regulator Input                          | Core regulator input voltage.                                                                                |

| 26                 | VFB                     | Input                | V <sub>I/O</sub> Switching<br>Regulator<br>Feedback      | Feedback terminal for $V_{\text{I/O}}$ switching regulator and internal logic supply.                        |

| 27                 | VSWITCH                 | Output               | V <sub>I/O</sub> Switching<br>Regulator Switch<br>Output | V <sub>I/O</sub> switching regulator switching output.                                                       |

| 28                 | B+                      | Input                | Power Supply<br>Input                                    | Regulator input voltage.                                                                                     |

| 29                 | VB                      | Output               | Boost Voltage                                            | Boost voltage storage node.                                                                                  |

| 30                 | CP2                     | Passive<br>Component | CP Capacitor<br>Positive                                 | Charge pump capacitor connection 2.                                                                          |

| 31                 | CP1                     | Passive<br>Component | CP Capacitor<br>Negative                                 | Charge pump capacitor connection 1.                                                                          |

| 32                 | СТ                      | Passive<br>Component | Reset Delay<br>Capacitor                                 | Reset delay adjustment capacitor.                                                                            |

#### **MAXIMUM RATINGS**

#### **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                              | Symbol                     | Max        | Unit     |

|---------------------------------------------------------------------|----------------------------|------------|----------|

| ELECTRICAL RATINGS                                                  |                            |            |          |

| Input Power Supply Voltage                                          | V <sub>B+</sub>            |            | V        |

| I <sub>B+</sub> = 0.0 A                                             |                            | -0.3 to 36 |          |

| Terminal Soldering Temperature (1)                                  | T <sub>SOLDER</sub>        | 260        | °C       |

| Power Dissipation (2)                                               | P <sub>D</sub>             | 3.0        | W        |

| ESD Standoff Voltage                                                |                            |            | V        |

| Non-Operating, Unbiased, Human Body Model (3)                       | V <sub>ESD1</sub>          | ±2000      |          |

| Thermal Resistance                                                  |                            |            | °C/W     |

| Junction-to-Ambient (4)                                             | $R_{\theta JA}$            | 45         |          |

| Junction-to-Ambient (2)                                             | $R_{\theta JA}$            | 25         |          |

| Junction-to-Exposed-Pad                                             | $R_{	heta JC}$             | 2.0        |          |

| THERMAL RATINGS                                                     |                            |            | •        |

| Operating Ambient Temperature                                       | T <sub>A</sub>             | 0 to 85    | °C       |

| Operating Junction Temperature                                      | T <sub>J</sub>             | 0 to 105   | °C       |

| Input Power Supply Voltage                                          | V <sub>B+</sub>            |            | V        |

| I <sub>B+</sub> = 0.0 A to 3.0 A                                    |                            | 13 to 32   |          |

| Quiescent Bias Current from B+ (5)                                  | I <sub>B+</sub> (Q)        |            | mA       |

| V <sub>B+</sub> = 13 V to 32 V                                      |                            | 7.5        |          |

| V <sub>I/O</sub> SWITCHING REGULATOR <sup>(6)</sup>                 |                            |            | <u> </u> |

| Maximum Output Voltage Startup Overshoot ( $C_{OUT}$ = 330 $\mu$ F) | V <sub>I/O</sub> (STARTUP) |            | V        |

| Mode0 = 0                                                           |                            | 5.4        |          |

| Mode0 = Open                                                        |                            | 3.6        |          |

| Maximum Output Current                                              | I <sub>VI/O</sub>          |            | mA       |

| $T_A = 0$ °C to 105°C                                               |                            | 700        |          |

#### Notes

- 1. Soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 2. With 2.0 in<sup>2</sup> of copper heatsink.

- 3. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ).

- 4. With no additional heatsinking.

- 5. Maximum quiescent power dissipation is 0.25 W.

- 6. 13 V  $\leq$  V  $_{B+} \leq$  32 V and -20°C  $\leq$  T  $_{J} \leq$  145°C unless otherwise noted.

#### **MAXIMUM RATINGS (continued)**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                                                                                                                                                                                         | Symbol                      | Max                       | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|------|

| V <sub>CORE</sub> LINEAR REGULATOR <sup>(7)</sup>                                                                                                                                                                                              |                             |                           |      |

| Maximum Output Voltage Startup Overshoot (C <sub>OUT</sub> = 10 μF) <sup>(8)</sup> Mode2=Low, Mode1=Low, Mode0=Low  Mode2=Open, Mode1=Low, Mode0=Don't Care  Mode2=Low, Mode1=Open, Mode0=Don't Care  Mode2=Open, Mode1=Open, Mode0=Don't Care | V <sub>CORE</sub> (STARTUP) | 3.6<br>2.7<br>2.0<br>1.65 | V    |

| Maximum Output Current $T_{J} = 0^{\circ}\text{C to } 105^{\circ}\text{C}, \ V_{\text{LINB+}} \leq V_{\text{CORE}}(\text{NOM}) + 0.8 \ \text{V}^{(9)}$                                                                                         | Ivcore                      | 500                       | mA   |

#### Notes

- 7. 13 V  $\leq$  V  $_{B+} \leq$  32 V and -20°C  $\leq$  T  $_{J} \leq$  145°C unless otherwise noted.

- 8. Refer to <u>Table 2</u>, page <u>9</u>.

- 9. Pulse testing with low duty cycle used.

### STATIC ELECTRICAL CHARACTERISTICS

#### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions 4.75 V  $\leq$  V $_{IO}$   $\leq$  5.25 V, 13 V  $\leq$  V $_{B+}$   $\leq$  32 V, and 0°C  $\leq$  T $_{J}$   $\leq$  105°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T $_{A}$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                          | Symbol                            | Min   | Тур  | Max   | Unit |

|-------------------------------------------------------------------------|-----------------------------------|-------|------|-------|------|

| SWITCHING REGULATOR (VI/O, MODE0)                                       | SWITCHING REGULATOR (VI/O, MODE0) |       |      |       |      |

| Logic Supply Voltage (I <sub>VI/O</sub> = 25 to 700 mA)                 | V <sub>I/O</sub>                  |       |      |       | V    |

| Mode0 = 0                                                               |                                   | 4.8   | 5.0  | 5.2   |      |

| Mode0 = Open (floating)                                                 |                                   | 3.15  | 3.25 | 3.45  |      |

| Output On Resistance                                                    | R <sub>DS(ON)</sub>               |       |      |       | Ω    |

| V <sub>B+</sub> = 13 V to 32 V                                          |                                   | 0.5   | 1.0  | 2.0   |      |

| Soft Start Threshold Voltage                                            | V <sub>I/O</sub> (SOFT)           |       |      |       | V    |

| Mode0 = any                                                             |                                   | _     | 2.5  | 3.1   |      |

| Current Limit Threshold (T <sub>J</sub> = 25°C to 100°C)                |                                   |       |      |       | Α    |

| Normal Operation                                                        | I <sub>LIMIT</sub> (OP)           | 1.9   | 2.4  | 2.9   |      |

| Soft Start, $V_{I/O} \le 2.5 \text{ V}$                                 | I <sub>LIMIT</sub> (SOFT)         | 1.0   | _    | 1.9   |      |

| Minimum Voltage Allowable on V <sub>SWITCH</sub> Terminal               | V <sub>VSWITCH</sub> (MIN)        |       |      |       | V    |

| T <sub>J</sub> = 25°C to 100°C                                          |                                   | -0.5  | _    | -     |      |

| LINEAR REGULATOR (VCORE, MODE 1, 2, 3, 4)                               |                                   |       | 1    |       |      |

| Supply Voltage (I <sub>VCORE</sub> = 5.0 mA) <sup>(10)</sup>            | V <sub>CORE</sub> (NOM)           |       |      |       | V    |

| Mode2=Low, Mode1=Don't Care, Mode0=Low                                  |                                   | 3.15  | 3.3  | 3.45  |      |

| Mode2=Low, Mode1=Don't Care, Mode0=Open                                 |                                   | 2.45  | 2.5  | 2.75  |      |

| Mode2=Open, Mode1=Don't Care, Mode0=Low                                 |                                   | 1.7   | 1.8  | 2.05  |      |

| Mode2=Open, Mode1=Don't Care, Mode0=Open                                |                                   | 1.425 | 1.5  | 1.575 |      |

| Supply Voltage (I <sub>VCORF</sub> = 500 mA) <sup>(10)</sup>            | V <sub>CORE</sub> (NOM)           |       |      |       | V    |

| Mode2=Low, Mode1=Don't Care, Mode0=Low                                  |                                   | 3.0   | _    | 3.4   |      |

| Mode2=Low, Mode1=Don't Care, Mode0=Open                                 |                                   | 2.2   | _    | 2.6   |      |

| Mode2=Open, Mode1=Don't Care, Mode0=Low                                 |                                   | 1.55  | _    | 1.9   |      |

| Mode2=Open, Mode1=Don't Care, Mode0=Open                                |                                   | 1.33  | -    | 1.53  |      |

| V <sub>CORE</sub> Dropout Voltage                                       | I <sub>VCORE</sub> (DROPOUT)      |       |      |       | V    |

| V <sub>CORE</sub> = V <sub>CORE</sub> (NOM), I <sub>VCORE</sub> = 0.5 A |                                   | -     | 0.5  | 0.8   |      |

| Normal Current Limit Threshold                                          | I <sub>LIMIT</sub>                |       |      |       | mA   |

| $T_J$ = 25°C to 100°C, $V_{LINB+}$ = $V_{CORE}$ (NOM) + 1.0 V           |                                   | 600   | 800  | 1000  |      |

#### Notes

10. Refer to Table 2, page 9.

### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 4.75 V  $\leq$  V $_{IO}$   $\leq$  5.25 V, 13 V  $\leq$  V $_{B+}$   $\leq$  32 V, and 0°C  $\leq$  T $_{J}$   $\leq$  105°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T $_{A}$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                             | Symbol                                   | Min                                      | Тур                                     | Max                                      | Unit |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------|-----------------------------------------|------------------------------------------|------|

| MODE TERMINALS OPERATING VOLTAGES                                                                                          |                                          |                                          |                                         |                                          |      |

| Mode Control Terminals Low Voltage                                                                                         | V <sub>IL</sub> (Mode <sub>n</sub> )     | _                                        | _                                       | 0.825                                    | V    |

| Mode Control Terminals High Voltage                                                                                        | V <sub>IH</sub> (Mode <sub>n</sub> )     | 2.6                                      | _                                       | _                                        | ٧    |

| Mode Control Terminals Voltage with Input Floating $V_{B+} = 13 \text{ V}$ to 14 V                                         | V <sub>Mode</sub> (FLOAT)                | 7.0                                      | 8.0                                     | 13                                       | V    |

| SUPERVISOR CIRCUITRY (RST, VCORE)                                                                                          |                                          |                                          |                                         | 1                                        |      |

| Minimum Function V <sub>B+</sub> for Charge Pump and Oscillator Running                                                    | V <sub>B+</sub> (MIN)                    | _                                        | _                                       | 9.0                                      | V    |

| Minimum V <sub>B+</sub> for $\overline{\text{RST}}$ Assertion, V <sub>B+</sub> Rising                                      | V <sub>B+</sub> (ASSERT)                 | _                                        | 1.9                                     | 2.2                                      | V    |

| $\overline{RST}$ Low Voltage $V_{B+}$ = 2.0 V, $I_{\overline{RST}} \le 5.0$ mA                                             | V <sub>OL</sub>                          | _                                        | 0.25                                    | 0.4                                      | ٧    |

|                                                                                                                            | V <sub>I/OT+</sub><br>V <sub>I/OT-</sub> | –<br>V <sub>I/O</sub> (NOM)<br>- 300 mV  | -                                       | V <sub>I/O</sub> (NOM)<br>- 50 mV<br>-   | V    |

| RST Hysteresis for V <sub>I/O</sub>                                                                                        | V <sub>HYSVI/O</sub>                     | 10                                       | _                                       | 100                                      | mV   |

| RST V <sub>CORE</sub> Threshold  V <sub>CORE</sub> Rising  V <sub>CORE</sub> Falling                                       | V <sub>CORET+</sub>                      | -<br>V <sub>CORE</sub> (NOM)<br>- 300 mV | -                                       | V <sub>CORE</sub> (NOM)<br>- 30 mV       | V    |

| RST Hysteresis for V <sub>CORE</sub> V <sub>B+</sub> = 13 V to 32 V                                                        | V <sub>HYS</sub> CORE                    | 10                                       | 50                                      | 100                                      | mV   |

| $V_{CORE}$ - $V_{I/O}$ for $V_{CORE}$ Shutdown<br>$V_{B+}$ = 13 V to 32 V                                                  | V <sub>CORE</sub> (SHUTDOWN)             | 0.5                                      | -                                       | 0.9                                      | V    |

| Thermal Shutdown Temperature T <sub>J</sub> Rising                                                                         | T <sub>J</sub> (TSD)                     | -                                        | _                                       | 170                                      | °C   |

| Overtemperature Hysteresis                                                                                                 | T <sub>J</sub> (HYSTERESIS)              | -                                        | 20                                      | _                                        | °C   |

| VB CHARGE PUMP                                                                                                             |                                          |                                          |                                         | •                                        |      |

| Boost Voltage (11)<br>$V_{B+} = 12 \text{ V}, I_{Vb} = 0.5 \text{ mA}$<br>$V_{B+} = 32 \text{ V}, I_{Vb} = 0.5 \text{ mA}$ | V <sub>B</sub>                           | V <sub>B+</sub> 8<br>V <sub>B+</sub> 10  | V <sub>B+</sub> 9<br>V <sub>B+</sub> 12 | V <sub>B+</sub> 10<br>V <sub>B+</sub> 14 | V    |

Notes

11. Bulk capacitor ESR ≤ 10 milliohms

### DYNAMIC ELECTRICAL CHARACTERISTICS

#### **DYNAMIC ELECTRICAL CHARACTERISTICS**

Characteristics noted under conditions 4.75 V  $\leq$  V $_{IO}$   $\leq$  5.25 V, 13 V  $\leq$  V $_{B+}$   $\leq$  32 V, and 0°C  $\leq$  T $_{J}$   $\leq$  105°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T $_{A}$  = 25°C under nominal conditions unless otherwise noted

| Characteristic                                                           | Symbol                          | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------|---------------------------------|-----|-----|-----|------|

| V <sub>I/O</sub> SWITCHING REGULATOR                                     |                                 |     |     |     | 1    |

| Duty Cycle                                                               | D                               | 45  | 49  | 55  | %    |

| Switching Rise and Fall Time                                             | t <sub>R</sub> , t <sub>F</sub> |     |     |     | ns   |

| Load Resistance = 100 $\Omega$ , V <sub>B+</sub> = 30 V                  |                                 | 20  | 35  | 50  |      |

| SUPERVISOR CIRCUITRY (RST)                                               | <u> </u>                        |     |     |     |      |

| RST Delay                                                                | t <sub>DELAY</sub>              |     |     |     | ms   |

| $C_{delay} = 0.1 \mu F$                                                  |                                 | 40  | 60  | 80  |      |

| RST Filter Time                                                          | t <sub>FILTER</sub>             |     |     |     | μS   |

| $V_{B+} = 9.0 \text{ V}$                                                 |                                 | 2.0 | 4.0 | 8.0 |      |

| RST Fall Time                                                            | t <sub>F</sub>                  |     |     |     | ns   |

| $C_L$ = 100 pF, $R_{PULLUP}$ = 4.7 k $\Omega$ , 90% to 10%               |                                 | _   | 25  | 75  |      |

| C Delay                                                                  |                                 |     |     |     |      |

| Charge Current                                                           | I <sub>CDLY</sub>               | 2.0 | 3.5 | 5.0 | μА   |

| Threshold Voltage                                                        | V <sub>THCD</sub>               | 1.7 | 2.0 | 2.2 | V    |

| NTERNAL OSCILLATOR                                                       | <u> </u>                        |     |     |     |      |

| Charge Pump and V <sub>I/O</sub> Switching Regulator Operating Frequency | f <sub>OP</sub>                 |     |     |     | kHz  |

| $V_{B+} = 12 \text{ V to } 32 \text{ V}$                                 |                                 | 140 | 170 | 260 |      |

#### **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

#### V<sub>I/O</sub> Switching Regulator

The  $V_{I/O}$  switching regulator output voltage is determined by the Mode digital input terminals. The 34710's Mode terminals select the output voltage. For example, if Mode2, Mode1, and Mode0 are set to 0, 0, 0 (respectively) then  $V_{I/O}$  will be set to 5.0 V; if Mode2, Mode1, and Mode0 are all left floating (i.e., Open, Open, and Open), then the voltage for  $V_{I/O}$  will be set to 3.3 V. Table 2 provides the truth table for setting the various combination of regulator outputs via the Mode pins.

The topology of the regulator is a hysteretic buck regulator operating from the internal ~200 kHz oscillator.

#### V<sub>CORE</sub> Linear Regulator

The V<sub>CORE</sub> linear LDO (low drop-out) regulator can produce either a +3.3 V, 2.5 V, 1.8 V, or 1.5 V output voltage at currents up to 500 mA. The input to the VCORE regulator is a terminal that may be connected to the V $_{\rm I/O}$  regulator output or to an external power supply. Note, the minimum input voltage level must be equal to or greater than the

selected  $V_{CORE}$  voltage + 0.8 V. (I.e., 0.8V is the LDO regulator drop out voltage.)

The Mode terminals select the output voltage as depicted in  $\underline{\mathsf{Table}\ 2}.$

Table 2. V<sub>I/O</sub> and V<sub>CORE</sub> Regulator

Output Voltage Selection

| Mode2 | Mode1 | Mode0 | V <sub>I/O</sub> (V) | V <sub>CORE</sub> (V) |

|-------|-------|-------|----------------------|-----------------------|

| 0     | 0     | 0     | 5.0                  | 3.3                   |

| 0     | 0     | Open  | 3.3                  | 2.5                   |

| 0     | Open  | 0     | 5.0                  | 1.8                   |

| 0     | Open  | Open  | 3.3                  | 1.8                   |

| Open  | 0     | 0     | 5.0                  | 2.5                   |

| Open  | 0     | Open  | 3.3                  | 2.5                   |

| Open  | Open  | 0     | 5.0                  | 1.5                   |

| Open  | Open  | Open  | 3.3                  | 1.5                   |

Open indicates terminal is not connected externally (i.e. floating).

#### **FUNCTIONAL TERMINAL DESCRIPTION**

#### Power Supply Input (B+)

Main supply voltage for the  $V_{I/O}$  Switching Regulator and general chip bias circuitry.

#### Core Voltage Regulator Input (Lin B+)

Supply voltage for the  $V_{CORE}$  Regulator. May be provided by the  $V_{I/O}$  regulator output or from an independent supply.

#### Mode Control (MODE 0,1,2)

Mode select terminals to select the  $V_{\text{I/O}}$  and  $V_{\text{CORE}}$  output voltages per table 2. Pull to ground for low state, float for high state.

#### Switching Capacitors 1 and 2 (CP1/CP2)

Terminals for the Charge Pump capacitor.

#### **Boost Voltage (VB)**

The Boost Voltage is an output terminal used for the charge pump boost voltage and is a connection point for the Charge Pump bulk capacitor.It provides a gate drive for the  $V_{\text{I/O}}$  Switch FET.

#### Reset (RST)

Reset is an output terminal for supervisory functions. This terminal is in high state during normal operation and low state

during fault conditions. This terminal has no input function and requires an external pull-up resistor.

The  $\overline{RST}$  terminal is an open drain output driver to prevent oscillations during the transition. It is recommended to connect a 0.1 uF capacitor between the CT pin and  $\overline{RST}$  pin. Note: error conditions must be present for a minimum time,  $t_{FILTER}$ , before the 34710 responds to them. Once all error conditions have been cleared,  $\overline{RST}$  is held low for an additional time of  $t_{DELAY}$ .

#### Reset Delay Capacitor (CT)

This terminal is the external delay. It is used with a capacitor to ground to delay RST turn-on time and to RST to prevent RST oscillations during chip power-on.

#### VI/O Switching Regulator Feedback (VFB)

This terminal is the feedback input for the  $V_{\text{I/O}}$  Switching Regulator and the output of the regulator application.

#### VI/O Switching Regulator output (VSWITCH)

This terminal is the Switching output for the  $V_{\text{I/O}}$  Buck Regulator. It has internal high side FET.

34710

#### SUPERVISORY FUNCTIONS

#### **Supervisory Circuitry**

The supervisory circuitry provides control of the  $\overline{RST}$  line, an open drain signal, based on system operating conditions monitored by the 34710.  $V_{I/O}$ ,  $V_{CORE}$ ,  $V_{B+}$ , and thermal shutdown (TSD) detectors in various parts of the chip are monitored for error conditions.  $V_{I/O}$ ,  $V_{CORE}$ ,  $V_{B+}$ , and thermal shutdown have both positive- and negative-going thresholds for triggering the reset function.

The supervisor circuitry also ensures that the regulator outputs follow a predetermined power-up and power-down sequence. Specifically, the sequencing ensures that  $V_{\text{I/O}}$  is never less than 0.9 V below  $V_{\text{CORE}}.$  This means that  $V_{\text{CORE}}$  -  $V_{\text{I/O}}$  will be clamped at 0.5 V, and that the  $V_{\text{CORE}}$  regulator

operation will be suppressed during startup and shutdown to ensure that  $V_{CORE}$  -  $V_{I/O}$  = 0.9 V.

#### **VB Charge Pump**

The high-side MOSFET in the switching regulator (buck converter) requires a gate drive supply voltage that is biased higher than the B+ voltage, and this boosted voltage is provided by the internal charge pump and stored in a capacitor between the VB pin and the B+ pin. The charge pump operates directly from the B+ supply, and uses an internal oscillator operating at 200 kHz.

#### **Internal Oscillator**

The internal oscillator provides a 200 kHz square wave signal for charge pump operation and for the buck converter.

#### TYPICAL APPLICATIONS

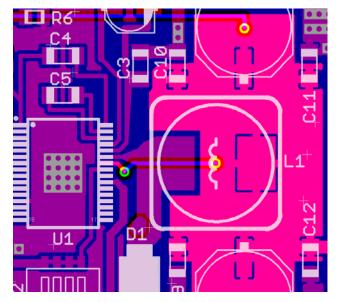

Figure 4. Typical Application Diagram

The MC34710 provides both a buck converter and an LDO regulator in one IC. Figure 4 above shows a typical application schematic for the MC34710. L1 is the buck converter's inductor. The buck inductor is a key component and must not only present the required reactance, but do so at a dc resistance of less than 20 milliohms in order to preserve the converter's efficiency. Also important to the converter's efficiency is the utilization of a low Vf Schottky diode for D1.

Note that a 0.1uF capacitor is connected between CT and the reset pins; this prevents any possibility of oscillations occurring on the reset line during transitions by allowing the CT terminal to discharge to ground potential via the RST pin, and then charge when RST returns to a logic high. The capacitor between the CP1 and CP2 pins is the charge pump's "bucket capacitor", and sequentially charges and discharges to pump up the reservoir capacitor connected to the VB pin. Note that the reservoir capacitor's cathode is connected to B+ rather than ground. Also note that the charge pump is intended only to provide gate-drive potential for the buck regulator's internal power MOSFET, and therefore connecting external loads to the VB pin is not recommended.

The IC's internal V<sub>CORE</sub> LDO regulator can provide up to 500 mA of current as long as the operating junction

temperature is maintained below 105 degrees C. The heatgenerating power dissipation of the LDO is primarily a function of the Volt x Amp product across the LINB+ and VCORE terminals. Therefore, if the LINB+ voltage is >> than the selected V<sub>CORE</sub> voltage + 0.8 V, it is recommended to use a power resistor in series with the LINB+ input to drop the voltage and dissipate the heat externally from the IC. For example, if the output of the buck regulator (V I/O on the schematic) is used as the input to LINB+, and the mode switches are set such that V I/O = 5 V and  $V_{CORF}$  = 3.3 V, then a series resistance of 1.8 ohms at the LINB+ pin would provide an external voltage drop at 500 mA while still leaving the minimum required headroom of 0.8 V. Conversely, if the mode switches are set such that V I/O = 3.3 V and  $V_{CORF}$  = 2.5 V, then no series resistance would be required, even at the maximum output current of 500 mA.

Designing a power supply circuit with the MC34710, like all dc-dc converter ICs, requires special attention not only to component selection, but also to component placement (i.e., printed circuit board layout). The MC34710 has a nominal switching frequency of 200 kHz, and therefore pcb traces between the buck converter discrete component terminals and the IC should be kept as short and wide as possible to keep the parasitic inductance low. Likewise, keeping these

pcb traces short and wide helps prevent the converter's high di/dt switching transients from causing EMI/RFI.

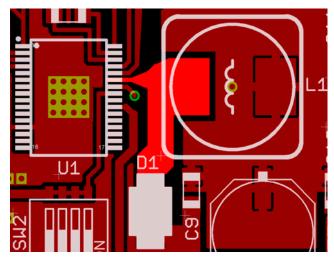

Figure 5. Typical PCB Layout

<u>Figure 5</u> shows a typical layout for the pcb traces connecting the IC's switching terminal (VSWITCH) and the power inductor, rectifier, and filter components.

Also, it is recommended to design the component layout so that the switching currents can be immediately sunk into a broad full-plane ground that provides terminations physically right at the corresponding component leads. This helps prevent switching noise from propagating into other sections of the circuitry.

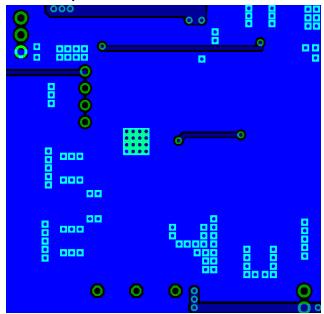

Figure 6. Bottom Copper Layout

<u>Figure 6</u> illustrates a pcb typical bottom copper layout for the area underneath a buck converter populated on the top of the same section of pcb.

The ground plane is highlighted so the reader may note how the ground plane has been kept as broad and wide as

possible. The square vias in the plane are located to provide an immediate path to ground from the top copper circuitry.

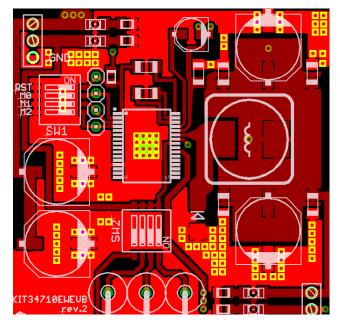

Figure 7. Top Copper Layout

Figure 7 shows the corresponding top copper circuit area with the component placement.

Again, the ground plane and the vias have been highlighted so the reader may note the proximity of these current sink pathways to the key converter components. It is also important to keep the power planes of the switching converter's output spread as broad as possible beneath the passive components, as this helps reduce EMI/RFI and the potential for coupling noise transients into adjacent circuitry.

Figure 8. Output Plane of Buck Converter

<u>Figure 8</u> shows the output plane of the buck converter highlighted.

This layout provides the lowest possible impedance as well as lowest possible dc resistance for the power routing. Note that the power path and its return should be placed, if possible, on top of each other on different layers or opposite sides of the pcb.

Small ceramic capacitors are placed in parallel with the Aluminum electrolytics so that the overall bulk filtering presents a low ESL to the high di/dt switching currents. Alternatively, special low ESL/ESR switching-grade electrolytics may be used.

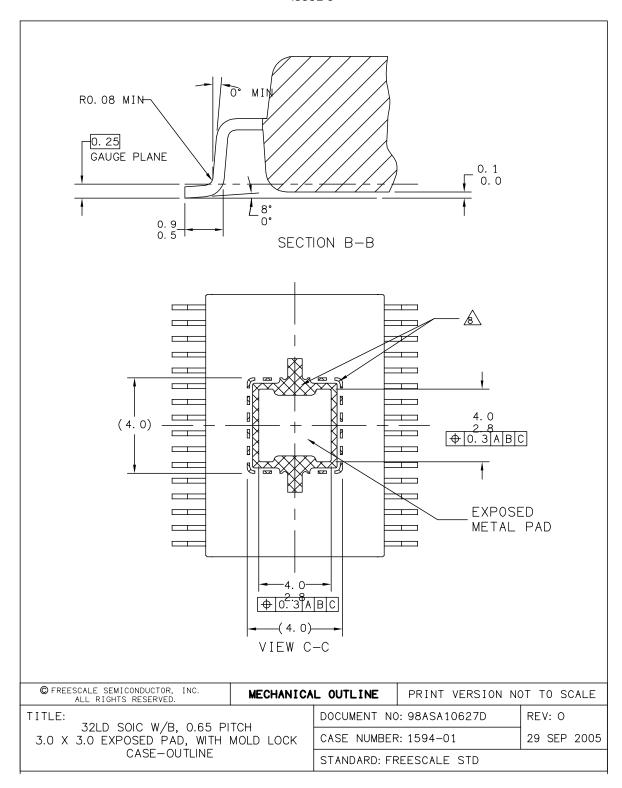

An additional feature of the MC34710 is the 32 SOICW-EP exposed pad package. The package allows heat to be conducted from the die down through the exposed metal pad underneath the package and into the copper of the pcb. In order to best take advantage of this feature, a grid array of thru-hole vias should be placed in the area corresponding to the exposed pad, and these vias then should then connect to a large ground plane of copper to dissipate the heat into the ambient environment. An example of these vias can be seen in the previous figures of a typical pcb layout.

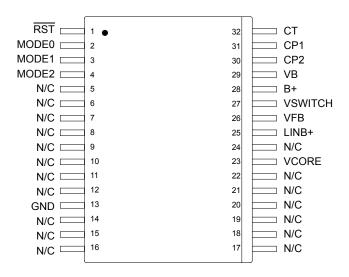

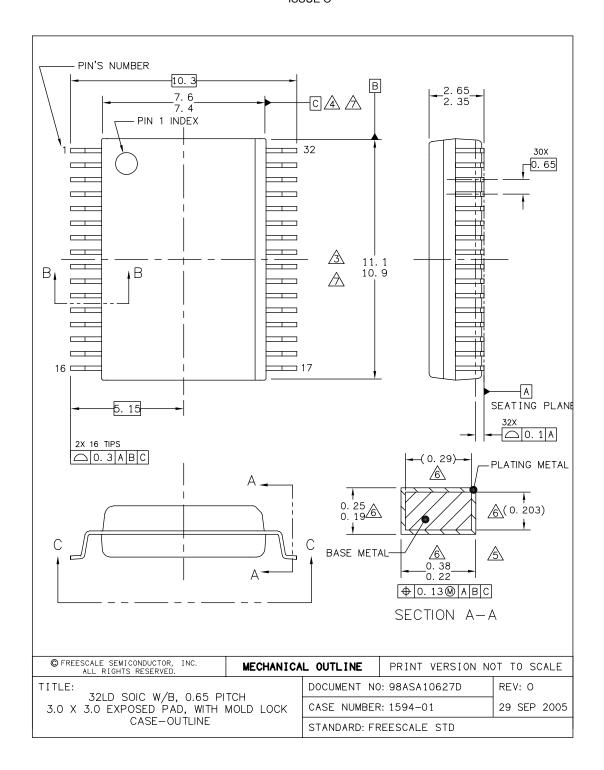

#### **PACKAGING**

#### **PACKAGE DIMENSIONS**

EW (Pb-FREE) SUFFIX

32-LEAD SOICW-EXPOSED PAD

PLASTIC PACKAGE

98ASA10627D

ISSUE O

# EW (Pb-FREE) SUFFIX 32-LEAD SOICW-EXPOSED PAD PLASTIC PACKAGE 98ASA10627D ISSUE O

## **REVISION HISTORY**

| REVISION | DATE   | DESCRIPTION OF CHANGES                                                                                                                                                                                                                                 |

|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0      | 3/2006 | <ul> <li>Converted to Freescale format</li> <li>Updated Maximum Ratings, Static and Dynamic Characteristics tables.</li> <li>Updated packaging drawing</li> <li>Changed terminal VI/O_OUT to VFB</li> <li>Implemented Revision History page</li> </ul> |

| 3.0      | 3/2006 | <ul> <li>Updated format from Preliminary to Advance Information.</li> <li>Format and style corrections to match standard template.</li> </ul>                                                                                                          |

#### How to Reach Us:

#### **Home Page:**

www.freescale.com

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

**Europe, Middle East, and Africa:** Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http:// www.freescale.com/enn

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application. Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2006, All rights reserved.