Order this document by EB381/D

**EB381**

# Migrating from the MC68HC811E2 to the MC68HC11F1

By Timothy J. Airaudi Applications Engineering Motorola Embedded Control Division Austin, Texas

## Introduction

This engineering bulletin explains how existing users of the MC68HC811E2 could migrate to the MC68HC11F1. The last date that the MC68HC811E2 can be ordered from Motorola is June 30, 2001. However, beyond that date, parts may be available from Motorola distributors.

The MC68HC811E2 is a versatile part used in many different types of applications. This document addresses applications that use the part in expanded mode only.

Customers using single-chip mode should see *Migrating from the MC68HC811E2 to the MC68HC711E9*, Motorola document order number EB380/D.

#### Engineering Bulletin

#### Migrating to the MC68HC11F1

For current MC68HC811E2 users with external memory systems (expanded mode operation), the MC68HC11F1 is a possible replacement part (see **Table 1**). The MC68HC11F1 can address 64 Kbytes of external memory in expanded mode and requires less glue logic than the MC68HC811E2.

Other advantages of migrating to the MC68HC11F1 are:

- More RAM

- More expanded mode input/output (I/O)

- Non-multiplexed address/data bus

- 3-volt operation

- Ability to run at higher speeds

For complete information on the MC68HC811E2, see the *M68HC11E Family Technical Data*, Motorola document order number M68HC11E/D. For information on the MC68HC11F1, see the *MC68HC11F1 Technical Data*, Motorola document order number MC68H11CF1/D. Both can be found at http://motorola.com/semiconductor (the Motorola World Wide Web site).

Major Differences

The major differences between these two parts are:

- Package options

- Memory map (memory, registers, etc.)

- EEPROM block protect

- CONFIG register

- External glue logic requirements

Engineering Bulletin Migrating to the MC68HC11F1

| Device                         | MC68HC811E2                                                       | MC68HC811F1                                                                                                               |

|--------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| RAM (Bytes)                    | 256                                                               | 1 K                                                                                                                       |

| EE (Bytes)                     | 2048                                                              | 512                                                                                                                       |

| Timer                          | 16-bit, 3-4 IC, 4-5 OC,<br>RTI, pulse accumulator                 | 16-bit, 3-4 IC, 4-5 OC,<br>RTI, pulse accumulator                                                                         |

| Input/Output (i/O)<br>Expanded | 22                                                                | 30                                                                                                                        |

| Serial                         | SCI<br>SPI                                                        | SCI<br>SPI                                                                                                                |

| Analog-to-Digital (A/D)        | 8-CH, 8-bit                                                       | 8-CH, 8-bit                                                                                                               |

| Operating Voltage (V)          | 5.0                                                               | 3.0<br>5.0                                                                                                                |

| Maximum Bus<br>Frequency (MHz) | 2                                                                 | 3<br>5                                                                                                                    |

| Temperature                    | C, V, M                                                           | C, V, M                                                                                                                   |

| Package Options                | 52 PLCC (FN);<br>48 DIP (P)                                       | 68 PLCC (FN);<br>80 LQFP (FU)                                                                                             |

| Comments                       | Secure device available,<br>MC68SEC811E2;<br>EEPROM block protect | 64-K external address<br>bus, 4-program chip<br>select, non-mux<br>address/data bus, 3-V,<br>3-MHz version<br>(MC68L11F1) |

| Document Order<br>Number       | MC68HC11E/D MC68HC811F1/                                          |                                                                                                                           |

#### **Table 1. Comparison Chart**

Difference: Package Options

The MC68HC811E2 is available in 52-pin PLCC (plastic leaded chip carrier) and 48-pin DIP (dual in-line pack) packages. The MC68HC11F1 is available in 68-pin PLCC and 80-pin LQFP (low-profile quad flat pack) packages.

#### <u>Case 1</u>

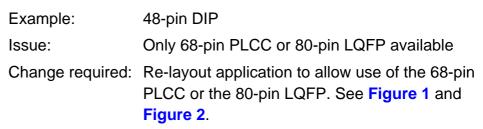

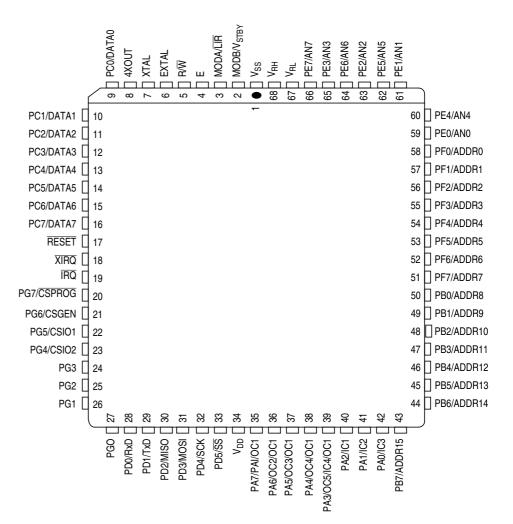

| Example:         | 52-pin PLCC                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Issue:           | Only 68-pin PLCC or 80-pin LQFP available                                                                           |

| Change required: | Re-layout application to allow use of the 68-pin PLCC or the 80-pin LQFP. See <b>Figure 1</b> and <b>Figure 2</b> . |

EB381

#### **Engineering Bulletin**

#### Case 2

Figure 1. Pin Assignments for MC68HC11F1 68-Pin PLCC

Engineering Bulletin Migrating to the MC68HC11F1

Figure 2. Pin Assignments for MC68HC11F1 80-Pin QFP

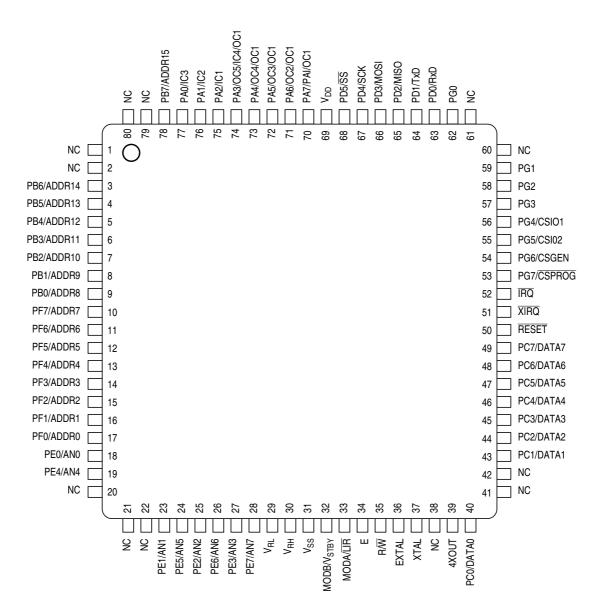

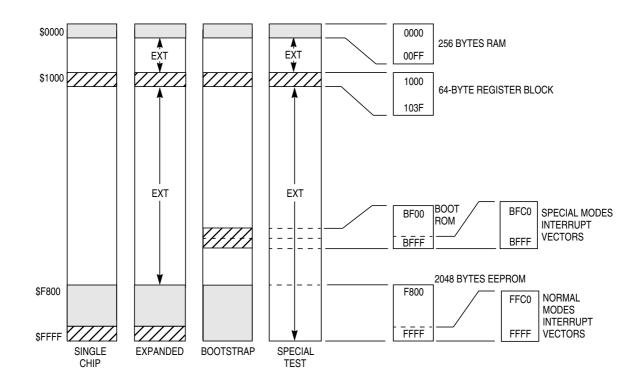

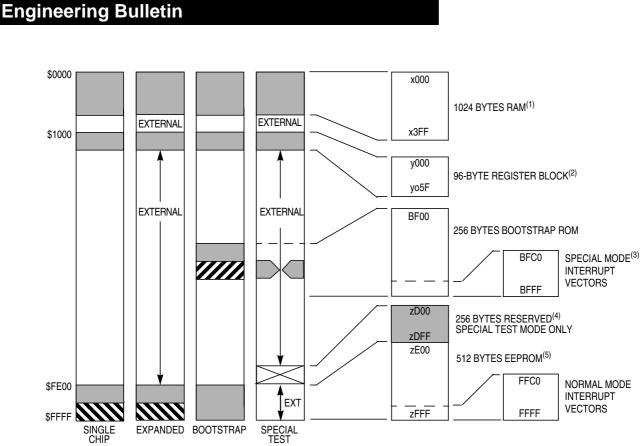

Difference:The MC68HC811E2 has the same memory mapped locations for the<br/>normal mode interrupt vectors. The RAM, EEPROM, external<br/>addressing, and registers for these devices are different. See Figure 3<br/>and Figure 4.

## **Engineering Bulletin**

| Case 1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example:         | RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Issue:           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Change required: | None. However, you may want to take advantage<br>of the extra 768 bytes of RAM. This block of RAM<br>is also relocatable on 4-K boundaries in the<br>64-Kbyte address space by writing an appropriate<br>value into bits 4–7 in the INIT register.                                                                                                                                                                                                         |

| <u>Case 2</u>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example:         | EPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Issue:           | The MC68HC11F1 has less EEPROM (512 bytes vs. 2048 bytes), and it is located at a different starting address (\$FE00 vs. \$F800).                                                                                                                                                                                                                                                                                                                          |

| Change required: | Change code to use new EEPROM block located from \$FE00 to \$FFDF.                                                                                                                                                                                                                                                                                                                                                                                         |

| Case 3           |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example:         | External address range                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Issue:           | External address range is different.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Change required: | Change the external address range from \$1040-\$F7FF to \$1060-\$FDFF.                                                                                                                                                                                                                                                                                                                                                                                     |

| Case 4           |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Example:         | Register block                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Issue:           | Register block is a different size and some register addresses have different meanings.                                                                                                                                                                                                                                                                                                                                                                    |

| Change required: | The register block on the MC68HC11F1 is<br>96 bytes instead of 64-bytes and is located at a<br>default location of \$1000–\$105F. This block of<br>RAM is also re-locatable on 4-K boundaries in the<br>64-Kbyte address space by writing to bits 0–3 in<br>the INIT register. These register addresses also<br>have different meanings: \$1001, \$1002, \$1003,<br>\$1005, \$1006, \$1036, \$1038, and \$103E.<br>\$105C–\$105F are additional registers. |

Engineering Bulletin Migrating to the MC68HC11F1

Figure 3. Memory Map for MC68HC811E2

Notes:

- 1. RAM can be remapped to any 4-byte boundary (\$x000). "x" represents the value contained in RAM [3:0] in the INIT register.

- 2. The register block can be remapped to any 4-byte boundary (\$y000). "y" represents the value contained in REG[3:0] in the INIT register.

- 3. Special test mode vectors are externally addressed.

- 4. In special test mode the address locations \$zD00-\$zDFF are not externally addressable. "z" represents the value of bits EE[3:0] in the CONFIG register.

- EEPROM can be remapped to any 4-byte boundary (\$z000). "z" represents the value contained in EE[3:0] in the CONFIG register.

#### Figure 4. MC68HC11F1 Memory Map

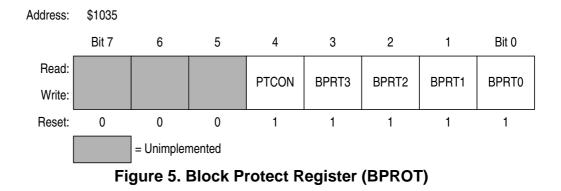

| Difference:<br>EEPROM Block<br>Protect | Since these two parts differ significantly regarding EEPROM size and location, the address range and block size that can be protected is different. See <b>Figure 5</b> , <b>Table 2</b> , and <b>Table 3</b> . |                                                         |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|

|                                        | Case 1                                                                                                                                                                                                          |                                                         |  |  |

|                                        | Example:                                                                                                                                                                                                        | EEPROM block protect                                    |  |  |

|                                        | Issue:                                                                                                                                                                                                          | EEPROM block protect addresses and sizes are different. |  |  |

|                                        |                                                                                                                                                                                                                 |                                                         |  |  |

Change required: The BPRT bits in the BPROT register (\$1035) must be changed to protect the address ranges and block sizes the user desires.

Engineering Bulletin Migrating to the MC68HC11F1

#### Table 2. EEPROM Block Protect in MC68HC811E2 MCUs

| Bit Name | Block Protected | Block Size |

|----------|-----------------|------------|

| BPRT0    | \$xB00-\$x9FF   | 512 bytes  |

| BPRT1    | \$xA00–\$xBFF   | 512 bytes  |

| BPRT2    | \$xC00–\$xDFF   | 512 bytes  |

| BPRT3    | \$xE00-\$xFFF   | 512 bytes  |

Table 3. EEPROM Block Protection in MC68HC11F1 MCUs

| Bit Name | Block Protected | Block Size |

|----------|-----------------|------------|

| BPRT0    | \$xE00-\$xE1F   | 32 bytes   |

| BPRT1    | \$xE20-\$xE5F   | 64 bytes   |

| BPRT2    | \$xE60-\$xEDF   | 128 bytes  |

| BPRT3    | \$xEE0-\$xFFF   | 288 bytes  |

### **Engineering Bulletin**

Difference:The operation of the CONFIG register on the MC68HC811E2 differsCONFIG Registerfrom the MC68HC11F1. See Figure 6, Figure 7, Table 4, and Table 5.

<u>Case 1</u>

| Example:         | CONFIG register                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Issue:           | Some of the bits in the CONFIG register have different meaning.                                                                                                                             |

| Change required: | The bits in the CONFIG register (\$103F) must be<br>changed to meet the user's requirements. Bit 3<br>(NOSEC) is not used and bits 4–7 (EEPROM<br>mapping) define different address ranges. |

| Address:           | \$103F |            |        |     |       |       |   |       |

|--------------------|--------|------------|--------|-----|-------|-------|---|-------|

|                    | Bit 7  | 6          | 5      | 4   | 3     | 2     | 1 | Bit 0 |

| Read:<br>Write:    | EE3    | EE2        | EE1    | EE0 | NOSEC | NOCOP |   | EEON  |

| Single-chip reset: | 1      | 1          | 1      | 1   | U     | U     | 1 | 1     |

| Bootstrap:         | 1      | 1          | 1      | 1   | U     | U(L)  | 1 | 1     |

| Expanded:          | U      | U          | U      | U   | 1     | U     | 1 | U     |

| Test:              | U      | U          | U      | U   | 1     | U(L)  | 1 | 0     |

|                    |        | = Unimplen | nented |     |       |       |   |       |

U indicates a previously programmed bit. U(L) indicates that the bit resets to the logic level held in the latch prior to reset, but the function of COP is controlled by the DISR bit in TEST1 register.

#### Figure 6. MC68HC811E2 System Configuration Register (CONFIG)

| EE[3:0] | EEPROM Location | EE[3:0] | EEPROM Location |

|---------|-----------------|---------|-----------------|

| 0000    | \$0800-\$0FFF   | 1000    | \$8800-\$8FFF   |

| 0001    | \$1800-\$1FFF   | 1001    | \$9800-\$9FFF   |

| 0010    | \$2800-\$2FFF   | 1010    | \$A800\$AFFF    |

| 0011    | \$3800-\$3FFF   | 1011    | \$B800-\$BFFF   |

| 0100    | \$4800-\$4FFF   | 1100    | \$C800-\$CFFF   |

| 0101    | \$5800-\$5FFF   | 1101    | \$D800\$DFFF    |

| 0110    | \$6800-\$6FFF   | 1110    | \$E800\$EFFF    |

| 0111    | \$7800-\$7FFF   | 1111    | \$F800-\$FFFF   |

|         |                 |         |                 |

#### Table 4. MC68HC811E2 EEPROM Mapping

EB381

Engineering Bulletin Migrating to the MC68HC11F1

| Address:        | \$103F |            |        |     |   |       |   |       |

|-----------------|--------|------------|--------|-----|---|-------|---|-------|

|                 | Bit 7  | 6          | 5      | 4   | 3 | 2     | 1 | Bit 0 |

| Read:<br>Write: | EE3    | EE2        | EE1    | EE0 |   | NOCOP |   | EEON  |

| Reset states:   |        |            |        |     |   |       |   |       |

| Single chip     | 1      | 1          | 1      | 1   | 1 | Р     | 1 | 1     |

| Expanded        | 1      | 1          | 1      | 1   | 1 | P(L)  | 1 | 1     |

| Bootstrap       | Р      | Р          | Р      | Р   | 1 | Р     | 1 | Р     |

| Special test    | Р      | Р          | Р      | Р   | 1 | P(L)  | 1 | 0     |

|                 |        | = Unimpler | nented |     |   |       |   |       |

P = Previously programmed bit

P(L) = P(L) indicates that the bit resets to the logic level held in the latch prior to reset, but the function of COP is controlled by DISR bit in TEST1 register.

#### Figure 7. M68HC11F1 System Configuration Register (CONFIG)

| EE[3:0] | EEPROM Position |

|---------|-----------------|

| 0000    | \$0E00-\$0FFF   |

| 0001    | \$1E00\$1FFF    |

| 0010    | \$2E00-\$2FFF   |

| 0011    | \$3E00-\$3FFF   |

| 0100    | \$4E00-\$4FFF   |

| 0101    | \$5E00-\$5FFF   |

| 0110    | \$6E00-\$6FFF   |

| 0111    | \$7E00-\$7FFF   |

#### Table 5. EEPROM Mapping

| EE[3:0] | EEPROM Position |

|---------|-----------------|

| 1000    | \$8E00-\$8FFF   |

| 1001    | \$9E00\$9FFF    |

| 1010    | \$AE00-\$AFFF   |

| 1011    | \$BE00-\$BFFF   |

| 1100    | \$CE00-\$CFFF   |

| 1101    | \$DE00-\$DFFF   |

| 1110    | \$EE00-\$EFFF   |

| 1111    | \$FE00-\$FFFF   |

## **Engineering Bulletin**

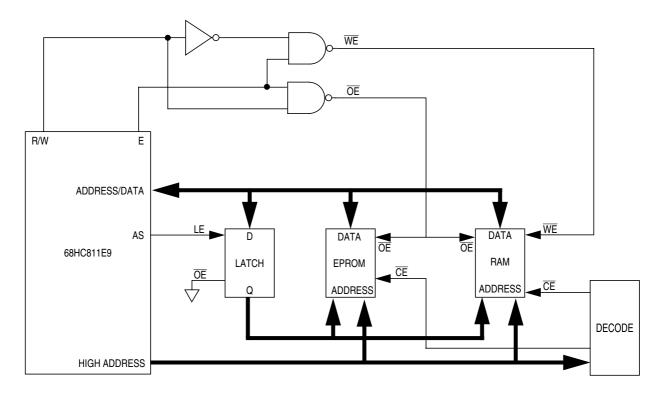

| Difference:<br>External Glue Logic<br>Requirements | <u>Case 1</u><br>Example:<br>Issue: | External glue logic<br>Some of the external glue logic requirements are<br>different.                                                                                                                                   |

|----------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

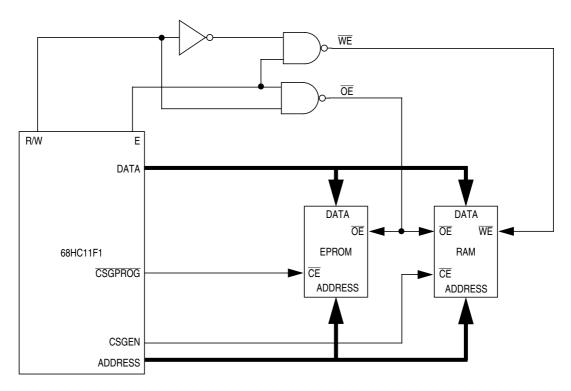

|                                                    | Change required:                    | The MC68HC11F1 has a non-multiplexed address/data bus and four programmable chip selects. This will eliminate the need for such external devices as a demultiplexer, a decoder, and a latch. See Figure 8 and Figure 9. |

EB381

Engineering Bulletin Migrating to the MC68HC11F1

#### Figure 9. MC68HC11F1 Non-Multiplexed Bus Example

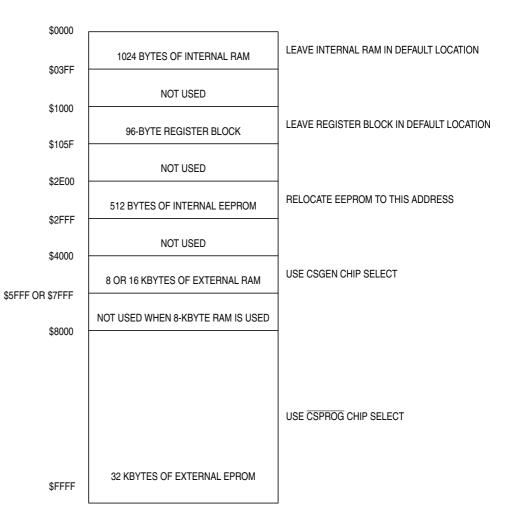

Memory Map Example This example is for connecting an 8- or 16-Kbyte external RAM and a 32-Kbyte external EPROM. See **Figure 10**.

- Leave internal RAM at default location (\$0000-\$03FF).

- Leave register block at default location (\$1000-\$105F).

- Relocate internal EEPROM to address \$2E00-\$2FFF. This is done by programming the EE0-EE3 bits in the CONFIG register (\$103F) to %0010. You may also need to program the EEON bit to ensure that the EEPROM is present in the memory map (see Figure 7).

- CSPROG comes up enabled in expanded mode. You will need to program the PSIZA and PSIZB bits in the CSCTL register (\$105D) to set an address range. In this example, PSIZA = 0 and PSIZB = 1 (\$8000–\$FFFF). The user may also want to clear the PSTHA and PSTHB bits in the CSSTRH register (\$105C) to ensure no clock stretch is used. Another option with CSPROG is the priority regarding CSGEN. This can be programmed using the GCSPR bit in the CSCTL register.

#### **Engineering Bulletin**

- For the CSGEN chip select, the G1SZA–G1SZC bits in the CSGSIZ register (\$105F) must be programmed to %011 for an 8-Kbyte RAM or to %010 for a 16-Kbyte RAM.

- Next, the starting address for this address must be programmed. This is done by programming bits GA13 and GA15 for the 8-Kbyte RAM or bits GA14 and GA15 for the 16-Kbyte RAM. Like the CSPROG, clear the GSTHA and GSTHB bits to disable the clock stretch.

- The user should also set the GNPOL bit (bit 4) in the CSGSIZ register to a 0 to make sure chip select CSGEN is an active low. Normally, the chip select for an external RAM device is made active with respect to the E clock going high. In this example, the CSGEN chip select needs to be made active during the address valid time. This is done by setting the GAVLD bit (bit 3) in the CSGSIZ register to a 1.

- The user should also check the other options available in the CSGSIZ register.

Freescale Semiconductor, Inc.

Engineering Bulletin Summary

Figure 10. MC68HC11F1 Expanded Mode Memory Map Example

## Summary

For those users using the MC68HC811E2 with external memory systems, the MC68HC11F1 is one possible migration path. Customers may also want to look at migrating to the MC68HC711E9 (see *Migrating from the MC68HC811E2 to the MC68HC711E9*, Motorola document order number EB380/D), or to the MC68HC812A4.

#### **Engineering Bulletin**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (is presented trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1-303-675-2140 or 1-800-441-2447

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu, Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852-26668334

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors/

© Motorola, Inc., 2001

For More Information On This Product, Go to: www.freescale.com