Issue 3

PMC-980616

5 Gbit/s ATM Switch Fabric Element

# **PM73488**

# **QSE**

# 5 Gbit/s ATM Switch Fabric Element

# **DATASHEET**

Released Issue 3: June 1999

Issue 3

PMC-980616

5 Gbit/s ATM Switch Fabric Element

AAL1gator, AAL1gator2, Evil Twin Switching, QRT, QSE, and SATURN are trademarks of PMC-Sierra, Inc.

AMCC is a registered trademark of Applied MicroCircuits Corporation.

i960 is a registered trademark of Intel Corporation.

National Semiconductor is a registered trademark of National Semiconductor Corporation.

Vitesse is a trademark of Vitesse Semiconductor Corporation.

All other brand or product names are trademarks of their respective companies or organizations.

U.S. Patents 5,557,607, 5,570,348, and 5,583,861

Copyright © 1999 PMC-Sierra, Inc. All Rights Reserved I

PMC-980616 Issue 3

## 5 Gbit/s ATM Switch Fabric Element

## **Public Revision History**

| Issue Number | Issue Date   | Details of Change                                                                     |

|--------------|--------------|---------------------------------------------------------------------------------------|

| Issue 1      | March 1998   | Creation of Document                                                                  |

| Issue 2      | October 1998 | Fixed all known typos/errors (e.g. wrong pinout: RAM_ADD(16) and RAM_PARITY swapped). |

| Issue 3      | June 1999    | Production Release Version                                                            |

PMC-980616

Issue 3

5 Gbit/s ATM Switch Fabric Element

# **Table of Contents**

|   |      | cription                                                |    |

|---|------|---------------------------------------------------------|----|

|   |      | tures                                                   |    |

|   |      | Switching Algorithm                                     |    |

|   |      | Multicast Support                                       |    |

|   |      | Diagnostic/Robustness Features                          |    |

|   |      | I/O Features                                            |    |

| 1 |      | the QSE Fits into Your System                           |    |

| 1 | 1.1  | QSE System Overview                                     |    |

|   | 1.2  | 32 x 32 Switch Application (5 Gbps)                     |    |

|   | 1.3  | 64 x 64 Switch Application (10 Gbps)                    |    |

|   | 1.4  | 5 Gbps to 20 Gbps Application Example - Seamless Growth |    |

|   | 1.5  | 5 Gbps to 160 Gbps Application Example – LAN-to-WAN.    |    |

| 2 |      | ory of Operation                                        |    |

| _ | 2.1  | Phase Aligners                                          |    |

|   |      | Data Drivers                                            |    |

|   | 2.2  | Unicast Routing and Distribution                        |    |

|   |      | Multicast Cell Flow                                     |    |

|   | 2.4  |                                                         |    |

|   |      | 2.4.1 Multicast Queue Engine                            |    |

|   |      | 2.4.2 Multicast Dequeue Engine                          |    |

|   | 2.5  | Arbiter                                                 |    |

|   | 2.6  | BP_ACK Drivers                                          |    |

|   | 2.7  | Interdevice Interconnectability                         |    |

|   | 2.8  | Network Topologies and the Speedup Factor (SF)          |    |

|   |      | 2.8.1 Network Philosophy                                |    |

|   |      | 2.8.2 Network Definition                                |    |

|   |      | 2.8.3 Speedup Factor (SF)                               |    |

| 3 | Exte | rnal Port Descriptions                                  |    |

|   | 3.1  | Switch Fabric Port and Interface Description            |    |

|   |      | 3.1.1 SE_SOC Encodings                                  | 39 |

|   |      | 3.1.2 Data Cell Format                                  | 40 |

|   |      | 3.1.3 BP_ACK Encodings                                  |    |

|   | 3.2  | Data Acknowledge                                        | 43 |

|   | 3.3  | Microprocessor Interface                                | 44 |

|   | 3.4  | Multicast SRAM Interface                                | 44 |

|   | 3.5  | Clocks and Timing Signals                               | 44 |

|   | 3.6  | CTRL_IN                                                 | 44 |

|   | 3.7  | STAT_OUT                                                | 45 |

|   | 3.8  | Fabric Switch-Over                                      | 45 |

| PMC-980616 Issue 3 5 Gbit/s ATM Switch Fabric Elem |

|----------------------------------------------------|

|----------------------------------------------------|

|   |                                                                 | 1.0 |

|---|-----------------------------------------------------------------|-----|

|   | 3.9 Cell Timing/Latency                                         |     |

| 4 | QSE Feature Descriptions                                        |     |

|   | 4.1 Distribution Algorithm                                      |     |

|   | 4.2 Cell Start Offset Logic                                     |     |

|   | 4.2.1 Relation Between External CELL_START and Local CELL_START |     |

|   | 4.2.2 Relation Between Local CELL_START and Data Out of the QSE |     |

|   | 4.3 General Description of Phase Aligners                       |     |

|   | 4.4 Multicast Backpressure Control                              |     |

|   | 4.5 Multilevel Reset                                            |     |

| 5 | Fault Specification                                             |     |

|   | 5. 1 Purpose                                                    |     |

|   | 5. 2 Basic Data and BP/ACK Flow                                 |     |

|   | 5. 3 Fault Detection Mechanisms                                 |     |

|   | 5.4 Interface Behavior.                                         |     |

|   | 5.5 IRT-to-Switch Fabric Interface                              | 53  |

|   | 5. 6 QSE Interface, Receive Data Direction                      |     |

|   | 5. 7 QSE Interface, Transmit Data Direction.                    |     |

|   | 5. 8 Switch Fabric-to-ORT Interface                             |     |

|   | 5. 9 Types of Failures and Their Manifestation                  |     |

| 6 | Signal Descriptions                                             | 58  |

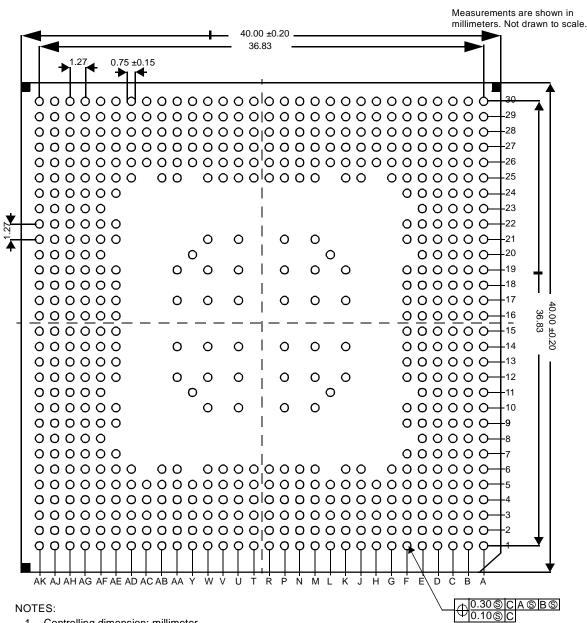

|   | 6.1 Package Diagram                                             | 58  |

|   | 6.2 Signal Locations (Signal Name to Ball)                      | 60  |

|   | 6.3 Signal Locations (Ball to Signal Name)                      | 65  |

|   | 6.4 Pin Descriptions                                            | 70  |

|   | 6.4.1 Processor Interface Signals                               | 72  |

|   | 6.4.2 Multicast RAM Interface Signals                           | 72  |

|   | 6.4.3 QSE Interface Signals                                     | 74  |

|   | 6.4.4 Boundary Scan Signals                                     | 79  |

|   | 6.4.5 Miscellaneous Signals                                     | 81  |

|   | 6.4.6 Total Pin Count                                           | 83  |

| 7 | Physical Characteristics                                        | 84  |

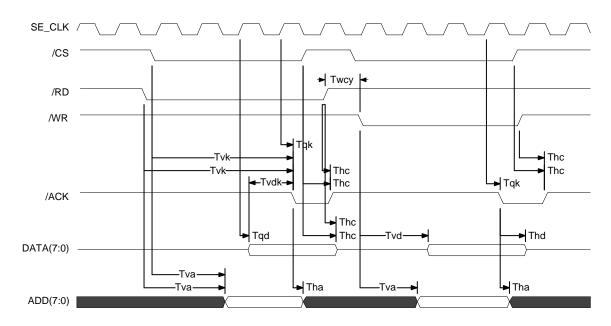

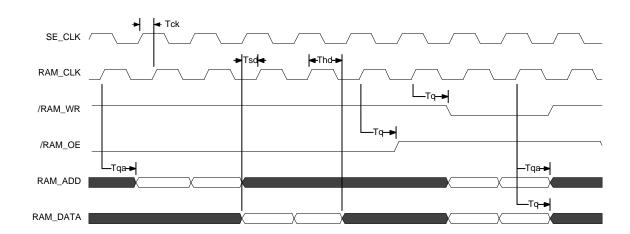

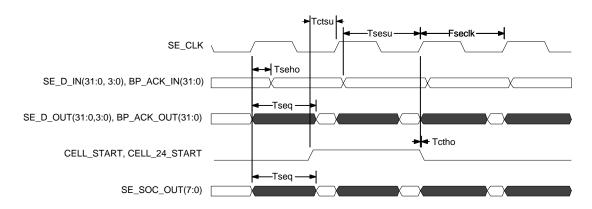

| 8 | Timing Diagrams                                                 | 86  |

|   | 8.1 Microprocessor Timing                                       | 86  |

|   | 8.2 RAM Timing                                                  | 87  |

|   | 8.3 QSE Interface Timing                                        | 88  |

|   | 8.4 Miscellaneous Timing                                        | 89  |

| 9 | Microprocessor Ports                                            | 92  |

|   | 9.1 Microprocessor Ports Summary                                | 92  |

|   | 9.2 Note on Error Detection and Reporting                       | 94  |

|   | 9.3 Microprocessor Ports Bit Definitions                        | 94  |

|   | 9.3.1 REVISION                                                  | 95  |

|   | 9.3.2 CHIP_MODE                                                 | 95  |

|   |                                                                 |     |

| PMC-980616 Issue 3 5 Gbit/s ATM Switch Fabric Elem |

|----------------------------------------------------|

|----------------------------------------------------|

|    | 9.3.3     | MULTICAST_GROUP_INDEX_REGISTER             | 96  |

|----|-----------|--------------------------------------------|-----|

|    | 9.3.4     | MULTICAST_GROUP_VECTOR_REGISTER            | 96  |

|    | 9.3.5     | MULTICAST_GROUP_OP                         | 97  |

|    | 9.3.6     | UC/MC_FAIRNESS_REGISTER                    | 97  |

|    | 9.3.7     | EXTENDED_CHIP_MODE                         | 97  |

|    | 9.3.8     | MULTICAST_GROUP_INDEX_MSB                  | 98  |

|    | 9.3.9     | INPUT_PORT_ENABLE                          | 98  |

|    | 9.3.10    | OUTPUT_PORT_ENABLE                         | 99  |

|    | 9.3.11    | INPUT_MARKED_CELLS_COUNT                   | 99  |

|    | 9.3.12    | OUTPUT_MARKED_CELLS_COUNT                  | 99  |

|    | 9.3.13    | PARITY_ERROR_PRESENT                       | 100 |

|    | 9.3.14    | PARITY_ERROR_LATCH                         | 100 |

|    | 9.3.15    | PARITY_ERROR_INT_MASK                      | 100 |

|    | 9.3.16    | SE_INPUT_PORT_FAIL_PRESENT                 | 101 |

|    | 9.3.17    | SE_INPUT_PORT_FAIL_LATCH                   | 102 |

|    | 9.3.18    | BP_ACK_FAIL_PRESENT                        | 102 |

|    | 9.3.19    | BP_ACK_FAIL_LATCH                          | 102 |

|    | 9.3.20    | BP_REMOTE_FAIL_PRESENT                     | 103 |

|    | 9.3.21    | BP_REMOTE_FAIL_LATCH                       | 103 |

|    | 9.3.22    | CONTROL_REGISTER                           | 103 |

|    | 9.3.23    | INTERRUPT_STATUS_REGISTER                  | 105 |

|    | 9.3.24    | MULTICAST_AGGREGATE_OUTPUT_AND_INPUT_MODES | 105 |

|    | 9.3.25    | UNICAST_AGGREGATE_OUTPUT_MODE              | 106 |

|    | 9.3.26    | SWITCH_FABRIC_ROW                          | 107 |

|    | 9.3.27    | SWITCH_FABRIC_COLUMN                       | 108 |

|    | 9.3.28    | CELL_START_OFFSET                          | 109 |

|    | 9.3.29    | BP_CONTROL_REGISTER                        | 109 |

|    | 9.3.30    | ACK_PAYLOAD                                | 109 |

|    | 9.3.31    | GANG_DEAD_ACK_PAYLOAD                      | 110 |

|    | 9.3.32    | EXTENDED_SWITCH_MODE                       | 110 |

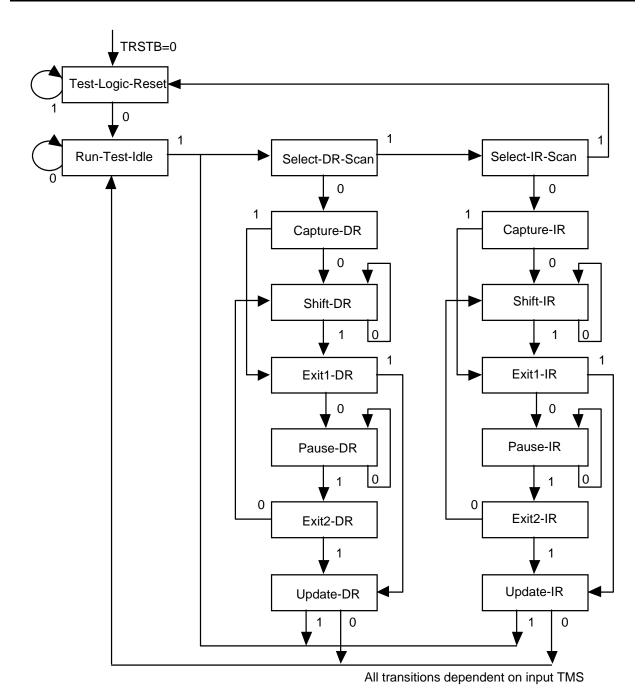

| 10 | JTAG      |                                            | 111 |

|    | 10.1 JTA  | G Support                                  | 111 |

|    | 10.2 TAP  | Controller                                 | 112 |

|    | 10.2.1    | Test-Logic-Reset:                          | 113 |

|    | 10.2.2    | Run-Test-Idle:                             | 114 |

|    | 10.2.3    | Capture-DR:                                | 114 |

|    | 10.2.4    | Shift-DR:                                  | 114 |

|    | 10.2.5    | Update-DR:                                 | 114 |

|    | 10.2.6    | Capture-IR:                                | 114 |

|    | 10.2.7    | Shift-IR:                                  | 114 |

|    | 10.2.8    | Update-IR:                                 | 114 |

|    | 10.3 Bour | ndary Scan Instructions                    | 114 |

|    |           |                                            |     |

| PMC-980616 | Issue 3              | 5 Gbit/s ATM Switch Fabric Element |

|------------|----------------------|------------------------------------|

|            |                      |                                    |

| 10.3.1     | BYPASS               |                                    |

| 10.3.2     | EXTEST               |                                    |

| 10.3.3     | SAMPLE               |                                    |

| 10.3.4     | IDCODE               |                                    |

| 10.3.5     | STCTEST              |                                    |

| 10.4 Bour  | ndary Scan Pin Order | 115                                |

PMC-980616

Issue 3

5 Gbit/s ATM Switch Fabric Element

# **List of Figures**

| Figure 1.  | QSE Interface Block Diagram                                             | 12 |

|------------|-------------------------------------------------------------------------|----|

| Figure 2.  | QSE System Overview                                                     | 13 |

| Figure 3.  | 32 x 32 Switch Application (5 Gbps)                                     | 14 |

| Figure 4.  | 64 x 64 Switch Application (10 Gbps)                                    | 14 |

| Figure 5.  | 5 Gbps ATM Switch Using 8 QRTs, and 1 QSE                               | 15 |

| Figure 6.  | 10 Gbps ATM Switch Using 16 QRTs, and 2 QSEs                            | 15 |

| Figure 7.  | 20 Gbps ATM Switch Using 32 QRTs, and 4 QSEs                            | 16 |

| Figure 8.  | 5 Gbps to 160 Gbps Switches Modeled Using Only Two Cards                | 17 |

| Figure 9.  | 5 Gbps ATM Switch                                                       | 18 |

| Figure 10. | 10 Gbps ATM Switch                                                      | 19 |

| Figure 11. | 15 Gbps ATM Switch                                                      | 20 |

| Figure 12. | 20 Gbps ATM Switch                                                      | 21 |

| Figure 13. | Basic QSE Flow                                                          | 22 |

| Figure 14. | Routing Bits Rotation for Unicast Traffic, Gang Mode of Four            | 24 |

| Figure 15. | Example of Multicast Cell Handling in the QSE                           | 27 |

| Figure 16. | Ideal Distributed Network                                               | 29 |

| Figure 17. | More Realistic Distributed Network                                      | 29 |

| Figure 18. | "Large" Distributed Network (Will not Work Well with Banyan Alone)      | 30 |

| Figure 19. | High-Level QRT/QSE System                                               | 30 |

| Figure 20. | (3) x 1 - 5 Gbps System                                                 | 31 |

| Figure 21. | (5) x 4 - 20 Gbps System                                                | 31 |

| Figure 22. | (1,3) x 1 - 10 Gbps System                                              | 32 |

| Figure 23. | Randomizer (with Evil Twin Switching Algorithm)                         | 33 |

| Figure 24. | Network Needs to be Run Faster than the Line Rate                       | 33 |

| Figure 25. | Definition of the Speedup Factor                                        | 34 |

| Figure 26. | How to Use the SF to Select Favorable Networks                          | 34 |

| Figure 27. | SE_SOC Encodings                                                        | 36 |

| Figure 28. | Expanded SE_SOC Encodings                                               | 36 |

| Figure 29. | BP_ACK Encodings                                                        | 39 |

| Figure 30. | QSE Cell-Level Timing                                                   | 44 |

| Figure 31. | QSE Switch Latency                                                      | 45 |

| Figure 32. | Basic Forward and Backward Data Path                                    | 46 |

| Figure 33. |                                                                         |    |

|            | Path)                                                                   |    |

| Figure 34. | 596-Ball Enhanced Plastic BGA Physical Dimensions Diagram (Top view)    |    |

| Figure 35. | 596-Ball Enhanced Plastic BGA Physical Dimensions Diagram (Bottom view) | 56 |

| Figure 36. |                                                                         | 68 |

| Figure 37. | Microprocessor Timing                                                   | 83 |

| PMC-980616 | Issue 3                             | 5 Gbit/s ATM Switch Fabric Elemen |

|------------|-------------------------------------|-----------------------------------|

|            |                                     |                                   |

| Figure 38. | RAM Interface                       |                                   |

| Figure 39. | QSE Bit-Level Timing                | 85                                |

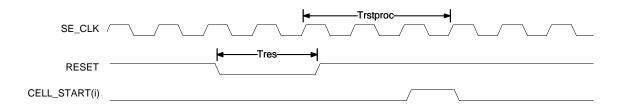

| Figure 40. | Reset Timing                        | 86                                |

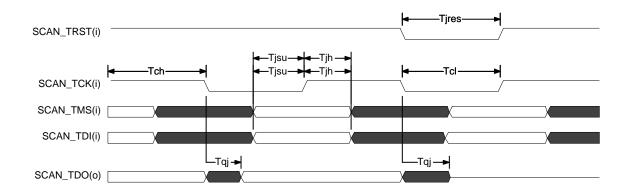

| Figure 41. | JTAG Timing                         | 87                                |

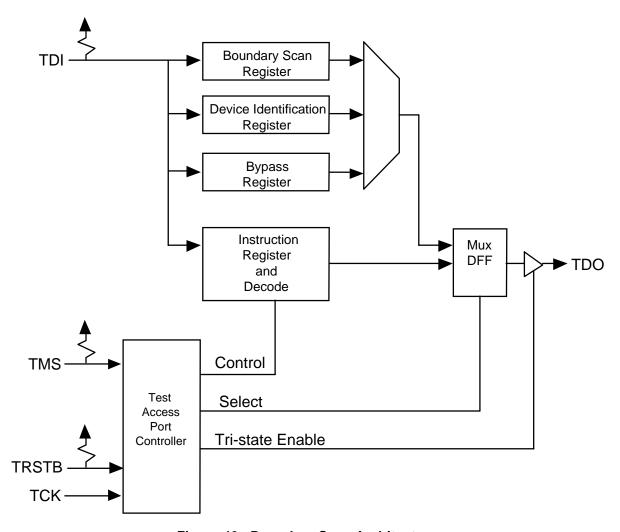

| Figure 42. | Boundary Scan Architecture          |                                   |

| Figure 43. | TAP Controller Finite State Machine | 110                               |

## PMC-980616

## Issue 3

5 Gbit/s ATM Switch Fabric Element

# **List of Tables**

| Table 1.  | BP_CONTROL_REGISTER; Threshold Control Bits for Each Set of 32 Buffers | 25  |

|-----------|------------------------------------------------------------------------|-----|

| Table 2.  | Speedup Factor (1-Stage Networks)                                      | 35  |

| Table 3.  | Speedup Factor (3-Stage Networks)                                      | 35  |

| Table 5.  | Regular Cell Format                                                    | 37  |

| Table 6.  | PM73488 Mode Idle Cell Format                                          | 38  |

| Table 7.  | Information Bit Encoding                                               | 40  |

| Table 8.  | Data Latencies                                                         | 43  |

| Table 9.  | Failure Conditions, IRT-to Switch Fabric Interface                     | 50  |

| Table 10. | Failure Conditions, QSE Receive Interface                              | 51  |

| Table 11. | Failure Conditions, QSE Transmit Interface                             | 52  |

| Table 12. | Failure Conditions, Switch Fabric-to-ORT Interface                     | 53  |

| Table 13. | Faults                                                                 | 53  |

| Table 14. | Signal Locations (Signal Name to Ball)                                 | 57  |

| Table 15. | Signal Locations (Ball to Signal Name)                                 | 62  |

| Table 16. | Processor Interface Signals (21 Signal Pins)                           | 69  |

| Table 17. | Multicast RAM Interface Signals (39 Signal Pins)                       | 69  |

| Table 18. | QSE Interface Signals (364 Signal Pins)                                | 71  |

| Table 19. | Boundary Scan Signals (8 Signal Pins)                                  | 76  |

| Table 20. | Miscellaneous Signals (8 Signal Pins)                                  | 78  |

| Table 21. | Pin Allocations                                                        | 80  |

| Table 22. | Absolute Maximum Ratings                                               | 81  |

| Table 23. | Recommended Operating Conditions                                       | 81  |

| Table 24. | DC Operating Conditions                                                | 81  |

| Table 25. | Capacitance                                                            | 82  |

| Table 26. | Estimated Package Thermal Characteristics                              | 82  |

| Table 27. | Microprocessor Timing                                                  | 83  |

| Table 28. | RAM Interface Timing                                                   | 84  |

| Table 29. | CTRL_IN, STAT_OUT, TEST_MODE and DEBUG Timing                          | 86  |

| Table 30. | Valid Window Timing                                                    | 87  |

| Table 31. | Microprocessor Ports Summary                                           | 89  |

| Table 32. | Boundary Scan Pin order                                                | 112 |

| Table 33. | Standard Abbreviations                                                 | 129 |

| Table 34. | Ordering Information                                                   | 132 |

ı

PMC-980616 Issue 3 5 Gbit/s ATM Switch Fabric Element

## **Product Overview**

## **DESCRIPTION**

The PM73488 (QSE) is an advanced communications device that enables the implementation of high performance switching systems. The QSE is a  $32 \times 32$  cell based switch element, with a total *sustainable bandwidth* of 5 Gb/s. (The *peak*, *or raw*, *bandwidth* is much more than that: about 8 Gb/s). The QSE is designed to be used with other QSE's as part of a larger switch fabric. Various QSE combinations allow fabrics with theoretical peak capacities ranging from 5 Gb/s (one QSE) to 160 Gb/s. The QSE is not ATM specific; however, should the QSE be used for switching ATM cells, the QSE cell size is large enough to allow efficient direct mapping between QSE Cells and ATM cells.

Multistage QSE Fabrics (Delta-Reverse Delta configuration) have rich connectivity with multiple paths between each source/destination pair. A QSE fabric performs cut-through unicast switching and uses Randomization and Evil-Twin algorithms to fully utilize these multiple paths and avoid the build up of internal hot spots. Randomization, in combination with multiple routing paths allows graceful degradation of QSE Fabric performance if internal links fail. To detect failed links, the QSE maintains and checks liveness patterns on input and output ports in hardware, and automatically routes around ports if they die.

QSE data ports are 6 bits wide including a 4-bit wide 66 MHz data path, a one-bit wide start-of-cell indication, and a one-bit wide acknowledgment signal. Each port contains "Phase Aligners" to recover the clock for that port, thus removing the need to synchronize all data to a single global clock.

When switching unicast traffic in a multistage fabric (one to three stages), the first nibble of the cell will come out of the last QSE stage before the last nibble of that cell enters the first stage. The cell thereby traverses the entire fabric in one cell time. If the cell sucessfully makes it to its destination, the ("egress") device accepting the cell from the last stage QSE has the opportunity to send a four bit "Ack Information Packet" back to source indicating what it did with this cell; at its simplest, the egress device can send back one pattern to indicate that the cell was accepted and another to indicate that the cell was dropped due to, say, buffer overflow.

It is also possible that the cell was dropped inside the QSE fabric due to say a collision with another cell. The QSE classifies lost cells as due to one of three causes (collision, all possible outputs dead, or parity errors) and will generate an "Ack Information Packet" back to the source to communicate this event. In each QSE, the 4 bit pattern in the information packet can be independently software configured for each of the three cases. Note that since each QSE can be separately programmed, the patterns can even be setup so that the source knows where the cell was dropped.

The information provided by the "Ack Information Packets" can be used by the device injecting cells into the first QSE stage to decide how to handle the cells; at its simplest, the device can resend cells that did not get through (a more sophisticated algorithm might also take into account where the cell was lost and the behavior of the evil twin algorithm to decide when to resend the cell; for example if the cell was dropped due to output congestion it might make sense to back off on cells to that output).

For unicast traffic, part of switch bandwidth will be used to resend cells that did not make it through the first time around. This implies that sustained throughput is less than peak switching capacity. The amount of bandwidth required for resending cells and the effect of resending on latency and "Cell Delay Variation (CDV)" has been extensively studied with analytical models of the fabric. These results have then been cross checked with results from simulating software models of the fabric. This data is crucial for designing fabrics that can efficiently support

guaranteed "Quality of Service (QOS)" requirements. The recommended QSE fabric configurations for high quality switching takes these results into account; for example the 3 stage 160 Gb/s sustained throughput fabric has a peak capacity of 256 Gb/s (60% margin).

The QSE fabric is store-and-forward for multicast traffic. Cell replication is performed in an optimal tree based manner where replication is done as far downstream as possible and each QSE contains cell buffers to buffer multicast cells. A multipriority backpressure feedback is used to control the flow of multicast cells through the fabric.

#### **FEATURES**

### **Switching Algorithm**

- Supports blocking resolution in the switch fabric.

- Guarantees a lower bound on switch performance using a patented randomization algorithm called Evil Twin Switching.

- Determines routes using specified bits in the header (self-routing switch fabric) for unicast traffic.

- Determines output groupings using a lookup table for multicast traffic.

- Allows output ports to be combined in groups of 1, 2, 4, 8, 16, or 32 for unicast traffic.

- Allows output ports to be combined in groups of 1, 2, or 4 for multicast traffic.

### **Multicast Support**

- Supports optimal tree-based multicast replication in the switch fabric.

- Supports 512 internal multicast groups, expandable to 256K with external SRAM.

- Provides 64 internal cell buffers for multicast cells.

#### **Diagnostic/Robustness Features**

- Checks the header parity.

- Counts tagged cells.

- Checks for connectivity and stuck-at faults on all switch fabric interconnects.

## I/O Features

- Provides 32 switch fabric interfaces with integrated phase aligner clock recovery circuitry.

- Provides a Start-Of-Cell (SOC) output per four switch element interfaces.

- Provides an external 8-bit Synchronous SRAM (SSRAM) interface for multicast group expansion.

- Provides a demultiplexed address/data CPU interface.

- Provides an IEEE 1149.1 (JTAG) boundary scan test bus.

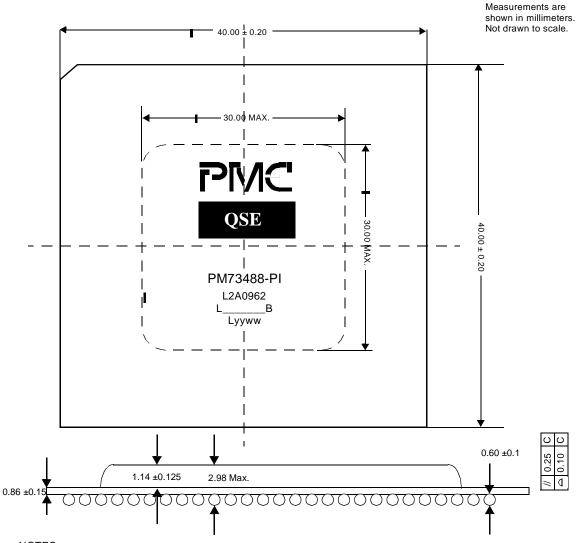

## **Physical Characteristics**

- 3.3 V supply voltage.

- 5 V tolerant inputs.

- 596-pin Enhanced Plastic Ball Grid Array (EPBGA) package.

- Operates from a single 66 MHz clock.

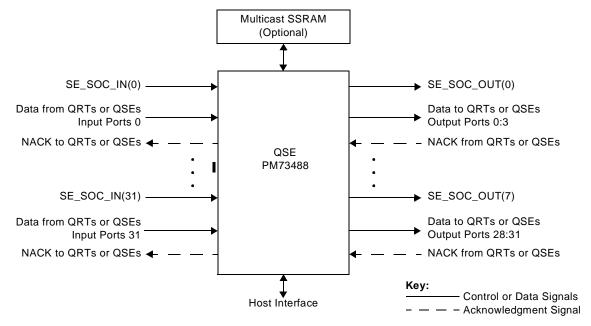

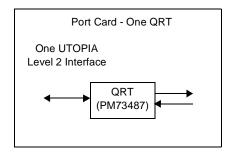

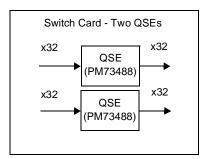

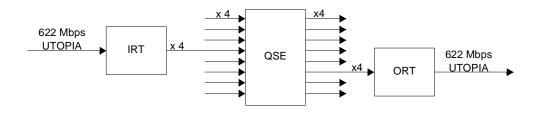

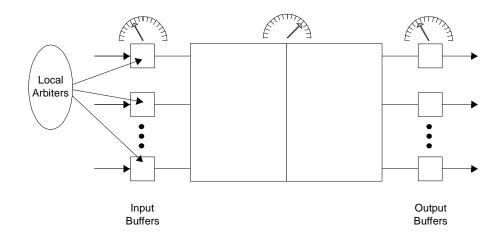

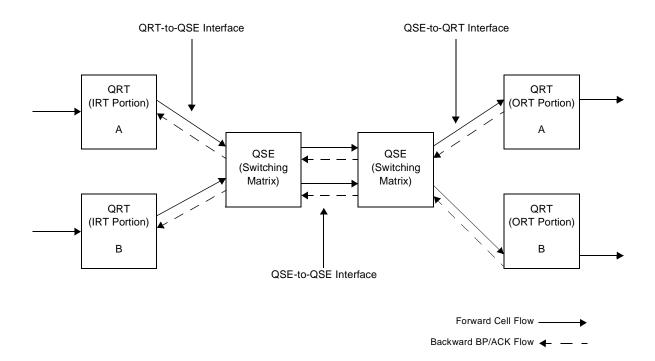

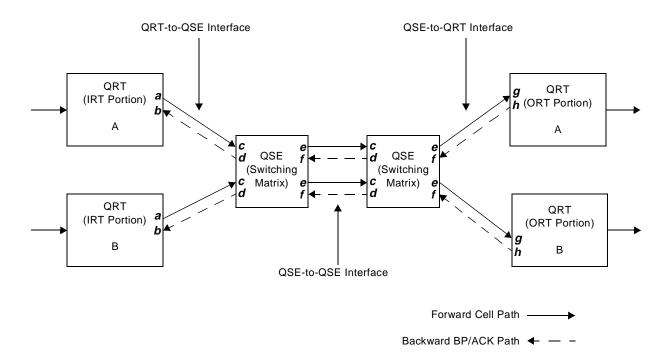

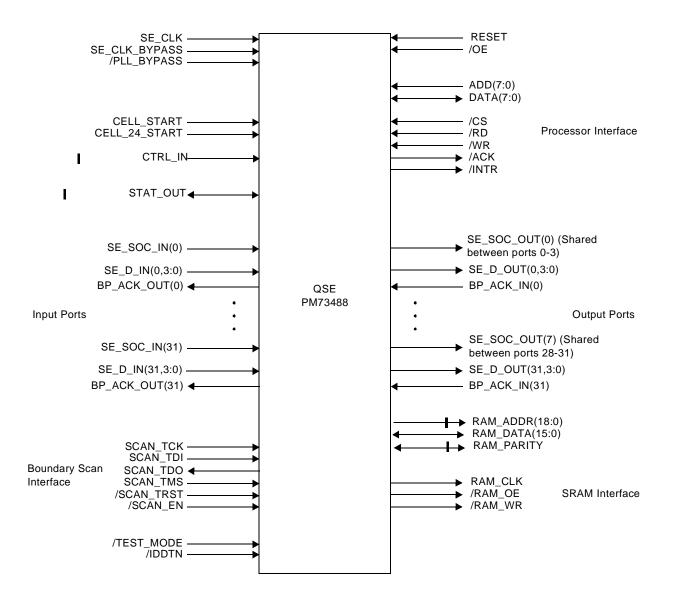

Figure 1 shows a QSE system block diagram.

Figure 1. QSE Interface Block Diagram

## 1 HOW THE QSE FITS INTO YOUR SYSTEM

The QSE, together with the QRT, supports a wide range of high-performance ATM switching systems. These systems range in size from 5 Gbps to 160 Gbps. The systems can be developed to provide scalability with linear cost. Another key feature of the QSE/QRT architecture is that it is exceptionally fault-tolerant, both in the switch fabric and the UTOPIA interface.

This section contains a quick overview of the QSE and several example applications:

- a 5 Gbps switch using PM73487s and a PM73488,

- a 10 Gbps switch using PM73487s and PM73488s,

- a switch architecture using PM73487s and PM73488s that scales from 5 Gbps to 20 Gbps,

- a switch architecture using PM73487s and PM73488s that scales from 5 Gpbs to 160 Gbps

## 1.1 QSE System Overview

The QSE is switch element, combinations of which allows switch fabric implementations that span from 5 Gbps to 160 Gbps. The bandwidth of a single QSE is 5Gbps of *sustainable* bandwidth; the raw, or peak, bandwidth is 8Gbps. (Thus the QSE has an in-built speed-up factor of 8/5 = 1.6.)

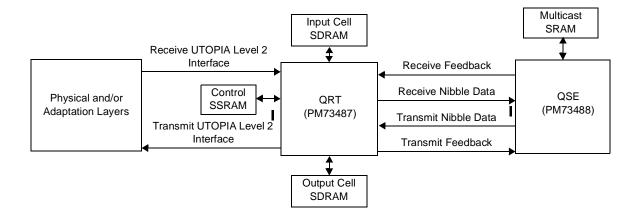

The QSE has 32 input ports and 32 output ports. Each port is a 66 MHz 6-bit interface, out of which 4 are data and 2 are control. Each port can be connected to another QSE or QRT. Figure 2 shows a QSE connected to a QRT.

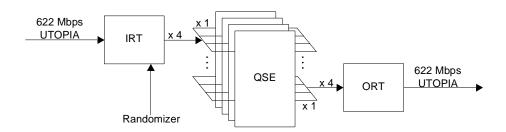

Figure 2. QSE System Overview

## 1.2 32 x 32 Switch Application (5 Gbps)

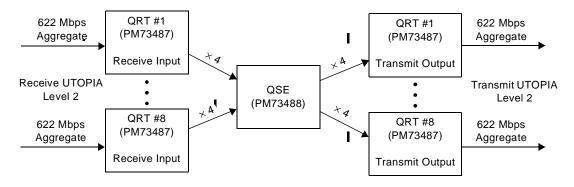

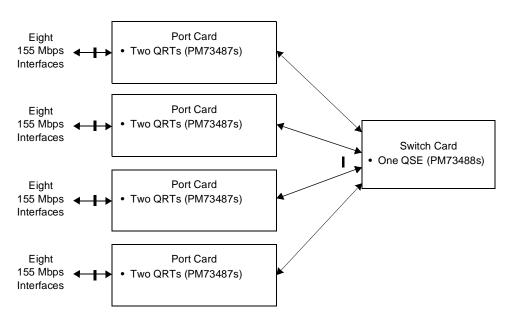

Figure 3 shows a basic  $32 \times 32$  switch application (5 Gbps) using one QSE and eight QRTs.

Figure 3. 32 x 32 Switch Application (5 Gbps)

## 1.3 64 x 64 Switch Application (10 Gbps)

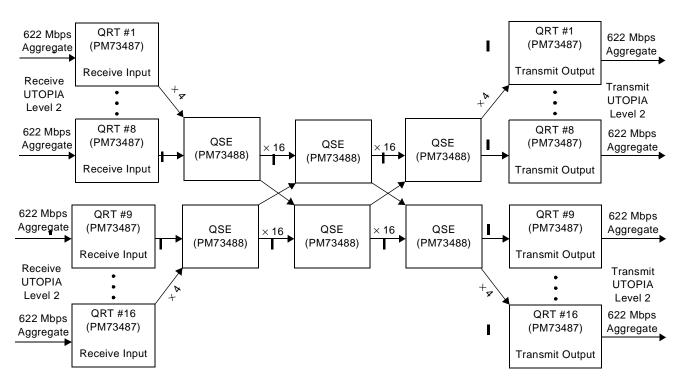

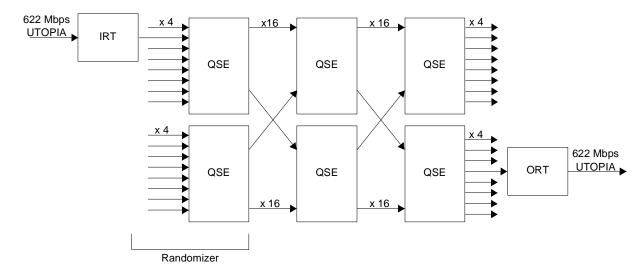

Figure 4 shows a  $64 \times 64$  switch application (10 Gbps) using 6 QSEs and 16 QRTs. This application uses QSEs in a 3-stage fabric. This sized system can be implemented in a single 19 inch rack.

Figure 4. 64 x 64 Switch Application (10 Gbps)

## 1.4 5 Gbps to 20 Gbps Application Example - Seamless Growth

Figure 5 illustrates the modularity of the QSE and QRT architecture. A 5 Gbps system can immediately be created (as shown in Figure 5), then be upgraded to 10 Gbps (as shown in Figure 6), or 20 Gbps (as shown in Figure 7 on page 19) with the QSE and the QRT. Since systems composed of the QSEs and QRTs are based on a single-stage switch fabric, the per-port cost for each system will remain the same.

Figure 5. 5 Gbps ATM Switch Using 8 QRTs, and 1 QSE

Figure 6. 10 Gbps ATM Switch Using 16 QRTs, and 2 QSEs

Figure 7. 20 Gbps ATM Switch Using 32 QRTs, and 4 QSEs

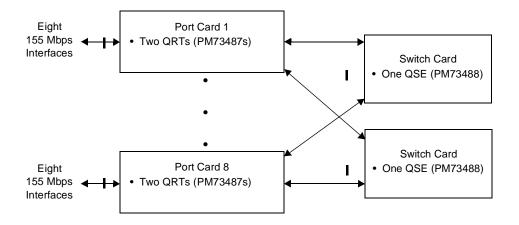

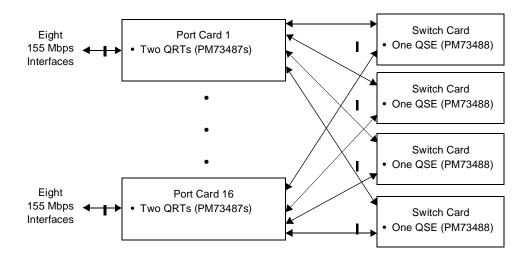

## 1.5 5 Gbps to 160 Gbps Application Example - LAN-to-WAN

A powerful application of the QRT and QSE devices is the creation of modules that can be used in a range of switches with only the interconnection changing between different sizes. ATM switches from 5 Gbps to 160 Gbps can be realized with only two unique cards. A port card has one QRT, and a switch card has two QSEs. The switch fabric consists of three stages, each with 32 QSEs (or 16 switch cards). To plan for future scalability, the middle stage must be built-in upfront. This is a one-time cost. Then, in order to scale in 5 Gbps increments, one switch card and its accompanying eight port cards should be added. Finer bandwidth scaling is possible by populating the additional switch card with port cards as needed (in increments of 622 Mbps). With this switch fabric topology, scaling is possible up to 160 Gbps. Once the initial middle stage cost has been incurred, the per-port cost for 5 Gbps through 160 Gbps systems remains constant

Figure 8. 5 Gbps to 160 Gbps Switches Modeled Using Only Two Cards

Figure 9. 5 Gbps ATM Switch

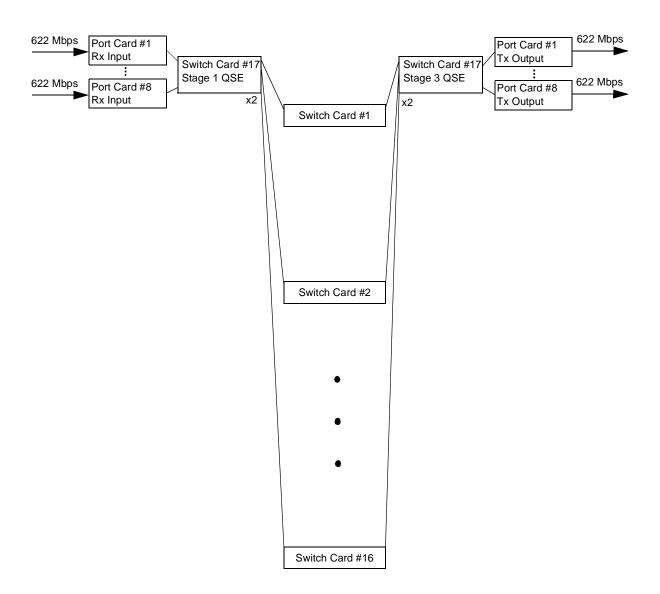

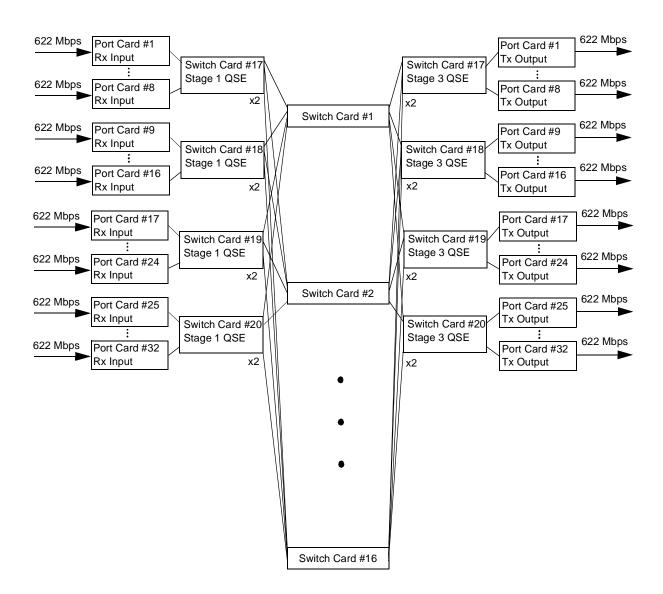

Figure 9 shows a 5 Gbps ATM switch using 8 port cards (8 QRTs) and 17 switch cards (34 QSEs). The middle stage is composed of 16 switch cards. The 5 Gbps bandwith is achieved by adding switch card #17 (which is depicted using two boxes: one stage 1 QSE and one stage 3 QSE), and eight port cards (each of which is depicted using two boxes: one for the Rx input side, and one for the Tx output side). Lines between stage 1 and stage 2, and stage 2 and stage 3 switch cards represent two sets of wires, one to each of the QSEs in the middle stage switch cards.

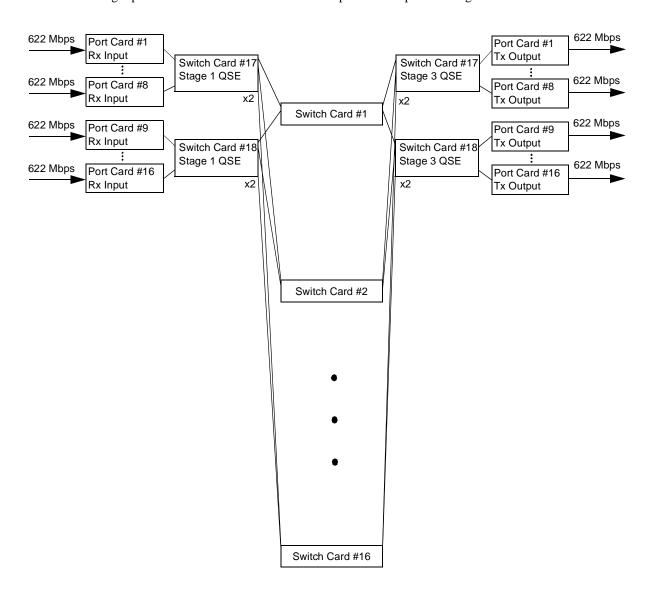

Figure 10 shows a 10 Gbps ATM switch using 16 port cards (16 QRTs) and 18 switch cards (36 QSEs). Here, another switch card and eight port cards have been added to the 5 Gbps switch depicted in Figure 9.

Figure 10. 10 Gbps ATM Switch

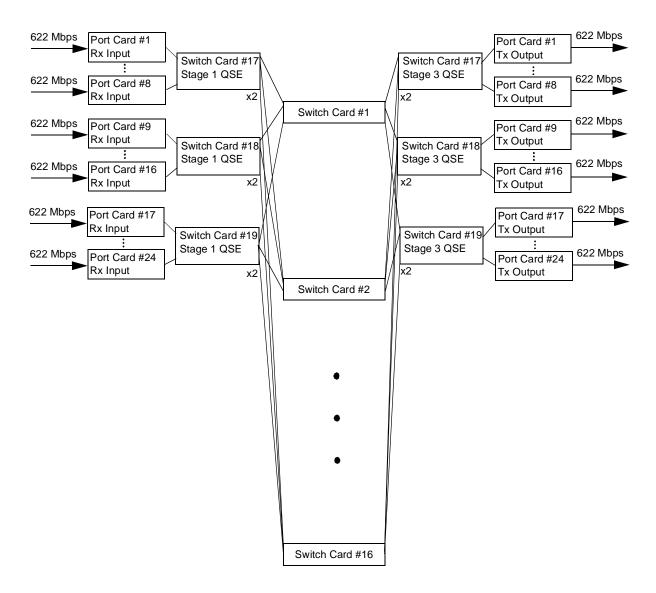

Figure 11 shows a 15 Gbps ATM switch using 24 port cards (24 QRTs) and 19 switch cards (38 QSEs). Here, once again, another switch card and eight port cards have been added

Figure 11. 15 Gbps ATM Switch

Figure 12 shows a 20 Gbps ATM switch composed of 32 port cards (32 QRTs) and 20 switch cards (40 QSEs). By adding additional sets of a switch card and eight port cards in the same manner, this system can scale up to 160 Gbps.

Figure 12. 20 Gbps ATM Switch

## 2 THEORY OF OPERATION

Multiple PM73488 QSEs can be combined to build a scalable switch fabric. The QSE switches data in the form of 118 nibble cells. The QSE has 32-input ports and 32 output ports, each containing a nibble-wide data interface, an SOC signal, and a backpressure/data-acknowledge signal.

Groups of 1, 2, 4, 8, 16, or 32 ports can be internally configured to act as a single aggregate port (also called gang) for unicast traffic. For multicast traffic, inputs and outputs can be grouped together in groups of 1, 2, or 4 ports. The input multicast grouping mode, output multicast grouping mode, and the unicast grouping modes do not need to be the same. Also, the QSE can be configured as a single 32 input  $\times$  32 output switch

The cell flow through the QSE has two separate data paths; one path for unicast cells and another path for multicast cells. Unicast cells are routed from one end of the switch fabric to the other end in a single cell time. In other words, no unicast cells are ever stored in the switch fabric. Unicast cells are stored only at the ingress and egress of the switch fabric. Multicast cells are routed in a store-and-forward manner. Each QSE can store up to 64 multicast cells. The QRT used as an interface to a switch fabric constructed with QSEs allows the construction of an ATM switch up to 160 Gbps.

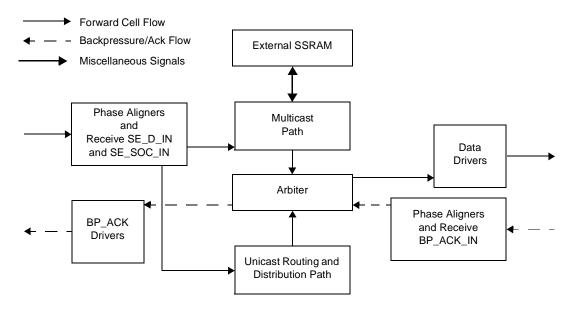

A diagram of the QSE cell flow is shown in Figure 13. The unicast cell flow contains a routing stage that uses routing information from the cell header to determine the output group. The multicast cell flow contains an interface to an external SSRAM that contains the Multicast Port Vector (MPV) information for routing cells to multiple output groups.

Figure 13. Basic QSE Flow

### 2.1 Phase Aligners

Phase aligners aid in constructing large systems. Clock information is recovered from the data sent to each QSE switch fabric port. Phase aligners are used on the BP\_ACK\_IN(31:0), SE\_SOC\_IN(31:0), and SE\_D\_IN(31:0, 3:0) signal lines. Since there is no setup or hold time requirements on these signals, the overall clock distribution scheme within the system can be simplified. However, overall system jitter and skew between signals on the same switch fabric data port must still be managed.

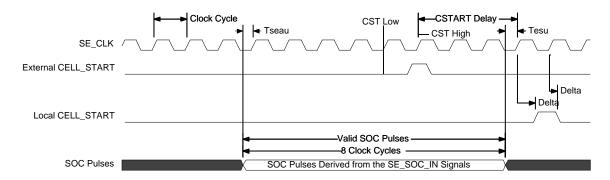

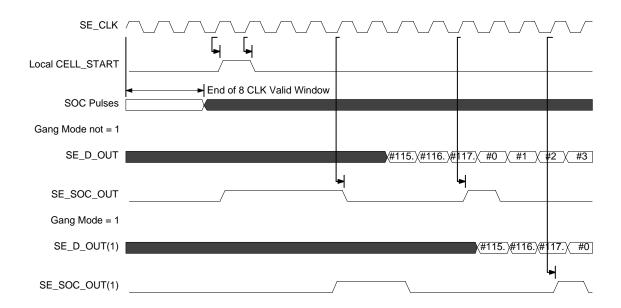

#### 2.2 Data Drivers

Another aid to constructing large systems is an elastic store at each QSE input data port. The data elastic store allows data arriving from different ports to be offset by up to a maximum of eight clock cycles. The internally generated and software programmable local CELL\_START signal marks the end of an 8-clock-period window within which the SOC marker on each of the SE\_SOC\_IN(31:0) lines must arrive.

### 2.3 Unicast Routing and Distribution

Each of the 32 nibble-wide inputs is connected to an output by a crossbar. This crossbar is transparently controlled by the cell's routing tag, which specifies the input-to-output connection. In the event of a conflict for an output port, higher priority cells are given preference over lower priority cells. There are three unicast cell priorities: high, medium, and low.

The gang of 32, also known as distribution mode, is a special unicast routing mode in which incoming unicast cells are routed to outputs using PMC's patented congestion-minimization (Evil Twin Switching) algorithm. In this mode, no routing information is used from the cell's routing tag.

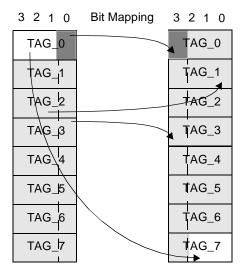

Depending on the gang mode, the QSE will need a number of routing bits to determine the output gang of a unicast cell. For example, in gang mode of four, there are eight output gangs, thus three routing bits are required for selecting the QSE. However, in distribution mode no routing bits are needed. The routing bits are taken from the head of the routing tag and are then shifted back in at the tail (which preserves header parity). This allows the next set of routing bits to be always accessible at the same spot in the tag, namely the head. The cell routing tag is broken into eight nibbles, namely TAG\_0 through TAG\_7.

Figure 14 on page 27 shows the tag rotation for gang mode of four (three routing bits are used by the QSE from TAG\_0 and then shifted back in at the tail of TAG\_7). TAG\_0 is broken up and part of it ended up at the end of TAG\_7 (shown by the white area in Figure 14 on page 27). As a result, all the other tags (TAG\_1 through TAG\_7) also get broken up and shifted (as shown by the light and dark gray areas of Figure 14 on page 27).

Figure 14. Routing Bits Rotation for Unicast Traffic, Gang Mode of Four

#### 2.4 Multicast Cell Flow

I

There are 64 internal cell buffers for multicast traffic. These buffers are shared among three multicast priorities: high, medium, and low. These 64 buffers are grouped into two sets of 32-cell buffers each. One set is dedicated to ports 0 to 15, the other set to ports 16 to 32.

A multicast queue engine dynamically allocates the cell buffers to incoming multicast cells. Each cell is buffered until it can be sent out on all output ports to which it should be routed. These output ports are designated by a Multicast Group Vector (MGV) that is associated with a Multicast Group Index (MGI) carried by each multicast cell. Each QSE holds multicast MGVs in an MGV RAM. The QSE has internal RAM to support up to 128 MGVs. This support can be extended up to 256K MGVs by using an external MGV RAM.

Each multicast cell contains the RAM address of the MGV it is supposed to use. When a multicast cell is received, its MGV is fetched from RAM and copied to the MULTICAST\_QUEUE\_COMPLETION register. The MULTICAST\_QUEUE\_COMPLETION register tracks to which QSE ports the cell needs to be sent before its cell buffer can be cleared. In a multistage QSE fabric, each multicast cell will look up MGVs at each QSE. The MGV's sequence determines which output ports will finally receive the cell. The MGV structure allows software to create an optimal distribution tree for each multicast cell.

Multicast operation can be best understood by considering the QSE multicast path as two separate engines; the multicast queue engine and the multicast dequeue engine. The multicast queue engine queues cells into the multicast cell buffers (of which there are 64), and issues backpressure on the BP\_ACK\_OUT(31:0) lines. The multicast dequeue engine selects and dequeues cells from the buffers for output ports as guided by the backpressure received on the BP\_ACK\_IN(31:0) lines.

### 2.4.1 Multicast Queue Engine

The multicast queue engine associates input ports with cell buffers, computes backpressure for the input ports, and stores incoming cells into the buffers. In doing so, it guarantees:

- No input port will have more than three cells pending in the QSE this can be changed to allow four pending cells by setting the "Allow 4 Bits Per Port" bit (bit 1) in the BP CONTROL register.

- No input port will have more than two high-priority cells pending.

- The sum of low- and medium-priority cells pending from any single input port will be less than 2.

In addition, the queue engine allows buffers to be reserved for high-priority cells or high/medium-priority cells. This is controlled by bits 2 and 3 of the BP\_CONTROL\_REGISTER (refer to section 9.3.29 "BP\_CONTROL\_REGISTER" on page 109). The four possible combinations for these two bits are listed in Table 1. The multicast queue engine will compute backpressure for the preceding QSE/QRT to ensure the constraints listed in Table 1 are satisfied. The same reservation policy applies to *both* sets of 32 buffers.

| 18 | able 1. BP_CONTROL | _REGISTER; I | i nresnoia Control | Bits for Each | Set of 32 Buffer | S |

|----|--------------------|--------------|--------------------|---------------|------------------|---|

|    |                    |              |                    |               |                  |   |

| Bit 3 | Bit 2 | Description                                                                                                                                                                                       |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | <ul> <li>Four buffers are reserved for high-priority cells.</li> <li>Four buffers are reserved for high- or medium-priority cells.</li> <li>All other buffers can be used by any cell.</li> </ul> |

| 0     | 1     | <ul><li>Four buffers are reserved for high-priority cells.</li><li>All other buffers can be used by any cell.</li></ul>                                                                           |

| 1     | 0     | <ul> <li>Eight buffers are reserved for high- or medium-priority cells.</li> <li>All other buffers can be used by any cell.</li> </ul>                                                            |

| 1     | 1     | All buffers can be used by any cell.                                                                                                                                                              |

After the MGV address for the cell enters the QSE, the MGV associated with that cell is fetched and loaded into the QUEUE\_COMPLETION\_REGISTER (an internal register) as soon as possible.

## 2.4.2 Multicast Dequeue Engine

In each cell time, the multicast dequeue engine selects one multicast cell for each of the 32 output ports. In effect, all multicast cells wanting to go to a particular output port arbitrate among themselves to select the most appropriate port. Arbitration occurs independently for all 32 ports. The cells winning the internal multicast arbitration then compete with the incoming unicast cells for access to the output ports. Multicast arbitration winners are chosen to satisfy the following conditions in this sequence:

- Obey backpressure from the down stream QSE or QRT. Only cells with the allowed priorities will take part in arbitration.

- Higher priority cells win over lower priority cells.

- Cells that came in earlier win over cells that came in later (if they have the same priority).

- If multiple cells have the same priority and came in simultaneously, cells from a random input gang group will be selected.

- If multiple cells have the same priority, came in simultaneously, and belong to the same input gang group, the cell with the lowest port number will be selected.

- Ties are broken randomly.

This arbitration occurs among all cells in the cell buffers and occurs for all 32 ports. In effect, arbitration occurs for output ports in sequence, starting with cells arbitrating for port 0, then for port 1, and continuing on until port 31 (even though the actual implementation uses a parallel algorithm).

Multicast cells that have won this arbitration then compete with unicast cells for access to the output ports. In this contention, the cell with the highest priority wins and ties are broken randomly according to the programmable ratio set in the UC/MC\_FAIRNESS\_REGISTER (refer to section 9.3.6 "UC/MC\_FAIRNESS\_REGISTER" on page 97).

All these operations are optimized so that, in the absence of congestion, it is possible for a multicast cell to leave the QSE in the cell time immediately after it arrived.

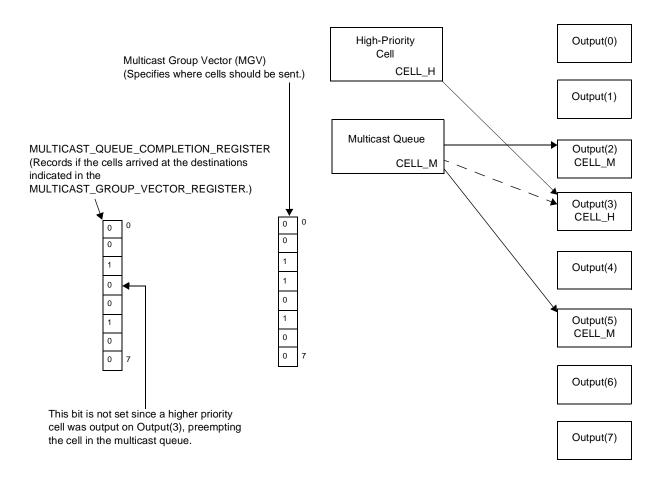

As mentioned before, the queue completion register (32-bit vector) indicates the outputs to which each multicast cell needs to go. As a cell goes out on its desired outputs, the appropriate bits in the queue completion register are cleared. When all bits in the queue completion register have been cleared, the cell is deleted from the internal buffers and the buffer is reused for new incoming traffic.

Figure 15 shows an example of a high-priority cell preempting a cell in the multicast queue, and the resulting bit settings in the MULTICAST\_QUEUE\_COMPLETION\_REGISTER (an internal register). (For the sake of simplicity, only 8 of the 32 outputs, and eight bits of the MGV\_REGISTER (refer to section 9.3.4 "MULTICAST\_GROUP\_VECTOR\_REGISTER" on page 96) and MULTICAST\_GROUP\_COMPLETION\_REGISTER (an internal register) are shown.)

Figure 15. Example of Multicast Cell Handling in the QSE

#### 2.5 Arbiter

The arbiter selects between unicast cells and multicast cells contending for the same output port. Higher priority cells are given preference over lower priority cells. If a multicast cell and unicast cell have the same priority, one cell is randomly chosen. The random choice can be biased in favor of either unicast cells or multicast cells at different points in the switch fabric by using the UC/MC\_FAIRNESS\_REGISTER (refer to section 9.3.6 "UC/MC\_FAIRNESS\_REGISTER" on page 97). In general, unicast cells should be favored at later stages in the switch fabric. Favoring unicast cells is necessary in multiple-stage switch fabrics since unicast cells are routed in a cut-through fashion and multicast cells are routed in a store-and-forward fashion. As such, a unicast cell becomes more "valuable" as it proceeds further in the switch fabric, since it did so at the expense of other cells.

For example, consider a congested 3-stage switch fabric where unicast cells and multicast cells of equal priorities collide at each stage in the fabric, without any biasing. A unicast cell must make it from ingress to egress in one cell time and the chances of doing so would be a little more than  $(1/2)^3 = 12.5\%$ . However, each multicast cell would have a 50% chance of advancing to the next stage in the switch fabric.

#### 2.6 BP ACK Drivers

The BP\_ACK\_OUT(31:0) lines are used to send information from a QSE to upstream QSEs or QRTs. These lines are used to send two types of information:

- Backpressure information (for unicast cells).

- Transmit acknowledge information (for multicast cells).

Backpressure information is sent for multicast cells. This information indicates to an upstream QRT or QSE if the QSE can accept another multicast cell in the next cell time. Backpressure information also indicates what multicast cell priorities the QSE can accept.

Cell transmit acknowledge information is sent for unicast cells. This information signals whether or not the unicast cell transmitted in the current cell time made it to its destination QRT. If the cell makes it to the destination QRT, an Acknowledgment (ACK) is sent. If the cell has been dropped in the switch fabric, information is sent back indicating if the cell was dropped internally Mid Switch Negative Acknowledgment (MNACK) or at the output of the switch fabric Output Negative Acknowledgment (ONACK). The MNACK and ONACK is used by the QRT to determine when to retry sending the given cell.

### 2.7 Interdevice Interconnectability

All input and output ports can be configured in groups of four to directly connect to either QRT devices or other QSE devices. This allows considerable flexibility in the switch fabric types and sizes that can be constructed using the entire PMC chip set.

#### 2.8 Network Topologies and the Speedup Factor (SF)

For many switch fabric architectures using the QSE, a single metric called the Speedup Factor (SF) allows comparison of different network topologies, which is independent of traffic load and type. The SF also allows for predictions about the network performance.

Before describing the SF metric, we will briefly discuss the network philosophy and the different network topologies.

## 2.8.1 Network Philosophy

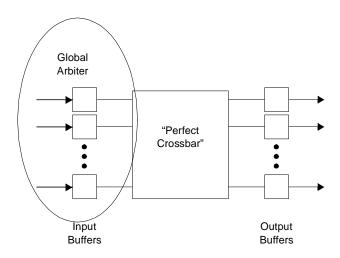

Given current technology, to scale through 160 Gbps, a network must be distributed and use buffers at the network inputs and outputs. In an ideal world, crossbars of any arbitrary size could be built to provide connectivity for the network inputs and outputs. Additionally, there would be a central "brain", or global arbiter, to control the input buffers and schedule cells optimally for routing in the network, as shown in Figure 16.

Figure 16. Ideal Distributed Network

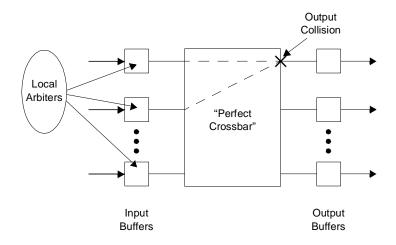

Unfortunately, given real constraints, it is not possible to have a global arbiter wired to each input that has knowledge of all cells in the system, and can quickly make optimal decisions about routing. Thus, each input must make decisions using knowledge local to its buffers. This results in the possibility of collisions at the network outputs, even though it is a "perfect" crossbar, as shown in Figure 17.

Figure 17. More Realistic Distributed Network

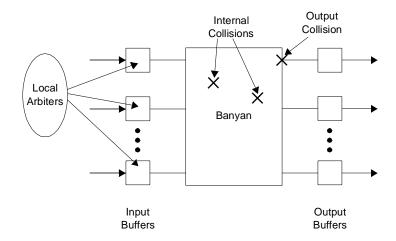

Replacing the idealized crossbar with a buildable, traditional Banyan network increases the possibility of internal network collisions, as shown in Figure 18. Given a particular Banyan network, one can always find a large class of traffic patterns that will cause many internal collisions. For large Banyan networks, the collision problem is greatly increased.

Figure 18. "Large" Distributed Network (Will not Work Well with Banyan Alone)

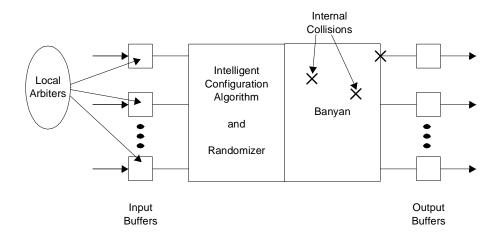

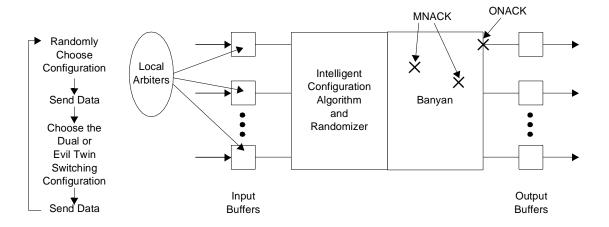

To reduce internal collisions in the traffic-dependent Banyan networks, the QRT/QSE network adds a distribution/randomizing network (shown in Figure 19) that uses a patented intelligent configuration algorithm, known as Evil Twin Switching. The algorithm (described in section 2.8.3 "Speedup Factor (SF)" on page 36) allows lower-bounding the network performance, independent of traffic patterns.

Figure 19. High-Level QRT/QSE System

To overcome the inefficiencies caused by collision in the network, the fabric must be run at a rate greater than line rate. The speedup factor is the minimum rate necessary to guarantee that the network is no longer the system bottleneck. Note that in this case, the network efficiently moves data from the input to the output buffers, and the switch performs similar to a purely output buffered switch.

#### 2.8.2 Network Definition

A large range of switch fabrics can be described as follows: with the following notation: "p" refers to the number of fabric planes, and "x," "y," and "z" refer to the routing tag size necessary to make routing decisions in the Banyan section of the network to route cells to the correct output port. This is summarized as follows:

```

(z)xp — 1-stage network

(y,z)xp — 3-stage network

```

Hence, the  $(3) \times 1$  network shown in Figure 20 refers to a single switch stage, and three routing bits are required to select from one of the eight output port groupings. (Recall that the QSE has 32 output ports that can be configured in groups of 1, 2, 4, 8, 16, or 32. In Figure 20, they are configured in groups of four. The input and output buffers provided by the QRT have four input ports and four output ports to the switch fabric, and are logically broken into the input half of the QRT (IRT) and output half of the QRT (ORT) for convenience.

Figure 20. (3) x 1 - 5 Gbps System

The  $(5) \times 4$  network shown in Figure 21 is an example of a network with four parallel planes. It demonstrates the flexibility allowed because the QRT has four input and output ports. In this case, randomization is performed in the IRT.

Figure 21. (5) x 4 - 20 Gbps System

In Figure 22, the first stage of QSEs is configured to provide the required randomization, and the next two switch stages route the cells to the final port destination. The second QSE stage needs only to make an "up" or "down" decision requiring a single routing bit, while the third QSE stage needs to select between eight QRTs, requiring three routing bits.

Figure 22. (1,3) x 1 - 10 Gbps System

## 2.8.3 Speedup Factor (SF)

If the traffic pattern presented to a particular Banyan network results in many internal collision, a shuffling pattern exists that has been proven to result in few internal collisions. Although a purely random reshuffling results in good behavior, we can lower-bound network performance by using randomization along with the Evil Twin Switching algorithm as shown in Figure 23. This algorithm is as follows: randomly choose a configuration, route data, choose the dual or Evil Twin Switching configuration, route data, and repeat. This algorithm minimizes the number of internal collisions. In 3-stage networks, the first stage of the QSEs provide this functionality.

Figure 23. Randomizer (with Evil Twin Switching Algorithm)

Even with a perfect crossbar for a network, there are still output collisions, and despite the Evil Twin Switching algorithm, there are still internal collisions (albeit fewer). Thus, multiple routing attempts must be made per cell to yield full throughput. This can be accomplished by running the switch fabric at a faster clock rate than the buffering logic.

Figure 24. Network Needs to be Run Faster than the Line Rate

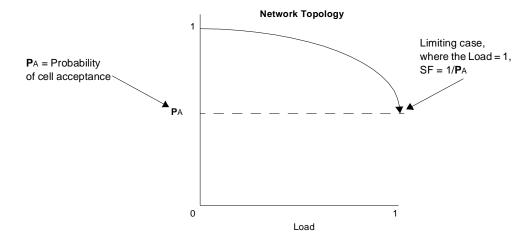

The chance for internal collisions increases as the network load increases, and the exact behavior varies with network topology. An example of this behavior is shown in Figure 25 and the SF is inferred from the limiting case where the network is fully loaded.

Figure 25. Definition of the Speedup Factor

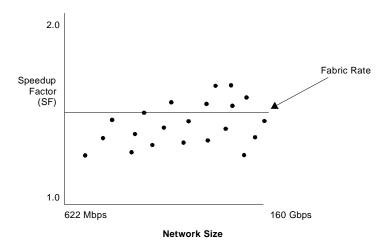

Given this notion of SF, "how much faster is fast enough?" Theoretical models and simulations can answer that question. Given that the switch fabric can be run at a certain clock rate relative to the buffering logic, we can know which networks to choose to prevent the network from becoming a bottleneck.

Figure 26. How to Use the SF to Select Favorable Networks

Table 2, Table 3 show all of the 1-, 3-stage network topologies requiring an SF of less than 1.6, which is the maximum speedup allowed by the actual implementation.

PMC-980616 Issue 3

5 Gbit/s ATM Switch Fabric Element

Table 2. Speedup Factor (1-Stage Networks)

| Network | Size<br>(Gbps) | Speedup Factor<br>(SF) | Number of QSEs |

|---------|----------------|------------------------|----------------|

| (3) × 1 | 5              | 1.22                   | 1              |

| (4) × 2 | 10             | 1.36                   | 2              |

| (5)×4   | 20             | 1.57                   | 4              |

Table 3. Speedup Factor (3-Stage Networks)

| Network          | Size<br>(Gbps) | Speedup Factor<br>(SF) | Number of QSEs |

|------------------|----------------|------------------------|----------------|

| $(1,3) \times 1$ | 10             | 1.28                   | 6              |

| $(1,4) \times 2$ | 20             | 1.41                   | 12             |

| $(2,3) \times 1$ | 20             | 1.32                   | 12             |

| $(2,4) \times 2$ | 40             | 1.46                   | 24             |

| $(3,3) \times 1$ | 40             | 1.39                   | 24             |

| $(3,4) \times 2$ | 80             | 1.53                   | 48             |

| $(4,3) \times 1$ | 80             | 1.49                   | 48             |

## 3 EXTERNAL PORT DESCRIPTIONS

### 3.1 Switch Fabric Port and Interface Description

Each port is a 6-bit interface consisting of:

- a nibble-wide data interface (SE D IN and SE D OUT),

- an SOC signal (SE\_SOC\_IN and SE\_SOC\_OUT), and

- a backpressure/data acknowledge signal (BP\_ACK\_IN and BP\_ACK\_OUT).

## 3.1.1 SE\_SOC Encodings

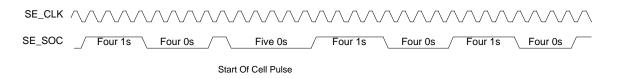

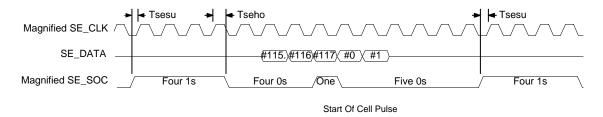

The SE\_SOC encodings (SE\_SOC\_IN(31:0), SE\_SOC\_OUT(7:0)) provide guaranteed transitions and SOC encodings.

The SE\_SOC signals carry a repeating four "0s" and four "1s" pattern to guarantee transitions required by the phase aligner. The SOC signal on data lines associated with an SE\_SOC line is indicated by a break in this repeating pattern. The SOC is a single "1" followed by five "0s". Figure 27 shows the guaranteed transitions. Figure 28 provides an expanded view of the signal transitions and the first nibble after the SOC pulse (nibble #0) corresponds to nibble "0" in Table 5 on page 40.

Figure 27. SE\_SOC Encodings

Figure 28. Expanded SE\_SOC Encodings

I

PMC-980616 Issue 3 5 Gbit/s ATM Switch Fabric Element

## 3.1.2 Data Cell Format

The regular cell format is shown in Table 5.

# Table 5. Regular Cell Format

| Nibble | Symbol                    | Definition                                                                                                                                                                                                                                                                           | Comment                                                                                                                                                                                              |

|--------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | PRES(1:0),<br>MC,<br>SP   | Pres = 10 <sub>b</sub> : Cell present.  01 <sub>b</sub> : Cell not present (See Table 6 on page 41).  00 <sub>b</sub> : Cell assumed to be not present (failure).  11 <sub>b</sub> : Cell assumed to be not present (failure).  MC = 1 <sub>b</sub> : Multicast Cell.  SP Spare bit. | The spare bit is not interpreted or used by the QSE.                                                                                                                                                 |

| 1      | SP(1:0),<br>PRIORITY(1:0) | SP(1:0) Spare bits.<br>Priority = $11_b$ : High-priority cell.<br>$10_b$ : Medium-priority cell.<br>$01_b$ : Low-priority cell.<br>$00_b$ : Undefined. Cell discarded by QSE.                                                                                                        | Priority for the switching fabric. The QRT should be configured never to generate priority $00_b$ cells, since they are discarded by the QSE. The spare bits are not interpreted or used by the QSE. |

| 2      | TAG_0                     | Routing tag 0 or MULTICAST_GROUP_INDEX(15:12). Refer to section 9.3.3 "MULTICAST_GROUP_INDEX_REGISTER" on page 96.                                                                                                                                                                   |                                                                                                                                                                                                      |

| 3      | TAG_1                     | Routing tag 1 or MULTICAST_GROUP_INDEX(11:8). Refer to section 9.3.3 "MULTICAST_GROUP_INDEX_REGISTER" on page 96.                                                                                                                                                                    |                                                                                                                                                                                                      |

| 4      | TAG_2                     | Routing tag 2 or MULTICAST_GROUP_INDEX(7:4). Refer to section 9.3.3 "MULTICAST_GROUP_INDEX_REGISTER" on page 96.                                                                                                                                                                     | Interpretation of TAG_5:0 depends on whether or not the cell is a multicast cell.                                                                                                                    |

| 5      | TAG_3                     | Routing tag 3 or MULTICAST_GROUP_INDEX(3:0). Refer to section 9.3.3 "MULTICAST_GROUP_INDEX_REGISTER" on page 96.                                                                                                                                                                     |                                                                                                                                                                                                      |

| 6      | TAG_4                     | Routing tag 4 or MULTICAST_GROUP_INDEX(23:20).                                                                                                                                                                                                                                       | Currently, QSE supports only 256K multicast group vectors, i.e. it only uses multicast group index(17:0). Therefore, bits 23:20 are ignored.                                                         |

| 7      | TAG_5                     | Routing tag 5 or MULTICAST_GROUP_INDEX(19:16). Refer to section 9.3.8 "MULTICAST_GROUP_INDEX_MSB" on page 98.                                                                                                                                                                        | Currently, QSE supports only 256K multicast group vectors, i.e. it only uses multicast group index(17:0). Therefore, bits (19:18) are ignored.                                                       |

| 8      | TAG_6                     | Routing tag 6.                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      |

# Table 5. Regular Cell Format (Continued)

| Nibble | Symbol                    | Definition                                                                                                                                                                                                                                                                                                                                        | Comment              |

|--------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 9      | TAG_7                     | Routing tag 7.                                                                                                                                                                                                                                                                                                                                    |                      |

| 10     | OUTCHAN_3                 | Interpreted as OUTCHAN(15:12) by a QRT.                                                                                                                                                                                                                                                                                                           | Not used by the QSE. |

| 11     | SP(1:0),<br>MB,<br>PARITY | SP(1:0) Spare bits.  MB Mark bit: Cells that are present and have this bit set are counted by the INPUT_MARKED_CELL_COUNT (refer to section 9.3.11  "INPUT_MARKED_CELLS_COUNT" on page 99) and OUTPUT_MARKED_CELL_COUNT (refer to section 9.3.12  "OUTPUT_MARKED_CELLS_COUNT" on page 99) counters.  P Should be odd parity over nibbles 0 to 11. |                      |

| 12     | OUTCHAN_2                 | Interpreted as OUTCHAN(11:8) by a QRT.                                                                                                                                                                                                                                                                                                            | Not used by the QSE. |

| 13     | OUTCHAN_1                 | Interpreted as OUTCHAN(7:4) by a QRT.                                                                                                                                                                                                                                                                                                             | Not used by the QSE. |

| 14     | OUTCHAN_0                 | Interpreted as OUTCHAN(3:0) by a QRT.                                                                                                                                                                                                                                                                                                             | Not used by the QSE. |

| 15     | VCI_3                     | Interpreted as Virtual Channel Identifier (VCI)(15:12) by a QRT.                                                                                                                                                                                                                                                                                  | Not used by the QSE. |

| 16     | VCI_2                     | Interpreted as VCI(11:8) by a QRT.                                                                                                                                                                                                                                                                                                                | Not used by the QSE. |

| 17     | VCI_1                     | Interpreted as VCI(7:4) by a QRT.                                                                                                                                                                                                                                                                                                                 | Not used by the QSE. |

| 18     | VCI_0                     | Interpreted as VCI(3:0) by a QRT.                                                                                                                                                                                                                                                                                                                 | Not used by the QSE. |

| 19     | PTI(2:0)/CLP              | Interpreted as the Payload Type Indicator (PTI) and Cell Loss Priority (CLP) fields from the cell by a PM73487A.                                                                                                                                                                                                                                  | Not used by the QSE. |

| 20     | SEQ_1                     | Interpreted as SEQ(7:4) by a QRT.                                                                                                                                                                                                                                                                                                                 | Not used by the QSE. |

| 21     | SEQ_0                     | Interpreted as SEQ(3:0) by a QRT.                                                                                                                                                                                                                                                                                                                 | Not used by the QSE. |

| 22-117 | Payload                   | Interpreted as 48 bytes of ATM cell payload by a QRT.                                                                                                                                                                                                                                                                                             | Not used by the QSE. |

The idle cell format is shown in Table 6. The idle cell format is chosen to make the interface robust to both stuck-at faults, as well as bridging faults on the data lines.

Table 6. PM73488 Mode Idle Cell Format

| Nibble | Symbol    | Definition                                                                               | Comment |

|--------|-----------|------------------------------------------------------------------------------------------|---------|

| 0      | Pres(3:0) | Pres = 0100 <sub>b</sub> : Cell not present.                                             |         |

| 1      | IDLE_0    | $IDLE_0 = 0000_b$ : All 0.                                                               |         |

| 2      | IDLE_1    | IDLE_1 = 1000 <sub>b</sub> : Marching 1 pattern, which protects against bridging faults. |         |

PMC-980616 Issue 3 5 Gbit/s ATM Switch Fabric Element

Table 6. PM73488 Mode Idle Cell Format (Continued)

| Nibble | Symbol   | Definition                                                                               | Comment |

|--------|----------|------------------------------------------------------------------------------------------|---------|

| 3      | IDLE_2   | IDLE_2 = 0100 <sub>b</sub> : Marching 1 pattern, which protects against bridging faults. |         |

| 4      | IDLE_3   | IDLE_3 = 0010 <sub>b</sub> : Marching 1 pattern, which protects against bridging faults. |         |

| 5      | IDLE_4   | IDLE_4 = 0001 <sub>b</sub> : Marching 1 pattern, which protects against bridging faults. |         |

| 6      | IDLE_5   | IDLE_5 = 0000 <sub>b</sub> :                                                             |         |

| 7      | IDLE_6   | $IDLE_{-}6 = 0000_{b}.$                                                                  |         |

| 8-15   | Reserved | (QSE currently outputs 0000 <sub>b</sub> .)                                              |         |

| 16-117 | Unused   | (QSE currently outputs 0000 <sub>b</sub> .)                                              |         |

## 3.1.3 BP\_ACK Encodings

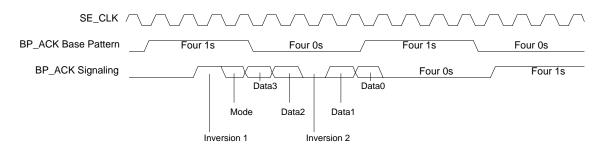

The BP\_ACK encodings (BP\_ACK\_IN and BP\_ACK\_OUT) guarantee transitions, and BP and ACK encodings are shown in Figure 29.

The BP\_ACK signal is used to signal backpressure/cell acknowledgment to the previous stage. To ensure the transitions required by the phase aligner, this line carries a repeating four "0s" and four "1s" pattern. The actual information is transferred by a break in this pattern (shown by BP\_ACK signaling in Figure 29). The pattern break is identified by a bit inversion (Inversion 1) on the line, followed by a mode, and two data bits, followed by a second inversion (Inversion2) of the expected bit, if the previous pattern had continued. This is followed by the last two bits. After these information bits, the repeating pattern restarts with four "0s".

Figure 29. BP\_ACK Encodings

The information bits encoding is described in Table 7.

**Table 7. Information Bit Encoding**

| Mode | Data 3                                                  | Data 2                                                    | Data 1                                                 | Data 0 | Description                                                                                                                                                                                               |

|------|---------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 1 = Backpressure<br>on high-priority<br>multicast cell. | 1 = Backpressure<br>on medium-priority<br>multicast cell. | 1 = Backpressure<br>on low-priority<br>multicast cell. | 0      | Backpressure information. This signal is present each cell time regardless of whether a cell was transmitted or not (on that link). This signal is withheld if any problem is detected on the input port. |

| 1    | 0                                                       | 0                                                         | 0                                                      | 0      | Unassigned.                                                                                                                                                                                               |

| 1    | 0                                                       | 1                                                         | 0                                                      | 0      | Signals MNACK.                                                                                                                                                                                            |

| 1    | 1                                                       | 0                                                         | 0                                                      | 0      | Signals ONACK.                                                                                                                                                                                            |

| 1    | 1                                                       | 1                                                         | 0                                                      | 0      | Signals ACK.                                                                                                                                                                                              |

## 3.2 Data Acknowledge

The data acknowledge signals (BP\_ACK\_IN and BP\_ACK\_OUT) are used to indicate if, at the current cell time, a cell was successfully transmitted or not. Data acknowledge is a single line per port that returns from a cell's destination in the reverse direction from the data flow. If the cell is being blocked by the switch, this information is generated directly by the QSE. If the cell is not being blocked by the switch, this information is forwarded from the next switch stage.

The data acknowledge signal provides the following information to the QRT:

- The cell was successfully received by the QRT at the cell destination (ACK).

- The cell was not accepted by the QRT at the cell destination (does not happen by design in the PM73487).

- The cell was blocked by the switch at the output of the switch fabric (refer to section 9.3.30 "ACK\_PAYLOAD" on page 109).

- The cell was blocked internal to the switch fabric (refer to section 9.3.30 "ACK\_PAYLOAD" on page 109).

- The cell was detected as a parity error cell by a QSE (refer to section 9.3.30 "ACK\_PAYLOAD" on page 109).

- The cell was headed to a gang of which all ports are dead (refer to section 9.3.31 "GANG\_DEAD\_ACK\_PAYLOAD" on page 110).

Thus, direct information is provided to the QRT on a per-cell basis and on a per-VC basis.

The QSE behavior to support the above scenario is as follows:

- If the cell was a parity errored cell, and the QSE is configured to check parity in the CHIP\_MODE register (refer to the field labeled "PARITY\_CHECK" on page 95), then the parity acknowledge in the ACK\_PAYLOAD register is sent (the default is ONACK).

- If the cell is dropped due to congestion at an output of the QSE, then Ack Payload for cells dropped due to congestion in the ACK\_PAYLOAD register is sent (bits3:0). Refer to bits 3:0 in section 9.3.31 "GANG\_DEAD\_ACK\_PAYLOAD" on page 110.

- If the cell was blocked at an output of the QSE because the entire gang is disabled (the default is ACK), then the cell is to be cleared when all ports to a QRT are known to be unavailable.

- If the cell was successfully routed through the QSE, the return path is set up to route the data-acknowledge signal back from the next switch stage.

For multicast traffic, the BP\_ACK\_IN and BP\_ACK\_OUT signals also serve as a backpressure signal, indicating at each cell time, the multicast cell priority the QSE can accept on the following cell time on a given port.

### 3.3 Microprocessor Interface

The QSE has a non-multiplexed, asynchronous, general-purpose microprocessor interface (PIF) through which the internal registers can be accessed. The external SSRAM is also indirectly accessed through this same interface.

### 3.4 Multicast SRAM Interface

The QSE supports 128 internal multicast groups, and is expandable up to 256K through an external SSRAM.

### 3.5 Clocks and Timing Signals

The QSE is driven from a single clock source up to a maximum clock rate of 66 MHz.

To indicate the SOC, there is one SE\_SOC\_IN signal per input port. There is one SE\_SOC\_OUT signal per group of four outputs.

Cells must arrive at the input ports within an eight clock-cycle window. A CELL\_START is used as a reference for an internal cell start signal to determine the eight clock-cycle window in which the SOC signal on the SE\_SOC\_IN lines are valid. The internal cell start signal delay from the external CELL\_START signal is programmed in the CELL START OFFSET (refer to section 9.3.28 "CELL START OFFSET" on page 109).

### 3.6 CTRL IN

CTRL\_IN is a one bit input port. Its function depends on the value of the "ENABLE\_STAT\_PINS" (bit 7) bit in the CHIP\_MODE register. When this bit is "0", CTRL\_IN directly sets the value of the internal "No Data Out" control bit. What this internal bit does is explained later. When this bit is "1", CTRL\_IN expects a data packet which sets the value of both, the internal "/No Data Out" and the "/No Data In" registers.

The format for the data packet is described below: