TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T C 9 3 0 9 A F

## SINGLE CHIP DTS MICROCONTROLLER (DTS-10)

The TC9309AF is a 4bit CMOS microcontroller for single chip digital tuning system with built-in prescaler, PLL and LCD driver.

The CPU has 4bit parallel addition/subtraction (AI, SI instructions, etc.) logical operation (OR, AN instructions, etc.) multiple bits judgment, comparison instructions (TM, SL instructions, etc.) and time base functions.

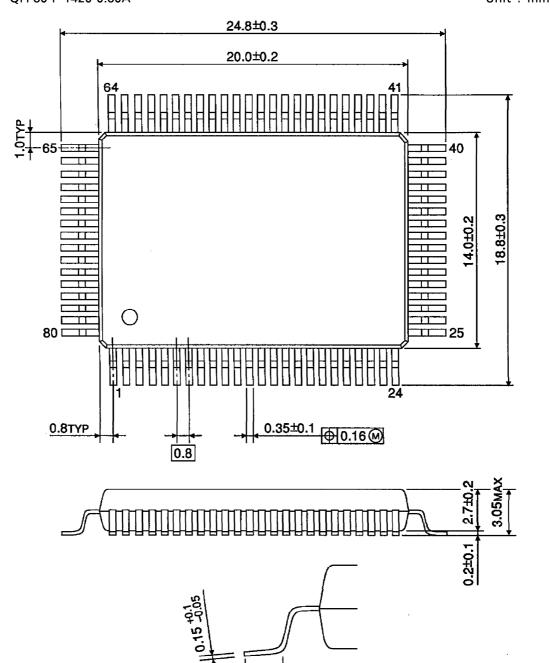

The TC9309AF is housed in as 80pin mini-flat package and is provided with ample I/O ports and exclusive key input ports which are controlled by powerful I/O instructions (IO, KEY instruction, etc.) and 1/2 duty and 1 /2 bias driving ample LCD use exclusive output terminals.

Weight: 1.57g (Typ.)

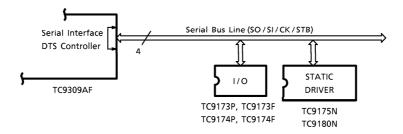

In addition, the TC9309AF has built in 2 modulus prescaler, PLL circuit, and IF counter that counts intermediate frequency (IF) in FM and AM bands for detecting broadcasting stations. Furthermore, the TC9309AF has built in serial bus control function (SIO instruction) to powerfully control peripheral ICs, 6bit A/D converter and D/A converter that are usable for field strength measurement and electronic volume control, and provides with many functions needed for digital tuning system.

#### **FEATURES**

- 4bit microcontroller single chip digital tuning system.

- $5V \pm 10\%$  single power supply, CMOS structure for low power dissipation.

- Built-in prescaler (Max. 140MHz signal is directly input in FM band), PLL and LCD driver (1/2 duty, 1/2 bias, frame frequency: 100Hz, 64 segments).

- Easy back up of data memory (RAM) and various ports (by the INH terminal).

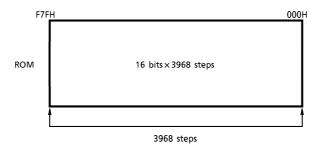

- Program memory (ROM): 16 bits x 3968 steps

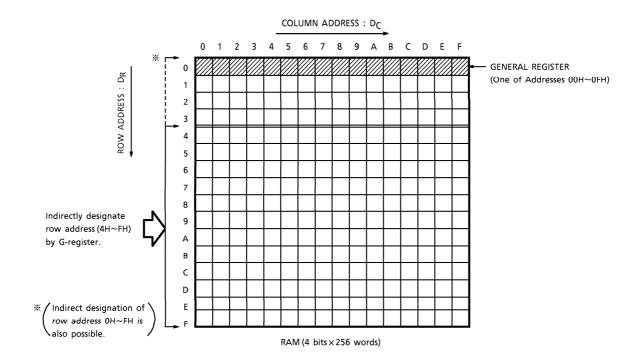

- Data memory (RAM) : 4 bits × 256 words

- 61 kinds of powerful instructions sets (all single word instructions)

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

- Instruction execution time 11.1 $\mu$ s (7.2MHz crystal connection)

- Abundant add and subtract instructions (Add instruction: 12, subtract instruction: 12)

- Powerful composite judging instructions (TMTR, TMFR, TMT, TMF instructions, etc.)

- Data transfer at the same row address is possible.

- Register indirect transfer is possible (MVGD, MVGS instructions)

- Powerful 16 general registers (arranged in RAM)

- Stack level: 2 levels

- Program memory (ROM) has no conception of page and field, and JUMP and CAL instructions can be freely contained in 3968 steps.

- Further, contents of 16bits data at any address in 1024 steps can be freely referred (DAL instruction)

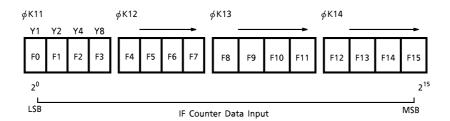

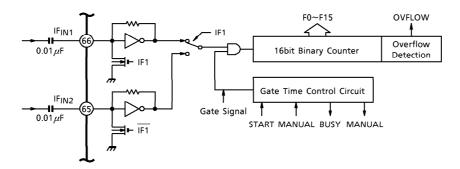

- Built-in 16bit general-use IF counter (IF<sub>IN1</sub>, IF<sub>IN2</sub>)

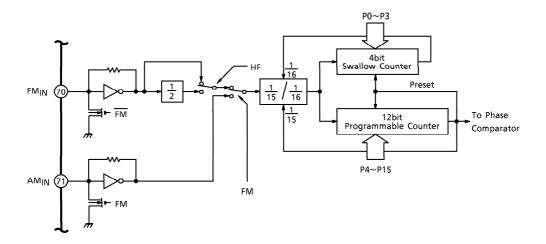

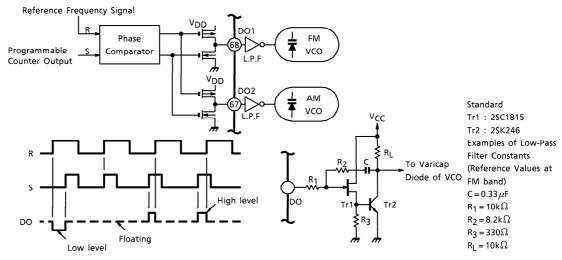

- Independent frequency input terminals for FM and AM (FM<sub>IN</sub>, AM<sub>IN</sub>), 2 phase comparator outputs (DO1, DO2)

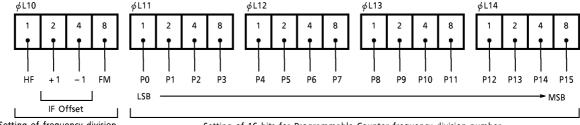

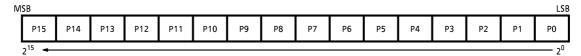

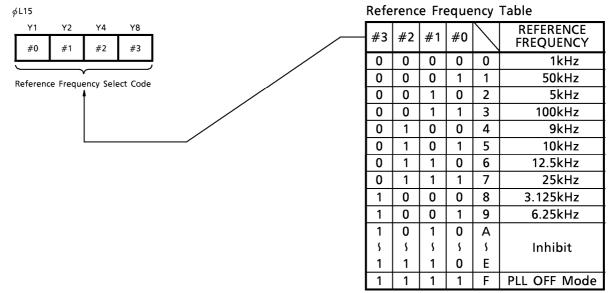

- 10 reference frequencies are programmable selectable (1, 3.125, 5, 6.25, 9, 10, 12.5, 25, 50, 100kHz)

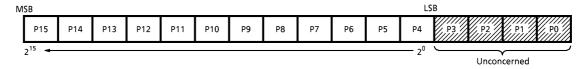

- Pulse swallow system and direct frequency division system are selectable by program according to receiving frequency band.

- IF correction at FM band is possible (Internal port for IF offset)

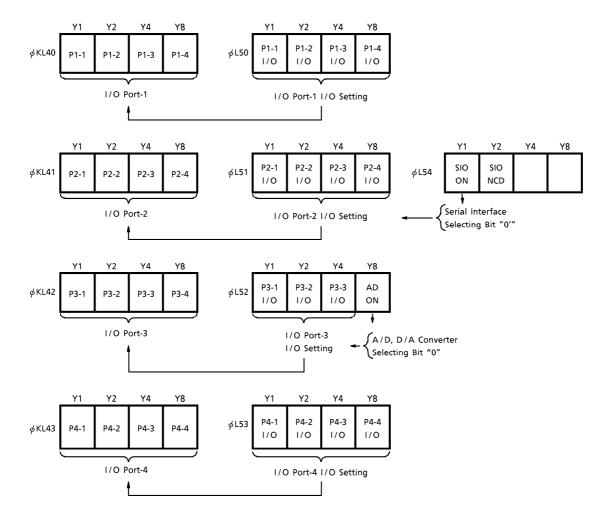

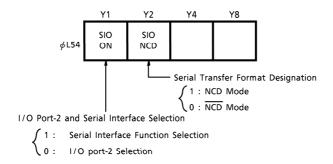

- Built-in powerful serial bus control function (I/O port-2 terminals are selectable by program.)

- Powerful I/O instructions (IO, KEY, SIO instruction, etc.)

- Exclusive key input port (K0~K3), abundant 32 terminals LCD driver.

- IF counter inputs (IF<sub>IN1</sub>, IF<sub>IN2</sub>) and input ports (IN1, IN2) are selectable by program.

- Max. 34 I/O ports (I/O settable ports: 15, output ports: 12, input ports: max. 7)

- Clock stop is possible by program (at CKTSP instruction : supply current below 10 μA)

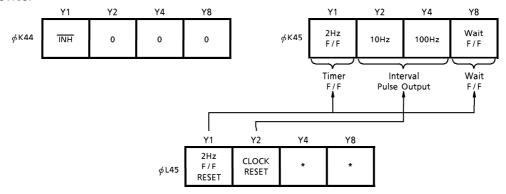

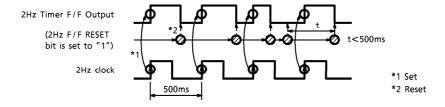

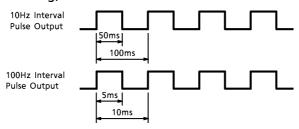

- Built-in 2Hz timer F/F, 10/100Hz internal pulse output (Internal port for time base)

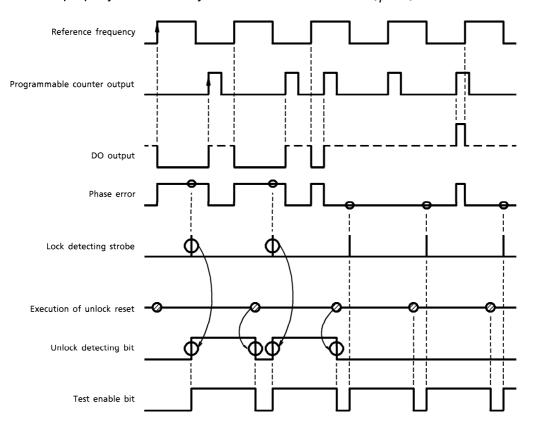

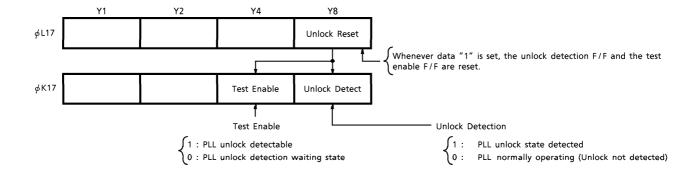

- Locked state of PLL is detectable (Internal port for PLL lock detection)

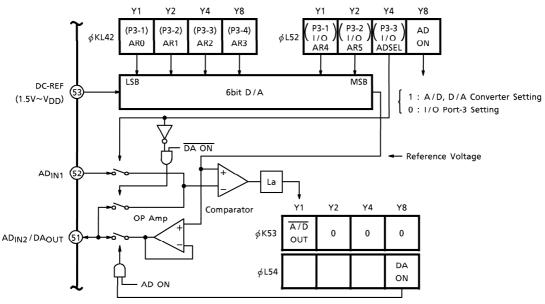

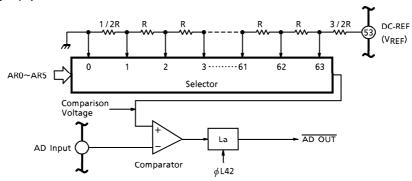

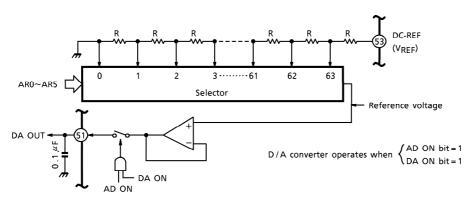

- Built-in 6bit A/D and D/A converters (Selectable by selecting I/O port-3 terminals (P3-1~P3-3) by program).

- OTP product : TC93P09F

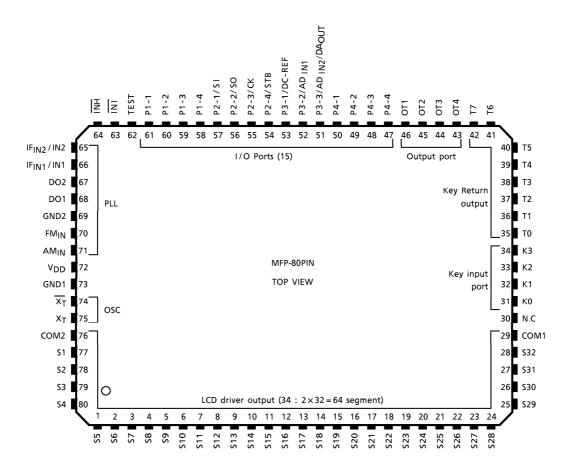

#### PIN CONNECTION

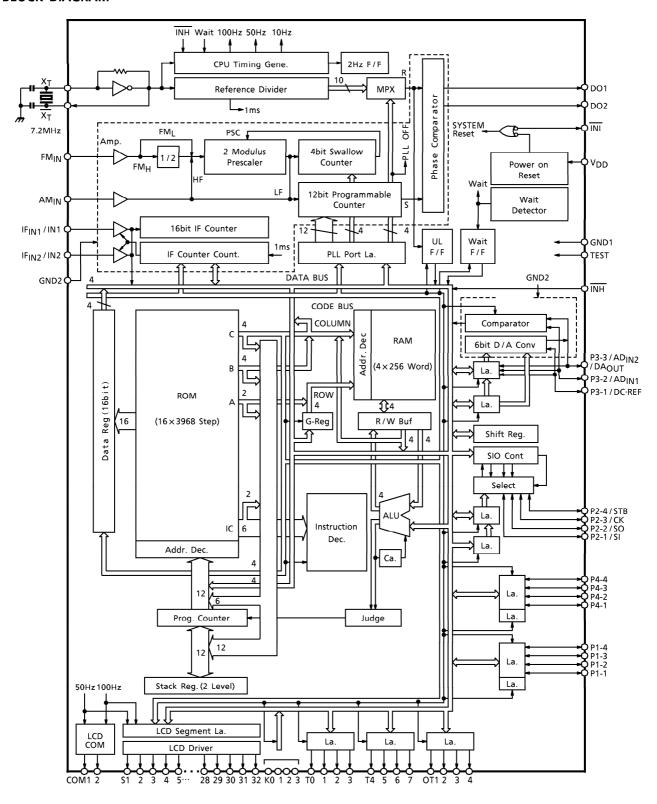

#### **BLOCK DIAGRAM**

## **PIN FUNCTION**

| PIN<br>No.    | SYMBOL              | PIN NAME              | FUNCTION / OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | REMARKS                                 |

|---------------|---------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

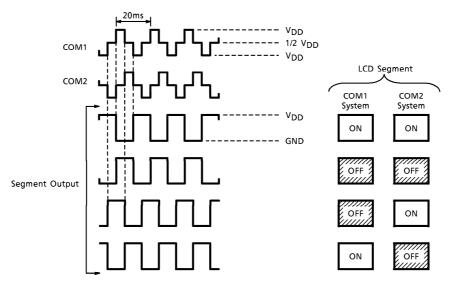

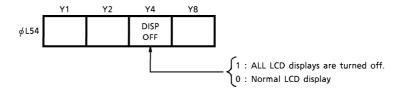

| 29<br>76      | COM1<br>COM2        | LCD Common<br>Output  | Common signal output terminals to LCD.  Maximum 64 segments can be displayed in a matrix with S1~S32.  Three levels of V <sub>DD</sub> , 1/2 V <sub>DD</sub> and GND are output to these terminals in a 50Hz cycle at intervals of 5ms.  (Note) At time of system reset and execution of CKSTP and DISP OFF, output is automatically fixed at "L" level.                                                                                                                                                | S P T T T T T T T T T T T T T T T T T T |

| 77~80<br>1~28 | \$1~\$4<br>\$5~\$32 | LCD Segment<br>Output | Segment signal output terminals to LCD.  Maximum 64 segments can be displayed in a matrix with COM1 and COM2.  Data are output to these terminals by executing SEG instruction (COM1 system) and MARK instruction (COM2 system).  As to segment decoding, it is possible to perform it by creating its decoding pattern in ROM area and using DAL command.  (Note) At time of system reset and execution of CKSTP command and DISP OFF, output is automatically fixed at "L" level.  (Refer to Note 3.) |                                         |

| 30            | N.C                 | No Connection         | As this terminal is not connected to internal chip, it can be left open or connected to GND or V <sub>DD</sub> freely. In case of OTP product TC93P09F, this terminal serves as V <sub>pp</sub> terminal and TC93P09F is readily usable when connected to V <sub>DD</sub> .                                                                                                                                                                                                                             | _                                       |

| 31~34         | K0∼K3               | Key Input Port        | 4bit input ports for key matrix input. When KEY instruction these ports specified in the operand is executed, data of these terminals are read in RAM. All terminals have built in pull-down resistors. Further, the output ports T0~T7 are normally used for key return timing signal.                                                                                                                                                                                                                 | V <sub>DD</sub>                         |

| PIN<br>No.     | SYMBOL                 | PIN NAME                       | FUNCTION / OPERATION                                                                                                                                                                                                                              | REMARKS         |

|----------------|------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

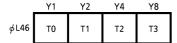

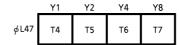

| 35~42          | то~т7                  | Key Timing<br>Output Port      | 4bit (T0~T3) and 4bit (T4~T7) output terminals. These ports are normally used for key return timing signal output of key matrix. (Refer to Notes 2 and 3.)                                                                                        |                 |

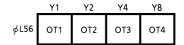

| 43~46          | OT4~OT1                | General-Purpose<br>Output Port | 4bit output ports.<br>(Refer to Notes 2 and 3.)                                                                                                                                                                                                   |                 |

| 47~50<br>58~61 | P4-4~P4-1<br>P1-4~P1-1 |                                | 4bit (P4-1~P4-4) and 4bit (P1-1~P1-4) I/O ports.  I/O designation for every bit can be made for these ports.  This designation is made according to contents of the internal ports called PORT4, PORT1 I/O CONTROL.  (Refer to Notes 1, 2 and 3.) | V <sub>DD</sub> |

| PIN<br>No.     | SYMBOL                                                        | PIN NAME                                                                                                            | FUNCTION / OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REMARKS                               |

|----------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 51<br>52<br>53 | P3-3<br>/ADIN2<br>/DAOUT<br>P3-2<br>/ADIN1<br>P3-1<br>/DC-REF | I/O Port 3 /AD Analog Voltage Input /DA Analog Voltage Output  /AD Analog Voltage Input  /Reference Voltage Input   | 3bit I/O ports.  I/O designation for every bit can be made for these ports.  This designation is made according to contents of the internal port called PORT-3  I/O CONTROL.  Further, these terminals also serve for the analog input of the built-in 2-channel A/D converter and analog output of 1-channel D/A converter.  A/D and D/A converter input/output selection is controlled according to contents of ADON, DAON or ADSEL bit.  The built-in A/D converter is of programmably sequential comparison type, and P3-1 is the reference voltage input, P3-2 is the analog comparison voltage input, and P3-3 is the analog comparison voltage input or analog voltage output.  (Note) A ladder resistance that generates internal D/A reference voltage is used commonly by the A/D and D/A converters.  When both the A/D and D/A converters are used simultaneously, DAON bit is set to "0" and D/A output is made to high impedance at time of A/D conversion.  It is therefore necessary to hold potential with a capacitor, etc.  (Refer to Notes 1, 2 and 3.) | V <sub>DD</sub> To AD or DA converter |

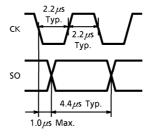

| 54~57          | P2-4/STB P2-3/CK P2-2/SO P2-1/SI                              | I/O Port 2<br>/Strobe Pulse<br>Output<br>/Serial Clock<br>Output<br>/Serial Data<br>Output<br>/Serial Data<br>Input | Abit I/O ports. I/O designation for every bit can be made for these ports. This designation is made according to contents of the internal port called PORT-2 I/O CONTROL. Further, these terminals are also used as the serial interface (SIO). Selection of SIO is controlled according to contents of SIO ON bit and in case of these serial interface, peripheral optional ICs can be controlled by executing SIO command. Serial transfer in NCD mode is programmably selectable. (Refer to Notes 1, 2 and 3.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |

| PIN<br>No. | SYMBOL | PIN NAME                   | FUNCTION / OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REMARKS         |

|------------|--------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 62         | TEST   | Test Mode<br>Control Input | Test mode control input terminal. The device is put in the test mode when "H" level signal is input and becomes the normal operating state when "L" level signal is input or in NC state. (A pull-down resistor has been built in.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>DD</sub> |

| 63         | ĪNĪ    | Initialize Input           | Device system reset signal input terminal. As long as the INI terminal is kept at "L" level, a system is kept in the reset state and when it becomes "H" level, a program startes from address 0.  Normally, the system is reset when 0~3.5V is supplied to the VDD terminal (Power ON Reset) and therefore, this terminal is used by fixing at "H" level.  (Note) After the system reset, I/O ports are set in the input mode.  However, the output state of output ports is indefinite and it is necessary to initialize them by program.                                                                                                                                                                                                                 |                 |

| 64         | ĪNĦ    | Inhibit Input<br>Terminal  | This is the INH port input terminal.  Normally, this terminal is used for radio mode selecting signal input or battery detection signal input.  When CKSTP instruction is used in a program and this CKSTP instruction is executed while the INH terminal is at "L" level, it is possible to stop the internal clock generator and CPU operation and put a system in the memory backup state with low current consumption (below 10μΑ).  (Note) CKSTP instruction is effective when the INH terminal is at "L" level and when this instruction is executed at "H" level, the same operation as NOOP instruction results.  (Note) In the radio OFF mode or back-up mode, it is necessary to set reference internal ports (4 bits) at all "1" (PLL OFF mode). |                 |

| PIN<br>No. | SYMBOL                                             | PIN NAME                                                                       | FUNCTION / OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REMARKS                |

|------------|----------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

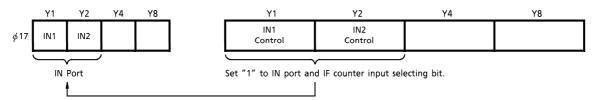

| 65<br>66   | IF <sub>IN2</sub> / IN2<br>IF <sub>IN1</sub> / IN1 | IF Signal<br>Input 2<br>/Input Port 2<br>IF Signal<br>Input 1<br>/Input Port 1 | IF signal input terminal of IF counter that detects auto stop by counting IF signal in FM and AM bands. Input frequency range is 0.1~20MHz (0.3Vp-p Min.) Having a built-in input amplifier, operates at small amplitude in C-connection. These terminals are usable programmably as input ports, and are selectable according to contents of the IN CONTROL Port. (Note) When IF counter is used, reference internal ports (4 bits) are set at all "1" or inputs that are not selected by IFIN1 bit (input selecting bit) are pulled down. (Refer to Note 1)                                                                      | R <sub>f1</sub><br>VDD |

| 67<br>68   | DO2<br>DO1                                         | Phase<br>Comparator<br>Output                                                  | PLL phase comparator output terminal.  Tri-state output.  If devided output signal from the programmable counter is higher than reference frequency, "H" level signal is output and if it is lower, "L" level signal is output and if matched, it becomes high impedance.  Signals from DO1 and DO2 are parallelly output.                                                                                                                                                                                                                                                                                                         | V <sub>DD</sub>        |

| 69         | GND2                                               | Analog GND<br>Terminal                                                         | GND terminal only for PLL, IF counter and AD/DA converter analog units.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                      |

| 70         | FMIN                                               | FM Band Signal<br>Input                                                        | Programmable counter input terminal for FM band.  The 1/2+pulse swallow system (FM <sub>H</sub> mode) and the pulse swallow system (FM <sub>L</sub> mode) are selectable by PLL instruction. In case of the pulse swallow system, local oscillation output (VCO output) of 10~140MHz (0.3V <sub>p-p</sub> Min.) is input and in case of 1/2 prescaler input, 10~185MHz (0.5V <sub>p-p</sub> Min.) is input.  Having a built-in input amplifier, operates at small amplitude with a capacitor connected.  (Note) When reference internal ports (4 bits) are set at all "1" or LF Mode or HF Mode is set, this input is pulled down. | Rf1                    |

| PIN<br>No. | SYMBOL          | PIN NAME                 | FUNCTION / OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REMARKS |

|------------|-----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

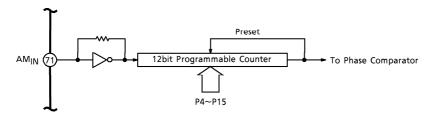

| 71         | AMIN            | AM Band Signal<br>Input  | Programmable counter input terminal for AM band.  The direct dividing system (LF mode) and the swallow system (HF mode) are freely selectable by PLL instruction.  In case of the direct dividing system (LF Mode), local oscillation output (VCO output) of 0.5~20MHz (0.3V <sub>p-p</sub> Min.) and in case of the pulse swallow system, 1~40MHz (0.3V <sub>p-p</sub> Min.) is input.  Having a built-in input amplifier, operates at small amplitude with a capacitor connected.  (Note) When reference internal ports (4 bits) are set at all "1" or FM <sub>H</sub> Mode or FM <sub>L</sub> Mode is set, this input is pulled down.                                                                                              | Rf1 VDD |

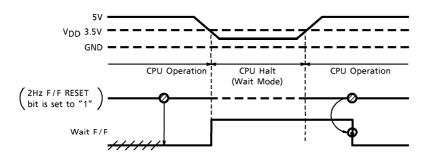

| 72         | V <sub>DD</sub> | Power Supply<br>Terminal | Power supply terminal.  At time of PLL operation, 5V ± 10% is applied.  In the back-up state (when executing CKSTP instruction), voltage can be reduced to 2V.  Further, when voltage drops below 3.5V during the operation of CPU, CPU stops (CPU Wait Mode) to prevent miss-function, it restarts when voltage increases above 3.5V.  As (Wait Mode) resulted under this condition can be detected by Wait F/F bit, perform initialization, clock correction, etc. by program.  Further, when 0 to 3.5V is applied to this terminal, a device is reset and a program starts from address 0 (power On Reset).  (Note) Rise time of supply voltage on a device shall be 10~100ms for the power ON reset operation.  (Refer to Note 1) |         |

| 73         | GND1            | Digital GND<br>Terminal  | GND terminal for CPU and the logic unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _       |

| PIN<br>No. | SYMBOL                           | PIN NAME                           | FUNCTION / OPERATION                                                                                                                                                                                                               | REMARKS                                       |

|------------|----------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 74<br>75   | X <sub>T</sub><br>X <sub>T</sub> | Crystal<br>Oscillation<br>Terminal | Crystal resonator connecting terminal. Connect a 7.2MHz crystal to this terminal. Adjust oscillation frequency (7.2MHz) while observing LCD segment waveform. When CKSTP instruction is executed, oscillation stops automatically. | X <sub>T</sub> V <sub>DD</sub> X <sub>T</sub> |

- (Note 1) When a device is reset (V<sub>DD</sub> = 0→3.5V and INI = "L"→"H"), I/O ports are set to the input, terminals serving as I/O ports and AD/DA converters are to the input of I/O ports, terminals serving as I/O ports and serial I/O ports are set to the input of I/O ports, and terminals serving as IF counter input and input port are set to IF counter input.

- (Note 2) When CKSTP instruction is executed, outputs of the output ports and I/O ports are all set at "L" level.

- (Note 3) When a device is reset, contents of output ports and internal ports are indefinite and it is therefore necessary to initialize them by program.

#### **DESCRIPTION OF OPERATION**

#### ○ CPU

The CPU consists of a program counter, stack register, ALU, program memory, data memory, G-register, data register, carry F/F, and judge circuit.

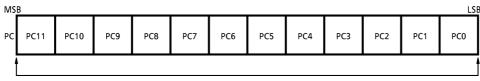

#### 1. Program counter (PC)

The program counter is a counter for addressing program memory (ROM) and consists of a 12bit binary up counter.

This counter is cleared by system resetting and a program starts from address 0.

Normally, whenever one instruction is executed, the count value is incremented by one.

When JUMP instruction or CAL instruction is executed, the address designated in the operand of that instruction is loaded.

Further, when an instruction having the skip function (AIS, SLT, TMT, RNS instructions, etc.) is executed and the result is a condition to be skipped, the program counter is incremented by two and skips next instruction.

12 bits

#### 2. Stack register (STACK)

This is a register consisting of  $2 \times 12$  bits and a value of the program content + 1, that is, return address is stored in this register when the subroutine call instruction is executed. The content of the stack register is loaded on the program counter when a return instruction (RN, RNS instruction) is executed.

The stack register has 2 stack levels and nesting is 2 levels.

#### 3. ALU

The ALU has the binary 4bit parallel addition and subtraction, logical operation, comparison and multiple bit judging functions.

Further, this CPU has no accumulator and contents of the data memory are directly treated in all operation.

#### 4. Program memory (ROM)

The program memory, consisting of 16 bits x 3968 steps, stores programs.

Usable address range is 3968 steps from address 000H to address F7FH.

The program memory has no concept of page and field, and JUMP and CAL instructions are freely usable in 3968 steps.

Further, it is possible to use any address of the program memory as data area and to load its contents in 16 bits in the data register by executing DAL instructions.

- (Note) Data area in the program memory shall be provided at address outside the program loop.

- (Note) Address in the program memory designatable as data area at time of DAL instruction execution is within 1024 steps from 000H to 3FFH.

#### 5. Data memory (RAM)

The date memory consists of 4 bits × 256 words and is used for data storage.

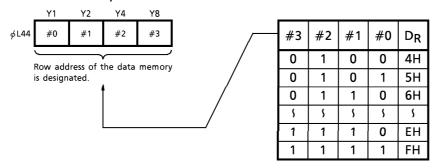

These 256 words are expressed by row address (4 bits) and column address (4 bits).

192 word (row address = 4H~FH) in the data memory are indirectly addressed by G-register.

Therefore, when data in this area are processed, it is necessary to perform the processing after designating row address in advance with G-register.

Further, address 00H ~0FH in the data memory are called the general register and usable only by designating column address (4 bits).

These 16 general registers can be used for operation and transfer with the data memory. In addition, it is also possible to use them as ordinary data memories.

- (Note) Column address (4 bits) designating a general register becomes Register No. of that general register.

- (Note) It is also possible to indirectly designate all row addresses (0H~FH) by G-register.

#### 6. G-Register (G-REG)

The G-register is a 4 bits register for addressing row addresses ( $D_R = 4H \sim FH$ ) of 192 words of the data memory.

Contents of this register becomes effective when MVGD/MVGS instruction is executed and have nothing to do with execution of other instructions.

This register is treated as one of ports and its contents are set when IO instruction is executed.

(Refer to Item 1 of Resister Ports.)

## 7. Data register (DATA REG)

This register consists of  $1 \times 16$  bits and 16bit data of any address  $000H\sim3FFFH$  of the program memory is loaded when DAL instruction is executed.

This register is treated as one of ports and its contents are read in 4 bits unit into the data memory when KEY instruction out of I/O instructions is executed. (Refer to Item 2 of Register Ports.)

## 8. Carry F/F (C.F/F)

This carry F/F is set when carry or borrow was generated as a result of execution of the calculation instruction and is reset when there is no carry nor borrow.

Contents of the carry F/F change only when the addition/subtraction instruction was executed and remain unchanged when other instructions were executed.

## 9. Judge circuit (J)

When any instruction having a skip function was executed, this circuit judges that skip condition. If the skip condition was satisfied, the program counter is incremented by two and skips a following instruction.

There are 29 instructions having the skip function.

(Refer to instructions with the \*mark on the List of Function and Operation of in Item 11)

#### 10. List of instructions sets

Total 61 instruction sets are available and they are all one word instruction.

These instruction are expressed in 6 bits instruction code.

| ILOW ~          | GH ORDER 2 BITS | 00        | 01        | 10                                   | 11                        |

|-----------------|-----------------|-----------|-----------|--------------------------------------|---------------------------|

| ORDER<br>4 BITS | 2 5113          | 0         | 1         | 2                                    | 3                         |

| 0000            | 0               | Al M, I   | AD r, M   |                                      | SLTI M, I                 |

| 0001            | 1               | AIS M, I  | ADS r, M  | CALL ADDR <sub>1</sub>               | SGEI M, I                 |

| 0010            | 2               | AIN M, I  | ADN r, M  | CALL ADDRI                           | SEQI M, I                 |

| 0011            | 3               | SI M, I   | SU r, M   |                                      | SNEI M, I                 |

| 0100            | 4               | SIS M, I  | SUS r, M  | MVSR M <sub>1</sub> , M <sub>2</sub> |                           |

| 0101            | 5               | SIN M, I  | SUN r, M  | MVIM M, I                            | HIMD ADDD.                |

| 0110            | 6               | LD r, M   | ORR r, M  | MVGD r, M                            | JUMP ADDR <sub>1</sub>    |

| 0111            | 7               | ST M, r   | ANDR r, M | MVGS M, r                            |                           |

| 1000            | 8               | AIC M, I  | AC r, M   | PLL M, C                             | TMTR r, M                 |

| 1001            | 9               | AICS M, I | ACS r, M  | SEG M, C                             | TMFR r, M                 |

| 1010            | Α               | AICN M, I | ACN r, M  | MARK M, C                            | TMT M, N                  |

| 1011            | В               | SIB M, I  | SB r, M   | IO M, C                              | TMF M, N                  |

| 1100            | С               | SIBS M, I | SBS r, M  | KEY M, C                             | TMTN M, N                 |

| 1101            | D               | SIBN M, I | SBN r, M  | SIO M, C                             | TMFN M, N                 |

| 1110            | E               | SEQ r, M  | ORIM M, I | XORIM M, I                           | DAL ADDR <sub>2</sub> , r |

| 1111            | F               | SNE r, M  | ANIM M, I | XORR r, M                            | RN, RNS,<br>CKSTP, NOOP   |

## 11.List of functions and operation of instructions

(Explanation of symbols on list)

M : Data Memory Address

Usually, one of data memory addresses 00H~3FH

r : General Register

One of data memory addresses 00H~0FH

PC : Program Counter (12 bits)

STACK : Stack Register (12 bits)

G : G-Register (4 bits)

DATA : Data Register (16 bits)

I : Immediate Data (4 bits)

N : Bit Position (4 bits)

— : ALL "0"

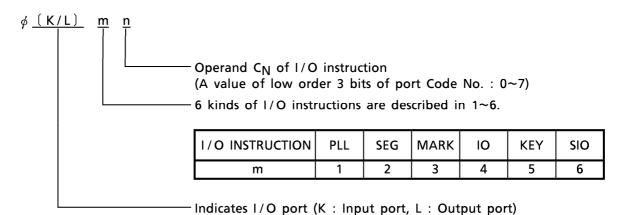

C : Port Code No. (4 bits)

$\mathsf{C}_\mathsf{N}$  : Low order 3 bits of Port Code No.

R<sub>N</sub> : General Register No. (4 bits)

ADDR<sub>1</sub> : Program Memory Address (12 bits)

ADDR<sub>2</sub> : High order 6 bits of Program Memory Address in Page 0.

Ca : Carry b : Borrow

PLL : Port treated by execution of PLL instruction

SEG : Port treated by execution of SEG instruction

MARK : Port treated by execution of MARK instruction

IO : Port treated by execution of IO instruction

KEY : Port treated by execution of KEY instruction

SIO : Port treated by execution of SIO instruction

: Contents of register or data memory

: Contents of port shown by Code No. C (4 bits)

: Contents of Data Memory shown by contents of Register or Data Memory

( ) P : Contents of Program Memory (16 bits)

IC : Instruction Code (6 bits)

\* : Instruction with skip function

D<sub>C</sub> : Data Memory Column Address (4 bits)

D<sub>R</sub> : Data Memory Row Address (2 bits)

| GR.                  |           | NO.              |                                                                       |                                       | MACHINE LANGUAGE (16bit) |                |                               |                |

|----------------------|-----------|------------------|-----------------------------------------------------------------------|---------------------------------------|--------------------------|----------------|-------------------------------|----------------|

| INST. G              | MNEMONIC  | SKIP<br>FUNCTION | EXPLANATION OF FUNCTION                                               | EXPLANATION OF OPERATION              | IC<br>(6bit)             | A<br>(2bit)    | B (4bit) DC DC DC DC DC DC DC | C<br>(4bit)    |

|                      | Al M, I   |                  | Add immediate data to memory                                          | M←(M) +I                              | 000000                   | D <sub>R</sub> | DC                            | I              |

|                      | AIS M, I  | *                | Add immediate data to memory, then skip if carry                      | M←(M) +1<br>Skip if carry             | 000001                   | D <sub>R</sub> | DC                            | I              |

|                      | AIN M, I  | *                | Add immediate data to memory, then skip if not carry                  | M←(M) +1<br>Skip if not carry         | 000010                   | D <sub>R</sub> | DC                            | I              |

|                      | AIC M, I  |                  | Add immediate data to memory with carry                               | M← (M) + I + ca                       | 001000                   | $D_{R}$        | DC                            | ı              |

|                      | AICS M, I | *                | Add immediate data to memory with carry, then skip if carry           | M←(M) +l+ca<br>Skip if carry          | 001001                   | D <sub>R</sub> | D <sub>C</sub>                | I              |

| UCTION               | AICN M, I | *                | Add immediate data<br>to memory with carry,<br>then skip if not carry | M←(M) +l+ca<br>Skip if not carry      | 001010                   | D <sub>R</sub> | DC                            | I              |

| INSTF                | AD r, M   |                  | Add memory to general register                                        | r←(r) + (M)                           | 010000                   | D <sub>R</sub> | DC                            | R <sub>N</sub> |

| ADDITION INSTRUCTION | ADS r, M  | *                | Add memory to general register, then skip if carry                    | r←(r) + (M)<br>Skip if carry          | 010001                   | D <sub>R</sub> | DC                            | R <sub>N</sub> |

| A                    | ADN r, M  | *                | Add memory to<br>general register, then<br>skip if not carry          | r←(r) + (M)<br>Skip if not carry      | 010010                   | D <sub>R</sub> | DC                            | R <sub>N</sub> |

|                      | AC r, M   |                  | Add memory to general register with carry                             | r←(r) + (M) + ca                      | 011000                   | D <sub>R</sub> | Dc                            | R <sub>N</sub> |

|                      | ACS r, M  | *                | Add memory to general register with carry, then skip if carry         | r←(r) + (M) + ca<br>Skip if carry     | 011001                   | D <sub>R</sub> | D <sub>C</sub>                | R <sub>N</sub> |

|                      | ACN r, M  | *                | Add memory to general register with carry, then skip if not carry     | r←(r) + (M) + ca<br>Skip if not carry | 011010                   | D <sub>R</sub> | DC                            | R <sub>N</sub> |

| GR.                     |           | NO               |                                                                                     |                                       | МАСН         | INE LAN        | GUAGE (                          | 16bit)         |

|-------------------------|-----------|------------------|-------------------------------------------------------------------------------------|---------------------------------------|--------------|----------------|----------------------------------|----------------|

| INST. G                 | MNEMONIC  | SKIP<br>FUNCTION | EXPLANATION OF FUNCTION                                                             | EXPLANATION OF<br>OPERATION           | IC<br>(6bit) | A<br>(2bit)    | B (4bit) DC DC DC DC DC DC DC DC | C<br>(4bit)    |

|                         | SI M, I   |                  | Subtract immediate data from memory                                                 | M← (M) – I                            | 000011       | D <sub>R</sub> | DC                               | I              |

|                         | SIS M, I  | *                | Subtract immediate data from memory, then skip if borrow                            | M←(M) - I<br>Skip if borrow           | 000100       | D <sub>R</sub> | DC                               | I              |

|                         | SIN M, I  | *                | Subtract immediate data from memory, then skip if not borrow                        | M←(M) -I<br>Skip if not borrow        | 000101       | D <sub>R</sub> | DC                               | I              |

|                         | SIB M, I  |                  | Subtract immediate data from memory, with borrow                                    | M← (M) – I – b                        | 001011       | D <sub>R</sub> | DC                               | I              |

| TION                    | SIBS M, I | *                | Subtract immediate data from memory with borrow, then skip if borrow                | M←(M) -I-b<br>Skip if borrow          | 001100       | D <sub>R</sub> | Dc                               | I              |

| SUBTRACTION INSTRUCTION | SIBN M, I | *                | Subtract immediate data from memory with borrow, then skip if not borrow            | M←(M) -I-b<br>Skip if not borrow      | 001101       | D <sub>R</sub> | DC                               | 1              |

| CTIO                    | SU r, M   |                  | Subtract memory from general register                                               | r←(r) – (M)                           | 010011       | D <sub>R</sub> | DC                               | R <sub>N</sub> |

| SUBTRA                  | SUS r, M  | *                | Subtract memory from general register, then skip if borrow                          | r←(r) - (M)<br>Skip if borrow         | 010100       | D <sub>R</sub> | DC                               | R <sub>N</sub> |

|                         | SUN r, M  | *                | Subtract memory from general register, then skip if not borrow                      | r←(r) - (M)<br>Skip if not borrow     | 010101       | D <sub>R</sub> | DC                               | R <sub>N</sub> |

|                         | SB r,M    |                  | Subtract memory from general register with borrow                                   | r←(r) - (M) - b                       | 011011       | D <sub>R</sub> | DC                               | R <sub>N</sub> |

|                         | SBS r, M  | *                | Subtract memory from<br>general register with<br>borrow, then skip if<br>borrow     | r←(r) - (M) - b<br>Skip if borrow     | 011100       | D <sub>R</sub> | DC                               | R <sub>N</sub> |

|                         | SBN r, M  | *                | Subtract memory from<br>general register with<br>borrow, then skip if<br>not borrow | r←(r) - (M) - b<br>Skip if not borrow | 011101       | D <sub>R</sub> | Dc                               | R <sub>N</sub> |

| GR.                    |        |                                 | N                |                                                                                         |                                          | МАСН         | INE LAN        | GUAGE (                                | 16bit)          |

|------------------------|--------|---------------------------------|------------------|-----------------------------------------------------------------------------------------|------------------------------------------|--------------|----------------|----------------------------------------|-----------------|

| INST. G                | MNEN   | /IONIC                          | SKIP<br>FUNCTION | EXPLANATION OF<br>FUNCTION                                                              | EXPLANATION OF<br>OPERATION              | IC<br>(6bit) | A<br>(2bit)    | B (4bit) DC | C<br>(4bit)     |

|                        | SLTI   | M, I                            | *                | Skip if memory is less than immediate data                                              | Skip if (M) <1                           | 110000       | D <sub>R</sub> | DC                                     | I               |

| NOI                    | SGEI   | M, I                            | *                | Skip if memory is greater than or equal to immediate data                               | Skip if (M) ≥ I                          | 110001       | D <sub>R</sub> | DC                                     | I               |

| COMPARISON INSTRUCTION | SEQI   | M, I                            | *                | Skip if memory is equal to immediate data                                               | Skip if (M) = I                          | 110010       | D <sub>R</sub> | DC                                     | I               |

| ARISON I               | SNEI   | M, I                            | *                | Skip if memory is not equal to immediate data                                           | Skip if (M) ≠ I                          | 110011       | D <sub>R</sub> | DC                                     | I               |

| COMP/                  | SEQ    | r, M                            | *                | Skip if general register is equal to memory                                             | Skip if (r) = (M)                        | 001110       | D <sub>R</sub> | DC                                     | R <sub>N</sub>  |

|                        | SNE    | r, M                            | *                | Skip if general register is not equal to memory                                         | Skip if (r) $\neq$ (M)                   | 001111       | D <sub>R</sub> | DC                                     | R <sub>N</sub>  |

|                        | LD     | r, M                            |                  | Load memory to general register                                                         | r← (M)                                   | 000110       | $D_{R}$        | DC                                     | R <sub>N</sub>  |

|                        | ST     | M, r                            |                  | Store general register to memory                                                        | M← (r)                                   | 000111       | D <sub>R</sub> | DC                                     | R <sub>N</sub>  |

| NSFER INSTRUCTION      | MVSR I | М <sub>1</sub> , М <sub>2</sub> |                  | Move memory to memory in the same row                                                   | $(D_R, D_{C1}) \leftarrow (D_R, D_{C2})$ | 100100       | D <sub>R</sub> | D <sub>C1</sub>                        | D <sub>C2</sub> |

| INSTE                  | MVIM   | M, I                            |                  | Move immediate data to memory                                                           | M←I                                      | 100101       | $D_{R}$        | DC                                     | I               |

| TRANSFER               | MVGD   | r, M                            |                  | Move memory to<br>destination memory<br>referring to G-register<br>and general register | ( (G) , (r) ) ← (M)                      | 100110       | D <sub>R</sub> | DC                                     | R <sub>N</sub>  |

|                        | MVGS   | M, r                            |                  | Move source memory referring to G-register and general register to memory               | M← ( (G) , (r) )                         | 100111       | D <sub>R</sub> | DC                                     | R <sub>N</sub>  |

| GR.                  |              |          | N<br>O           |                                                             |                                                     | МАСН                   | INE LAN        | GUAGE (        | (16l | oit)           |                |

|----------------------|--------------|----------|------------------|-------------------------------------------------------------|-----------------------------------------------------|------------------------|----------------|----------------|------|----------------|----------------|

| INST. G              | MNEM         | ONIC     | SKIP<br>FUNCTION | EXPLANATION OF FUNCTION                                     | EXPLANATION OF<br>OPERATION                         | IC<br>(6bit)           | A<br>(2bit)    | B<br>(4bit)    | (4   | C<br>4bit)     |                |

|                      | PLL          | PLL M, C |                  | Input PLL port data to memory                               | M← (PLL) C                                          | 101000                 | D <sub>R</sub> | DC             | 0    | c <sub>N</sub> |                |

|                      | 1            | 101, C   |                  | Output contents of memory to PLL port                       | ( PLL ) <b>C← (M)</b>                               | 101000                 | D <sub>R</sub> | DC             | 1    | c <sub>N</sub> |                |

|                      | SEG          | М, С     |                  | Input SEG port data to memory                               | M←(SEG) <sub>C</sub>                                | 101001                 | D <sub>R</sub> | DC             | 0    | c <sub>N</sub> |                |

| OUTPUT INSTRUCTION   | JLG          | IVI, C   |                  | Output contents of memory to SEG port                       | ( SEG ) <b>C</b> ←(M)                               | 101001                 | D <sub>R</sub> | DC             | 1    | c <sub>N</sub> |                |

| TRUC                 | MARK         | М, С     |                  | Input MARK port data to memory                              | M← ( MARK ) C                                       | 101010                 | D <sub>R</sub> | DC             | 0    | c <sub>N</sub> |                |

| NI TI                | - IVII-AICIC | IVI, C   | IVI, C           |                                                             | Output contents of memory to MARK port              | ( MARK ) <b>C</b> ←(M) | 101010         | D <sub>R</sub> | DC   | 1              | c <sub>N</sub> |

| UTPL                 | Ю            | М, С     |                  | Input IO port data to memory                                | M← ( IO ) C                                         | 101011                 | D <sub>R</sub> | DC             | 0    | c <sub>N</sub> |                |

| AND 0                |              | 101, C   |                  | Output contents of memory to IO port                        | ( IO ) C←(M)                                        | 101011                 | D <sub>R</sub> | DC             | 1    | c <sub>N</sub> |                |

| INPUT A              | KEY          | М, С     |                  | Input KEY port data to memory M← ( KEY ) C                  |                                                     | 101100                 | D <sub>R</sub> | DC             | 0    | c <sub>N</sub> |                |

| N N                  |              | IVI, C   |                  | Output contents of memory to KEY port                       | ( KEY ) <b>C</b> ←(M)                               | 101100                 | D <sub>R</sub> | D <sub>C</sub> | 1    | c <sub>N</sub> |                |

|                      | SIO          | М, С     | N4 C             |                                                             | Serial input port data of external device to memory | M←(SIO) <sub>C</sub>   | 101101         | D <sub>R</sub> | DC   | 0              | c <sub>N</sub> |

|                      | 310          | IVI, C   |                  | Serial output contents of memory to port of external device | (SIO) C←M                                           | 101101                 | D <sub>R</sub> | DC             | 1    | c <sub>N</sub> |                |

| NO N                 | ORR          | r, M     |                  | Logical OR of general register and memory                   | r← (r) ∨ (M)                                        | 010110                 | D <sub>R</sub> | DC             |      | R <sub>N</sub> |                |

| STRUCTION            | ANDR         | r, M     |                  | Logical AND of general register and memory                  | r← (r) ∧ (M)                                        | 010111                 | D <sub>R</sub> | DC             |      | R <sub>N</sub> |                |

| N INS                | ORIM         | М, І     |                  | Logical OR of memory and immediate data                     | M← (M) ∨ I                                          | 011110                 | $D_{R}$        | DC             |      | I              |                |

| LOGICAL OPERATION IN | ANIM         | М, І     |                  | Logical AND of<br>memory and<br>immediate data              | M← (M) ∧ I                                          | 011111                 | D <sub>R</sub> | DC             |      | 1              |                |

| CAL OP               | XORIM        | l M, I   |                  | Logical exclusive OR of memory and immediate data           | M← (M) ⊕ I                                          | 101110                 | D <sub>R</sub> | DC             |      | 1              |                |

| 1907                 | XORR         | r, M     |                  | Logical exclusive OR of general register and memory         | r←(r) ⊕ (M)                                         | 101111                 | D <sub>R</sub> | DC             |      | R <sub>N</sub> |                |

| GR.                    |                          | N<br>O           |                                                                                               |                                                        | MACH         | INE LAN                   | GUAGE (              | 16bit)         |

|------------------------|--------------------------|------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------|---------------------------|----------------------|----------------|

| INST. G                | MNEMONIC                 | SKIP<br>FUNCTION | EXPLANATION OF<br>FUNCTION                                                                    | EXPLANATION OF OPERATION                               | IC<br>(6bit) | A<br>(2bit)               | B<br>(4bit)          | C<br>(4bit)    |

|                        | TMTR r, M                | *                | Test general register bits by memory bits, then skip if all bits specified are true           | Skip if r ( N (M) )<br>= all "1"                       | 111000       | D <sub>R</sub>            | DC                   | R <sub>N</sub> |

| CTION                  | TMFR r, M                | *                | Test general register<br>bits by memory bits,<br>then skip if all bits<br>specified are false | Skip if r ( N (M) )<br>= all "0"                       | 111001       | D <sub>R</sub>            | DC                   | R <sub>N</sub> |

| JUDGE INSTRUCTION      | TMT M, N                 | *                | Test memory bits,<br>then skip if all bits<br>specified are true                              | Skip if M (N)<br>= all "1"                             | 111010       | D <sub>R</sub>            | DC                   | N              |

| BIT JUDG               | TMF M, N                 | *                | Test memory bits,<br>then skip if all bits<br>specified are false                             | Skip if M (N)<br>= all "0"                             | 111011       | D <sub>R</sub>            | DC                   | N              |

| 8                      | TMTN M, N                | *                | Test memory bits,<br>then not skip if all<br>bits specified are true                          | Skip if M (N)<br>= not all "1"                         | 111100       | D <sub>R</sub>            | DC                   | N              |

|                        | TMFN M, N                | *                | Test memory bits,<br>then not skip if all<br>bits specified are false                         | Skip if M (N)<br>= not all "0"                         | 111101       | D <sub>R</sub>            | DC                   | N              |

| TION                   | CAL ADDR <sub>1</sub>    |                  | Call subroutine                                                                               | $STACK \leftarrow (PC) + 1$ and $PC \leftarrow ADDR_1$ | 1000         | AD                        | DR <sub>1</sub> (12b | oit)           |

| UTINE                  | RN                       |                  | Return to main routine                                                                        | PC← (STACK)                                            | 111111       | 00                        | I                    | _              |

| SUBROUTINE INSTRUCTION | RNS                      | *                | Return to main routine and skip unconditionally                                               | PC← (STACK) and skip                                   | 111111       | 01                        | -                    | _              |

| JUMP<br>INSTRUCTION    | JUMP ADDR <sub>1</sub>   |                  | Jump to the address specified                                                                 | PC←ADDR <sub>1</sub>                                   | 1101         | ADDR <sub>1</sub> (12bit) |                      | oit)           |

| OTHER<br>INSTRUCTIONS  | DAL ADDR <sub>2,</sub> r |                  | Load program<br>memory in page 0 to<br>DATA register                                          | DATA← ( ADDR <sub>2</sub><br>+ (r) ) p in page 0       | 111110       | ADI<br>(6b                |                      | R <sub>N</sub> |

| OT                     | CKSTP                    |                  | Clock generator stop                                                                          | Stop clock generator if $\overline{\text{INH}} = "0"$  | 111111       | 10                        | _                    | _              |

| ے                      | NOOP                     |                  | No operation                                                                                  | _                                                      | 111111       | 11                        |                      | _              |

- (Note 1) When executing I/O instruction, input/output of the instruction is automatically controlled according to a value of the most significant bit of Port Code No. (C).

- MSB of Code No. (C) = "1" : Output instruction

- MSB of Code No. (C) = "0" : Input instruction

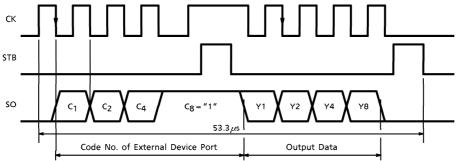

- (Note 2) Basically execution of SIO instruction is treated similar to execution of other I/O instructions (PLL instruction, SEG instruction, etc.) except the following points:

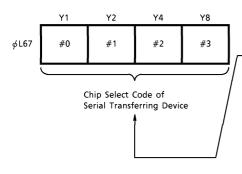

- First, it is necessary to select an external device that becomes a destination of transferring serial data by the chip select code ((C) = FH).

(Refer to Item 1 of Serial Interface.)

- SIO instruction execution time is 55.5  $\mu$ s (5 machine cycle).

- (Note 3) As the TC9309AF has no input port that is treated in the execution of SEG and MARK instructions, this input instruction cannot be used.

- (Note 4) Low order 4 bits out of the program memory address 10 bits designated by DAL instruction are to be indirectly addressed according to contents of the general register.

- DAL instruction execution time is  $22.2\mu s$  (2 machine cycle).

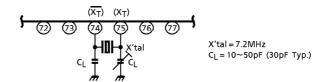

## O Connection of crystal resonator

Connect a 7.2MHz crystal resonator to the crystal oscillator terminal ( $X_T$ ,  $\overline{X_T}$  terminal) of a device as illustrated below. This oscillation signal is supplied to the clock generator and the reference frequency divider for generating various CPU timing signals and reference frequency signals. Adjust crystal oscillation frequency while monitoring segment output terminal.

(Note) Use a crystal resonator having a low CI value and good starting characteristic.

## O System reset

When "L" level signal is input to the  $\overline{\text{INI}}$  terminal or  $0\sim3.5\text{V}$  is supplied to the  $V_{DD}$  terminal (Power ON Reset), system reset is applied to a device. After 10ms of standby time passed after the system reset, a program starts from address 0.

Normally, as the Power ON reset function is used, the INI terminal shall be fixed at "H" level.

- (Note 1) During the system reset and subsequent standby time, LCD common output and segment output are fixed at "L" level.

- (Note 2) After the system reset, I/O ports are all set in the input mode.

However, no initialization of output ports and internal ports (G-Register, etc.) is performed. In particular, contents of these ports become indefinite when the power source is initially turned on and therefore, it becomes necessary to initialize them programmatically as necessary.

**TOSHIBA**

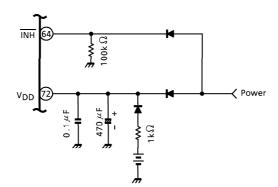

#### O Clock stop mode

If CKSTP instruction was executed when the  $\overline{\text{INH}}$  terminal is at "L" level, the clock generator and CPU in a device stop to operate completely and it becomes possible to get the memory back-up state with low current consumption (10 $\mu$ A Max. at V<sub>DD</sub> = 5V).

At this time, the LCD display output terminals and output ports are all fixed at "L" level automatically and programmatic process of the output terminals are not necessary. In this clock stop mode, supply voltage can be dropped to 2V.

In the clock stop mode, a program stops at the executing address of CKSTP instruction, the clock stop mode is released when the  $\overline{\text{INH}}$  terminal becomes "H" level and after 10ms of standby time passed, the instruction of next address is executed.

- (Note 1) In the clock stop mode, the output terminals are all fixed at "L" level but data immediately before the clock stop mode are kept in the contents of the output ports.

- (Note 2) If CKSTP instruction was executed during INH = "H" level, the same operation as NOOP instruction is carried out. (The system is not put in the clock stop mode.)

- (Note 3) ON/OFF of PLL circuit is performed according to contents of the reference port. It is therefore necessary to put a device in the PLL OFF mode (to set the reference port data "F") before CKSTP instruction is executed.

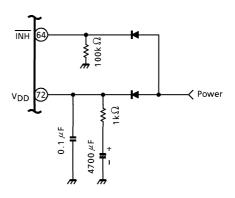

Example of Battery Back-Up Circuit

Example of Capacitor Back-Up Circuit

| FORTING CONTIER DATA   FORTING CONTIER DATA | O I/O PORT | ORT      |                |          | i      |          |               |        |   |               |      |            |            |             |            |            |       |                         |                |       |              |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|----------------|----------|--------|----------|---------------|--------|---|---------------|------|------------|------------|-------------|------------|------------|-------|-------------------------|----------------|-------|--------------|------------|

| Note of the contribution | - ~        | L-       | PLL (          | (ф1)     |        | SE       | (CC<br>(€2)   | Σ<br>Z |   | ⊿ARK          | COM2 |            |            | <u>o</u>    | (04)       |            |       | KE                      | (45)           |       | (9¢) OIS     | 6)         |

| FOUNTER DATA   FOUN |            | 7        | Y2             | 74       | У8     |          | -             |        |   |               | γ4   | γ8         | ۲1         | ۲2          | γ4         | ٧8         | ۲۱    | Y2                      | Υ4             | Y8    | ۲۱ ۲۷ ۲      | Y4 Y8      |

| FOUNTER DATA   FOUNTER COUNTER DATA   FOUNTER DATA   FOUNTER DATA   FOUNTER DATA   FOUNTER DATA   FOUNTER DATA   FOUNTER COUNTER DATA   FOUNTER DATA   FOU |            |          |                |          |        |          |               |        | _ |               |      |            |            | 1/0/        | PORT-1     |            |       |                         |                |       |              |            |

| FOOLINIER DATA   FOOLINIER DATA   FOOLINIER DATA   FOOLINIER DATA   FOOLINIER DATA   FOOLINIER DATA   FOOLINIER COUNTER COUN | _          |          | '              |          |        |          |               |        | _ |               |      |            | -1         | -2          | -3         | -4         |       |                         |                |       |              |            |

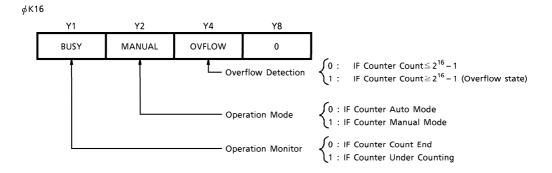

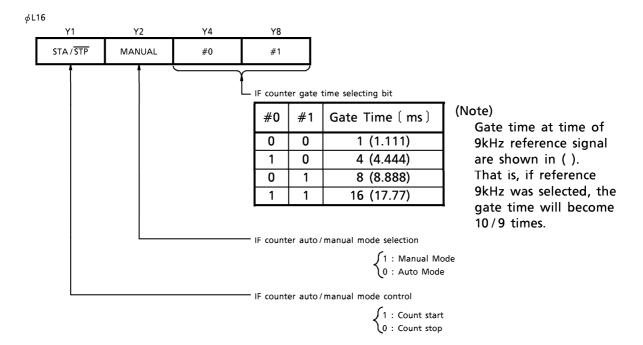

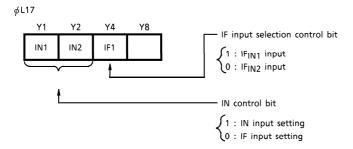

| FOO   FI   F2   F3   F6   F7   F2   F3   F4   F5   F6   F7   F7   F8   F9   F8   F9   F9   F9   F9   F9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 -        |          | IF COUNT       | TER DATA |        | -        |               |        |   |               |      |            |            | 1/0 }       | PORT-2     |            |       |                         |                |       |              |            |

| F COUNTER DATA   F COUNTER    | _          | 6        | E              | F2       | 33     | _        |               |        |   | _             |      |            | -1         | -2          | m<br>      | -4         |       |                         |                |       |              |            |

| F4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1          |          | IF COUNT       | TER DATA |        |          |               |        |   | _             |      |            | 1/0        | ORT-3/      | DA REF.    | DATA       |       | KEY                     | INPUT          |       | r - 1        |            |

| FE   F9   F10   F11   F12   F13   F14   F15   F15   F14   F15   F15   F14   F15    | $\sim$     | F4       | F5             | F6       | F7     |          |               |        |   |               |      | l          | -1<br>/AR0 | _2<br>/ AR1 | _3<br>/AR2 |            |       | 7                       | 2              | K3    |              |            |

| F8   F9   F10   F11   F14   F15   F15   F14   F15    | 1 0        |          | IF COUNT       | TER DATA |        |          | -             |        |   |               |      |            |            | 1/0/        | PORT-3     |            |       |                         | -              | _     | SERIAL INPUT | NPUT       |

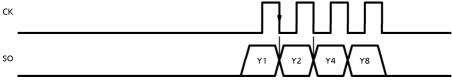

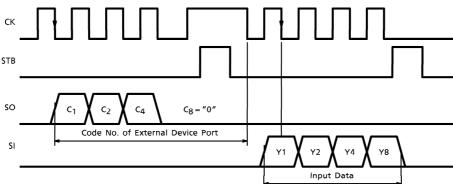

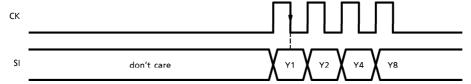

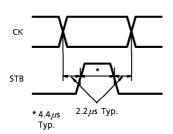

| F12   F13   F14   F15   F14   F15   F15   F14   F15  | n 1        | F8       | F9             | F10      | F11    |          | -             |        |   |               |      |            | -1         | 2           | -3         | <b>—</b> 4 | 2     | _                       | ,              | •     | CODE No. (C) | o. (C)     |