# **Oki Semiconductor** Z550 UART

0.5µm Technology Mega Macrocell for Universal Asynchronous Receiver/Transmitter

# DESCRIPTION

The Z550 UART Mega Macrocell is a featured library element in all of OKI's  $0.5\mu$ m Sea of Gates and  $0.5\mu$ m Customer Structured Array families. The OKI implementation of the mega macrocell is fully compatible with industry standard 16550 functions.

The Z550 UART Mega Macrocell is an Asynchronous Communication Element (ACE), functionally equivalent to the industry standard 16550 with 16 byte FIFOs available on both the transmitter and receiver. It serves as a serial I/O interface in microcomputer systems performing serial to parallel conversions on data characters received from peripheral devices or modems and parallel to serial conversions on data characters transmitted by the CPU. In FIFO mode, the FIFOs are enabled allowing 16 bytes of data to be stored during both transmit and receive operations. The receive FIFO also provides three bits per byte of error data. The status of the ACE can be read at any time by the CPU. Available information includes the type and condition of transfer operations being performed and error conditions involving parity, overrun, framing or break interrupt. The ACE includes a built in baud rate generator with 18 programmable baud rates.

# FEATURES

- Full double buffering

- Full status reporting

- 16 byte receive and transmit FIFOs reduce CPU interrupts

- Independent control of transmit, receive, line status data set interrupts and FIFOs

- Modem control signals include: CTS, DCD, DSR, DTR, RI, RTS

- Programmable serial interface characteristics:

- 5, 6, 7, or 8 bit characters

- odd, even, or no parity generation and detection

- 1, 1.5, or 2 stop bits

- Programmable Baud Rate Generator (dc to 56k baud)

- Unique OKI methodology for input timing analysis

- Tailored design flow and test procedure alleviates user from test vector generation to verify Z550 functionality

- Specially developed software merges OKI test vectors with the user's circuit

This Mega Macrocell Data Sheet contains all necessary information to enable the user to design a circuit using the Z550 functions for OKI's 0.5µm Sea of Gates and 0.5µm Customer Structured Array families.

# Supported ASIC Families

| Family Name | Family Type               |

|-------------|---------------------------|

| MSM13R0000  | Sea of Gates              |

| MSM98R000   | Customer Structured Array |

# Recommended Operating Conditions (V<sub>SS</sub> = 0 V)

|                       |                 | Rated value |     |     |       |

|-----------------------|-----------------|-------------|-----|-----|-------|

| Parameter             | Symbol          | Min         | Тур | Max | Units |

| Power supply voltage  | V <sub>DD</sub> | 2.7         | 3.3 | 3.6 | v     |

| Operating temperature | Тј              | -40         | +25 | +85 | °C    |

#### **Mega Macrocell characteristics**

| Mega<br>Macrocell | Description                           | Logic<br>Gate<br>Count | Used Core Raw<br>Gates | Number of<br>Mega<br>Macrocell Pins | Number<br>of Core<br>Rows <sup>[1]</sup> | Number of<br>Core<br>Columns <sup>[1]</sup> |

|-------------------|---------------------------------------|------------------------|------------------------|-------------------------------------|------------------------------------------|---------------------------------------------|

| Z550              | Asynchronous Communication<br>Element | 5392                   | 9519<br>(56.6%)        | 46                                  | 57                                       | 167                                         |

1. Row/Column values (aspect ratio) include margin for layout overhead external to the mega macrocell for interconnection of input/output pins and power buses.

|    | DI (0:7) | DO (0:7) |  |

|----|----------|----------|--|

|    | CS 0-1   | OE       |  |

| —c | CS2N     | DDIS     |  |

|    | A (0:2)  | DTR      |  |

| C  | ADSN     | RTS      |  |

|    | DIS      | OUT1     |  |

| C  | DISN     | OUT2     |  |

|    | DOS      | SOUT     |  |

| C  | DOSN     | INTR     |  |

|    | CLK      | BAUD     |  |

|    | MR       | TXRDY    |  |

|    | CTS      | RXRDY    |  |

|    | DSR      |          |  |

|    | RI       |          |  |

|    | DCD      |          |  |

|    | RCLK     |          |  |

|    | SIN      |          |  |

|    |          |          |  |

Figure 1. Logic Symbol

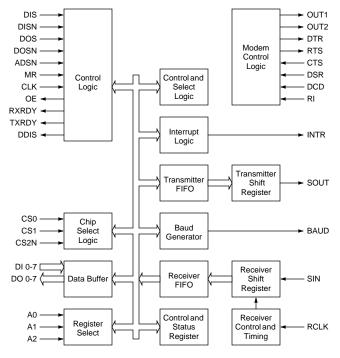

Figure 2. Block Diagram

3

# SIGNAL DESCRIPTIONS

| Signal Name            | Туре | Fan-In | Fan-Out<br>Max | Signal Description                                                                                                                                                                                                                                                                    |

|------------------------|------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DI 0-7                 | I    | 1      | -              | Data Input. Data Inputs 0-7 are used to transfer data and control information from the external system to the ACE. DI0 is the first data bit to be transferred.                                                                                                                       |

| CS 0-1, 2N             | I    | 1      | -              | Chip Select. The device is selected when CS0 and CS1 are high and CS2N is low.                                                                                                                                                                                                        |

| A 0-2                  | 1    | 1      | -              | Address. Address Lines 0-2 select the internal registers.                                                                                                                                                                                                                             |

| ADSN                   | I    | 1.6    | -              | Address Strobe. The state of the Chip Select and Address Lines are latched when ADSN is low.                                                                                                                                                                                          |

| DIS                    | I    | 1      | -              | Read Strobe. Data transfers from the ACE to the output data bus when DIS is high.                                                                                                                                                                                                     |

| DISN                   | 1    | 1      | -              | Read Strobe. Same as DIS but active low.                                                                                                                                                                                                                                              |

| DOS                    | I    | 1      | -              | Write Strobe. Data transfers from the input data bus to the ACE when DIS is high.                                                                                                                                                                                                     |

| DOSN                   | I    | 1      | -              | Write Strobe. Same as DOS but active low.                                                                                                                                                                                                                                             |

| CLK                    | I    | 1      | -              | Clock. Input for external timing reference.                                                                                                                                                                                                                                           |

| MR                     | I    | 1      | -              | Master Reset. A high level resets the device, forcing the ACE into an idle state<br>and suspends all data activity until programmed to resume. The MCR and its<br>output is cleared. The LSR is cleared except for the THRE and TEMT bits,<br>which are both sets.                    |

| CTS                    | I    | 1      | -              | Clear To Send. The state of CTS can be read from bit 4 (CTS) of the MSR. Bit<br>0 (DCTS) of the MSR is set if the CTS input changes state since the last time<br>the MSR was read. CTS low indicates to the ACE that data on SOUT can be<br>transmitted.                              |

| DSR                    | I    | 1      | -              | Data Send Ready. The state of DSR can be read from bit 5 (DSR) of the MSR.<br>Bit 1 (DDSR) of the MSR is set if the DSR input changes state since the last<br>time the MSR was read. DSR low indicates to the ACE that there is data ready<br>for it to receive.                      |

| RI                     | I    | 1      | -              | Ring Indicator. A low signal indicates that a telephone ringing signal has<br>been received by the modem. The state of RI can be read from bit 6 (RI) of the<br>MSR. Bit 2 (TERI) of the MSR is set if the RI input changes from high to low<br>since the last time the MSR was read. |

| DCD                    | I    | 1      | -              | Data Carrier Detect. The DCD signal indicates that the data carrier has been detected by the modem. The state of DCD can be read from bit 7 (DCD) of the MSR. Bit 3 (DDCD) of the MSR is set if the DCD input changed state since the last time the MSR is read.                      |

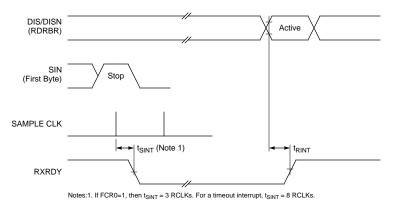

| RCLK                   | I    | 5      | -              | Receive Clock. This signal is an external input to the ACE's receiver logic (it is 16X the SIN data rate).                                                                                                                                                                            |

| SIN                    | I    | 2.5    | -              | Serial Input. The Serial Input receives serial data from the modem or other se-<br>rial data source into the ACE.                                                                                                                                                                     |

| DO 0-4<br>DO5<br>DO6-7 | 0    | -      | 16<br>19<br>16 | Data Output. Data Outputs 0-7 are used to transfer data and status informa-<br>tion from the ACE to your system. DI0 is the first data bit to be received.                                                                                                                            |

| OE                     | 0    | -      | 40             | Output Enable. This signal is a 3-state control used to configure the LSI pins of the ASIC for production testing.                                                                                                                                                                    |

| DDIS                   | 0    | -      | 15             | Driver Disable. The macrocell asserts this signal LOW while the system is reading data from the ACE.                                                                                                                                                                                  |

# SIGNAL DESCRIPTIONS(CONTINUED)

| Signal Name | Туре | Fan-In | Fan-Out<br>Max | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTR         | 0    | -      | 16             | Data Terminal Ready. The macrocell sets this signal LOW when a logic 1 has<br>bene written to bit 0 (DTR) of the MCR. This signal is set high when a logic 0<br>is written to bit 0 of the MCR or whenever a reset occurs. A low DTR indicates<br>that the ACE is ready to receive data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RTS         | 0    | -      | 16             | Request To Send. This signal is set low by writing a logic 1 to bit 1 of the MCR.<br>It is set high when a logic 0 is written to bit 1 of the MCR or whenever a reset<br>occurs. A low RTS signal indicates that the ACE has data ready to transmit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OUT1        | 0    | -      | 16             | Output 1. This output is set low by writing a logic 1 to bit 2 of the MCR, and set high by writing a logic 0 to bit 2 of the MCR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OUT2        | 0    | -      | 16             | Output 2. This output is set low by writing a logic 1 to bit 3 of the MCR, and set high by writing a logic 0 to bit 3 of the MCR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SOUT        | 0    | -      | 19             | Serial Data Out. This output is the serial data output of the ACE's transmitter circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

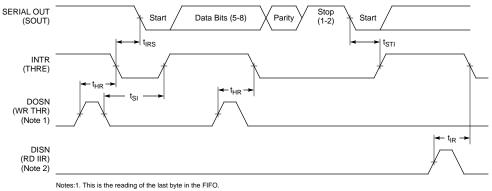

| INTR        | 0    | -      | 18             | Interrupt. The Interrupt output goes high whenever a Transmitter Holding<br>Register Empty, Received Data Available, Receiver Error Flag, Modem Status<br>condition or Trigger Charge Timeout (in FIFO mode) is detected and it is en-<br>abled in the IER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

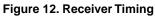

| BAUD        | 0    | -      | 15             | Baud Rate Out. This signal is the output of the internal Baud Rate Generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

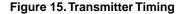

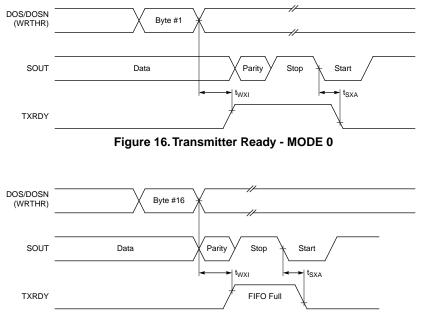

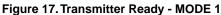

| TXRDY       | 0    | -      | 19             | Transmit Ready. this signal provides two types of DMA signaling selected by<br>bit 3 of the FCR when operating with the FIFO's enabled.<br>In mode 0 (bit 3 of the FCR = 0), TXRDY will be active (= 0) when the XMIT FIFO<br>and XMIT holding register contain no characters. TXRDY will go high when<br>the first character is loaded into the holding register of the XMIT FIFO. This<br>mode is normally used for single transfer DMA operation.<br>In mode 1 (bit 3 of the FCR = 1), TXRDY will be active (=0) when there are no<br>characters in the XMIT FIFO. TXRDY will go high when the XMIT FIFO is com-<br>pletely full. This mode is normally used when continual multiple transfers,<br>that fill the FIFO, are made.<br>NOTE: If the FIFO's are disabled (FIFO mode 0) only single DMA transfers are<br>allowed.    |

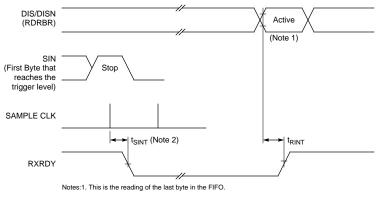

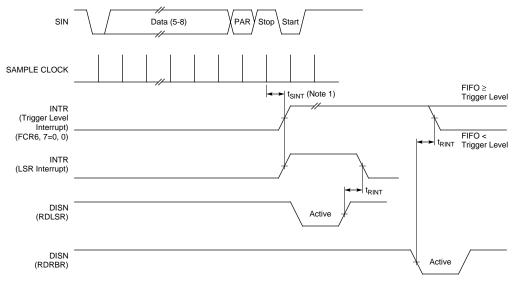

| RXRDY       | 0    | -      | 19             | Receiver Ready. this signal provides two types of DMA signaling selected by<br>bit 3 of the FCR when operating with the FIFO's enabled.<br>In mode 0 (bit 3 of the FCR = 0), RXRDY will be active (=0) when the RCVR<br>FIFO and RCVR holding register contain at least one characters. RXRDY will<br>go high when there are no more characters in the FIFO or holding register.<br>This mode is normally used for single transfer DMA operation.<br>In mode 1 (bit 3 of the FCR = 1), RXRDY will be active (=0) when the timeout<br>or trigger levels are reached. RXRDY will go high when the FIFO or holding<br>register is empty. This mode is normally used when continual multiple trans-<br>fers, that fill the FIFO, are made.<br>NOTE: If the FIFO's are disabled (FIFO mode 0) only single DMA transfers are<br>allowed. |

# FUNCTIONAL DESCRIPTION

## Registers

Three types of internal registers are used in the ACE. The three types are the Control, Status, and Data registers. The control registers are the Bit Rate Select Register DLL (Divisor Latch LSB) and DLM (Divisor Latch MSB), Line Control Register, Interrupt Enable Register, and the Modem Control Registers. The status registers are the Line Status Registers and the Modem Status Register. The data registers are the Receiver Buffer Register and the Transmitter Holding Register. The Address, Read, and Write inputs are used in conjunction with the Divisor Latch Access Bit in the Line Control Register [LCR(7)] to select the register to be written or read (see the table below). Individual bits within these registers are referred to by the register mnemonic and the bit number in parenthesis. As an example, LCR(7) refers to Line Control Register Bit 7.

# Serial Channel Internal Register<sup>[1]</sup><sup>[2]</sup>

| DLAB | A2 | A1 | A0 | Mnemonic Register |                                               |

|------|----|----|----|-------------------|-----------------------------------------------|

| 0    | 0  | 0  | 0  | RBR               | Receiver Buffer Register (read only)          |

| 0    | 0  | 0  | 0  | THR               | Transmitter Holding Register (write only)     |

| 0    | 0  | 0  | 1  | IER               | Interrupt Enable Register                     |

| х    | 0  | 1  | 0  | lir               | Interrupt Identification Register (read only) |

| Х    | 0  | 1  | 1  | LCR               | Line Control Register                         |

| Х    | 1  | 0  | 0  | MCR               | Modem Control Register                        |

| Х    | 1  | 0  | 1  | LSR               | Line Status Register                          |

| Х    | 1  | 1  | 0  | MSR               | Modem Status Register                         |

| Х    | 1  | 1  | 1  | SCR               | Scratch Register                              |

| 1    | 0  | 0  | 0  | DDL               | Divisor Latch (LSB)                           |

| 1    | 0  | 0  | 1  | DLM               | Divisor Latch (MSB)                           |

1. X = "Don't Care", 0 = Logic Low, 1 = Logic High.

2. The serial channel is accessed when -CS0 is low.

# Transmitter Buffer Register and Receiver Buffer Register

The Transmitter Buffer Register and Receiver Buffer Register are data registers that hold from five to eight bits of data. If less than eight data bits are transmitted, data is right justified to the LSB. Bit 0 of a data word is always the first serial data bit received and transmitted. The ACE data registers are double-buffered so that read and write operations may be performed when the UART is performing the parallel-to-serial or serial-to-parallel conversion.

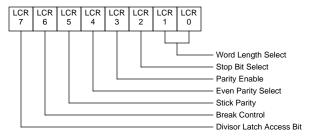

## Line Control Register

The format of the data character is controlled by the Line Control Register. The contents of the LCR may be read, eliminating the need for separate storage of the line characteristics in system memory. The contents of the LCR is shown in *Figure 3* and described in the following table.

# Line Control Register Description

| LCR Bit(s) | Description                                                                                        |                                     |                                |                                                |                                                                                                                                                  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LCR(0) and | Word length select bits. The number of bits in each serial character is programmed as shown below. |                                     |                                |                                                |                                                                                                                                                  |  |  |  |  |

| LCR(1)     |                                                                                                    | LCR(1)                              | LCR(0)                         | Word Length                                    | -                                                                                                                                                |  |  |  |  |

|            |                                                                                                    | 0                                   | 0                              | 5 data bits                                    | -                                                                                                                                                |  |  |  |  |

|            |                                                                                                    | 0                                   | 1                              | 6 data bits                                    |                                                                                                                                                  |  |  |  |  |

|            |                                                                                                    | 1                                   | 0                              | 7 data bits                                    |                                                                                                                                                  |  |  |  |  |

|            |                                                                                                    | 1                                   | 1                              | 8 data bits                                    | _                                                                                                                                                |  |  |  |  |

| LCR(2)     | one stop bit is generated. If L                                                                    | CR(2) is a logic<br>vhen either a 6 | c "1" when a<br>6, 7, or 8 bit | a 5 bit word length is<br>word length is seled | character. If LCR(2) is a logic "0",<br>selected, 1.5 stop bits are gener-<br>cted, two stop bits are generated.                                 |  |  |  |  |

| LCR(3)     | Parity Enable. When LCR(3) is checked.                                                             | s high, a parity                    | / bit betwee                   | n the last data word                           | bit and stop bit is generated and                                                                                                                |  |  |  |  |

| LCR(4)     | Even Parity Select. When pari even parity.                                                         | ty is enabled [                     | LCR(3) = 1],                   | LCR(4) = 0 selects of                          | odd parity, and LCR(4) = 1 selects                                                                                                               |  |  |  |  |

| LCR(5)     |                                                                                                    | from that indic                     | ated by LC                     | R(4). This allows par                          | smission and reception of a parity<br>ity to be forced to a known state                                                                          |  |  |  |  |

| LCR(6)     | state. The break is disabled by no effect on the transmitter lo                                    | y setting LCR(                      | 6) to a logic<br>ntrol enable  | "0". The Break Cont<br>s the CPU to alert a    | s forced to the spacing (logic "0")<br>rol bit acts only on SOUT and has<br>terminal in a computer communi-<br>ill be transmitted because of the |  |  |  |  |

|            | Load all "0"s (pad character) in response to THRE.                                                 |                                     |                                |                                                |                                                                                                                                                  |  |  |  |  |

|            | Set the break in response to the next THRE.                                                        |                                     |                                |                                                |                                                                                                                                                  |  |  |  |  |

|            | Wait for the transmitter to be                                                                     | e idle (TEMT =                      | 1), then clea                  | ar the break when no                           | rmal transmission is restored.                                                                                                                   |  |  |  |  |

| LCR(7)     |                                                                                                    | tor during read                     | d or write op                  | erations. LCR(7) mu                            | ess the Divisor Latches DLL and<br>st be set low (logic "0") to access<br>ers.                                                                   |  |  |  |  |

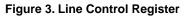

## Line Status Register

The Line Status Register (LSR) is a single register that provides status indications. The LSR is usually the first register read by the CPU to determine the cause of an interrupt or to poll the status the serial channel. The contents of the LSR is shown in *Figure 4* and described in the following table.

| Figure | 4        | l ine | Status | Register |

|--------|----------|-------|--------|----------|

| riguic | <b>-</b> | LINC  | olulus | Register |

| LSR Bit(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSR(0)     | Data Ready (DR). Data Ready is set high when an incoming character has been received and transferred into the Receiver Buffer Register. LSR(0) is reset low by a CPU read of the data in the Receiver Buffer Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LSR(1)     | Overrun Error (OE). Overrun Error indicates that data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register, overwriting the previous character. The OE indicator is reset whenever the CPU reads the contents of the Line Status Register. An overrun error will occur in the FIFO Mode after the FIFO is full and the next character is completely received. The overrun error is deleted by the CPU on the first LSR read after it happens. The character in the shift register is not transferred to the FIFO but it is overwritten.                                                                                                                                                                                                                                                                                                                 |

| LSR(2)     | Parity Error (PE). Parity Error indicates that the received data character does not have the correct parity, as selected by LCR(3) and LCR(4). The PE bit is set high upon detection of a parity error, and is reset low when the CPU reads the contents of the LSR.<br>In the FIFO Mode, the Parity Error is associated with a particular character in the FIFO. LCR(2) indicates the error when the character is at the top of the FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LSR(3)     | Framing Error (FE). Framing Error indicates that the received character did not have a valid stop bit. LSR(3) is set high when the stop bit following the last data bit or parity bit is detected to be a logic "0" (spacing level). The FE indicator is reset low when the CPU reads the contents of the LSR. In the FIFO Mode, the Framing Error is associated with a particular character in the FIFO. LCR(3) indicates the error when the character is at the top of the FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LSR(4)     | Break Interrupt (BI). Break Interrupt is set high when the received data input is held in the spacing (logic "0") state for a full word transmission time (start bit + data bits + parity + stop bits). The BI indicator is reset when the CPU reads the contents of the Line Status Register.<br>In the FIFO Mode, this is associated with a particular character in the FIFO. LCR(4) reflects the BI when the break character is at the top of the FIFO. The error is deleted by the CPU when its associated character is at the top of the FIFO during the first LSR read. Only one zero character is loaded into the FIFO when a BI occurs.<br>LSR(1)-LSR(4) are the error conditions that produce a Receiver Line Status interrupt [priority 1 interrupt in the Interrupt Identification Register (IIR)] when any of the conditions are detected. This interrupt is enabled by setting IER(2)=1 in the Interrupt Enable Register. |

#### Line Status Register Description (Continued)

| LSR Bit(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSR(5)     | THRE indicates that the ACE is ready to accept a new character for transmission. The THRE bit is set high when a character is transferred from the Transmitter Holding Roister into the Transmitter Shift Register. LSR(5) is reset low by the loading of the Transmitter Holding Register by the CPU. LSR(5) is not reset by a CPU read of the LSR. In FIFO Mode, when the XMIT FIFO is empty, this bit is set. It is cleared when one byte is written to the XMIT Fife.<br>When the THRE interrupt is enabled IER(1), THRE causes a priority 3 interrupt in the IIR. If THRE is the interrupt source indicated in IIR, INTR is cleared by a read of the IIR. |

| LSR(6)     | Transmitter Empty (TEMT). TEMT is set high when the Transmitter Holding Register (THR) and the Trans-<br>mitter Shift Register (TSR) are both empty. LSR(6) is reset low when a character is loaded into the THR and<br>remains low until the character is transferred out of SOUT. TEMT is not reset low by a CPU read of the LSR.<br>In the FIFO Mode, when both the transmitter FIFO and shift register are empty, this bit is set to one.                                                                                                                                                                                                                  |

| LSR(7)     | This bit is always 0 in the Z450 Mode. In FIFO Mode, it is set when at least one of the following data errors is in the FIFO: Parity Error, Framing Error or Break Interrupt indication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

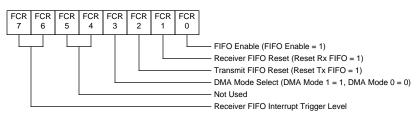

#### **FIFO Control Register**

The FIFO Control Register is a write only register at the same location as the IIR. It is used to enable and clear the FIFOs, set the trigger level of the RCVR FIFO, and select the type of DMA signaling.

Figure 5. FIFO Control Register

#### **FIFO Control Register Description**

| FCR Bit(s) | Description                                                                                                                                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCR(0)     | FIFO ENABLE. Enables both the XMIT and RCVR FIFOs. Programming of other FCR bits is enabled by set-<br>ting FCR(0)=1. The FIFOs operate in Z450 mode when FCR(0)=0. All bytes in both FIFOs can be cleared au-<br>tomatically from the FIFOs when changing from FIFO mode to Z450 mode and vice versa. |

| FCR(1)     | RCVR FIFO Reset. This bit clears all bytes in the RCVR FIFO and resets the counter logic to 0 when it is set to a one. It does not clear the receive shift register.                                                                                                                                   |

| FCR(2)     | XMIT FIFO Reset. This bit clears all bytes in the XMIT FIFO and resets the counter logic to 0 when it is set to a one. This does not clear the transmit shift register.                                                                                                                                |

| FCR Bit(s)    | Description                                                                                                                                                                                                                                                                 |             |                                        |                              |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------|------------------------------|--|--|--|

| FCR(3)        | DMA Mode Select. This bit controls the method of DMA signaling that will be used. If FCR(3)=1, the part will operate in Mode 1. It will be in Mode 0 if FCR(3)=0. These modes are only valid if FCR(0)=1. It directly affects the operation of the RXRDY and TXRDY outputs. |             |                                        |                              |  |  |  |

| FCR(4)-FCR(5) | These bits are not used.                                                                                                                                                                                                                                                    |             |                                        |                              |  |  |  |

| FCR(6)-FCR(7) | Rx FIFO Interrupt Trigger Level. These two bits are used to set the trigger level for the RCVR FIFO interrupt.                                                                                                                                                              |             |                                        |                              |  |  |  |

|               | KX FIFO Interrupt Trigger Level. These two bits a                                                                                                                                                                                                                           | are used to | set the trigger level                  | for the RCVR FIFO Interrupt. |  |  |  |

|               | FCR (7)                                                                                                                                                                                                                                                                     | FCR (6)     | Rx FIFO Trigger<br>Level (Bytes)       | —                            |  |  |  |

|               |                                                                                                                                                                                                                                                                             |             | Rx FIFO Trigger                        | —                            |  |  |  |

|               |                                                                                                                                                                                                                                                                             | FCR (6)     | Rx FIFO Trigger<br>Level (Bytes)       | —                            |  |  |  |

|               |                                                                                                                                                                                                                                                                             | FCR (6)     | Rx FIFO Trigger<br>Level (Bytes)<br>01 | —<br>—                       |  |  |  |

## **FIFO Control Register Description (Continued)**

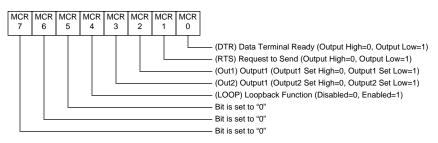

## **Modem Control Register**

The Modem Control Register (MCR) controls the interface with a modem or data set as shown in *Figure 6* and the following table. The MCR can be written and read. The RTS and DTR outputs are directly controlled by bits in this register. A high input asserts a low (true) at the output pins.

## Figure 6. Modem Control Register

#### Modem Control Register Description

| MCR Bit(s) | Bit Description                                                                                                   |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| MCR(0):    | When MCR(0) is set high, the DTR output is forced low. When MCR(0) is reset low, the DTR output is forced high.   |  |  |  |

| MCR(1):    | When MCR(1) is set high, the RTS output is forced low. When MCR(1) is reset low, the RTS output is forced high.   |  |  |  |

| MCR(2):    | When MCR(2) is set high, the OUT1 output is forced low. When MCR(2) is reset low, the OUT1 output is forced high. |  |  |  |

| MCR Bit(s)            | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MCR(3):               | When MCR(3) is set high, the OUT2 output is forced low. When MCR(3) is reset low, the OUT2 output is forced high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| MCR(4):               | MCR(4) provides a local loop back feature for diagnostic testing. When MCR(4) is set high, Serial Output (SOUT) is set to the marking (logic "1") state. The receiver data input, Serial Input (SIN) is disconnected and the output of the Transmitter Shift Register is looped back into the Receiver Shift Register input. The four modem control inputs (CTS, DSR, DCD, and RI) are disconnected. The four MCR bits DTR, RTS, OUT1, and OUT2 are internally connected to MSR(5), MSR(4), MSR(6), and MSR(7) in that order. The modem control output pins are forced to their inactive state (high). In the diagnostic mode, data transmitted is immediately received. This allows the processor to verify the transmit and receive data paths of the selected serial channel. Interrupt control is fully operational. However, interrupts are generated by controlling the lower four MCR bits internally. Interrupts are not generated by activity on the external pins represented by those four bus. |  |  |  |  |

| Bits MCR(5) - MCR(7): | Permanently set to logic "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

## Modem Control Register Description (Continued)

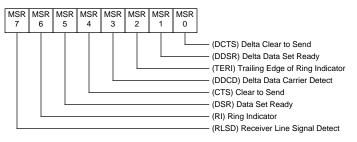

#### Modem Status Register

The Modem Status Register (MSR) provides the CPU with status of the modem input lines from modems or peripheral devices. The MSR allows the CPU to read the serial channel modem signal inputs by accessing the data bus interface of the ACE. In addition to the current status information, four bits of the MSR indicate whether the modem inputs have changed since the last reading of the MSR. The delta status bus are set high when a control input from the modem changes state, and reset low when the CPU reads the MSR.

The modem input lines are CTS, DSR, RI, and DCD. MSR(4) - MSR(7) are status indications of these lines. A status bit = 1 indicates the input is a low. A status bit = 0 indicates the input is high. If the modem status interrupt in the Interrupt Enable Register is enabled [IER(3)=1] an interrupt is generated whenever

MSR(0)-MSR(3) is set to a one. The MSR is a priority 4 interrupt. The contents of the Modem Status Register are described in *Figure 7* and the following table.

Figure 7. Modem Status Register

## Modem Status Register Description

| MSR Bit | Description                                                                                                                                                                                                                                                                                                             |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSR(0)  | Delta Clear to Send (DCTS): DCTS indicates that the CTS input to the serial channel has changed state since the last time it was read by the CPU                                                                                                                                                                        |

| MSR(1)  | Delta Data Set Ready (DDSR): DDSR indicates that the DSR input to the serial channel has changed state since the last time it was read by the CPU.                                                                                                                                                                      |

| MSR(2)  | Trailing Edge of Ring Indicator (TERI): TERI indicates that the RI input to the serial channel has changed state from high to low since the last time it was read by the CPU. Low to high transitions on RI do not activate TERI.                                                                                       |

| MSR(3)  | Delta Data Carrier Detect (DDCD): DDCD indicates that the DCD input to the serial channel has changed state since the last time it was read by the CPU.                                                                                                                                                                 |

| MSR(4)  | Clear to Send (CTS): CTS is the complement of the CTS input from the modem indicating to the serial channel that the modem is ready to receive data from the serial channel's transmitter output (SOUT). If the serial channel is in loop mode [MSR(4) = 1], MSR(4) is equivalent to the RTS value in the MCR.          |

| MSR(5)  | Data Set Ready (DSR): Data Set Ready (DSR) is the compliment of the DSR input from the modem to the serial channel which indicates that the modem is ready to provide data to the serial channel receiver circuitry. If the channel is in the loop mode [MCR(4) = 1], MSR(5) is equivalent to the DTR value in the MCR. |

| MSR(6)  | Ring indicator (RI): is the compliment of the RI input. If the channel is in the loop mode [MCR(4) = 1], MSR(6) is equivalent to the OUT1 value in the MCR.                                                                                                                                                             |

| MSR(7)  | MSR(7) Data Carrier Detect (DCD): Data Carrier Detect indicates the compliment of the Data Carrier Detect (DCD) input. If the channel is in the loop mode [MCR(4) = 1], MSR(7) is equivalent to OUT2 value in the MCR.                                                                                                  |

Reading the MSR Register will clear the delta modem status indications but has no effect on the other status bits.

For LSR and MSR, the setting of status bits is inhibited during status register read operations. If a status condition is generated during a read operation, the status bit is not set until the trailing edge of the read.

If a status bit is set during a read operation, and the same status condition occurs, that status bit will be cleared at the trailing edge of the read instead of being set again.

## Scratchpad Register

The Scratchpad Register is an 8-bit, Read/Write register that has no effect on either channel in the ACE. It is intended to be used by the programmer for temporarily data storage.

## Interrupt Identification Register

The Interrupt Identification Register (IIR) in the serial channel of the ACE provides interrupt interfacing capability. To minimize software overhead, the serial channel prioritizes interrupts into four levels. The four levels of interrupt conditions are:

#### **Interrupt Priorities**

| Interrupt Condition                | Priority |

|------------------------------------|----------|

| Receiver Line Status               | 1        |

| Received Data Ready                | 2        |

| Transmitter Holding Register Empty | 3        |

| Modem Status                       | 4        |

Information indicating that a prioritized interrupt is pending and the type of interrupt is stored in the Interrupt Identification Register (IIR). When addressed during chip select time, the IIR indicates the highest priority interrupt pending. No other interrupts are acknowledged until that interrupt is serviced by the CPU. The contents of the IIR is shown in the following tables.

## Interrupt Identification Register Bits

| IIR Bit(s)        | Bit Description                                                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|

| IIR(0)            | When IIR(0) is low, an interrupt is pending. When IIR(0) is high, no interrupt is pending.                                      |

| IIR(1) and IIR(2) | These two bits are used to identify the highest priority interrupt pending as indicated in the following table.                 |

| IIR(3)            | This bit is always logic "0" in Z450 Mode. In FIFO Mode, this bit is set along with IIR(2) when a timeout interrupt is pending. |

| IIR(4) and IIR(5) | These bits of the IIR are always logic "0".                                                                                     |

| IIR(6) and IIR(7) | FRC(0)=1 sets these bits to logic "1".                                                                                          |

## Interrupt Identification (IIR) Register Description

| FIFO<br>Mode<br>Only | Ir    | iterrupt l | dentifica | ation             |                            | Interrupt Set and Reset Functi                                                            | ons                                            |

|----------------------|-------|------------|-----------|-------------------|----------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------|

| Bit 3                | Bit 2 | Bit 1      | Bit 0     | Priority<br>Level | Interrupt Flag             | Interrupt Source                                                                          | Interrupt Reset Control                        |

| 0                    | 0     | 0          | 1         | -                 | None                       | None                                                                                      | -                                              |

| 0                    | 1     | 1          | 0         | First             | Receiver Line<br>Status    | OE, PE, FE, or BI                                                                         | LSR Read                                       |

| 0                    | 1     | 0          | 0         | Second            | Received Data<br>Available | Receiver data available for 450<br>or 550 mode, or trigger level<br>reached for FIFO mode | RBR read or FIFO drops below the trigger level |

| FIFO<br>Mode<br>Only | Ir    | iterrupt l | dentifica | ation             |                                    | Interrupt Set and Reset Functi                                                                                                                                                                                                                        | ons                      |

|----------------------|-------|------------|-----------|-------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Bit 3                | Bit 2 | Bit 1      | Bit 0     | Priority<br>Level | Interrupt Flag                     | Interrupt Source                                                                                                                                                                                                                                      | Interrupt Reset Control  |

| 1                    | 1     | 0          | 0         | Second            | Trigger Change<br>Level Indication | Minimum of one character in<br>the RCVR FIFO and no<br>character input or removed<br>during a time period<br>depending on how many<br>characters are in FIFO and<br>what the trigger level is set at<br>(3.5 to 4.5 character times <sup>[1]</sup> ). | RBR read                 |

| 0                    | 0     | 1          | 0         | Third             | THRE                               | THRE                                                                                                                                                                                                                                                  | Read of IIR or THR write |

| 0                    | 0     | 0          | 0         | Fourth            | Modem Status                       | CTS, DSR, RI, or DCD                                                                                                                                                                                                                                  | MSR read                 |

## Interrupt Identification (IIR) Register Description

1. The exact time will be [(word length) x 7 - 2] x 8 + [(trigger level - number of characters) x 8 + 1] RCLKs.

## Interrupt Enable Register

The Interrupt Enable Register (IER) is used to independently enable the four serial channel interrupts which activate the interrupt (INTR) output. All interrupts are disabled by resetting IER(0) - IER(3) of the Interrupt Enable Register to a logic "0". Interrupts are enabled by setting the appropriate bits of the IER high. Disabling the interrupt system inhibits the Interrupt Identification Register and the INTR output. All other system functions operate in their normal manner, including the setting of the Line Status and Modem Status Registers. The contents of the Interrupt Enable Register is described in the following table.

#### Interrupt Enable Register Bits

| IER Bit(s)       | Bit Description                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------|

| IER(0):          | When programmed high (IER(0) = Logic "1"), ERBFI enables the Received Data Available Interrupt.            |

| IER(1):          | When programmed high (IER(1) = Logic "1"), ETBEI enables the Transmitter Holding Register Empty Interrupt. |

| IER(2):          | When programmed high (IER(2) = Logic "1"), ELSI enables the Receiver Line Status Interrupt.                |

| IER(3):          | When programmed high (IER(3) = Logic "1"), EDSSI enables the Modem Status Interrupt.                       |

| IER(4) - IER(7): | These four bits of the IER are logic "0".                                                                  |

## **Baud Rate Generator**

The ACE serial channel contains a programmable Baud Rate Generator (BRG) that divides the clock (DC to 3.1 MHz) by any divisor from 1 to 216-1. The output of the Baud Rate Generator is referred to as RCLK. The frequency of RCLK 16x the data rate. The desired divisor is calculated by the following equation: [divisor = clock ÷ (baud rate x 16)]. Two 8-bit divisor latch registers store the divisor in a 16-bit binary format. These Divisor Latch registers must be loaded during initialization. Upon loading ether of the Divisor Latches, a 16-bit baud counter is immediately loaded. This prevents long counts on initial load. Setting DLL = 1 and DLM = 0 selects a divisor = 1 (dividing by 1 gives maximum baud rate for a given input frequency at the CLK input).

The BRG can use any of four different popular frequencies to provide standard baud rates. These frequencies are 1.8432 MHz, 2.4576 MHz, 3.072 MHz, and 8 MHz. The following tables illustrate the divisors needed to obtain standard bit rates from 50 to 256k bps using these three clock frequencies.

| Desired BAUD Rate | Divisor Used | Percent Error Difference<br>Between Desired and Actual |

|-------------------|--------------|--------------------------------------------------------|

| 50                | 2304         | -                                                      |

| 75                | 1536         | -                                                      |

| 110               | 1047         | 0.026                                                  |

| 134.5             | 857          | 0.058                                                  |

| 150               | 768          | -                                                      |

| 300               | 384          | -                                                      |

| 600               | 192          | -                                                      |

| 1200              | 96           | -                                                      |

| 1800              | 64           | -                                                      |

| 2000              | 58           | 0.69                                                   |

| 2400              | 48           | -                                                      |

| 3600              | 32           | -                                                      |

| 4800              | 24           | -                                                      |

| 7200              | 16           | -                                                      |

| 9600              | 12           | -                                                      |

| 19200             | 6            | -                                                      |

| 38400             | 3            | -                                                      |

| 56000             | 2            | 2.86                                                   |

#### BAUD Rates (1.8432 MHz Clock)

#### BAUD Rates (2.4576 MHz Clock)

| Desired BAUD Rate | Divisor Used | Percent Error Difference<br>Between Desired and Actual |

|-------------------|--------------|--------------------------------------------------------|

| 50                | 3072         | -                                                      |

| 75                | 2048         | -                                                      |

| 110               | 1396         | 0.026                                                  |

| 134.5             | 1142         | 0.0007                                                 |

| 150               | 1024         | -                                                      |

| 300               | 512          | -                                                      |

| 600               | 256          | -                                                      |

| 1200              | 128          | -                                                      |

| 1800              | 85           | 0.392                                                  |

| 2000              | 77           | 0.260                                                  |

| 2400              | 64           | +                                                      |

| 3600              | 43           | 0.775                                                  |

| 4800              | 32           | -                                                      |

| 7200              | 21           | 1.587                                                  |

| 9600              | 16           | -                                                      |

| 19200             | 8            | -                                                      |

| 38400             | 4            | -                                                      |

| Desired BAUD Rate | Divisor Used | Percent Error Difference<br>Between Desired and Actual |

|-------------------|--------------|--------------------------------------------------------|

| 50                | 3840         | -                                                      |

| 75                | 2560         | -                                                      |

| 110               | 1745         | 0.026                                                  |

| 134.5             | 1428         | 0.034                                                  |

| 150               | 1280         | -                                                      |

| 300               | 640          | -                                                      |

| 600               | 320          | -                                                      |

| 1200              | 160          | -                                                      |

| 1800              | 107          | 0.312                                                  |

| 2000              | 96           | -                                                      |

| 2400              | 80           | -                                                      |

| 3600              | 53           | 0.628                                                  |

| 4800              | 40           | -                                                      |

| 7200              | 27           | 1.23                                                   |

| 9600              | 20           | -                                                      |

| 19200             | 10           | -                                                      |

| 38400             | 5            | -                                                      |

#### BAUD Rates (3.072 MHz Clock)

## **BAUD Rates (8 MHz Clock)**

| Desired BAUD Rate | Divisor Used to<br>Generate 16x Clock | Percent Error Difference<br>Between Desired and Actual |  |

|-------------------|---------------------------------------|--------------------------------------------------------|--|

| 50                | 1000                                  | _                                                      |  |

| 75                | 6667                                  | 0.005                                                  |  |

| 110               | 4545                                  | 0.010                                                  |  |

| 134.5             | 3717                                  | 0.013                                                  |  |

| 150               | 3333                                  | 0.010                                                  |  |

| 300               | 1667                                  | 0.020                                                  |  |

| 600               | 833                                   | 0.040                                                  |  |

| 1200              | 417                                   | 0.080                                                  |  |

| 1800              | 277                                   | 0.080                                                  |  |

| 2000              | 250                                   | -                                                      |  |

| 2400              | 208                                   | 0.160                                                  |  |

| 3600              | 139                                   | 0.080                                                  |  |

| 4800              | 104                                   | 0.160                                                  |  |

| 7200              | 69                                    | 0.644                                                  |  |

| 9600              | 52                                    | 0.160                                                  |  |

| 19200             | 26                                    | 0.160                                                  |  |

| 38400             | 13                                    | 0.160                                                  |  |

| 56000             | 9                                     | 0.790                                                  |  |

| 128000            | 4                                     | 2.344                                                  |  |

| 256000            | 2                                     | 2.344                                                  |  |

## **Master Reset**

After power up, the ACE MR input should be held high to reset the ACE to an idle mode. A high, logic "1", on MR causes the following:

1. Initializes the transmitter and receiver internal clock counters.

2. Clears the Line Status Register (LSR), except for Transmitter Shift Register Empty (TEMT) and Transmit Holding Register Empty (THRE), which are set. When interrupts are subsequently enabled, an interrupt occurs due to THRE. The Modem Control Register (MCR) is also cleared. All of the discrete lines, memory elements and miscellaneous logic associated with these register bits are also cleared or turned off. The Line Control Register (LCR), Divisor Latches, Receiver Buffer Register, and Transmitter Buffer Register are not effected.

A summary of the effect of a reset on the ACE is given in the table below.

Following removal of the reset condition (MR low), the ACE remains in the idle mode until programmed.

| Register/Signal                      | Reset Control            | Reset                                                          |  |

|--------------------------------------|--------------------------|----------------------------------------------------------------|--|

| Interrupt Enable Register            | Reset                    | All bits low (0-3 forced and 4-7 permanent)                    |  |

| Interrupt Identification<br>Register | Reset                    | Bit 0 is high, Bits 1 and 2 low, Bits 3-7 are permanently low. |  |

| Line Control Register                | Reset                    | All bits low.                                                  |  |

| MODEM Control Register               | Reset                    | All bits low.                                                  |  |

| Line Status Register                 | Reset                    | All bits low, except bits 5 and 6.                             |  |

| MODEM Status Register                | Reset                    | Bits 0-3 low, Bits 4-7 input signal.                           |  |

| SOUT                                 | Reset                    | High                                                           |  |

| Interrupt (RCVR Errs)                | Read LSR/Reset           | Low                                                            |  |

| Interrupt (RCVR Data Ready)          | Read RBR/Reset           | Low                                                            |  |

| Interrupt (THRE)                     | Read IIR/Write THR/Reset | Low                                                            |  |