# HD66350T (TFT Driver)

## 256-level Grayscale TFT for XGA/SXGA/UXGA Systems

# HITACHI

ADE-207-297(Z) Preliminary Rev.0.6 December 1998

#### Description

The HD66350T is a TFT-LCD source driver LSI suitable for XGA, SXGA, and UXGA systems. It receives 8-bit-per-pixel digital display data, and generates and outputs voltages for 256 grayscales. The output circuit includes an operational amplifier, and is capable of alternate output of 256 positive-polarity grayscale voltages and 256 negative-polarity grayscale voltages on individual output pins (dot inversion drive).

Users can select 384 or 402 outputs. For XGA and SXGA, respectively, eight and ten 384-output LSIs are used. For UXGA, twelve 402-output LSIs are used.

#### Features

- High-speed operation

- Operating clock: 65 MHz (Vcc = 3.0 to 3.6 V) and 50 MHz (Vcc = 2.5 to 3.0 V)

- Operational power-supply voltage range

- ---  $V_{CC} = 2.5$  to 3.6 V ---  $V_{LCD} = 10$  to 15.5 V

- LCD drive voltage

- Low-voltage side: 0.1 to  $V_{LCD}/2 0.2$  (V)

- High-voltage side:  $V_{LCD}/2 + 0.2$  to  $V_{LCD} 0.1$  (V)

- LCD drive outputs

- 384/402 outputs can be selected: Eight 384-output LSIs for XGA, Ten 384-output LSIs for SXGA, and Twelve 402-output LSIs for UXGA

- Data inversion function

- Each port has a data inversion pin (a total of two pins), which reduces the power consumption of the data buses.

- Multicolor display

- The HD66350T receives 8-bit-per-pixel digital display data, and selects and outputs a display voltage from 256 grayscale voltages, enabling a maximum of 16,770,000 display colors (full colors) when using R/G/B color filters.

- 48 data bits (8 grayscale code bits × RGB × 2 ports)

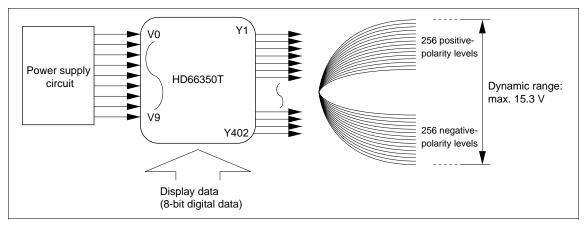

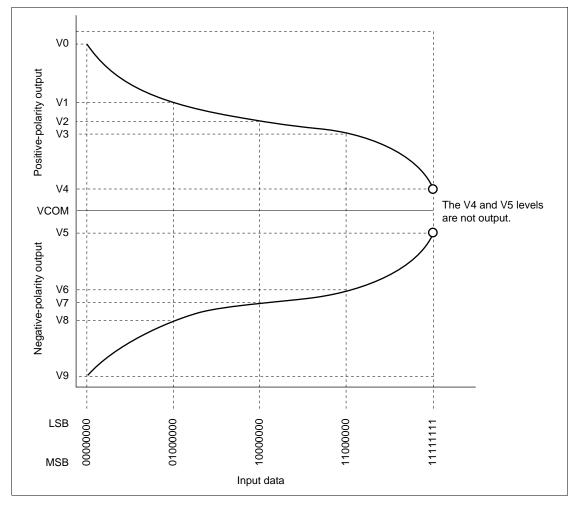

- High-voltage asymmetric drive

- The wide dynamic range of 15.3 V and the ability to output positive-polarity and negative-polarity voltages make it unnecessary to provide a counter-electrode alternating current. Also, since both positive-polarity and negative-polarity voltages are generated by an externally provided reference power supply, gamma compensation is possible according to the characteristics of the liquid crystal.

- Dot inversion drive

- The voltage can be alternated between positive polarity and negative polarity on individual output pins, allowing a dot-by-dot inversion drive even with a single-sided layout configuration. This provides a high-quality display with little crosstalk.

- Low-output voltage deviation of ±3 mV

- Operational amplifier

- The output circuit includes an operational amplifier.

- Bidirectional shift

- Package

TCP (customized package dimensions)

- Supported systems

XGA (1024 × 768 dots), SXGA (1280 × 1024 dots), and UXGA (1600 × 1200 dots)

- Applications

- Portable PCs and monitors

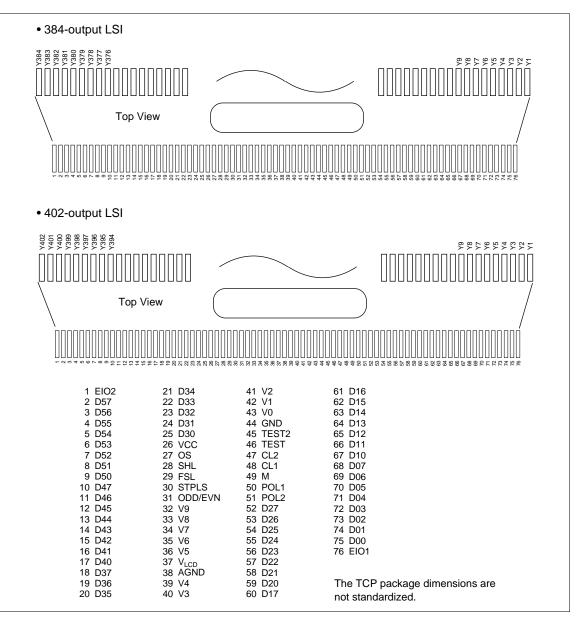

#### **Pin Arrangement**

Figure 1 Pin Arrangement

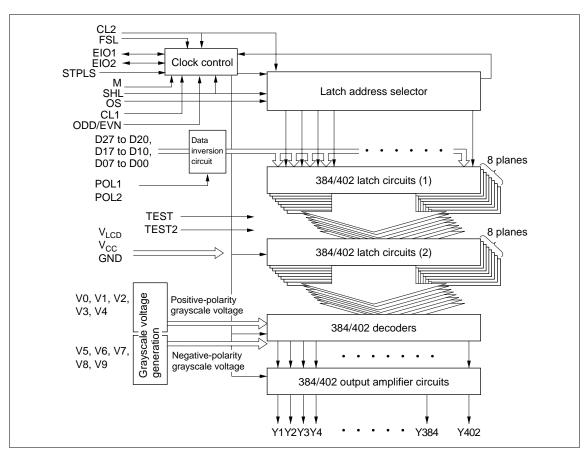

#### **Internal Block Diagram**

Figure 2 Block Diagram

1. Clock control unit

Generates the chip-enable signals (EIO2, EIO1) and controls internal timing signals.

2. Data inversion circuit

Uses the POL1 and POL2 signals to perform data polarity inversion (POL = 1) or non-inversion (POL = 0) processing of input display data.

3. Latch address selector

Generates latch signals for sequentially latching the input display data. Setting the OS pin enables the operation of the 384-output driver (OS = 0) or 402-output driver (OS = 1).

4. Latch circuits (1)

$402 \times 8$ -bit latch circuits that sequentially latch 6-output  $\times 8$ -bit input display data.

5. Latch circuits (2)

Perform latching, in synchronization with CL1, of the  $402 \times 8$ -bit data latched by latch circuits (1).

#### 6. Decoders

Decode the 8-bit data and select the liquid-crystal application voltages.

#### 7. Grayscale voltage generation unit

Performs resistance- and capacitance-division of the external input voltage, and generates 256 positive-polarity grayscales and 256 negative-polarity grayscales.

#### 8. Output amplifier circuits

Output the grayscale voltage that has been selected for each output and buffered in the operational amplifier.

### **Pin Functions**

#### Table 1 Pin Functions

| Signal Name                | Quantity | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>LCD</sub>           | 1        | Power supply | $V_{LCD}$<br>$V_{CC}$<br>$V_{CC}$<br>$V_{CC}$ - GND: Driver-circuit power supply<br>$V_{CC}$ - GND: Logic-circuit power supply                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>cc</sub>            | 1        | Power supply | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GND/AGND                   | 2        | Power supply |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V9 to V5                   | 5        | Power supply | Reference power supply for generating the liquid-crystal application voltage. Supplies a voltage in the range VLCD/2 + 0.5 to VLCD - 0.1 V to pins V0–V4, and a voltage in the range 0.1 V to VLCD/2 - 0.5 to pins V5–V9.                                                                                                                                                                                                                                                                                                                                      |

| V4 to V0                   | 5        | -            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CL1                        | 1        | Input        | Data of one line is transferred to the latch at the rising edge<br>of this clock, and the liquid-crystal application voltage is<br>output at the falling edge. One pulse must be input in each<br>horizontal period.                                                                                                                                                                                                                                                                                                                                           |

| CL2                        | 1        | Input        | Display data is latched at the rising edge of this clock.<br>For the 384-output LSIs, after the start pulse input, the start<br>pulse output goes high at the rising edge of the 63rd (66th)<br>clock, and this becomes the start pulse of the next-stage<br>driver. The 65th (68th) clock of the first-stage driver is the<br>start-pulse latch clock of the next-stage driver.<br>After the start pulse input, display data latching is halted<br>automatically when 66 (69) clock pulses are input.<br>(Values in parentheses are for the 402-output LSIs.) |

| POL1, POL2                 | 1        | Input        | Data-polarity inversion signal to reduce power consumption<br>of data bus lines in the interface.<br>When POL1 or POL2 is high, display data is inverted in the<br>driver. When POL1 or POL2 is low, display data is input<br>without inversion in the driver.<br>The POL1 signal controls the polarity of 24 data (D00 to<br>D27). The POL2 signal controls the polarity of 24 data (D30<br>to D57).<br>When POL1 or POL2 is not used, this pin must be either                                                                                                |

| <b></b>                    |          | · .          | high or low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D57 to D50,                | 48       | Input        | Inputs 8-bit (grayscale data) $\times$ 6-pixel display data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D47 to D40,                |          |              | Dx0 is the LSB, and Dx7 is the MSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D37 to D30,<br>D27 to D20, |          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D17 to D20,                |          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D07 to D00                 |          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                            |          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Signal Name | Quantity | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-------------|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| EIO1, EIO2  | 2        | Input/output | Chip-enable signals. Input/output switching is controlled by<br>the SHL signal. When these signals are used as inputs,<br>display data latching is performed when the input goes high.<br>When these signals are used as outputs, a low-to-high<br>transition is made at the rising edge of the 63rd (66th) clock<br>of the CL2 signal, and the next-stage driver is activated.<br>(Values in parentheses are for the 402-output LSIs.) |  |  |  |  |  |  |

|             |          |              | SHE         EIO1         EIO2           V <sub>CC</sub> Input         Output                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|             |          |              | GND Output Input                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Μ           | 1        | Input        | Current-alternating signal, controlling the liquid-crystal<br>alternating-current drive. The M signal is input after<br>provision of a setup time with respect to the rise of the CL1<br>signal. Positive-polarity (V0–V4) and negative-polarity (V5–<br>V9) output voltages are generated as shown below<br>according to the polarity of the latched M signal.                                                                         |  |  |  |  |  |  |

|             |          |              | MOdd output pins (Y1,Y3,,Y383)Even output pins (Y2,Y4,,Y384)0Positive-polarity liquid-crystal<br>application voltage is outputNegative-polarity liquid-crystal<br>application voltage is output1Negative-polarity liquid-crystal<br>application voltage is outputPositive-polarity liquid-crystal<br>application voltage is output                                                                                                      |  |  |  |  |  |  |

| OS          | 1        | Input        | Pin for switching the number of outputs. When OS is low,<br>this LSI operates as a 384-output product. When OS is high,<br>this LSI operates as a 402-output product.                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|             |          |              | Since this pin performs 50-k $\Omega$ pull-down processing within the chip, it must be opened or low when used as the 384-output product. When this pin is used as the 402-output product, it must be high.                                                                                                                                                                                                                             |  |  |  |  |  |  |

| FSL         | 1        | Input        | Pin for switching the operating speed.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|             |          |              | When it is used in the range of 40 to 65 MHz, input high level. When it is used in the range of 30 to 40 MHz, input low level.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|             |          |              | Since this pin performs 50-k $\Omega$ pull-down processing within the chip, it can be opened when it is used in the range of 30 to 40 MHz.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| STPLS       | 1        | Input        | Input the same signal as the start pulse, which is input in the first-stage IC, to the STPLS pin in all drivers. This pin is required for high-speed operation.                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| ODD/EVN     | 1        | Input        | When this pin is used for 402-output operation (OS = high),<br>use the first, third, or fifth pin as low level in the order of<br>fetched data. Use the second, fourth, or sixth pin as high<br>level. This pin is required for 402-output operation.                                                                                                                                                                                   |  |  |  |  |  |  |

|             |          |              | When this pin is used for 384-output operation (OS = low), set this pin to low in all drivers. Since this pin performs 50- $k\Omega$ pull-down processing within the chip, it can be opened.                                                                                                                                                                                                                                            |  |  |  |  |  |  |

#### Table 1 Pin Functions (cont)

| Signal Name | Quantity | Input/Output                                                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|-------------|----------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Y1 to Y402  | 402      | Output                                                                                           | Signal lines for output of liquid-crystal application voltages.<br>For the 384-output LSI, 18 invalid outputs can be selected to<br>not lead to the TCP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| TEST, TEST2 | 2        | Input                                                                                            | Test pins. Set these pins to low. Since these pins perform $50\text{-}k\Omega$ pull-down processing within the chip, use them opened or low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| SHL         | 1        | Controls display-data shift direction. <ul> <li>384-output LSI (OS is low or opened).</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|             |          |                                                                                                  | V <sub>CC</sub> D57 to D50<br>D47 to D40<br>D47 to D40<br>V380<br>D47 to D50<br>D47 to D50<br>D47 to D50<br>D47 to D40<br>D57 to D50<br>V6<br>D47 to D40<br>V5<br>D37 to D30<br>D47 to D40<br>V5<br>D47 to D40<br>V5<br>V6<br>D47 to D40<br>V5<br>V6<br>V6<br>V6<br>V7<br>V6<br>V7<br>V6<br>V6<br>V7<br>V6<br>V7<br>V6<br>V7<br>V6<br>V7<br>V6<br>V7<br>V6<br>V7<br>V6<br>V7<br>V7<br>V6<br>V7<br>V7<br>V7<br>V7<br>V7<br>V7<br>V7<br>V7<br>V7<br>V7<br>V7<br>V7<br>V7 |  |  |  |  |  |  |  |

|             |          |                                                                                                  | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

#### Table 1 Pin Functions (cont)

| Signal Name | Quantity | Input/Output | Function                                                                                                                                                                                                                                                                                            |                                                                                                |  |  |  |  |  |  |

|-------------|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SHL         | 1        | Input        | • 402-output LSI (OS is high).                                                                                                                                                                                                                                                                      |                                                                                                |  |  |  |  |  |  |

|             |          |              | V <sub>CC</sub> D57 to D50<br>D47 to D40<br>D37 to D30<br>D47 to D40<br>D37 to D30<br>D27 to D20<br>D17 to D10<br>D07 to D00           D57 to D50<br>D47 to D40<br>D37 to D30<br>D27 to D20<br>D17 to D10<br>D07 to D00           D57 to D50<br>D47 to D40<br>D7 to D20<br>D17 to D10<br>D07 to D00 | Y402<br>Y400<br>Y399<br>Y399<br>Y399<br>Y399<br>Y399<br>Y5<br>Y5<br>Y4<br>Y5<br>Y4<br>Y2<br>Y1 |  |  |  |  |  |  |

|             |          |              | GND<br>GND                                                                                                                                                                                                                                                                                          | Y402<br>Y400<br>Y399<br>Y399<br>Y397<br>Y6<br>Y5<br>Y4<br>Y3<br>Y2<br>Y1                       |  |  |  |  |  |  |

#### Table 1 Pin Functions (cont)

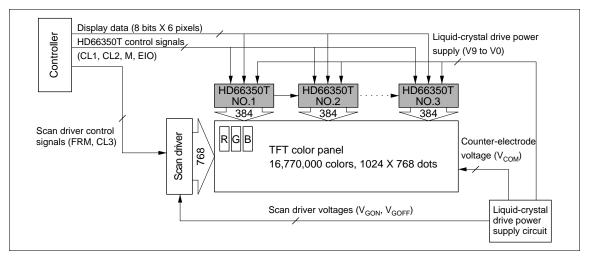

#### System Overview

Figure 3 is a block diagram of the configuration of an XGA ( $1024 \times 768$ ) compatible TFT color panel with the HD66350Ts. The HD66350T latches 8-bit data for each dot, selects a level from the 256 positive-polarity or negative-polarity liquid-crystal application voltages generated internally, and outputs that voltage.

By configuring pixels using R/G/B color filters, a full-color display of approximately 16,770,000 colors can be achieved.

Figure 3 System Block Diagram

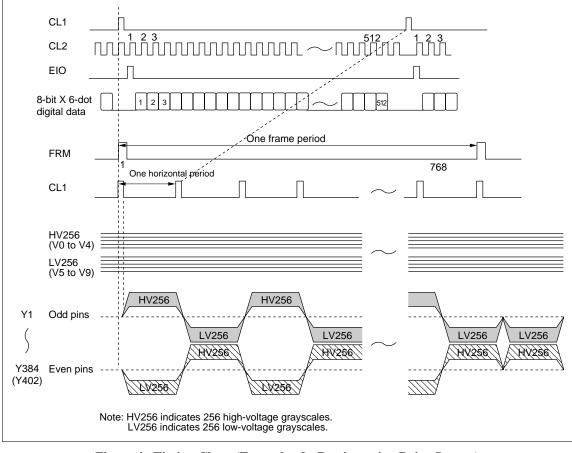

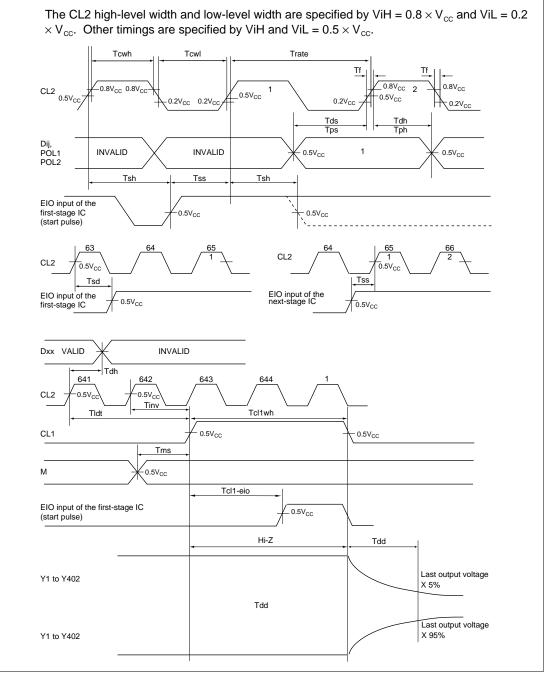

Figure 4 Timing Chart (Example of a Dot-inversion Drive System)

### **Operation Timing**

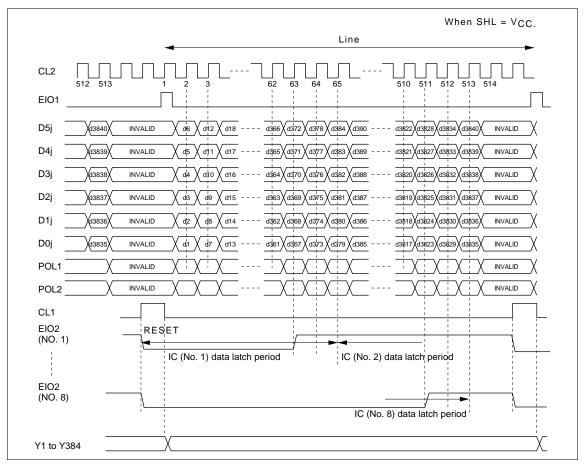

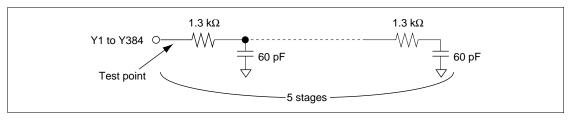

Figure 5 Operation Timing

The high level of the enable-input signal (when SHL =  $V_{CC}$ : EIO1) is latched at the rising edge of the data-latch clock signal CL2, and data latching begins after one CL2 signal cycle. Data of 8 bits × RGB × 2 pixels, i.e. 6 outputs, are simultaneously latched at the rising edge of the CL2 signal. At the rising edge of the 63rd clock pulse of the CL2 signal, the enable-output signal (when SHL =  $V_{CC}$ : EIO2) is driven high, and the operation is automatically halted (the standby state is entered) when latching of data for 384 outputs is completed. By connecting the EIO2 pin to the next-stage EIO1 pin, the next-stage IC is activated in the same way. All the IC enable-output signals are reset at the rising edge of the CL1 signal.

The data-latch clock signal CL2 does not require a clock-halted period. At least two clocks must be added to the necessary CL2 clocks (512 clocks for XGA) in each horizontal period.

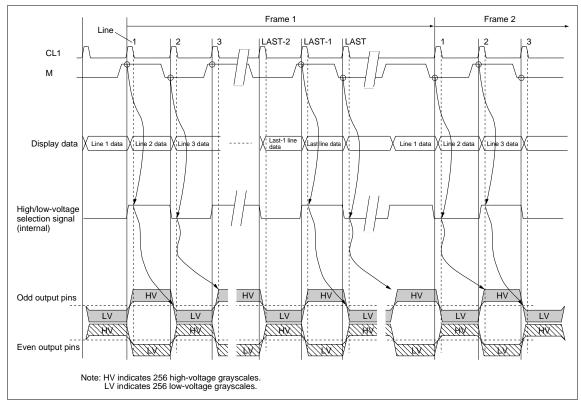

### **M Signal and Data Input**

This example shows the relationship between the data input, M signal, and output level, with dot-bydot inversion and frame inversion. The HD66350T driver must hold the M signal during the high-level period of CL1. The grayscale-voltage selection circuits for high and low voltages are operated according to the M signal level at the rise of CL1, and the grayscale voltages are output at the following rising edges of CL1.

To provide stable output operation of the buffer amplifier, the output is placed in the high-impedance state in the high-level period of CL1.

Figure 6 Relationship between the M Signal and Data Input

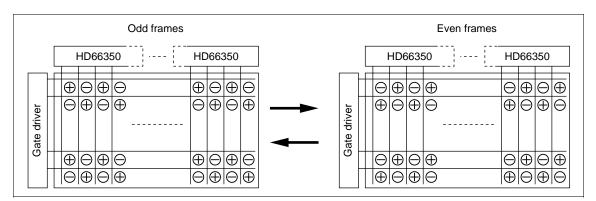

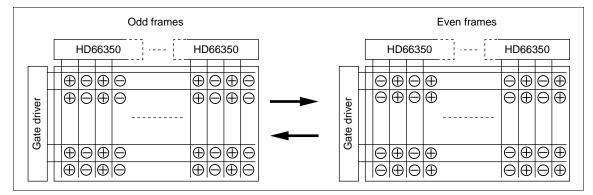

#### **Pin-by-pin Inversion Drive**

With regard to the inversion standard voltage for individual adjacent odd and even output pins, the HD66350T can generate 256-level positive-polarity and negative-polarity grayscale voltages. In addition, the liquid-crystal alternating-current drive can be controlled by switching the polarity of the M signal. (See the Pin Functions section.)

In this way, when HD66350Ts are arranged on either the upper or lower side of a TFT LCD panel, a dot inversion drive can be used in which grayscale voltages of different polarities are applied to individual adjacent dots by switching the M signal on each CL1 clock, reducing the crosstalk which adversely affects image quality, and thus achieving a high-quality display.

Figure 7 Dot Inversion Drive

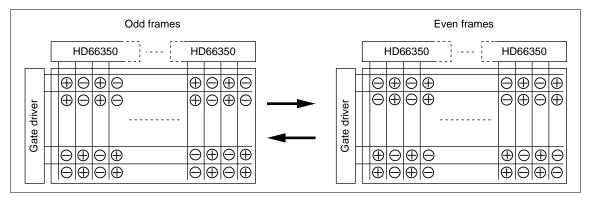

When the M signal switches on each CL1n clock, the following n-raster-row inversion drive can be used on each horizontal dot and vertical n-raster-row.

Figure 8 n-raster-row Inversion Drive

When the M signal switches on each FLM signal, the following frame inversion drive can be used on each horizontal dot and vertical frame.

Figure 9 Frame Inversion Drive

#### **System Application**

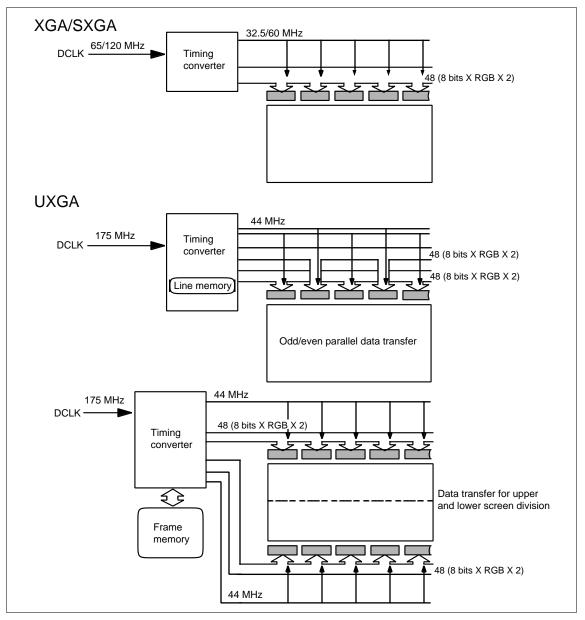

Figure 10 shows system applications for XGA-, SXGA-, and UXGA-sized TFT color panels with the HD66350Ts.

For the XGA or SXGA size, the dot clock frequency is halved by the timing converter and data are transferred to the drivers. For the UXGA size, after the dot clock frequency is halved, data are transferred to odd and even drivers in parallel with the frequency halved again. Since one horizontal period is shorter for the UXGA size, the screen can be divided into upper and lower screens for the purpose of transferring data if the display panel has a large TFT load capacitance.

Figure 10 System Applications

### **Display Data and Output Voltage**

With input of a 10-level liquid-crystal power supply and 8-bit digital data, the HD66350T outputs 256 grayscale voltage levels on the high-voltage side and 256 grayscale voltage levels on the low-voltage side.

Tables 2 and 3 show the relationship between the input voltages of the liquid-crystal power supply, digital codes, and output voltages.

Figure 11 Selection of the LCD Drive Output Level

#### Ladder Resistance Values (Reference Values)

|        | Resistance | Resistance |                    |  |  |  |  |

|--------|------------|------------|--------------------|--|--|--|--|

| V0,V9  | Name       | Value      | V0 R 0             |  |  |  |  |

| 10,10  | R0         | 600        |                    |  |  |  |  |

|        | R1         | 516        | <b>≹</b> R 1       |  |  |  |  |

|        | R2         | 450        | ↓ R 2              |  |  |  |  |

|        | R3         | 390        |                    |  |  |  |  |

|        | R4         | 339        |                    |  |  |  |  |

|        | R5         | 300        | ₹ <sup>R 7</sup>   |  |  |  |  |

|        | R6         | 270        | V1                 |  |  |  |  |

| 14.10  | R7         | 255        | ſ                  |  |  |  |  |

| V1,V8  | R8         | 240        | ₹ <sup>R</sup> 9   |  |  |  |  |

|        | R9         | 240        | V2                 |  |  |  |  |

|        | R10        | 240        | V3                 |  |  |  |  |

|        | R11        | 240        |                    |  |  |  |  |

|        | R12        | 243        | <b>≷</b> R 31      |  |  |  |  |

|        | R13        | 252        | V4 ———<br>Separate |  |  |  |  |

|        | R14        | 261        | V5 R 31            |  |  |  |  |

|        | R15        | 264        |                    |  |  |  |  |

| V2,V7  | R16        | 270        | V6                 |  |  |  |  |

|        | R17        | 285        | V7 ———             |  |  |  |  |

|        | R18        | 300        |                    |  |  |  |  |

|        | R19        | 315        | <b>₹</b> R 9       |  |  |  |  |

|        | R20        | 330        | ↓<br>≶R 8          |  |  |  |  |

|        | R21        | 354        | V8                 |  |  |  |  |

|        | R22        | 366        | <b>₹</b> R7        |  |  |  |  |

|        | R23        | 390        |                    |  |  |  |  |

| V3,V6  | R24        | 420        | <b>₹</b> R 2       |  |  |  |  |

|        | R25        | 480        | <br>≥ R 1          |  |  |  |  |

|        | R26        | 540        | <b>~</b> ``        |  |  |  |  |

|        | R27        | 600        | ₹ <sup>R 0</sup>   |  |  |  |  |

|        | R28        | 660        | V9]                |  |  |  |  |

|        | R29        | 720        | Figure 12 Ladder   |  |  |  |  |

|        | R30        | 900        | Resistance         |  |  |  |  |

| \/A\/F | R31        | 1200       |                    |  |  |  |  |

| V4,V5  | Total      | 13230      |                    |  |  |  |  |

Table 2

256 Positive-polarity Grayscale Levels

| Display Data |     |     |     |     |     |     |     |                                        |                           |

|--------------|-----|-----|-----|-----|-----|-----|-----|----------------------------------------|---------------------------|

| Code         | Di7 | Di6 | Di5 | Di4 | Di3 | Di2 | Di1 | 256 Positive-polarity Grayscale Levels |                           |

| 0040<br>00h  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0                                      | V 0                       |

| 01h          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1                                      | <b>Å</b>                  |

| 02h          | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0                                      |                           |

| 03h          | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1                                      | Divided into eight levels |

| 04h          | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0                                      |                           |

| 05h          | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1<br>0                                 |                           |

| 06h<br>07h   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1                                      |                           |

| 08h          | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0                                      | V0-(V0-V1)X600/3120       |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 10h          | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0                                      | V0-(V0-V1)X1116/3120      |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 18h          | 0   | 0   | 0   | 1   | 1   | 0   | 0   | 0                                      | V0-(V0-V1)X1566/3120      |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 20h          | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0                                      | V0-(V0-V1)X1956/3120      |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 28h          | 0   | 0   | 1   | 0   | 1   | 0   | 0   | 0                                      | V0-(V0-V1)X2295/3120      |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 30h          | 0   | 0   | 1   | 1   | 0   | 0   | 0   | 0                                      | V0-(V0-V1)X2595/3120      |

|              |     | -   |     |     | -   |     |     |                                        | Divided into eight levels |

| 38h          | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 0                                      | V0-(V0-V1)X2865/3120      |

|              |     |     |     |     |     | -   |     |                                        | Divided into eight levels |

| 40h          | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0                                      | V 1                       |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 48h          | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 0                                      | V1-(V1-V2)X240/1980       |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 50h          | 0   | 1   | 0   | 1   | 0   | 0   | 0   | 0                                      | V1-(V1-V2)X480/1980       |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 58h          | 0   | 1   | 0   | 1   | 1   | 0   | 0   | 0                                      | V1-(V1-V2)X720/1980       |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 60h          | 0   | 1   | 1   | 0   | 0   | 0   | 0   | 0                                      | V1-(V1-V2)X960/1980       |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 68h          | 0   | 1   | 1   | 0   | 1   | 0   | 0   | 0                                      | V1-(V1-V2)X1203/1980      |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 70h          | 0   | 1   | 1   | 1   | 0   | 0   | 0   | 0                                      | V1-(V1-V2)X1455/1980      |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 78h          | 0   | 1   | 1   | 1   | 1   | 0   | 0   | 0                                      | V1-(V1-V2)X1716/1980      |

|              |     |     |     |     |     |     |     |                                        | Divided into eight levels |

| 80h          | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0                                      | V2                        |

| Table 2 | 256 Positive-polarity | Grayscale Levels (cont) |

|---------|-----------------------|-------------------------|

|---------|-----------------------|-------------------------|

| Code<br>80h | Di7 |        |     |     |     |     |     | OFO Desitive aslasity Oscillar 1 |                                        |  |

|-------------|-----|--------|-----|-----|-----|-----|-----|----------------------------------|----------------------------------------|--|

| 80h         |     | Di6    | Di5 | Di4 | Di3 | Di2 | Di1 | Di0                              | 256 Positive-polarity Grayscale Levels |  |

|             | 1   | 0      | 0   | 0   | 0   | 0   | 0   | 0                                | V2                                     |  |

|             |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| 88h         | 1   | 0      | 0   | 0   | 1   | 0   | 0   | 0                                | V2-(V2-V3)X270/2610                    |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| 90h         | 1   | 0      | 0   | 1   | 0   | 0   | 0   | 0                                | V2-(V2-V3)X555/2610                    |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| 98h         | 1   | 0      | 0   | 1   | 1   | 0   | 0   | 0                                | V2-(V2-V3)X855/2610                    |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| A0h         | 1   | 0      | 1   | 0   | 0   | 0   | 0   | 0                                | V2-(V2-V3)X1170/2610                   |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| A8h         | 1   | 0      | 1   | 0   | 1   | 0   | 0   | 0                                | V2-(V2-V3)X1500/2610                   |  |

|             |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| B0h         | 1   | 0      | 1   | 1   | 0   | 0   | 0   | 0                                | V2-(V2-V3)X1854/2610                   |  |

|             |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| B8h         | 1   | 0      | 1   | 1   | 1   | 0   | 0   | 0                                | V2-(V2-V3)X2220/2610                   |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| C0h         | 1   | 1      | 0   | 0   | 0   | 0   | 0   | 0                                | V3                                     |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| C8h         | 1   | 1      | 0   | 0   | 1   | 0   | 0   | 0                                | V 3 - (V 3 - V 4) X420/5520            |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| D0h         | 1   | 1      | 0   | 1   | 0   | 0   | 0   | 0                                | V3-(V3-V4)X900/5520                    |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| D8h         | 1   | 1      | 0   | 1   | 1   | 0   | 0   | 0                                | V 3 - (V 3 - V 4) X1440/5520           |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| EOh         | 1   | 1      | 1   | 0   | 0   | 0   | 0   | 0                                | V 3 - (V 3 - V 4) X2040/5520           |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| E8h         | 1   | 1      | 1   | 0   | 1   | 0   | 0   | 0                                | V3-(V3-V4)X2700/5520                   |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| F0 h        | 1   | 1      | 1   | 1   | 0   | 0   | 0   | 0                                | V3-(V3-V4)X3420/5520                   |  |

| l           |     |        |     |     |     |     |     |                                  | Divided into eight levels              |  |

| F8 h        | 1   | 1      | 1   | 1   | 1   | 0   | 0   | 0                                | V 3 - (V 3 - V 4) X4320/5520           |  |

| F9 h        | 1   | 1      | 1   | 1   | 1   | 0   | 0   | 1                                | • • • • • • • • • • • • • • • • • • •  |  |

| FA h        | 1   | 1      | 1   | 1   | 1   | 0   | 1   | 0                                |                                        |  |

| FB h        | 1   | 1      | 1   | 1   | 1   | 0   | 1   | 1                                | Divided into eight levels              |  |

| FCh<br>FDh  | 1   | 1      | 1   | 1   | 1   | 1   | 0   | 0                                | Divided into eight levels              |  |

| FDh         | 1   | 1<br>1 | 1   | 1   | 1   | 1   | 0   | 1<br>0                           |                                        |  |

| FFh         | 1   | 1      | 1   | 1   | 1   | 1   | 1   | 1                                | V4+1/8X(V3-V4)X1200/5520               |  |

| Display Data |     |     |     |     |     |     |     |     |                                        |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------------------|--|

| Code         | Di7 | Di6 | Di5 | Di4 | Di3 | Di2 | Di1 | Di0 | 256 Negative-polarity Grayscale Levels |  |

| 00h          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | V <u>9</u>                             |  |

| 01h          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | <b>A</b>                               |  |

| 02h          | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |                                        |  |

| 03h<br>04h   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | Divided into eight levels              |  |

| 05h          | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |                                        |  |

| 06h          | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   |                                        |  |

| 07h          | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   |                                        |  |

| 08h          | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | V9-(V9-V8)X600/3120                    |  |

| l            |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 10h          | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | V9-(V9-V8)X1116/3120                   |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 18h          | 0   | 0   | 0   | 1   | 1   | 0   | 0   | 0   | V9-(V9-V8)X1566/3120                   |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 20h          | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | V9-(V9-V8)X1956/3120                   |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 28h          | 0   | 0   | 1   | 0   | 1   | 0   | 0   | 0   | V9-(V9-V8)X2295/3120                   |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 30h          | 0   | 0   | 1   | 1   | 0   | 0   | 0   | 0   | V9-(V9-V8)X2595/3120                   |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 38h          | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 0   | V9-(V9-V8)X2865/3120                   |  |

| l            |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 40h          | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | V8                                     |  |

| 1            |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 48h          | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 0   | V8-(V8-V7)X240/1980                    |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 50h          | 0   | 1   | 0   | 1   | 0   | 0   | 0   | 0   | V8-(V8-V7)X480/1980                    |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 58h          | 0   | 1   | 0   | 1   | 1   | 0   | 0   | 0   | V8-(V8-V7)X720/1980                    |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 60h          | 0   | 1   | 1   | 0   | 0   | 0   | 0   | 0   | V 8 - (V 8 - V 7) X960/1980            |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 68h          | 0   | 1   | 1   | 0   | 1   | 0   | 0   | 0   | V8-(V8-V7)X1203/1980                   |  |

| l            |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 70h          | 0   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | V 8 - (V 8 - V 7 ) X1455/1980          |  |

|              |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 78h          | 0   | 1   | 1   | 1   | 1   | 0   | 0   | 0   | V8-(V8-V7)X1716/1980                   |  |

| l            |     |     |     |     |     |     |     |     | Divided into eight levels              |  |

| 80h          | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | V7                                     |  |

Table 3

256 Negative-polarity Grayscale Levels

| Table 3 | 256 Negative-polarity Grayscale Levels (cont) |

|---------|-----------------------------------------------|

|---------|-----------------------------------------------|

| Code         Di7         Di6         Di3         Di4         Di3         Di2         Di1         Di0         256         Megative-polarity Grayscale Levels           80h         1         0         0         0         0         0         0         V         V           88h         1         0         0         0         1         0         0         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Display Data |     |   |          |   |     |     |     |     |                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|---|----------|---|-----|-----|-----|-----|----------------------------------------|

| Image: Second  | Code         | Di7 |   | <u> </u> |   | Di3 | Di2 | Di1 | Di0 | 256 Negative-polarity Grayscale Levels |

| BBh         1         0         0         1         0         0         0         V7-(V7-V6)X270/2610           90h         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         V7-(V7-V6)X555/2610           98h         1         0         0         1         1         0         0         0         V7-(V7-V6)X555/2610           98h         1         0         0         1         1         0         0         0         V7-(V7-V6)X170/2610           A0h         1         0         1         0         0         0         V7-(V7-V6)X1500/2610           1         0         1         0         0         0         V7-(V7-V6)X1500/2610           1         0         1         1         0         0         0         V7-(V7-V6)X1500/2610           1         1         1         1         0         0         0         V7-(V7-V6)X1500/2610           1         1         0         1         1         0         0         V7-(V7-V6)X1500/2610           1         1         0         1 </td <td>80h</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>V7</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80h          | 1   | 0 | 0        | 0 | 0   | 0   | 0   | 0   | V7                                     |

| On         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I <thi< th="">         I         <thi< th=""> <thi< th=""></thi<></thi<></thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | l            |     |   |          |   |     |     |     |     | Divided into eight levels              |

| 90h         1         0         0         1         0         0         0         0         V7-(V7-V6)X555/2610           98h         1         0         0         1         1         0         0         0         V7-(V7-V6)X555/2610           98h         1         0         0         1         1         0         0         0         V7-(V7-V6)X555/2610           A0h         1         0         1         0         0         0         0         V7-(V7-V6)X1170/2610           A8h         1         0         1         0         1         0         0         0         V7-(V7-V6)X1500/2610           I         0         1         0         1         0         0         0         V7-(V7-V6)X1500/2610           I         0         1         1         0         0         0         0         V7-(V7-V6)X1540/2610           I         0         1         1         1         0         0         0         V7-(V7-V6)X1540/2610           I         0         0         0         0         0         0         V7-(V7-V6)X220/2610           I         1         0         0         0 </td <td>88h</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>V7-(V7-V6)X270/2610</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 88h          | 1   | 0 | 0        | 0 | 1   | 0   | 0   | 0   | V7-(V7-V6)X270/2610                    |

| On         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I <thi< th="">         I         <thi< th=""> <thi< th=""></thi<></thi<></thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | l            |     |   |          |   |     |     |     |     | Divided into eight levels              |

| 98h         1         0         0         1         1         0         0         0         V7-(V7-V6)X855/2610           A0h         1         0         1         0         0         0         0         0         V7-(V7-V6)X855/2610           A0h         1         0         1         0         1         0         0         0         0         V7-(V7-V6)X1170/2610           A8h         1         0         1         0         1         0         0         0         0         V7-(V7-V6)X1500/2610           B0h         1         0         1         1         0         0         0         0         V7-(V7-V6)X1824/2610           B8h         1         0         1         1         0         0         0         V7-(V7-V6)X1824/2610           B8h         1         0         1         1         0         0         0         V7-(V7-V6)X1824/2610           B8h         1         0         1         1         0         0         0         V7-(V7-V6)X1824/2610           Divided into eight levels         Divided into eight levels         Divided into eight levels         Divided into eight levels           C0 h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90h          | 1   | 0 | 0        | 1 | 0   | 0   | 0   | 0   | V7-(V7-V6)X555/2610                    |

| Image: Second system         A0h       1       0       1       0       0       0       0       0       V7-(V7-V6)X1170/2610         Image: Second system       Image: Second system </td <td>l</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>Divided into eight levels</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                             | l            |     |   |          |   |     |     |     |     | Divided into eight levels              |

| A0h       1       0       1       0       0       0       0       V7-(V7-V6)X1170/2610         A8h       1       0       1       0       1       0       1       0       0       0       V7-(V7-V6)X1170/2610         B0h       1       0       1       0       1       0       0       0       V7-(V7-V6)X1500/2610         B0h       1       0       1       1       0       0       0       V7-(V7-V6)X1500/2610         B0h       1       0       1       1       0       0       0       V7-(V7-V6)X1542/2610         Image: Construct of the constr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 98h          | 1   | 0 | 0        | 1 | 1   | 0   | 0   | 0   | V7-(V7-V6)X855/2610                    |

| ABh       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       0       0       0       V7-(V7-V6)X1500/2610         I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>Divided into eight levels</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |     |   |          |   |     |     |     |     | Divided into eight levels              |

| A8h       1       0       1       0       0       0       V7-(V7-V6)X1500/2610         B0h       1       0       1       1       0       0       0       0       V7-(V7-V6)X1500/2610         B0h       1       0       1       1       0       0       0       0       V7-(V7-V6)X1854/2610         II       0       1       1       1       0       0       0       V7-(V7-V6)X2220/2610         II       1       0       0       0       0       0       V7-(V7-V6)X2220/2610         II       1       0       0       0       0       0       V7-(V7-V6)X2220/2610         II       1       0       0       0       0       0       V86         C0h       1       1       0       0       0       V6       Divided into eight levels         C8h       1       1       0       0       0       0       V6-(V6-V5)X420/5520         II       1       0       1       0       0       0       V6-(V6-V5)X1440/5520         II       1       1       0       0       0       V6-(V6-V5)X2700/5520         II       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AOh          | 1   | 0 | 1        | 0 | 0   | 0   | 0   | 0   | V7-(V7-V6)X1170/2610                   |

| BOh         1         0         1         1         0         0         0         0         V7-(V7-V6)X1854/2610           B8h         1         0         1         1         1         0         0         0         0         V7-(V7-V6)X1854/2610           B8h         1         0         1         1         1         0         0         0         V7-(V7-V6)X2220/2610           I         1         0         0         0         0         0         V7-(V7-V6)X2220/2610           I         1         0         0         0         0         0         V6           C0h         1         1         0         0         0         0         0         V6           I         1         0         0         1         0         0         0         V6         V6-(V6-V5)X420/5520           I         1         0         1         1         0         0         0         V6         V6-(V6-V5)X40/5520           I         1         1         0         0         0         0         V6         V6-(V6-V5)X2040/5520           I         1         1         1         0 <th< td=""><td>l</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>Divided into eight levels</td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | l            |     |   |          |   |     |     |     |     | Divided into eight levels              |