### **NEC**

## **Application Note**

## USAGE OF $\mu$ PC1663, DC to VHF WIDEBAND DIFFERENTIAL INPUT AND OUTPUT AMPLIFIER IC

#### The information in this document will be updated without notice.

This document outlines a typical application of this product, that is, provides an example for designing concept of an external circuit directly required for this product. NEC only assures the quality and characteristics of this product specified in the Data Sheet, and is not responsible for any user's product designs or application sets.

The peripheral circuit shown in this document is just an example prepared for evaluating the operations of this product, and does not imply that the circuit configurations or constants are recommended values or regulations. In addition, these circuits are not intended for any mass-produced application sets. This is because the analog characteristics vary depending on the external parts used, mounting patterns, and other conditions.

For this reason, customers are responsible for designing external circuits according to user-designed system requirements by referring this document, and should also confirm the characteristics of their application circuit before use.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5

### **CONTENTS**

| 1. | GEN  | ERAL                                                                      | 7  |  |  |  |  |  |

|----|------|---------------------------------------------------------------------------|----|--|--|--|--|--|

| 2. | BASI | BASIC OPERATIONS                                                          |    |  |  |  |  |  |

|    | 2.1  | Outline of Operations                                                     | 7  |  |  |  |  |  |

|    | 2.2  | Determination of Gain                                                     | 8  |  |  |  |  |  |

|    | 2.3  | Gain Adjustments                                                          | 8  |  |  |  |  |  |

| 3. | ELEC | ELECTRICAL CHARACTERISTICS                                                |    |  |  |  |  |  |

|    | 3.1  | Differential Voltage Gain (AvD)                                           | 11 |  |  |  |  |  |

|    | 3.2  | Bandwidth (BW)                                                            | 11 |  |  |  |  |  |

|    | 3.3  | Rise Time (t <sub>r</sub> ) and Propagation Delay Time (t <sub>pd</sub> ) | 11 |  |  |  |  |  |

|    | 3.4  | Input Resistance (Rin)                                                    | 11 |  |  |  |  |  |

|    | 3.5  | Input Capacitance (Cin)                                                   | 11 |  |  |  |  |  |

|    | 3.6  | Input Offset Current (Iio)                                                | 11 |  |  |  |  |  |

|    | 3.7  | Input Bias Current (IB)                                                   | 12 |  |  |  |  |  |

|    | 3.8  | Input Noise Voltage (Vn)                                                  | 12 |  |  |  |  |  |

|    | 3.9  | Input Voltage Range (VI)                                                  | 12 |  |  |  |  |  |

|    | 3.10 | Common Mode Rejection Ratio (CMR)                                         | 12 |  |  |  |  |  |

|    | 3.11 | Supply Voltage Rejection Ratio (SVR)                                      | 12 |  |  |  |  |  |

|    | 3.12 | Output Offset Voltage (Vo(off))                                           | 13 |  |  |  |  |  |

|    | 3.13 | Output Common Mode Voltage (Vo(cm))                                       | 13 |  |  |  |  |  |

|    | 3.14 | Output Voltage Swing (Vop-p)                                              | 13 |  |  |  |  |  |

|    | 3.15 | Output Sink Current                                                       | 13 |  |  |  |  |  |

|    | 3.16 | Power Supply Current                                                      | 13 |  |  |  |  |  |

| 4. | PRE  | CAUTIONS FOR DESIGN IN                                                    | 14 |  |  |  |  |  |

|    | 4.1  | Cautions on Layout and Wiring                                             | 14 |  |  |  |  |  |

|    | 4.2  | Cautions on External Circuit                                              | 14 |  |  |  |  |  |

|    | 4.3  | Other Caution Points                                                      | 14 |  |  |  |  |  |

| 5. | APPI | ICATION CIRCUIT EXAMPLES                                                  | 16 |  |  |  |  |  |

|    | 5.1  | Video Line Driver Circuit Example                                         | 16 |  |  |  |  |  |

|    | 5.2  | Optical Signal Detection Circuit Example                                  | 17 |  |  |  |  |  |

| 6. | EXA  | MPLE OF MOUNTING MEASURING CIRCUIT ON PRINTED BOARD                       | 18 |  |  |  |  |  |

|    | 6.1  | Example of Mounting $\mu$ PC1663G on Printed Board                        | 18 |  |  |  |  |  |

|    | 6.2  | Example of Mounting μPC1663GV on Printed Board                            | 19 |  |  |  |  |  |

| 7. | CON  | CLUSION                                                                   | 20 |  |  |  |  |  |

#### 1. GENERAL

The  $\mu$ PC1663 is a differential input, differential output wideband amplifier IC that uses a high-frequency (fr = 6 GHz) silicon bipolar process (called NESAT<sup>TM</sup> 1). This process improves bandwidth, phase characteristics, input noise voltage characteristics, and low power consumption compared to conventional HF-band differential amplifier ICs.

These features make this device suitable as a wideband amplifier in high-definition TVs, high-resolution monitors, broadcasting satellite receivers, and video cameras, as a sense amplifier in high-density CCD and optical pick-up products, or as a pulse amplifier for optical data links.

Note, however, that this device's wide frequency range means that extra caution is required with regard to factors such as oscillation.

This application note describes how to use the  $\mu$ PC1663 and its application circuits.

#### 2. BASIC OPERATIONS

#### 2.1 Outline of Operations

Vcc R10€ ≶R11 R2  $Q_5$  $2.4 \text{ k}\Omega$  $R_{11}$  1.1  $k\Omega$  $\mathbf{Q}_{6}$  $2.4 \text{ k}\Omega$  $R_{12}$  750  $\Omega$  $R_{13}$  300  $\Omega$ R۹  $50 \Omega$ Qз  $Q_4$  $50 \Omega$  $R_{14}$  7  $k\Omega$  $R_4$ 590  $\Omega$  $R_{15}$  7  $k\Omega$  $R_5$ IN<sub>2</sub> R<sub>16</sub> 1.2 kΩ IN<sub>1</sub>O 590 Ω  $R_6$  $Q_2$ R<sub>14</sub> G<sub>1A</sub>O О **G**1в O OUT<sub>1</sub> R<sub>7</sub>  $600 \Omega$  $R_{17}$  400  $\Omega$ R<sub>8</sub>  $10 \text{ k}\Omega$  $R_{18}$  1.2  $k\Omega$ ≶R₄ OUT2 ∕₩ **R**15 R<sub>9</sub>  $1.4 \text{ k}\Omega$  $R_{19}$  400  $\Omega$ (G<sub>2A</sub>)Note -(G<sub>2B</sub>)  $R_{10}$  1.1  $k\Omega$ R12≶ ≶R18 ⋛R6 ≷R16  $Q_8$ Q9 Q10 Q11 R17€ R<sub>9</sub> R13 € R19 € **Note:** The  $\mu$ PC1664, which included G<sub>2A</sub> and G<sub>2B</sub> pins, has been discontinued. 9

Figure 1. Internal Equivalent Circuit

Figure 1 shows an internal equivalent circuit diagram of the  $\mu$ PC1663. It is a DC direct-coupled amplifier in which two emitter-followers for transistors Q<sub>5</sub> and Q<sub>6</sub> are added to the two-stage differential configuration and in which feedback is propagated from the output via R<sub>14</sub> and R<sub>15</sub>.

Since OUT<sub>1</sub> and OUT<sub>2</sub> are differential outputs, the output voltage changes to the reverse direction at precisely double the gain (single-end) of differential voltage  $\Delta V_{DIF}$  added between the differential inputs IN<sub>1</sub> and IN<sub>2</sub>. OUT<sub>1</sub> operates in phase with IN<sub>1</sub> and OUT<sub>2</sub> operates in phase with IN<sub>2</sub>, so that, for example:

When IN<sub>1</sub> > IN<sub>2</sub>, OUT<sub>1</sub> changes to positive and OUT<sub>2</sub> changes to negative

Vcc

When  $IN_1 < IN_2$ ,  $OUT_1$  changes to negative and  $OUT_2$  changes to positive

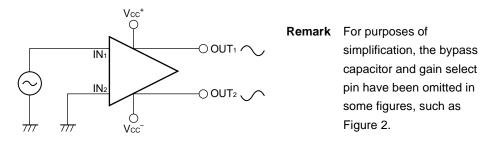

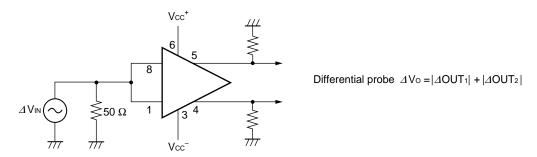

Accordingly, as is shown in Figure 2, if a sine wave is input to  $IN_1$  when  $IN_2$  is used as a ground, a sine wave having the same phase as the  $IN_1$  input is output via  $OUT_1$  and a sine wave having a  $180^{\circ}$  inverted phase is output via  $OUT_2$ .

Figure 2. Response to Sine Wave Input

#### 2.2 Determination of Gain

Given  $r_{e1}$  and  $r_{e2}$  as the resistance values corresponding to the input differential transistors  $Q_1$  and  $Q_2$ , the gain can be approximated via the following equations.

Gain AVD1 for IN1 and OUT1

AVD1

$$\doteq \frac{R_{14}}{r_{e1} + R_3 + R_5}$$

.....(1)

Gain AVD2 for IN2 and OUT2

$$A_{VD2} \doteq \frac{R_{15}}{r_{e2} + R_4 + R_6} \qquad (2)$$

Consequently, assuming that  $\Delta V_{DIF} = V_{IN1} - V_{IN2}$  as the differential voltage between IN<sub>1</sub> and IN<sub>2</sub>, the output voltage can be calculated as follows.

$$|\Delta OUT_1| = \frac{|\Delta V_{DIF}|}{2} \cdot A_{VD1}....(3)$$

$$|\Delta OUT_2| = \frac{|\Delta V_{DIF}|}{2} \cdot A_{VD2}....(4)$$

Since AVD1 = AVD2, we can add equations (3) and (4) to obtain the following.

$$Avd1 = \frac{|\Delta OUT_1| + |\Delta OUT_2|}{|\Delta V_{DIF}|} \dots (5)$$

In equations (3), (4), and (5), AVD1 (AVD2) represents the differential output gain corresponding to the differential input voltage. Therefore, the differential voltage gain and AVD1/2 (AVD2/2) are defined as single-end voltage gain since it represents only one-sided output corresponding to the differential input voltage.

#### 2.3 Gain Adjustments

The gain values shown in equations (1) and (2) in section 2.2 above are determined according to the resistance applied to the emitter side of input differential transistors Q<sub>1</sub> and Q<sub>2</sub>.

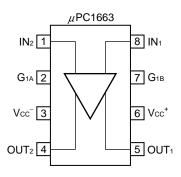

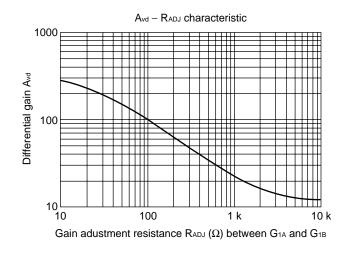

Accordingly, in the equivalent circuit shown in Figure 1, a short between gain select pins G<sub>1A</sub> and G<sub>1B</sub> or insertion of an adjusting resistor can be used to adjust the gain in steps.

Setting a short between G<sub>1A</sub> and G<sub>1B</sub> sets maximum gain, with a typical value of 320 times the differential gain. Setting an open connection between G<sub>1A</sub> and G<sub>1B</sub> sets minimum gain, with a typical value of 10 times the differential gain. The electrical characteristics for the two gain select pin conditions, when Gain 1 is the maximum gain and Gain 2 is the minimum gain, are shown in Table 3.

If a gain adjusting resistor is inserted between G1A and G1B (as shown in Figure 4), any desired gain level can be obtained. Depending on the application circuit, if the Rs value is changed, the input voltage amplitude appears like it fluctuates due to changes in the interstage impedance, but the gain of the IC itself does not vary.

Figure 3. Pin Configuration of  $\mu$ PC1663 (Top View)

Figure 4. Differential Voltage Gain vs. Gain Adjustment Resistance Characteristics

#### 3. ELECTRICAL CHARACTERISTICS

The absolute maximum ratings are listed in Table 1, recommended operating conditions in Table 2, and electrical characteristics in Table 3. Due to limitations that depend on the package, the supply voltage and temperature range differ slightly. The electrical characteristics are identical, however, because the same chip is employed.

**Table 1. Absolute Maximum Ratings**

| Parameter                     | Symbol           | Condition                                                                    | μPC1663C                        | μPC1663G                        | μPC1663GV                       | Unit |

|-------------------------------|------------------|------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|------|

| Power supply voltage          | Vcc <sup>±</sup> | T <sub>A</sub> = +25°C                                                       | ±8                              | ±7                              | ±7                              | V    |

| Total dissipation             | P <sub>D</sub>   | Note                                                                         | 500<br>(T <sub>A</sub> = +85°C) | 280<br>(T <sub>A</sub> = +75°C) | 280<br>(T <sub>A</sub> = +75°C) | mW   |

| Differential input voltage    | VID              | T <sub>A</sub> = +25°C                                                       | ±5                              | ±5                              | ±5                              | V    |

| Common mode input voltage     | Vісм             | T <sub>A</sub> = +25°C,<br>within Vcc <sup>-</sup> to Vcc <sup>+</sup> range | ±6                              | ±6                              | ±6                              | ٧    |

| Output current                | lo               | T <sub>A</sub> = +25°C                                                       | 35                              | 35                              | 35                              | mA   |

| Operating ambient temperature | TA               |                                                                              | -45 to +85                      | -45 to +75                      | -45 to +75                      | °C   |

| Storage temperature           | T <sub>stg</sub> |                                                                              | -55 to +150                     | -55 to +150                     | -55 to +150                     | °C   |

**Note** When mounted on a double sided copper clad  $50 \times 50 \times 1.6$  mm epoxy glass PWB

**Table 2. Recommended Operating Conditions**

| Parameter                 | Symbol                                 | MIN. | TYP. | MAX. | Unit |

|---------------------------|----------------------------------------|------|------|------|------|

| Power supply voltage      | Vcc <sup>±</sup> (μPC1663C)            | ±2   | ±6   | ±7   | V    |

| Power supply voltage      | Vcc <sup>±</sup> (μPC1663G, μPC1663GV) | ±2   | ±6   | ±6.5 | ٧    |

| Output source current     | lo source                              |      |      | 20   | mA   |

| Output sink current       | lo sink                                |      |      | 2.5  | mA   |

| Operating frequency range | f <sub>opt</sub>                       | DC   |      | 200  | MHz  |

Table 3. Electrical Characteristics (TA = +25°C, Vcc<sup>±</sup> =  $\pm6$  V)

| Parameter                   |        | Symbol            | Condition                                          | MIN. | TYP. | MAX. | Unit             |

|-----------------------------|--------|-------------------|----------------------------------------------------|------|------|------|------------------|

| Differential voltage gain   | Gain 1 | $A_{\text{vd}}$   | f = 10 MHz (Note 1)                                | 200  | 320  | 500  |                  |

|                             | Gain 2 |                   | f = 10 MHz (Note 2)                                | 8    | 10   | 12   |                  |

| Bandwidth                   | Gain 1 | BW                | Rs = 50 Ω                                          | _    | 120  | 1    | MHz              |

|                             | Gain 2 |                   | (3 dB down point)                                  | _    | 700  | 1    |                  |

| Rise time                   | Gain 1 | tr                | Rs = 50 $\Omega$ , Vout = 1 VP-P                   | _    | 2.9  | ı    | ns               |

|                             | Gain 2 |                   |                                                    | _    | 2.7  | 1    |                  |

| Propagation delay           | Gain 1 | <b>t</b> pd       | Rs = 50 $\Omega$ , Vout = 1 VP-P                   | _    | 2    | l    | ns               |

|                             | Gain 2 |                   |                                                    | _    | 1.2  | 1    |                  |

| Input resistance            | Gain 1 | Rin               |                                                    | _    | 4.0  | l    | kΩ               |

|                             | Gain 2 |                   |                                                    | 50   | 180  | -    |                  |

| Input capacitance           |        | Cin               |                                                    | _    | 2    | 1    | pF               |

| Input offset current        |        | lio               |                                                    | _    | 0.4  | 5.0  | μΑ               |

| Input bias current          |        | lR                |                                                    | _    | 20   | 40   | μΑ               |

| Input noise voltage         |        | $V_n$             | Rs = 50 $\Omega$ , 10 k to 10 MHz                  | _    | 3    | _    | $\mu V_{r.m.s}$  |

| Input voltage range         |        | Vı                |                                                    | ±1.0 | _    | ı    | V                |

| Common mode rejection ratio | Gain 2 | CMR               | $V_{cm} = \pm 1 \text{ V, f} \leq 100 \text{ kHz}$ | 53   | 94   | _    | dB               |

| Supply voltage rejection i  | atio   | SVR               | ∆V = ±0.5 V                                        | 50   | 70   | 1    | dB               |

| Output offset voltage       | Gain 1 | Vo(off)           | $V_{O(off)} =  OUT_1 - OUT_2 $                     | _    | 0.3  | 1.5  | V                |

| Gain 2                      |        |                   |                                                    | _    | 0.1  | 1.0  |                  |

| Output common mode voltage  |        | Vo(cm)            |                                                    | 2.4  | 2.9  | 3.4  | V                |

| Output voltage swing        |        | V <sub>Op-p</sub> | Single end                                         | 3.0  | 4.0  |      | V <sub>P-P</sub> |

| Output sink current         |        | İsink             |                                                    | 2.5  | 3.6  | _    | mA               |

| Power supply current        |        | Icc               |                                                    | _    | 13   | 20   | mÁ               |

Notes 1. Gain 1 is when gain select pins  $G_{1A}$  and  $G_{1B}$  are connected

2. Gain 2 is when none of the gain select pins are connected

**Remark** The detailed specifications and package drawings should be referred to the data sheet (G11024E).

The electrical characteristics are defined as follows.

#### 3.1 Differential Voltage Gain (AVD)

As was described in section 2.2, this indicates the ratio between the differential input and differential output voltage.

$$Av_{D} = \frac{|\varDelta OUT_{1}| + |\varDelta OUT_{2}|}{|\varDelta V_{DIF}|} \quad or \quad \frac{\varDelta |OUT_{1} - \varDelta OUT_{2}|}{|\varDelta V_{DIF}|}$$

The single-end gain (Avs) for single-side output is expressed as one half of Avp shown below.

Avs=

$$\frac{|\Delta OUT_1|}{|\Delta V_{DIF}|}$$

or  $\frac{|\Delta OUT_2|}{|\Delta V_{DIF}|}$

#### 3.2 Bandwidth (BW)

This is defined as the bandwidth when there is a 3-dB down gain (1 /  $\sqrt{2}$ ) in relation to the DC gain.

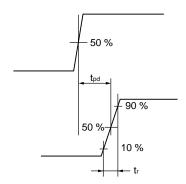

#### 3.3 Rise Time (tr) and Propagation Delay Time (tpd)

These are defined as shown below for this IC.

Figure 5. Measurement Conditions for tpd and tr

#### 3.4 Input Resistance (Rin)

This indicates the ratio of the change in the input bias voltage ( $\Delta I_B$ ) to the change in the input voltage ( $\Delta V_IN$ ).

$$Rin = \Delta Vin/\Delta IB$$

The input resistance is defined as the product of the input transistor's current gain  $\beta$  and the emitter resistance. Therefore, this value is reduced in relation to higher gain values.

#### 3.5 Input Capacitance (Cin)

This indicates the capacitance between the input and the GND.

#### 3.6 Input Offset Current (IIo)

This is the offset current of the dual input bias current.

$$I_{10} = |IB_1 - IB_2|$$

#### 3.7 Input Bias Current (IB)

This indicates the base current at input transistors Q1 and Q2.

#### 3.8 Input Noise Voltage (Vn)

In Figure 6, the value measured by an RF AC voltmeter is divided by the single-end gain value.

Figure 6. Input Noise Voltage Measurement Circuit

#### 3.9 Input Voltage Range (V<sub>I</sub>)

This indicates the input voltage range for normal operation, during which input signals must be within this range. With the intermediate potential between  $Vcc^+$  and  $Vcc^-$  as the center, the input voltage range is guaranteed within  $\pm 1$  V (when  $Vcc^+ - Vcc^- = 12$  V).

#### 3.10 Common Mode Rejection Ratio (CMR)

Figure 7. Common Mode Rejection Ratio Measurement Circuit

This indicates the rate of variation in the input conversion offset relative to the common mode input signal. This can be expressed as follows, based on the circuit shown in Figure 7.

$$CMR = 20 \log \frac{\Delta V_{IN}}{\Delta V_{O}} \cdot A_{VD}$$

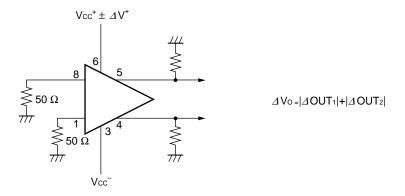

#### 3.11 Supply Voltage Rejection Ratio (SVR)

This indicates the rate of variation in the input conversion offset relative to the supply voltage.

This can be expressed as follows, based on the circuit shown in Figure 8.

$$SVR = 20 \log \frac{\Delta V^{+}}{\Delta Vo} \cdot AVD$$

Figure 8. Supply Voltage Rejection Ratio Measurement Circuit (V\* side)

#### 3.12 Output Offset Voltage (Vo(off))

This indicates the DC voltage difference between both outputs when both of the differential inputs voltage is not applied.

$$V_{O(off)} = |OUT_1 - OUT_2|$$

#### 3.13 Output Common Mode Voltage (Vo(cm))

This indicates the average value from both output's DC voltages when both of the differential inputs voltage is not applied.

$$V_{O(CM)} = \frac{OUT_1 + OUT_2}{2}$$

#### 3.14 Output Voltage Swing (Vop-p)

This indicates the maximum amplitude (swing) that occurs without distortion, mainly in the output common mode voltage.

#### 3.15 Output Sink Current

This indicates the sink current capacity of transistors Q<sub>10</sub> and Q<sub>11</sub>. If a current that exceeds this value is accepted, the output voltage swing is greatly reduced.

#### 3.16 Power Supply Current

This indicates the circuit current and does not include the output load current.

#### 4. PRECAUTIONS FOR DESIGN IN

#### 4.1 Cautions on Layout and Wiring

In high-frequency circuits, the PCB design can considerably influence circuit performance.

When using this device with an especially high gain, you must note that oscillation might occur even when there is only a slight amount of external feedback.

The following cautions concern the device mounting layout.

- Form as wide an area as possible for the ground pattern so as to prevent feedback due to conductor inductance (a double sided copper clad epoxy glass PWB is recommended).

- Make the leads from external components and the link wiring between front and rear components as short as

possible.

- Use a single ground as the ground for input/output circuit and the power supply.

- Form the ground pattern to shield the input and output wiring so as to prevent feedback due to stray capacitance.

- Lay out the output signal current path at a distance from the input wiring.

- The power supply is bypassed very near to the IC's power supply pin by a small-inductance, high-frequency capacitor. If the power supply wiring is long, insert a small resistance (up to 10 Ω) in series.

- The ground for the bypass capacitor should be laid out in order to form a loop only with the power supply line so as to prevent the high-frequency current that runs throughout the PCB from entering the input.

#### 4.2 Cautions on External Circuit

This IC features greatly improved phase characteristics, such that the characteristics inherent to this IC make it one of the more stable wideband amplifier ICs. However, the following cautions should be noted when this IC is used in application circuits.

- Whenever possible, the signal source resistance values should be the same for the two inputs. Signal source

resistance values should be minimized, with 1 kΩ maximum (If the signal source impedance is too large, the

input amplitude becomes large and the output will become saturated).

- Whenever possible, the load resistance values should be the same for the two outputs.

- \* For this IC, it is essential that a balance be maintained between the two lines (IN<sub>1</sub> to OUT<sub>1</sub> and IN<sub>2</sub> to OUT<sub>2</sub>) in the application circuit.

#### 4.3 Other Caution Points

• Use of single (power) supply

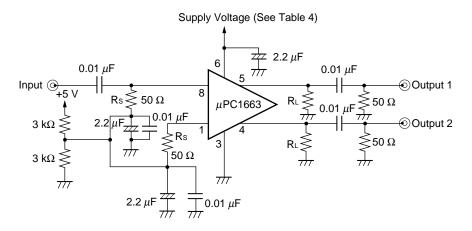

This IC can be used with a single supply if the input voltage is biased at the intermediate between  $Vcc^{-}$  and  $Vcc^{-}$ , as is shown in the application circuit example in the data sheet. More detailed circuit examples and their characteristics are shown in Figure 9 and Tables 4 and 5.

Note, however, that in this case the load current along R<sub>L</sub> is more than twice as great as when the load is connected with  $\pm$  power supply to a ground (recommended: max. 20 mA, lo =  $\frac{V_{O(CM)}}{R_L}$ ).

Figure 9. Example Using Single Power Supply

Table 4. Reference Usage Range

| Parameter      | Symbol                              | Condition           | μPC1663C    | μPC1663G    | μPC1663GV   | Unit |

|----------------|-------------------------------------|---------------------|-------------|-------------|-------------|------|

| Supply voltage | Vcc <sup>+</sup> – Vcc <sup>-</sup> | Single power supply | -0.3 to +16 | -0.3 to +14 | -0.3 to +14 | V    |

Table 5. +5 V Single Power Supply Operation Performance (Based on Figure 9)

| Parameter             |                        | Condition                                      | Characteristics | Unit   |

|-----------------------|------------------------|------------------------------------------------|-----------------|--------|

| Gain                  | Gain 1                 | 15 MHz                                         | 35              | dB     |

|                       | Gain 2                 |                                                | 11              |        |

| Bandwidth             | Gain 1                 | 3 dB down point                                | 106             | MHz    |

|                       | Gain 2                 |                                                | 115             |        |

| Rise time             | Gain 1                 | Rs = 50 Ω, Vout = 80 mV <sub>P-P</sub>         | 2.2             | ns     |

| Propagation delay     | Gain 1                 | Rs = 50 $\Omega$ , Vout = 80 mV <sub>P-P</sub> | 2.8             | ns     |

| time                  | Gain 2                 | Rs = 50 $\Omega$ , Vout = 60 mV <sub>P-P</sub> | 1.8             |        |

| Phase                 | Gain 1                 | 100 MHz                                        | -123            | degree |

|                       | Gain 2                 |                                                | -93             |        |

| Output, Max.          | R <sub>L</sub> = 240 Ω | $R_L = 50 \Omega$                              | 5.0             | dBm    |

|                       | R <sub>L</sub> = 910 Ω | 15 MHz                                         | 0               |        |

| R <sub>L</sub> = 80 Ω |                        |                                                | -11.5           |        |

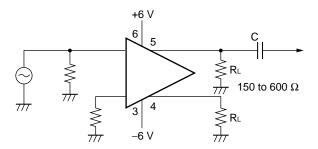

#### • Driving a low-impedance line

As was described in section 3.15 above, the sink current of the IC itself is only 3.6 mA (TYP.), which is inadequate for driving a low-impedance line such as a video line. As is shown in Figure 10, it is possible to drive a low-impedance line if a bypass resistor rated between 150 and 600  $\Omega$  is connected and a capacitor coupling is used to link the increased drive capacity of the output-level emitter-follower.

In this case, the output current (Io =  $(V_{O(CM)} / R_L)$  generated based on the  $R_L$  value should not be more than 20 mA.

Figure 10. Driving a Low Impedance Line

#### 5. APPLICATION CIRCUIT EXAMPLES

#### 5.1 Video Line Driver Circuit Example

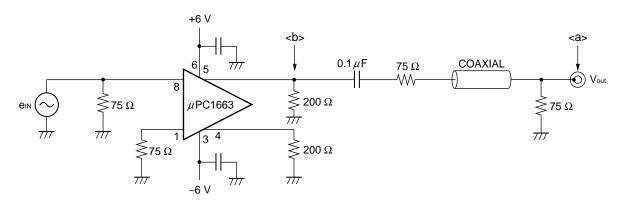

Figure 11. Video Line Driver Circuit Example

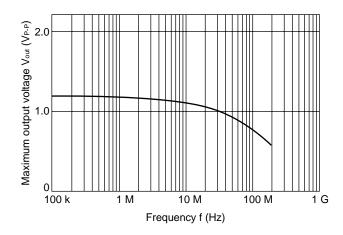

Figure 12. Vout vs. f Characteristics (Video Line, Single End)

Remark The measurement results in Figure 12 are the values of point <a> in Figure 11 of the application circuit. The values for the  $\mu$ PC1663 are those of point <br/>b>, therefore when converted, they are equivalent to approximately twice the value of Vout at point <a>>. Because the measured values at point <a> are single-end, in the case of differential I/O, the values of points <a> and <b> are twice the value of the singleend values.

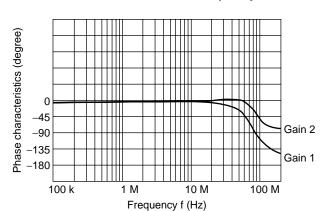

Figure 13. Phase Characteristics vs. Frequency Characteristics

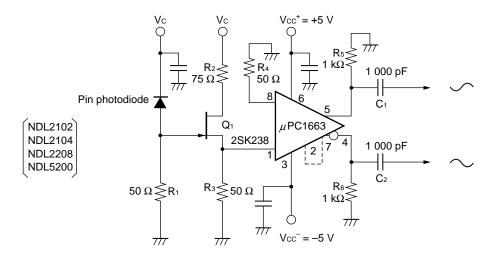

### 5.2 Optical Signal Detection Circuit Example

Figure 14. Optical Signal Detection Circuit Example

Since a high gain value may lower the IC's input impedance, stable operation can be ensured by including an FET buffer (source follower), as is shown in Figure 14. This FET buffer also shifts the level of the input voltage from the diode. For detail on the FET and PIN photodiode, see the data sheet for each product.

#### 6. EXAMPLE OF MOUNTING MEASURING CIRCUIT ON PRINTED BOARD

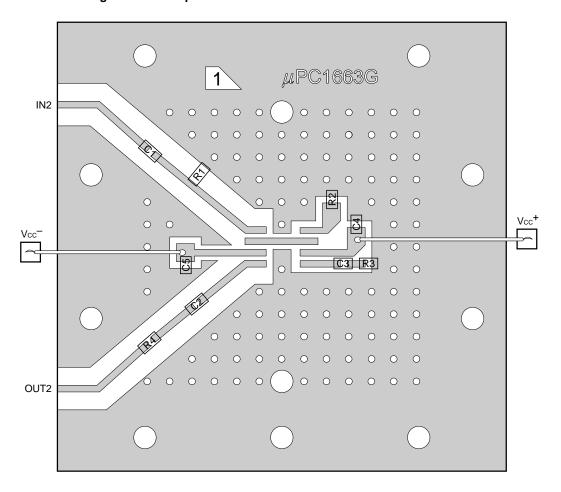

### 6.1 Example of Mounting $\mu$ PC1663G on Printed Board

Figure 15 shows an example of mounting of 8-pin SOP 225-mil type product on a PCB for use in the test circuit described in the  $\mu$ PC1663 data sheet. The evaluation board in Figure 15 is designed for single-end test circuit of IN2 input and OUT2 output.

Figure 15. Example of assembled test Circuit on Evaluation Board

#### **Parts Table**

| No.     | Value   |

|---------|---------|

| C1 to 3 | 0.1 μF  |

| C4 to 5 | 1000 pF |

| R1 to 2 | 50 Ω    |

| R3      | 1 kΩ    |

| R4      | 950 Ω*  |

#### **Notes on Printed Board**

- (\*1) 35- $\mu$ m copper patterning on both sides of 50  $\times$  50  $\times$  0.4-mm polyimide board

- (\*2) Rear side ground pattern

- (\*3) Solder plating of patterning side

- (\*4)  $\circ$  O is through-hole.

- (\*5) To mount C2, pattern should be cut.

<sup>\*</sup> R4 is the value obtained by subtracting the impedance of the measuring instrument from R3.

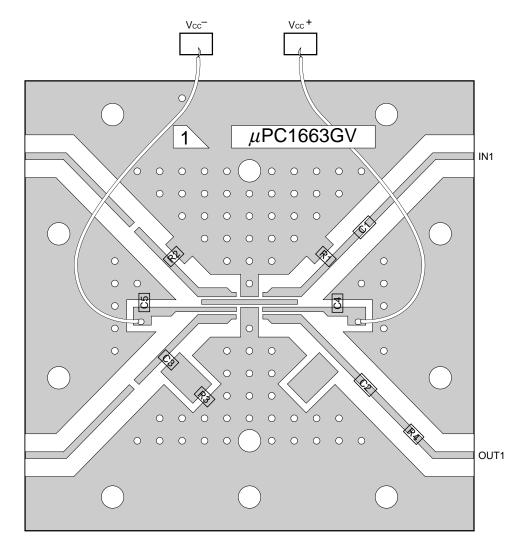

#### 6.2 Example of Mounting $\mu$ PC1663GV on Printed Board

Figure 16 shows an example of mounting of 8-pin SSOP 175-mil type product on a PCB for use in the test circuit described in the  $\mu$ PC1663 data sheet. This evaluation board can be used either for a single-end or differential amplifier. The assembled example in Figure 16 is for a single-end amplifier and provides one IN1 and one OUT1 pins.

Figure 16. Example of assembled test Circuit on Evaluation Board

#### **Parts Table**

| No.     | Value   |

|---------|---------|

| C1 to 3 | 0.1 μF  |

| C4 to 5 | 1000 pF |

| R1 to 2 | 50 Ω    |

| R3      | 1 kΩ    |

| R4      | 950 Ω*  |

#### **Notes on Printed Board**

- (\*1) 35- $\mu$ m copper patterning on both sides of 50  $\times$  50  $\times$  0.4-mm polyimide board

- (\*2) Rear side ground pattern

- (\*3) Solder plating of patterning side

- (\*4) ∘ O is through-hole.

- (\*5) To mount R4, pattern should be cut.

<sup>\*</sup> R4 is the value obtained by subtracting the impedance of the measuring instrument from R3.

#### 7. CONCLUSION

The usage of the  $\mu$ PC1663 DC to VHF wideband differential input and output amplifier IC has been described above.

Another product that uses a high-frequency process, the  $\mu$ PC2726T, is also offered as an L-band differential input and differential output wideband amplifier IC that operates up to 1.6 GHz.

### **Reference Materials**

$\mu$ PC1663 Data Sheet (Document No. G11024E)  $\mu$ PC2726T Data Sheet (Document No. P10873E)

to our customers is complete, bug free

# Facsimile Message Although NEC has taken all possible steps to ensure that the documentation supplied to our customers is complete, bug free

| From                   | 1:                                                                               |                                                                             | and up-to-date, we readily accept that errors may occur. Despite all the care and precautions we©vetaken, you may |                                                                                                                                    |               |      |  |  |

|------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------|------|--|--|

| Name                   |                                                                                  |                                                                             |                                                                                                                   | encounter problems in the documentation Please complete this form wheneve you@dlike to report errors or sugges improvements to us. |               |      |  |  |

| Compa                  | any                                                                              |                                                                             |                                                                                                                   |                                                                                                                                    |               |      |  |  |

| Tel.                   |                                                                                  | FAX                                                                         |                                                                                                                   |                                                                                                                                    |               |      |  |  |

| Addres                 | ss                                                                               |                                                                             |                                                                                                                   |                                                                                                                                    |               |      |  |  |

|                        |                                                                                  |                                                                             |                                                                                                                   | Thank you for yo                                                                                                                   | our kind supp | ort. |  |  |

| NEC I<br>Corpo<br>Fax: | America Electronics Inc. brate Communications Dept 1-800-729-9288 1-408-588-6130 | NEC Electronics I                                                           |                                                                                                                   | Asian Nations except I<br>NEC Electronics Singap<br>Fax: +65-250-3583                                                              |               |      |  |  |

| Techr                  | oe<br>Electronics (Europe) GmbH<br>nical Documentation Dept.<br>+49-211-6503-274 | Korea<br>NEC Electronics Hong Kong Ltd.<br>Seoul Branch<br>Fax: 02-528-4411 |                                                                                                                   | Japan NEC Corporation Semiconductor Solution Engineering Division Technical Information Support Dept. Fax: 044-548-7900            |               |      |  |  |

| NEC (                  | n <b>America</b><br>do Brasil S.A.<br>+55-11-6465-6829                           | Taiwan NEC Electronics Fax: 02-719-595                                      |                                                                                                                   |                                                                                                                                    |               |      |  |  |

| l woul                 | d like to report the folk                                                        | owing error/make                                                            | the following s                                                                                                   | uggestion:                                                                                                                         |               |      |  |  |

| Docur                  | nent title:                                                                      |                                                                             |                                                                                                                   |                                                                                                                                    |               |      |  |  |

| Docur                  | nent number:                                                                     |                                                                             |                                                                                                                   | Page number: _                                                                                                                     |               |      |  |  |

|                        |                                                                                  |                                                                             |                                                                                                                   |                                                                                                                                    |               |      |  |  |

|                        |                                                                                  |                                                                             |                                                                                                                   |                                                                                                                                    |               |      |  |  |

| If poss                | sible, please fax the re                                                         | ferenced page or                                                            | drawing.                                                                                                          |                                                                                                                                    |               |      |  |  |

|                        | Document Rating                                                                  | Excellent                                                                   | Good                                                                                                              | Acceptable                                                                                                                         | Poor          |      |  |  |

|                        | Clarity                                                                          |                                                                             |                                                                                                                   |                                                                                                                                    |               |      |  |  |

|                        | Technical Accuracy                                                               |                                                                             |                                                                                                                   |                                                                                                                                    |               |      |  |  |

|                        | Organization                                                                     |                                                                             |                                                                                                                   |                                                                                                                                    |               |      |  |  |