January 1996

#### DESCRIPTION

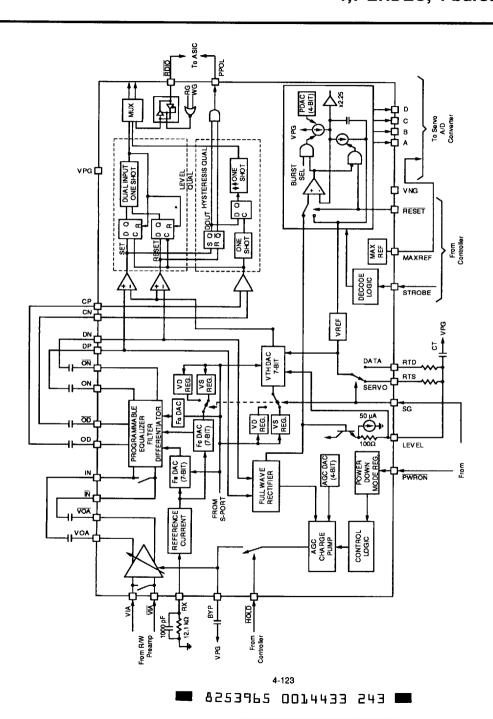

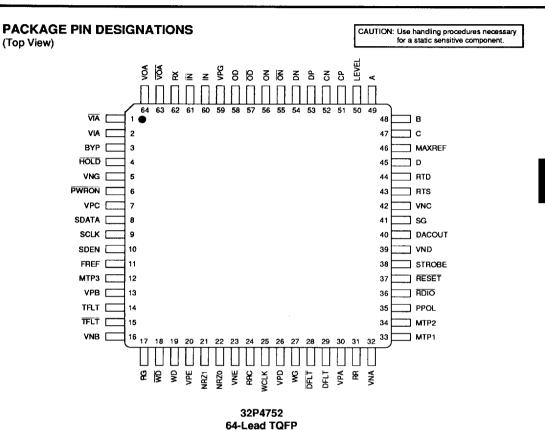

The SSI 32P4752 devices are high performance BiCMOS single chip read channel ICs that contain all the functions needed to implement a complete zoned recording read channel for hard disk drive systems. Functional blocks include the pulse detector, programmable filter, 4-burst servo capture, time base generator, and data separator with 1,7 RLL ENDEC. Data rates from 18 to 64 Mbit/s can be programmed using an internal DAC whose reference current is set by a single external resistor. For reduced clocking speeds, the 32P4752 employs a dual-bit parallel interface to the controller.

Programmable functions of the SSI 32P4752 devices are controlled through a bi-directional serial port and banks of internal registers. This allows zoned recording applications to be supported without changing external component values from zone to zone.

The SSI 32P4752 utilize an advanced BiCMOS process technology along/ with advanced circuit design techniques which result in high performance devices with low power consumption.

#### **FEATURES**

#### **GENERAL:**

- DAC controlled programmable data rates from 18 to 64 Mbit/s

- Complete zoned recording application support

- Low power operation < 600 mW typical at 5V</li>

- Bi-directional serial port for register access

- Register programmable power management (sleep mode <0.5 mA)

- Power supply range (4.5 to 5.5V)

- Small footprint 64-lead TQFP package

#### **PULSE DETECTOR:**

- Fast attack/decay modes for rapid AGC recovery

- Dual rate charge pump for fast transient recovery

- Low Drift AGC hold circuitry

- Temperature compensated, exponential control AGC

- Wide bandwidth, high precision full-wave rectifier (continued)

# BLOCK DIAGRAM VIA ACC PHOD HOLD HOLD

■ 8253965 0014383 998 ■

#### FEATURES (continued)

#### PULSE DETECTOR: (continued)

- Dual mode pulse qualification circuitry (user selectable)

- CMOS RDIO signal output for servo timing support

- · Internal LOW-Z and fast decay timing

- 0.6 ns max. pulse pairing at 64 Mbit/s using a 6 MHz sine wave input

#### **SERVO CAPTURE:**

- 4-burst servo capture with A, B, C, D outputs

- Internal hold capacitors

- Separate registers for fc and VTH during servo mode

- 4-bit DAC for AGC level control (0.8 to 1.2 Vp-p)

#### PROGRAMMABLE FILTER:

- Programmable cutoff frequency of 9 to 27 MHz

- Programmable group delay equalization with asymmetrical zero

- Programmable boost/equalization of 0 to 13 dB

- Matched normal and differentiated outputs

- ± 15% fc accuracy

- ± 2% maximum group delay variation to fc

- · Less than 1.5% total harmonic distortion

- Low-Z input switch

- No external filter components required

#### TIME BASE GENERATOR:

- Better than 1% frequency resolution

- Up to 96 MHz frequency output

- Independent M and N divide-by registers

- VCO center frequency matched to data synchronizer VCO

#### **DATA SEPARATOR:**

- Fast acquisition phase lock loop with zero phase restart technique

- · Dual-bit NRZ interface

- Integrated 1.7 RLL Encoder/Decoder

- Programmable decode window symmetry control via serial port

- Window shift control 33% (4-bit)

- Includes delayed read data and VCO clock monitor points

- Programmable early/late write precomp (3-bits each)

- Differential PECL write data output

- Hard sector operation

- VCO and Synchronized Read Data test points

#### **FUNCTIONAL DESCRIPTION**

The SSI 32P4752 implement a high performance complete read channel, including pulse detector, 4-burst servo capture, programmable active filter, time base generator, and data separator with 1,7 RLL ENDEC, at data rates up to 64 Mbit/s.

#### PULSE DETECTOR CIRCUIT DESCRIPTION

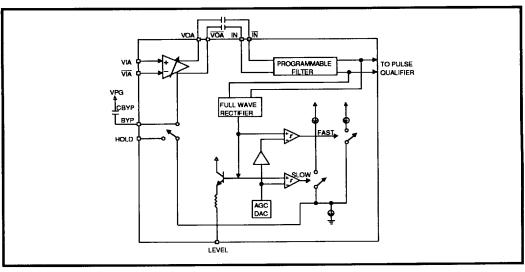

The pulse detector, in conjunction with the programmable filter, provides all the data processing functions necessary for detection and qualification of encoded read signals. The signal processing circuits include a wide band variable gain amplifier; a wide bandwidth, high precision fullwave rectifier; and a dual rate charge pump. The entire signal path is fully-differential to minimize external noise pick up.

#### AGC CIRCUIT

The gain of the AGC amplifier is controlled by the voltage (VBYP) stored on the BYP hold capacitor (CBYP), Figure 1. A dual rate charge pump drives CBYP with currents that depend on the instantaneous differential voltage at the DP/DN pins. Attack currents lower VBYP which reduces the amplifier gain, while decay currents increase Very which increases the amplifier gain. When the signal at DP/DN is greater than 100% of the programmed AGC level, the nominal attack current of 0.17 mA is used to reduce the amplifier gain. If the signal is greater than 125% of the programmed AGC level, a fast attack current of eight (8) times nominal is used to reduce the gain. This dual rate approach allows AGC gain to be quickly decreased when it is too high yet minimizes distortion when the proper AGC level has been acquired.

A constant decay current of 4  $\mu$ A increases the amplifier gain when the signal at DP/DN is less than the programmed AGC level. The large ratio (0.17 mA:4  $\mu$ A) of the nominal attack and nominal decay currents enables the AGC loop to respond to the peak amplitudes of the incoming read signal rather than the average value.

4-74

8253965 0014384 824 🖿

FIGURE 1: AGC Block

#### **AGC MODE CONTROL**

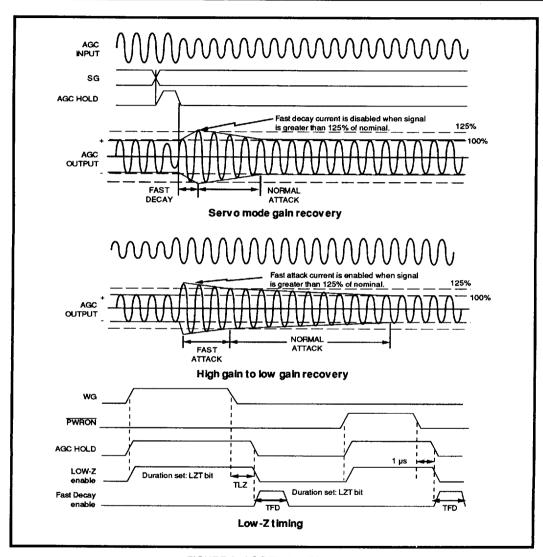

When write gate (WG) is driven high, the dual rate charge pump is disabled causing the AGC amplifier gain to be held constant. The input impedance of both the AGC amplifier and the programmable filter is reduced. When the WG pin transitions from high to low, the Low-Z mode is activated. In this mode, the input impedance at both the AGC amplifier and the programmable filter remain low to allow for quick recovery of the AC coupling capacitors. Directly following the Low-Z mode is the fast decay mode which allows rapid acquisition of the proper AGC level. In fast decay mode, an internal FET is switched on to drive a high current into the BYP pin. The current remains active until the signal at DP/DN is above 125% of the nominal amplitude, or until an internal timer expires. After the fast decay current is disabled, the normal AGC sequence is enabled. The duration of both the Low-Z and fast Decay modes can be set to either 1 µs or 2 µs by programming bit D7 in the write precomp register. A fast decay sequence is also initiated on the edges of servo gate (SG). Each edge of SG triggers a 400 ns (typ.) AGC hold period to allow the filter to settle. The fast decay current is enabled at the end of the HOLD period. When the pulse detector is powered-down,

VBYP will be held constant subject to leakage currents only. Upon power-up, the Low-Z/fast decay sequence is executed to rapidly recover from any transients or driftwhich may have occurred on the BYP hold capacitor, Figure 2.

External control for enabling the dual rate charge pump is also provided. Driving the HOLD pin low forces the dual rate charge pump output current to zero. In this mode, VBYP will be held constant subject only to leakage currents.

#### **RDIO** Output Pin

A TTL compatible inverted Read Data I/O (RDIO) is provided to monitor the pulse detector output. This pin will be held high when SG is low and either RG or WG are high to reduce noise and accompanying jitter during read or write modes. Its falling edge indicates the occurrence of valid data pulse.

4-75

FIGURE 2: AGC Timing Diagrams

<sup>4-76</sup> ■ A253965 DO14386 6T? ■

#### FUNCTIONAL DESCRIPTION (continued)

#### **QUALIFIER SELECTION**

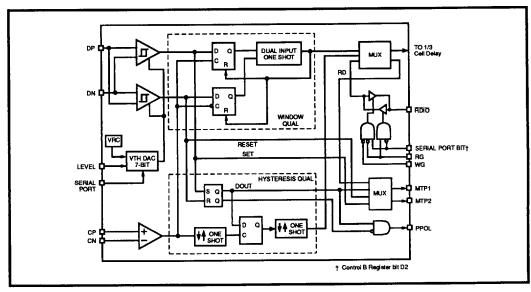

The 32P4752 provide both hysteresis and dual comparator pulse qualification circuits that may be independently selected for read mode and servo mode operation, Figure 3. For read mode operation the pulse qualifier method is selected by setting the MSB in the data threshold control register (DTCR). The lower 7 bits of the DTCR also set the hysteresis level of the

comparators for read mode. For servo mode operation the pulse qualifier method is selected by setting the MSB in the servo threshold control register (STCR). The lower 7 bits of the STCR set the hysteresis level of the comparators for servo mode:

Qualification threshold% = (84.5 • VTHDAC/127) - 2.17% (48 ≤ VTHDAC ≤ 127)

where

VTHDAC = DTCR or STCR value

FIGURE 3: Pulse Qualification

#### FUNCTIONAL DESCRIPTION (continued)

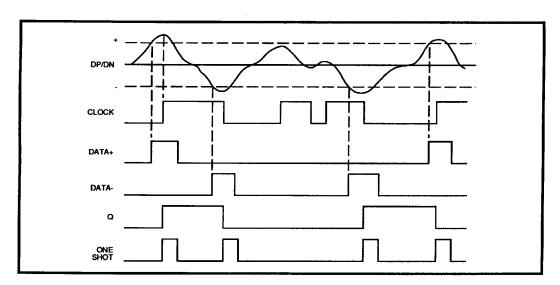

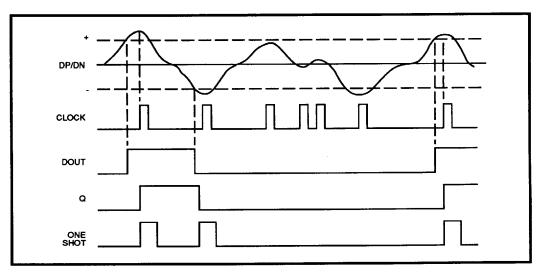

#### HYSTERESIS COMPARATOR QUALIFICATION

When the Hysteresis Qualification mode is selected, the same threshold qualification comparators and clock comparators are used to implement a polarity checking rule. In this mode, a positive peak that clears the established threshold level will set the SR Flip-Flop and trigger the bidirectional one-shot that creates the read data pulses. In order to get another pulse clocked out, a peak of the opposite polarity must clear the negative threshold level to reset the SR Flip Flop and trigger the bidirectional one-shot, Figure 5.

#### **DUAL COMPARATOR QUALIFICATION**

When in Dual Comparator mode, independent positive and negative threshold qualification comparators are used to suppress the error propagation of a positive and negative threshold comparator. However a slight amount of hysteresis is included to increase the comparator output time when a signal that just exceeds the threshold level is detected. This eases the timing with respect to the zero crossing clock comparator. A differential comparator with programmable threshold

allows differential signal qualification for noise rejection. The programmable threshold, VTH, is driven by a multiplying DAC which is driven by the LEVEL voltage and referenced to VRC (VRC is the internal bandgap reference). Thresholds from 30 to 80% may be set with a resolution of better than 1%. A parallel R-C network of RTD and CT sets the threshold time constant when not in the servo mode. A qualified signal zero crossing at the CP-CN inputs triggers the output one shot, Figure 4.

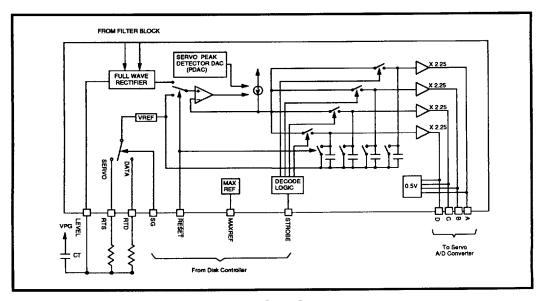

#### SERVO DEMODULATOR CIRCUIT DESCRIPTION

The 32P4752 servo sections capture four separate servo bursts and provide A, B, C, and D burst outputs, Figure 6. Internal burst hold capacitors are provided to support low leakage burst capture and reduce external component count. To support embedded servo applications, the 32P4752 provide additional programming registers that set the filter cutoff frequency (fc) and the hysteresis threshold level (VTH) for servo mode. When SG is activated or deactivated there is a nominal 0.3  $\mu$ s settling time for the internal DACs to recover from the register switching.

FIGURE 4: Dual Comparator Timing Diagram (Refer to Figure 3: Level Qualification Section)

4-78

**■** 8253965 0014388 47T **■**

FIGURE 5: Hysteresis Comparator Timing Diagram

FIGURE 6: Servo Capture

4-79

**8253965 0014389 306**

#### FUNCTIONAL DESCRIPTION (continued)

#### **SERVO MODE OPERATION**

When the servo gate (SG) is asserted, the control DACs for fc and VTH switch from the data mode registers to the servo mode registers and the AGC goes into the HOLD/fast decay mode. In addition, filter boost is disabled (as determined by the boost control bit), the AGC level is adjusted according to the AGC Level DAC and the RTS servo time constant setting resistor is connected to VRC (VRC is the internal bandgap reference.) By disabling the boost and providing the servo control register for fc the servo signal to noise ratio can be greatly improved. When SG is activated or deactivated there is a nominal 0.3 µs settling time for the internal DACs to recover from the register switching. During serve mode, the AGC circuit remains active. A 4-bit DAC (DACA) is used to set the AGC level over a range of 0.80 to 1.20 Vp-p as follows:

VAGC = 1.2 - (DACA • 0.02668) Vp-p where DACA is the value of the AGC Level register

Typically, a servo preamble is used to achieve the desired AGC level and then the  $\overline{\text{HOLD}}$  pin is asserted to hold the AGC gain. When SG goes low to terminate the servo mode, the AGC goes into the HOLD (0.4  $\mu$ s)/fast decay (1  $\mu$ s) mode to allow for fast transition into the read or write mode.

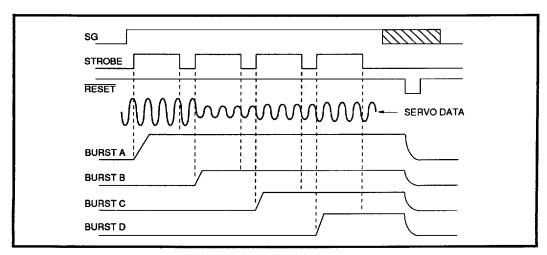

#### **BURST CAPTURE**

The 32P4752 burst capture is controlled by a single external pin designated STROBE and an internal counter. When SG is active, the first pulse on the STROBE pin gates the output of the servo peak detector to the A burst hold capacitor. The capacitor charges for as long as the STROBE pulse is high. On the falling edge of the STROBE signal, the internal counter is incremented. The next STROBE pulse will then gate the servo peak detector output to the B burst hold capacitor, Again, the capacitor charges for as long as the STROBE pulse is high. On the falling edge of STROBE, the counter is incremented again and the C burst is captured on the next STROBE pulse. On the next falling edge of STROBE, the counter is incremented again and the D burst is captured on the next STROBE pulse. After the falling edge of the fourth STROBE pulse, the counter is reset to zero and the burst capture process can be repeated. See Figure 7 for timing information. The internal counter is also reset when the SG pin is deactivated. The voltage level on each hold capacitor is then provided to buffer amplifiers which generate the servo output signals. A 1 Vp-p differential voltage at the DP/DN pins will result in a 2.15V peak burst amplitude. The servo output signals (A, B, C, D) are referenced above an internal baseline of 0.5V. The output voltage at the MAXREF pin is a nominal 3.1V, and represents the maximum voltage to

FIGURE 7: Servo Capture Timing Diagram

4-80

8253965 0014390 028

#### **BURST CAPTURE** (continued)

which the servo signal outputs will swing. It is typically used as the reference voltage for an external A/D converter. MAXREF is internally reduced to a 0.5 volt level, and establishes the servo zero-signal baseline.

All four internal burst hold capacitors are discharged when the RESET pin is driven low. The RESET control input overrides the STROBE signals. The 32P4752 has high-resolution, bi-directional current reset in which the capacitor baseline voltage will be equal to the zero-signal baseline voltage.

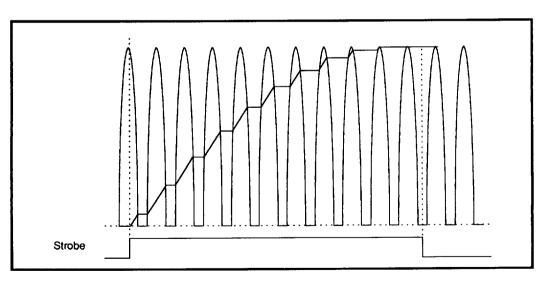

The drive current of the servo peak detector charge pump is set by a 4-bit word (DACP) addressed through the serial port. The LSB value is  $6 \mu A$ , and the offset is

1 LSB such that "0000" corresponds to 6  $\mu$ A and "1111" results in 96  $\mu$ A. Maximum noise immunity is obtained in the servo peak detector by choosing the smallest value of charge current to charge the internal 10 pF hold capacitor during the burst acquisition time, see Figure 8.

Table 1 shows the recommended IDAC settings as a function of the strobe command duration to achieve acquisition to 99.5% of intended final value. These values are calculated with Fservo = 6.66 MHz at DP/DN.

The peak detector exhibits constant gain for inputs at DP/DN from 0.2 to 1.2 Vp-p with small non-linearities below 0.2V.

**TABLE 1: IDAC Settings vs Strobe Time**

| PDAC Word:        | 0000 | 00001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 |

|-------------------|------|-------|------|------|------|------|------|------|------|

| Strobe Time (µs): | 6.8  | 4.8   | 3.4  | 2.1  | 1.5  | 1.2  | 0.83 | 0.77 | 0.74 |

| PDAC Word:        | 1001 | 1010  | 1011 | 1100 | 1101 | 1110 | 1111 | -    |      |

| Strobe Time (µs): | 0.71 | 0.68  | 0.66 | 0.64 | 0.63 | 0.62 | 0.61 |      |      |

FIGURE 8: Servo Burst Aquisition (SG = RESET = 1)

4-81

■ 8253965 0014391 T64 |

#### FUNCTIONAL DESCRIPTION (continued)

#### TIMING OUTPUTS

To support servo timing recovery, the pulse detector section provides a TTL output of the servo information via the RDIO pin. A negative pulse is generated for each servo peak that is qualified through the pulse detector circuitry. Additional servo timing information is supported by the PPOL output. The PPOL pin provides pulse polarity information for the qualified peaks, where a high level TTL output indicates a positive pulse. To reduce noise progagation, RDIO will be held high and PPOL will be held low when SG is low and either RG or WG are high.

#### PROGRAMMABLE FILTER CIRCUIT DESCRIPTION

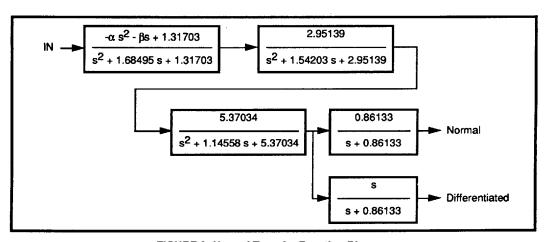

The SSI 32P4752 include a programmable filter which consists of a normal output and a separate time-differentiated output. The normal low-pass output is of a seven-pole two-real-zero type. With a zero placed at the origin, the filter also provides the time-differentiated output to be used in time qualification of the data qualifier circuit. To ease the timing requirement in peak detection of signals slightly above the qualification threshold, the time-differentiated output is purposely delayed by 1.2 ns relative to the normal output. The normalized transfer functions are shown in Figure 9.

While the cutoff frequency is scaled by replacing s with  $s/2\pi fc$ , the boost and group delay equalization are controlled by varying the values of a and b. Both outputs have matched group delays (<1 ns typical.) The group delay matching is unaffected by any amount of programmed equalization or bandwidth. Programmable bandwidth and boost/equalization are provided by internal 7-bit control DACs. The programmable characteristics are automatically switched during servo mode to improve signal to noise ratio. Differentiation pulse slimming equalization which does not affect the filter's group delay response, is accomplished by a two-pole low-pass with a two-pole high-pass feed forward section to provide complimentary real axis zeros. A variable attenuator is used to program the zero locations. The filter implements a 0.05 degree equiripple linear phase response.

#### **FILTER OPERATION**

AC coupled differential signals from the AGC amplifier are applied to the IN/IN inputs of the filter. To improve settling time of the coupling capacitors, the IN/IN inputs are placed into a Low-Z state for 1 µs when WG goes inactive or when the PWRON pin is brought low. The programmable bandwidth and boost/equalization features are controlled by internal DACs and the

FIGURE 9: Normal Transfer Function Diagram

4-82

🖿 8253965 QQ14392 9TQ 🖿

registers programmed through the serial port. The current reference for both DACs is set using a single external resistor connected from pin RX to ground. The voltage at pin RX is proportional to absolute temperature (PTAT), hence the current for the DACs is a PTAT reference current. A 1000 pF capacitor should be connected in parallel with RX to reduce harmonic distortion.

#### **BANDWIDTH CONTROL**

The programmable bandwidth is set by the filter cutoff DAC. This DAC has two separate 7-bit registers that can program the DAC value as follows:

$fc = Fc = 0.2223 \cdot DACF - 1.2348 (46 \le DACF \le 127)$

where DACF = DMCR or SMCR value

In the data mode, the Data Mode Cutoff Register (DMCR) is used to determine the filter's unboosted 3 dB cutoff frequency fc. This is the -3 dB frequently with both  $\alpha$  and  $\beta$  equal to 0. In the servo mode, the Servo Mode Cutoff Register (SMCR) is used. Switching of the registers is controlled by the servo gate (SG) pin. The filter cutoff set by the internal DAC is the unboosted 3 dB frequency. When boost/equalization is added, the actual -3 dB point will move out. The ratio of the actual -3 dB cutoff frequency to the programmed cutoff frequency as a function of alpha boost and group delay variation  $\Delta\%$  is tabulated in Table 2.

#### **BOOST/EQUALIZATION CONTROL**

Boost is defined as the amount of peaking in the magnitude response at the cutoff frequency due to  $\alpha \neq 0$  and/ or  $\beta \neq 0$ .

Alpha boost ( $\alpha \neq 0$ ,  $\beta = 0$ ) does not affect the filter's group delay response. In general, the actual boost with group delay equalization is higher than the alpha boost. However, with alpha boost > 3 dB the difference is minimal. The 7-bit Filter Boost Control Register (FBCR) determines the amount of alpha boost that will be added to the -3 dB cutoff frequency, as follows:

Alpha Boost =

20 log [(0.025 • FBCR + 0.000039 • FBCR • DACF) + 1]dB (0 ≤ DACS ≤ 127)

where DACF is the filter cutoff register

For example, with the DAC set for maximum output (FBCR = 7F or 127) there will be 13 dB of boost added at the unboosted -3 dB frequency. This will result in

+10 dB of signal boost above the 0 dB baseline. When SG is active the boost can be disabled by setting bit 7 in FBCR. When bit 7 is "0" and SG is active the boost will automatically be set to 0 dB. If bit 7 is "1" the boost will remain at its programmed value regardless of the state of SG.

By applying group delay equalization  $(\alpha=0,\,\beta\neq0)$  the group delay response of the filter can be altered. The group delay  $\Delta\%$  is defined as the percentage change in absolute group delay value at DC with respect to that without the equalization applied  $(\beta\neq0).$  The group delay  $\Delta\%$  at low frequencies can be programmed between -30% and +30% by the 8-bit Filter Group Delay Control Register (FGCR), with the MSB acting as a sign bit, as follows:

Group Delay  $\Delta\%$  = -0.2362 • DACG • 100% (0  $\leq$  DACG  $\leq$  127), or

Group Delay  $\Delta$ % = 0.2362 • (DACG - 128) • 100% (128 ≤ DACG ≤ 255)

Where DACG is the FGCR value

When SG is active the beta boost is controlled by setting bit 7 in SMCR. When bit 7 is "0" and SG is active the beta boost will automatically be set to 0 dB. It bit 7 is "1" the beta boost will remain at its programmed value regardless of the state of S.

When both  $\alpha \neq 0$ ,  $\beta \neq 0$ , the total amount of boost is largely dominated by the alpha only, particularly when alpha boost is  $\geq 3$  dB. Table 3 lists the actual boost as a function of the applied alpha boost and group delay equalization.

4-83

8253965 0014393 837 1

TABLE 2: Ratio of Actual -3 dB Bandwidth to Cutoff Frequency

| ALPHA |      |      | G    | roup Delay A | \%   |      | * .*** |

|-------|------|------|------|--------------|------|------|--------|

| BOOST | ±30% | ±25% | ±20% | ±15%         | ±10% | ±5%  | 0.00   |

| 0 DB  | 1.58 | 1.45 | 1.30 | 1.17         | 1.07 | 1.02 | 1.00   |

| 1     | 1.67 | 1.57 | 1.47 | 1.36         | 1.27 | 1.21 | 1.19   |

| 2     | 1.78 | 1.71 | 1.64 | 1.56         | 1.50 | 1.46 | 1.44   |

| 3     | 1.90 | 1.85 | 1.80 | 1.76         | 1.72 | 1.70 | 1.69   |

| 4     | 2.01 | 1.98 | 1.96 | 1.93         | 1.91 | 1.90 | 1.90   |

| 5     | 2.13 | 2.11 | 2.09 | 2.08         | 2.07 | 2.06 | 2.06   |

| 6     | 2.23 | 2.22 | 2.21 | 2.20         | 2.20 | 2.20 | 2.20   |

| 7     | 2.33 | 2.32 | 2.32 | 2.31         | 2.31 | 2.31 | 2.31   |

| 8     | 2.42 | 2.41 | 2.41 | 2.41         | 2.41 | 2.40 | 2.40   |

| 9     | 2.50 | 2.50 | 2.50 | 2.49         | 2.49 | 2.49 | 2.49   |

| 10    | 2.58 | 2.58 | 2.58 | 2.58         | 2.57 | 2.57 | 2.57   |

| 11    | 2.66 | 2.65 | 2.65 | 2.65         | 2.65 | 2.65 | 2.65   |

| 12    | 2.73 | 2.73 | 2.73 | 2.73         | 2.73 | 2.73 | 2.73   |

| 13    | 2.80 | 2.80 | 2.80 | 2.80         | 2.80 | 2.80 | 2.80   |

TABLE 3: Actual Boost vs Alpha Boost & Group Delay Change

| ALPHA |       | Group Delay ∆% |       |       |        |       |       |  |

|-------|-------|----------------|-------|-------|--------|-------|-------|--|

| BOOST | ±30%  | ±25%           | ±20%  | ±15%  | ±10%   | ±5%   | 0.00  |  |

| 0 DB  | 2.92  | 2.21           | 1.54  | 0.93  | 0.44   | 0.12  | 0.00  |  |

| 1     | 3.46  | 2.84           | 2.27  | 1.76  | 1.35   | 1.09  | 1.00  |  |

| 2     | 4.05  | 3.52           | 3.03  | 2.61  | . 2.28 | 2.07  | 2.00  |  |

| 3     | 4.26  | 4.25           | 3.84  | 3.49  | 3.23   | 3.06  | 3.00  |  |

| 4     | 5.40  | 5.02           | 4.68  | 4.40  | 4.18   | 4.05  | 4.00  |  |

| 5     | 6.15  | 5.83           | 5.55  | 5.32  | 5.15   | 5.04  | 5.00  |  |

| 6     | 6.94  | 6.67           | 6.44  | 6.25  | 6.12   | 6.03  | 6.00  |  |

| 7     | 7.76  | 7.54           | 7.36  | 7.20  | 7.09   | 7.02  | 7.00  |  |

| 8     | 8.61  | 8.44           | 8.28  | 8.06  | 8.07   | 8.02  | 8.00  |  |

| 9     | 9.50  | 9.35           | 9.22  | 9.13  | 9.06   | 9.02  | 9.00  |  |

| 10    | 10.38 | 10.27          | 10.17 | 10.10 | 10.04  | 10.01 | 10.00 |  |

| 11    | 11.30 | 11.21          | 11.14 | 11.08 | 11.03  | 11.01 | 11.00 |  |

| 12    | 12.24 | 12.17          | 12.11 | 12.06 | 12.03  | 12.01 | 12.00 |  |

| 13    | 13.19 | 13.14          | 13.09 | 13.05 | 13.02  | 13.01 | 13.00 |  |

FIGURE 10: Time Base Generator Phase Locked Loop

#### FUNCTIONAL DESCRIPTION (continued)

#### TIME BASE GENERATOR CIRCUIT DESCRIPTION

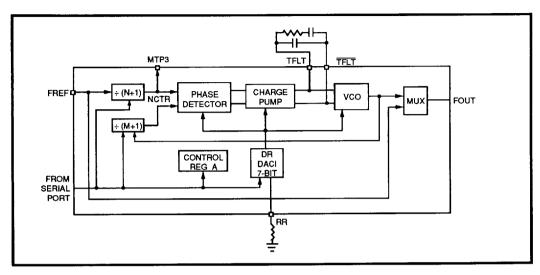

The time base generator, which is a PLL based circuit, provides programmable reference frequency FOUT, Figure 10. The frequency can be programmed with an accuracy better than 1%. An external passive loop filter is required to control the PLL locking characteristics. The filter is fully-differential and balanced in order to suppress common mode noise.

In read, write and idle modes, the time base generator is programmed to provide a stable reference frequency (FOUT) for the data synchronizer. In write and idle modes, FOUT is the output of the time base generator. In read mode FOUT is disabled after the data synchronizer has achieved lock and switched over to read data as the source for the RRC. This minimizes jitter in the data synchronizer PLL. The reference frequency is programmed using the M and N registers of the time base generator via the serial port, and is related to the external reference clock input, FREF, as follows:

$$FOUT = ((M+1)/(N+1))FREF$$

The VCO center frequency and the phase detector gain of the time base generator are controlled by an

internal IDAC addressed through the Data Recovery Control Register (DRCR). To change the FOUT frequency, new values are preloaded into the M and N registers via the serial port. Acquisition of the new frequency begins only after a write operation is completed to the DRCR. To insure precise tracking of the data separator to the time base VCO, the control voltage from the VCO is converted to a current which is provided to the data separator VCO and 1/3 cell delay. The VCO frequency equation is:

Fvco =  $[12.5/(RR + 0.4)] \cdot [(0.715 \cdot IDAC) + 6.8]$  MHz =  $1.5 \cdot NRZ$  data rate.  $(28 \le IDAC \le 127)$

where IDAC is the value in the DRCR and RR is the value (k $\Omega$ ) of the external RR resistor.

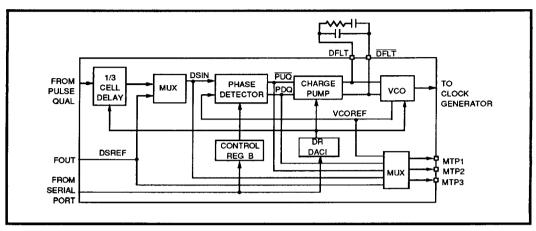

#### DATA SEPARATOR CIRCUIT DESCRIPTION

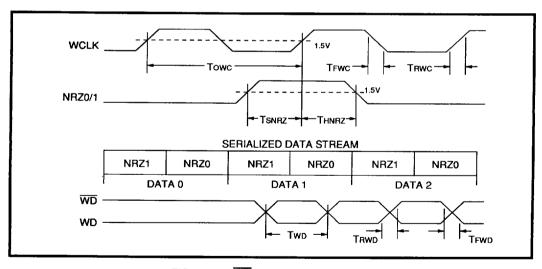

The data separator circuit provides complete encoding, decoding, and synchronization for RLL 1,7 format data. In the read mode, the circuit performs sync field search and detect, data synchronization and data decoding. In the write mode, the circuit provides data encoding and write precompensation for NRZ data applied to the NRZ0/1 pins. Data rate is established by the internal time base generator and IDAC.

4-85

💻 8253965 0014395 6**0**T 📟

FIGURE 11: Data Separator Phase Locked Loop

#### FUNCTIONAL DESCRIPTION (continued)

#### PHASE LOCKED LOOP

The circuit employs a dual mode phase detector; harmonic in the read mode and non-harmonic in the write and idle modes, Figure 11. In the read mode the harmonic phase detector updates the PLL with each occurrence of a DRD pulse. In the write and idle modes the non-harmonic phase detector is continuously enabled, thus maintaining both phase and frequency lock onto the reference frequency of the internal time base generator. By acquiring both phase and frequency lock to the input reference frequency and utilizing a zero phase restart technique, the VCO transient is minimized and false lock to read data is eliminated. The phase detector incorporates a charge pump in order to drive the loop filter directly. The polarity and width of the output current pulses correspond to the direction and magnitude of the phase error.

The data synchronizer also requires an external passive loop filter to control its PLL locking characteristics. This filter is also fully-differential and balanced in order to suppress common mode noise.

#### **READ/WRITE MODE CONTROL**

The read gate (RG) and write gate (WG) inputs control device operation in data mode. RG is an asynchronous input that must be initiated at the start of a valid preamble

field. It can be terminated at any position on the disk. WG is also an asynchronous input. It can be initiated at any time but should not be terminated prior to the last output write data pulse. To insure that the device will not enter any unknown states. RG overrides WG.

#### **READ MODE**

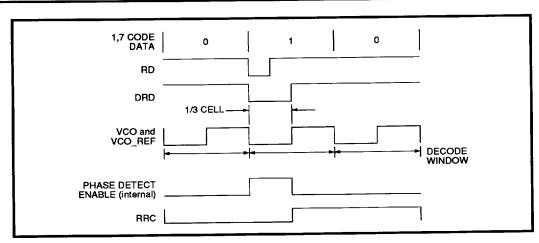

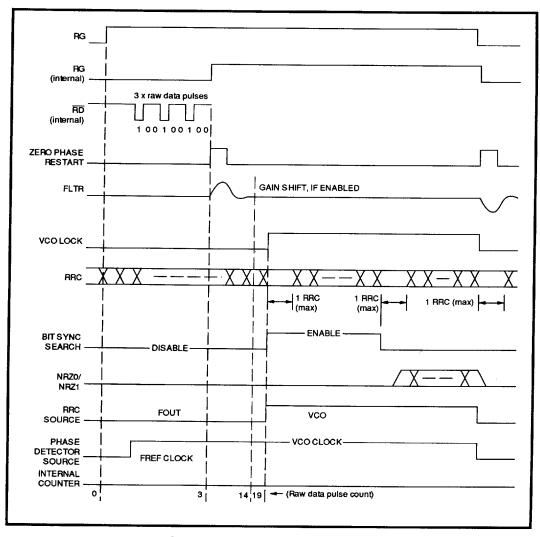

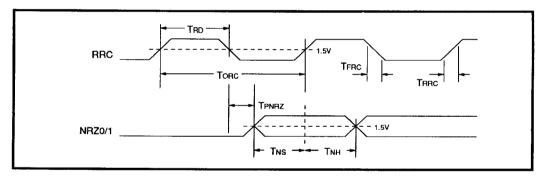

The data synchronizer utilizes a fully integrated fast acquisition PLL to accurately develop the decode window. Read gate (RG) initiates the PLL locking sequence and selects the PLL reference input; a high level (read mode) selects the internal RD input and a low level selects the reference clock. In the read mode the falling edge of  $\overline{D}\overline{RD}$  enables the phase detector while the rising edge is phase compared to the rising edge of the VCO reference (VCOR.) As depicted in Figure 12,  $\overline{D}\overline{RD}$  is a 1/3 NRZ bit cell wide pulse whose leading edge is defined by the falling edge of  $\overline{RD}$ . A decode window is developed from the VCOR clock.

#### VCO Lock and Bit Sync Enable

One of two VCO locking modes will be entered depending on the state of the gain shift (GS) bit, or bit 1, in the Control B register. An internal read gate is asserted 3 DRD transitions after read gate is asserted, see Figure 13. The phase detector then enters a high gain mode of operation to support fast phase acquisition. After an internal counter counts a total of 14 transitions

4-86

8253965 0014396 546 📟

FIGURE 12: Data Synchronization Waveform

FIGURE 13: Read Mode Locking Sequence

#### VCO Lock and Bit Sync Enable (continued)

of the internal DRD signal, including the 3 transitions prior to internal read gate, the gain is reduced by a factor of 3 if GS = 1. If GS = 0 the gain remains constant. This gain shift reduction reduces the bandwidth and damping factor of the loop by √3 which provides improved jitter performance in the data follow mode. The counter continues to count the next 5 DRD transitions (a total of 19 • 3T from assertion of RG) and then asserts an internal VCO lock signal. The VCO lock signal activates the decoder bit synchronization circuitry to define the proper decode boundries. The next 2 • 3T patterns are used to set the proper decode window so that VCO is in sync with RRC and RRC is in sync with the data. Following this, the NRZ outputs are enabled and the data is toggled through the decoder for the duration of the RG.

When the VCO lock signal is asserted, the internal RRC source is switched from the time base generator output to the VCO output signal that is phase locked to DRD. During the internal RRC switching period the external RRC signal may be held for a maximum of 1 NRZ clock period, however no short duration glitches will occur.

#### Window Shift

Shifting the phase of the VCO clock effectively shifts the relative position of the  $\overline{DRD}$  pulse within the decode window. Decode window control is provided via the WS control bits of the Window Shift Control Register (WSCR).

The magnitude of the window shift is given by:

% VCO Period = 2.23% • (15 - WSDAC) where WSDAC is the WSCR value For example,

0100 → 24.53% window shift

#### NON READ MODE

In the non-read modes, the PLL is locked to the reference clock. This forces the VCO to run at a frequency which is very close to that required for tracking actual data. When the reference input to the PLL is switched, the VCO is stopped momentarily, then restarted in an accurate phase alignment with the next PLL reference input pulse. By minimizing the phase alignment error in this manner, the acquisition time is substantially reduced.

#### WRITE MODE

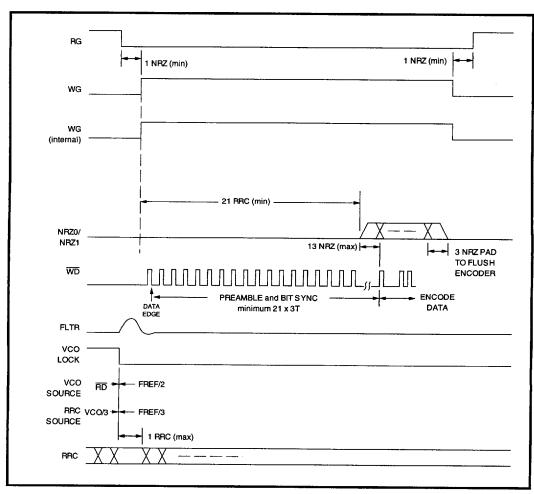

In the write mode the circuit converts NRZ data from the controller into 1,7 RLL formatted data for storage on the disk. Write mode is entered by asserting the write gate (WG) while the RG and SG are held low. During write mode the VCO and the RRC are referenced to the internal time base generator signal. The write data output is a differential PECL signal. The rising edge of the WD pin is the active edge. External termination of the WD/WD pins is required.

#### Write Mode Operation

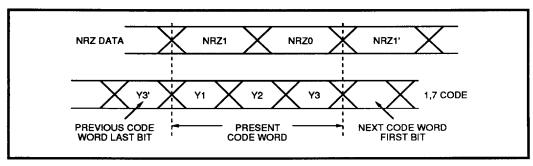

Write mode is entered by asserting WG high ("1") while RG and SG are held low ("0"). A preamble pattern of at least 19 '3T' patterns must be generated before any coded data can be written. The 3T preamble is written by holding both NRZ0 and NRZ1 low ("0") while WCLK is toggled. The first non zero NRZ input bits indicate the end of the preamble pattern. After a delay of 3 WCLK time periods, non-preamble data begins to toggle out WD. At the end of the write cycle, 3 WCLK cycles of blank NRZ should be added to insure the encoder is flushed of data before the WG can be transitioned low. WD stops toggling a maximum of 2 WCLK time periods after WG goes low. Reference Figures 14 and 15 for detailed timing information. In Figure 15, note that the NRZ1 bit is shifted into the encoder first and the NRZ0 bit is shifted into the encoder second. Because two bits are clocked into the device on each WCLK pulse, the encoder will always generate a predictable pattern.

#### **Direct Write Function**

The 32P4752 include a Direct Write (DW) function that allows the NRZ0 data to bypass the encoder and write precomp circuitry. When the DW bit is set in the CBR, the data applied to NRZ0 will bypass the encoder and write precomp and directly control the WD/WD output buffer. This allows the user to perform DC erase and media tests.

A rising edge at NRZ0 causes a rising edge on  $\overline{WD}$  and a falling edge on  $\overline{WD}$ . A falling edge at NRZ0 causes a falling edge on  $\overline{WD}$  and a rising edge on  $\overline{WD}$ . The DW bit also overrides SG, RG, and WG.

4-89

8253965 0014399 255

FIGURE 14: Write Data Operation

FIGURE 15: NRZ Data Word to 1,7 Code Word Bit Comparison (Reference Table 7 for decode scheme)

#### FUNCTIONAL DESCRIPTION (continued)

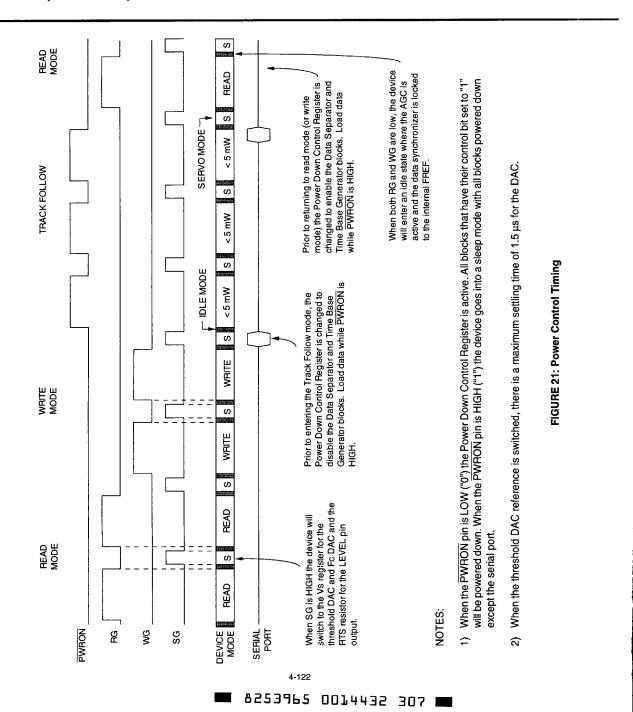

#### **OPERATING MODES AND CONTROL**

The device has several operating modes that support read, write, servo, and power management functions. Mode selection is accomplished by controlling the read gate (RG), write gate (WG), servo gate (SG), and PWRON pins. Additional modes are also controlled by programming the Power Down Control Register (PDCR), the Control A (CAR) register, and the Control B (CBR) register via the serial port.

#### **External Mode Control**

All operating modes of the device are controlled by driving the read gate (RG), write gate (WG), servo gate

(SG), and PWRON pins with TTL compatible signals (refer to Table 4). For normal operation the PWRON pin is driven low. During normal operation the device is controlled by the read gate (RG), write gate (WG), and servo gate (SG) pins. Servo gate (SG) determines the active mode of the device. When SG is high, the device enters the servo mode, regardless of the state of either RG or WG. When SG is low, RG and WG can be used. When RG is high the device is in read mode regardless of the state of WG. When SG and RG are both low, WG is brought high to enter write mode. If SG, RG, and WG pins are all low the device will be in idle mode.

#### REGISTER DESCRIPTION

#### **Control Registers**

The serial port registers allow the user to configure the device. The register map for the device is shown in Table 5. The bits of these registers are defined as follows:

#### **POWER DOWN CONTROL REGISTER (PDCR)**

| BIT | NAME   | DESCRIPTION                                                                                                                                                                             |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | PD/SVO | Pulse detector/servo power enable: Determines the state of the pulse detector and servo circuits when PWRON pin is low.  0 = Circuits enabled  1 = Circuits powered down                |

| 1   | NA     | Not used. Set to zero                                                                                                                                                                   |

| 2   | FLTR   | Filter power enable: Determines the state of the filter when PWRON pin is low.  0 = Filter enabled  1 = Filter powered down                                                             |

| 3   | DS     | Data separator power enable: Determines the state of the data separator circuit when PWRON pin is low.  0 = Data separator enabled 1 = Data separator powered down                      |

| 4   | TBG    | Time base generator power enable: Determines the state of the Time base generator circuit when PWRON pin is low.  0 = Time base generator enabled  1 = Time base generator powered down |

| 5-7 | N/A    | Device ID: These bits are a read only ID code for the device.                                                                                                                           |

#### REGISTER DESCRIPTION (continued)

#### **DATA MODE CUTOFF (DACF)**

| BIT | NAME   | DESCRIPTION                                                                                                                            |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0-6 | DMC    | Filter cutoff setting for data mode. Substitute this value for DACF into the cutoff calculation for the filter in data mode operation. |

| 7   | OSC ON | Enable oscillator: 0 = disabled 1 = enabled                                                                                            |

#### SERVO MODE CUTOFF (DACF)

| 0-6 | DMC | Filter cutoff setting for servo mode. Substitute this value for DACF into the cutoff calculation for the filter in servo mode operation. |

|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GDE | Group delay enabled in servo mode.  0 = disabled  1 = enabled                                                                            |

#### **FILTER BOOST REGISTER (DACS)**

| 0-6 | FBC | Filter boost setting. Substitute this value for DACS into filter calculations.                                                               |

|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SBE | Servo boost enable: Determines if boost is enabled when SG is high.  0 = Boost disabled when SG is high.  1 = Boost enabled when SG is high. |

#### **FILTER GROUP DELAY REGISTER (DACG)**

| 0-6 | GDM | Filter group delay magnitude. Substitute this value for DACG into group delay calculation. |

|-----|-----|--------------------------------------------------------------------------------------------|

| 7   | GDS | Group delay sign. 0 = negative 1 = positive                                                |

#### **DATA THRESHOLD REGISTER (VTHDAC)**

| 0-6 | DTH | Data threshold setting. Substitute this value for VTHDAC into the threshold calculation for data mode operation.                      |

|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DQ  | Qualifier select: Determines the type of qualifier used in data<br>mode.<br>0 = Hysteresis qualifier<br>1 = Dual comparator qualifier |

#### **SERVO THRESHOLD REGISTER (VTHDAC)**

| 0-6 | STH | Servo threshold setting. Substitute this value for VTHDAC into the threshold calculation for servo mode operation.              |

|-----|-----|---------------------------------------------------------------------------------------------------------------------------------|

| 7   | SQ  | Qualifier select: Determines the type of qualifier used in servo mode.  0 = Hysteresis qualifier  1 = Dual comparator qualifier |

4-93

**8253965 0014403 506**

#### **REGISTER DESCRIPTION** (continued)

#### **CONTROL A REGISTER (CAR)**

| BIT | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                   |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | EPDT   | Enable Phase Detector (Time Base Generator): This bit disables the output of the phase detector to the VCO. An external voltage applied across the TFLT pins drives the VCO to a fixed frequency.  0 = Phase detector disabled 1 = Phase detector enabled (normal operation)                  |

| 1   | UT     | Enable Pump Up Current (Time Base Generator): This bit enables a test mode for checking the charge pump output current. The charge pump will source a fixed DC current from TFLT and sink the current at TFLT.  0 = Not in pump up test mode. 1 = continuous pump up, for test use only.      |

| 2   | DT     | Enable Pump Down Current (Time Base Generator): This bit enables a test mode for checking the charge pump output current. The charge pump will source a fixed DC current from TFLT and sink the current at TFLT.  0 = Not in pump down test mode 1 = continuous pump down, for test use only. |

| 3   | MTP3E  | This bit enables the MTP3 test point output buffer.  0 = Test point disabled  1 = Test point enabled                                                                                                                                                                                          |

| 4   | BYPT   | This bit enables a time base generator bypass mode where the FREF input is connected to the data separator phase detector input.  0 = Time base generator in use 1 = Time base generator bypassed                                                                                             |

| 5/6 | TMS0/1 | These bits select the test point signal sources (ref Table 9)                                                                                                                                                                                                                                 |

| 7   | FDTM   | This bit continuously enables the AGC fast decay current.  0 = Fast decay current always on  1 = Normal fast decay operation  Set to 1 for normal operation.                                                                                                                                  |

#### **CONTROL B REGISTER (CBR)**

| BIT | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                               |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | DW    | This bit enables the direct write (Bypass Endec) function.  0 = ENDEC in use.  1 = Bypass encoder, NRZ0 buffered to WD/WD.                                                                                                                                                                |

| 1   | GS    | This enables the data separator phase detector gain switch in read mode.  0 = Gain remains high for the entire read cycle.  1 = 14 • 3T (read mode only) following RG01 transition.  Switches from high to low after gain.                                                                |

| 2   | RDIO  | This bit enables the RDIO pin as an input or output.  0 = RDIO is an output 1 = RDIO is an input                                                                                                                                                                                          |

| 3   | EPDD  | Enable Phase Detector (Data Separator): This bit disables the output of the phase detector to the VCO. An external voltage applied across the DFLT pins drives the VCO to a fixed frequency.  0 = Phase detector charge pump disabled  1 = Phase detector active                          |

| 4   | UD    | Enable Pump Up Current (Data Separator): This bit enables a test mode for checking the charge pump output current. The charge pump will source a fixed DC current from DFLT and sink the current at DFLT.  0 = not in pump up test mode 1 = continuous pump up, for test use only         |

| 5   | DD    | Enable Pump Down Current (Data Separator): This bit enables a test mode for checking the charge pump output current. The charge pump will source a fixed DC current from DFLT and sink the current at DFLT.  0 = Not in pump down test mode.  1 = Continuous pump down, for test use only |

| 6   | MTPEN | This bit enables the multiplexed test points (MTP1, 2, 3)  0 = Test points disabled  1 = Test points enabled                                                                                                                                                                              |

| 7   | ТМ    | Test mode bit: SSi use only. Set to 0 for normal operation.                                                                                                                                                                                                                               |

#### N COUNTER REGISTER

| 0-6 | N      | N counter value.                                                                                         |

|-----|--------|----------------------------------------------------------------------------------------------------------|

| 7   | TBG KD | Determines the phase detector gain of the TBG.  0 = KD is 1 • nominal value  1 = KD is 3 • nominal value |

#### M COUNTER REGISTER

| 0-7 | M | M counter value. |

|-----|---|------------------|

|     |   |                  |

#### REGISTER DESCRIPTION (continued)

### **DATA RECOVERY REGISTER (DRCR)**

| BIT | NAME | DESCRIPTION                                                                                          |

|-----|------|------------------------------------------------------------------------------------------------------|

| 0-6 | IDAC | Center frequency DAC value. Sets the center frequency for the data synchronizer VCO and the TBG VCO. |

| 7   | NSYC | This bit enables synchronization between STROBE and FWR output.  0 = in sync.  1 = no sync.          |

#### **WINDOW SHIFT REGISTER (WSR)**

| 0-3 | ws      | Window                          | shift DAC r      | nagnitude                                                                                                                                                                           |

|-----|---------|---------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | WSD     |                                 | shift directi    |                                                                                                                                                                                     |

| 5   | WSE     | Window<br>0 = Disat<br>1 = Enab |                  | ).                                                                                                                                                                                  |

| 6-7 | TDAC0/1 | on the DA                       | ACOUT test       | select: Selects the DAC output to be provided to point. The preferred setting when DACOUT is is to set TDAC0 = 1 and TDAC1 = 0:                                                     |

|     | j       | TDAC1                           | TDAC0            | DAC MONITORED                                                                                                                                                                       |

|     |         | 0<br>0<br>1<br>1                | 0<br>1<br>0<br>1 | Filter Fc DAC Qualifier threshold DAC (VTH) Window shift DAC Write precomp DAC; the selection of the early or late DAC is controlled by the WPE bit. WPE = 0 — Late WPE = 1 — Early |

#### WRITE PRECOMP REGISTER (WPR)

|     | OMIT REGISTER ( | Wrny                                                                                                                                                                          |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-2 | WPE             | Write precomp early/magnitude.                                                                                                                                                |

| 3   | WPE             | Write precomp enable. 0 = Disable 1 = Enable                                                                                                                                  |

| 4-6 | WPL             | Write precomp late magnitude.                                                                                                                                                 |

| 7   | LZT             | Low-Z time period: Determines the time period for the low-Z and fast decay one-shots.  0 = 1 μs nominal (0.4 μs hold on SG edges)  1 = 2 μs nominal (0.5 μs hold on SG edges) |

#### **AGC LEVEL REGISTER (ALR)**

| BIT | NAME | DESCRIPTION                                                                                                                                         |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3 | ADAC | AGC level DAC value. Sets AGC level in servo mode.                                                                                                  |

|     |      | 0000 = 1.2 Vp-p<br>1111 = 0.8 Vp-p                                                                                                                  |

| 4-7 | PDAC | Servo peak detector current DAC value. Sets the servo peak detector current in 6 μA steps.  0000 = 6 μA charge current  1111 = 96 μA charge current |

#### **Power Down Control**

For power management, the PWRON pin can be used in conjunction with the Power Down Control Register (PDCR) to set the operating mode of the device. The PDCR provides a control bit for each of the functional blocks. When the PWRON pin is brought high ("1") the device is placed into sleep mode (<0.5 mA) and all circuits are powered down except the serial port. This allows the user to program the serial port registers while still conserving power. Register information is retained during the sleep mode so it is not necessary to reprogram the serial port registers after returning to an active mode. When the PWRON pin is low ("0"), the contents of the PDCR determine which blocks will be active. Register mapping for the PDCR is shown in Table 5. To improve recovery time from the sleep mode, the inputs to the filter and AGC circuits are placed into a Low-Z mode.

**TABLE 4: Mode Control Table**

| ſ     | ON | TRO<br>NE | )L |                                                                                                                                                                                                                                                                                  | CC  | DAC   |          | ESIS       |

|-------|----|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------|------------|

| PWRON | RG | SG        | WG | DEVICE MODE                                                                                                                                                                                                                                                                      | VTH | ည     | BOOST    | HYSTERESIS |

| 1     | х  | Х         | Х  | <b>SLEEP MODE:</b> All functions are powered down. The serial port registers remain active and register programming data is saved.                                                                                                                                               | off | off   | off      | off        |

| 0     | 0  | 0         | 1  | WRITE MODE: The pulse detector is inactive. The data synchronizer VCO is locked to the internal time base generator. Write precomp circuit is clocked by internal time base.                                                                                                     | DR  | DR    | DR       | DR         |

| 0     | 1  | 0         | Х  | <b>READ MODE:</b> The pulse detector is active. The data synchronizer begins the preamble lock sequence.                                                                                                                                                                         | DR  | DR    | DR       | DR         |

| 0     | X  | 1         | Х  | SERVO MODE: The pulse detector is active and the servo control registers are enabled for the Fc DAC and the VTH DAC. RDIO is also active. The data synchronizer and time base generator can be disabled using the PDCR.                                                          |     | SR    | <b>A</b> | SR         |

| ┢     |    |           |    |                                                                                                                                                                                                                                                                                  |     | או חי | SBE :    | = 1        |

| 0     | 0  | 0         | 0  | IDLE MODE: The contents of the PDCR determine which blocks are powered-up. In normal operation with all blocks powered-up, the pulse detector is active, the data synchronizer VCO is locked to the time base generator, and the data control registers are used for VTH and FC. | DR  | DR    | DR       | DR         |

|       |    |           |    | If multiple control signals are active, the priority order will be PWRON, SG, RG, and WG. For example, if SG and RG are both "1", the servo mode will be active.                                                                                                                 |     |       |          |            |

DAC Control Key: DR = data register, SR = servo register, off = disabled

TABLE 5: Serial Port Register Mapping

| REGISTER NAME      | 94 | ₹ | 8              | ADDRESS      | Ø            | 0A | WH | -20                                      |                                    | DAT                                   | DATA BIT MAP                     |                                        |                                 |                                | 8                                      |

|--------------------|----|---|----------------|--------------|--------------|----|----|------------------------------------------|------------------------------------|---------------------------------------|----------------------------------|----------------------------------------|---------------------------------|--------------------------------|----------------------------------------|

| POWER DOWN CONTROL | 0  | - | -              | 100          | 1            | 0  | 0  | ·                                        | ı                                  | :                                     | TBG<br>1 = Disable<br>0 = Emable | DATA SEP<br>1 = Disable<br>0 = Erreble | FILTER 1 = Disable 0 = Enable   | NC                             | PD/SERVO<br>1 = Disable<br>0 = Enable  |

| DATA MODE CUTOFF   | 0  | - | -              | 0            | <del>-</del> | =  | 0  | 0SC ON<br>1 ± 0SC ON<br>0 = 0SC OFF      | FcpDACF<br>BIT 6                   | FcpDACF<br>BIT 5                      | FcoDACF<br>BIT 4                 | FceDACF<br>BiT 3                       | FcoDACF<br>BIT 2                | FceDACF<br>Bit 1               | FceDACF<br>BIT 0                       |

| SERVO MODE CUTOFF  | 0  | 0 | -              | 0            | -            | -  | 0  | GDE Boost<br>1 = Enable<br>0 = Disable   | FosDACF<br>BIT 6                   | FosDACF<br>BIT S                      | FcsDACF<br>BIT 4                 | FcsDACF<br>BIT 3                       | FosDACF<br>BIT 2                | FosDACF<br>BIT 1               | FcsDACF<br>BIT 0                       |

| FILTER BOOST       | ٥  | - | -              | °<br>-       | -            | F  | 0  | Servo Boost<br>1 z Enebie<br>0 z Disable | DACS<br>BIT 6                      | DACS                                  | DACS<br>BIT 4                    | DACS<br>BIT 3                          | DACS<br>BIT 2                   | DACS<br>BIT 1                  | DACS                                   |

| DATA THRESHOLD     | 0  | - | -              | -            | -            | 0  | 0  | Data Qual.<br>1 = Dual<br>0 = Hys        | ToDAC<br>BIT 6                     | ToDAC<br>BIT 5                        | ToDAC<br>BIT 4                   | TpDAC<br>BIT 3                         | TpDAC<br>BIT 2                  | TpDAC<br>BIT 1                 | TeDAC<br>BIT 0                         |

| SERVO THRESHOLD    | 0  | 0 | -              | 0            | <u> </u>     | 0  | ٥  | Servo Quel.<br>1 = Duel<br>0 = Hys       | TsDAC<br>BIT 6                     | TsDAC<br>BIT 5                        | TsDAC<br>BIT 4                   | TsDAC<br>BIT 3                         | TSDAC<br>BIT 2                  | TaDAC<br>BIT 1                 | TaDAC<br>BIT 0                         |

| CONTROLA           | ٥  | 0 | <del>  -</del> | 0            | -            | 0  | 0  | FD Yest<br>1 = Disable<br>0 = Enable     | TMB1                               | TMSO                                  | TBG<br>1 = Bypase<br>0 = Normal  | MTP3<br>1 = Enable<br>0 = Disable      | PUMP DWN<br>1 = ON<br>0 = OFF   | PUMP UP<br>1 = ON<br>0 = OFF   | PHASE DET<br>1 = Enable<br>0 = Disable |

| CONTROLB           | ٥  | - | 0              | <del>-</del> | -            | 0  | 0  | TEST MODE<br>1 * RESET<br>0 = NORMAL     | MTPEN<br>1 = Enable<br>0 = Disable | PUMP DWN<br>1 = ON<br>0 = OFF         | PUMP UP<br>1 = ON<br>0 = OFF     | PHASE DET<br>1 = Enable<br>0 = Disable | RDIO<br>1 = Input<br>0 = Output | GAIN SHFT<br>1 = ON<br>0 = OFF | DIR WRITE<br>1 = ON<br>0 = OFF         |

| N COUNTER          | 0  | 0 | -              | -            | -            | 0  | 0  | TBG KD<br>1=3x KD<br>0=1x KD             | N COUNT<br>BIT 6                   | N COUNT<br>BIT 5                      | N COUNT<br>BIT 4                 | N COUNT<br>BIT 3                       | N COUNT<br>BIT 2                | N COUNT<br>BIT 1               | N COUNT<br>BIT 0                       |

| M COUNTER          | ٥  | - | -              | <del>-</del> | -            | 0  | 0  | M COUNT<br>BIT 7                         | M COUNT<br>BIT 6                   | M COUNT<br>BIT 5                      | M COUNT<br>BIT 4                 | M COUNT<br>BIT 3                       | M COUNT<br>BIT 2                | M COUNT<br>BIT 1               | M COUNT<br>BIT 0                       |

| DATA RECOVERY      | 0  | 0 | Ö              | -            | 1 0          | 0  | 0  | NO_SYNC<br>SET TO 0                      | DAC<br>BIT 6                       | DAC                                   | DAC<br>BIT 4                     | DAC<br>BIT 3                           | DAC<br>BIT 2                    | DAC<br>BiT 1                   | DAC                                    |

| WINDOW SHIFT       | 0  | 0 | 0              | -            | 0            | 1  | 0  | TDAC 1                                   | трас о                             | WIN SHFT<br>1 = Enable<br>0 = Disable | WS DIR<br>1 = Late<br>0 = Early  | WS3                                    | WS2                             | WS1                            | WSO                                    |

| WRITE PRECOMP      | 0  | 0 | 0              | +            | 1 0          | 1  | 0  | Low-Z Time<br>1 x 2 µe<br>0 = 1 µg       | WL2                                | WL1                                   | WLO                              | WR PRCMP<br>1 = Enable<br>0 = Disable  | WE2                             | WE1                            | WEO                                    |

| AGCLEVEL           | 0  | - | 0              | 0            | 0 1          | 0  | 0  | PDAC<br>BIT 3                            | PDAC<br>BIT 2                      | PDAC<br>BIT 1                         | PDAC<br>BIT 0                    | ADAC<br>BIT3                           | ADAC<br>BIT 2                   | ADAC<br>BIT 1                  | ADAC<br>BIT 0                          |

| GDE BOOST          | 0  | 0 | 1              | 1 0          | 0            | 1  | 0  | GD DIR<br>1 = POS<br>0 = NEG             | GD DAC<br>BIT 6                    | GD DAC<br>BIT 5                       | GD DAC<br>BIT 4                  | GD DAC<br>BIT 3                        | GD DAC<br>BIT 2                 | GD DAC<br>BIT 1                | ab DAC<br>BITO                         |

|                    |    | l |                | l            |              |    |    |                                          |                                    |                                       |                                  | •                                      |                                 |                                |                                        |

\* Denotes SSI internal test bits. These bits should be set to 0 in normal operation.

4-99

■ 8253965 0014409 T24 |

#### REGISTER DESCRIPTION (continued)

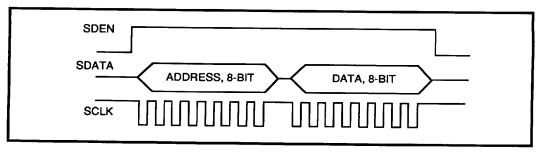

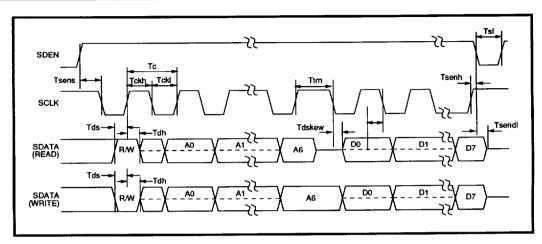

#### SERIAL INTERFACE OPERATION

The serial interface is a bi-directional port for reading and writing programming data from/to the internal registers of the 32P4752. For data transfers SDEN is brought high, serial data is presented at the SDATA pin, and a serial clock is applied to the SCLK pin. After the SDEN goes high, the first 16 pulses applied to the SCLK pin will shift the data presented at the SDATA pin into an internal shift register on the rising edge of each clock. An internal counter prevents more than 16 bits from being shifted into the register. The data in the shift register is latched when SDEN goes low. If less than 16 clock pulses are provided before SDEN goes low, the data transfer is aborted.

All transfers are shifted into the serial port LSB first. The first byte of the transfer is address and instruction information. The LSB of this byte is the R/W bit which determines if the transfer is a read (1) or a write (0). The remaining 7-bits determine the internal register to be accessed. Table 5 provides register mapping information. The second byte contains the programming data. In read mode (R/W=1) the 32P4752 will output the register contents of the selected address. In write mode the device will load the selected register with data presented on the SDATA pin. At initial power-up, the contents of the internal registers will be in an unknown state and they must be programmed prior to operation. During power down modes, the serial port remains active and register programming data is retained.

FIGURE 16: Serial Port Transfer Format

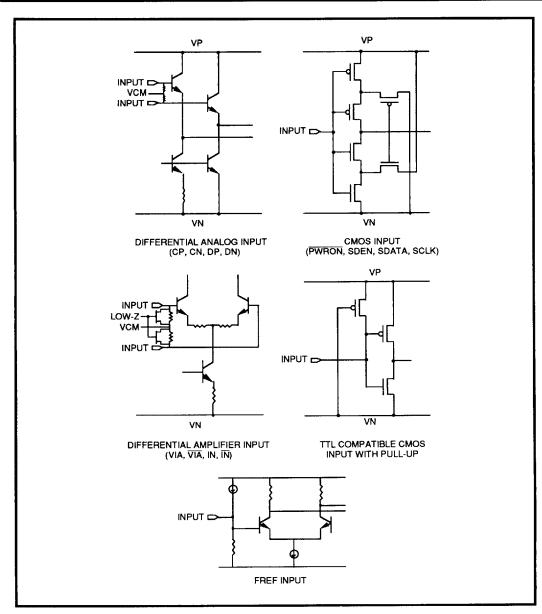

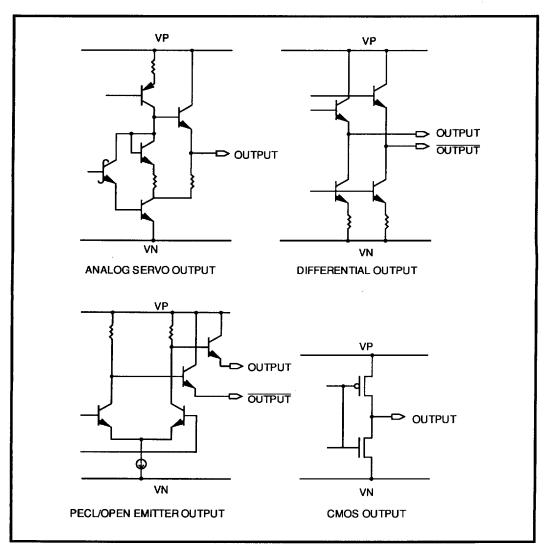

FIGURE 17: Input Structures

4-101 8253965 001,4411, 682 **....**

**FIGURE 18: Output Structures**

<sup>4-102</sup> ■ 8253965 0014412 519 **■**

#### **PIN DESCRIPTION**

#### **POWER SUPPLY PINS**

| NAME | TYPE | DESCRIPTION                                           |  |

|------|------|-------------------------------------------------------|--|

| VPA  |      | Data separator PLL analog power supply pin            |  |

| VPB  |      | Time base generator PLL analog power supply pin       |  |

| VPC  |      | Internal ECL, CMOS logic power supply pin             |  |

| VPE  |      | WD/WD buffer digital power supply pin                 |  |

| VPD  |      | TTL buffer I/O digital power supply pin               |  |

| VPG  |      | Pulse detector, filter, servo analog power supply pin |  |

| VNA  |      | Data separator PLL analog ground pin                  |  |

| VNB  |      | Time base generator PLL analog ground pin             |  |

| VNC  |      | Internal ECL, CMOS logic ground pin                   |  |

| VND  |      | TTL buffer I/O digital ground pin                     |  |

| VNG  |      | Pulse detector, filter, servo analog ground pin       |  |

| VNE  |      | WD/WD buffer digital ground pin                       |  |

#### INPUT PINS

| VIA, VIA | ı | AGC AMPLIFIER INPUTS: Differential AGC amplifier input pins.                                                                                                                                                                                                                                                                  |

|----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DP, DN   | I | ANALOG INPUTS FOR DATA PATH: Differential analog inputs to data comparators, full-wave rectifier.                                                                                                                                                                                                                             |

| CP, CN   | 1 | ANALOG INPUTS FOR CLOCK PATH: Differential analog inputs to the clock comparator.                                                                                                                                                                                                                                             |

| PWRON    | l | Power Enable: TTL compatible CMOS power control input. A low level CMOS input enables power to circuitry according to the contents of the PDCR. A high level CMOS input shuts down all circuitry.                                                                                                                             |

| HOLD     | 1 | HOLD CONTROL: TTL compatible CMOS control pin which, when pulled low, disables the AGC charge pump and holds the AGC amplifier gain at its present value.                                                                                                                                                                     |

| STROBE   |   | BURST STROBE: TTL compatible CMOS burst strobe input. A high level TTL input will enable the servo peak detector to charge one of the burst capacitors. The falling edge of STROBE increments an internal counter that determines which burst capacitor will charge on the next STROBE pulse (reference Figure 7 for timing.) |

| RESET    | I | RESET CONTROL INPUT: TTL compatible CMOS reset input. A low level TTL input will discharge the internal servo burst hold capacitors on channels A-D.                                                                                                                                                                          |

| IN, ĪN   | 1 | FILTER SIGNAL INPUTS: The AGC output signals must be AC coupled into these pins.                                                                                                                                                                                                                                              |

4-103

**=** 8253965 0014413 455 **==**

#### PIN DESCRIPTION (continued)

#### **INPUT PINS** (continued)

| NAME   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                               |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FREF   | l    | REFERENCE FREQUENCY INPUT: Frequency reference input for the time base generator. FREF should be driven either by a direct coupled TTL signal or by an AC coupled ECL signal.                                                                                                             |

| NRZ0/1 | 1/0  | NRZ I/O PORT: TTL compatible CMOS NRZ data port. In read mode, valid data is output on these pins with each cycle of RRC. In write mode, data input on these pins is clocked into the device by WCLK.                                                                                     |

| RG     | l    | READ GATE: TTL compatible CMOS read gate input. A high level TTL input selects the RD input and enables the read mode/address detect sequences. A low level selects the FREF input.                                                                                                       |

| SG     | _    | SERVO GATE: TTL compatible CMOS servo gate input. A high level TTL input activates the servo mode by selecting the servo control registers, the RDIO pin active in idle mode, the PPOL pin also active in idle mode, and the RTS resistor.                                                |

| WCLK   | ļ    | WRITE CLOCK: TTL compatible CMOS write clock input. Must be synchronous with the write data NRZ0/1 input. For short cable delays, WCLK may be connected directly to pin RRC.For long cable delays, WCLK should be connected to an RRC return line matched to the NRZ data bus line delay. |

| WG     | 1    | WRITE GATE: TTL compatible CMOS write gate input. A high level input enables the write mode.                                                                                                                                                                                              |

#### **OUTPUT PINS**

| MTP1,2,3          | 0 | MULTIPLEXED TEST POINTS: Open emitter ECL output test points. Internal test signals are routed to these test points as determined by the CAR and CBR. Two pull up and down resistors are required to use this pin. They should be removed during normal operation to reduce power dissipation. (Reference Table 9)                                               |

|-------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OD, <del>OD</del> | 0 | FILTER DIFFERENTIATED OUTPUTS: Filter differentiated outputs. These outputs are AC coupled into the CP/CN inputs.                                                                                                                                                                                                                                                |

| ON, ON            | 0 | FILTER NORMAL OUTPUTS: Filter normal low pass output signals. These outputs are AC coupled into the DP/DN inputs.                                                                                                                                                                                                                                                |

| PPOL              | 0 | PULSE POLARITY: Pulse polarity CMOS compatible output. The output is high when the pulse being qualified is positive and it is low when the pulse being qualified is negative.                                                                                                                                                                                   |

| RDIO              | 0 | READ DATA I/O: Bi-directional TTL compatible CMOS pin. RDIO outputs RD pulses when in idle or servo modes of operation. RDIO is an input when the RDIO bit is enabled in the CBR.                                                                                                                                                                                |

| RRC               | 0 | READ REFERENCE CLOCK: Read clock CMOS compatible output. During a mode change, no glitches are generated and no more than one lost clock pulse will occur. When RG goes high, RRC initially remains synchronized to FOUT. When the Sync Bits are detected, RRC is synchronized to the $\overline{DRD}$ . When RG goes low, RRC is synchronized back to the FOUT. |

4-104

#### OUTPUT PINS (continued)

| NAME                | TYPE | DESCRIPTION                                                                                                                                                                                               |

|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VOA, <del>VOA</del> | 0    | AGC AMPLIFIER OUTPUT: Differential AGC amplifier output pins. These outputs are ac coupled into the filter inputs (IN/IN).                                                                                |

| WD/WD               | 0    | WRITE DATA: Differential PECL encoded write data. The rising edge of the WD pin represents the data bit (precomped edge). These are open emitter outputs, and an external pull-down resistor is required. |

#### **ANALOG PINS**

| A, B, C, D | 0 | SERVO OUTPUTS: These outputs are processed versions of the voltages captured on the servo hold capacitors. They are referenced to an internally generated, 0.5V baseline.                                                                                                                                       |

|------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYP        | 0 | The AGC integrating capacitor CA, is connected between BYP and VPG.                                                                                                                                                                                                                                             |

| TFLT/TFLT  | 0 | PLL LOOP FILTER: These pins are the connection points for the time base generator loop filter.                                                                                                                                                                                                                  |

| DACOUT     | 0 | DAC VOLTAGE TEST POINT: This test point monitors the outputs of the internal DACs. The source DAC is selected by programming the two MSBs of the WSCR register.                                                                                                                                                 |

| DFLT/DFLT  | 0 | PLL LOOP FILTER: These pins are the connection points for the data separator loop filter.                                                                                                                                                                                                                       |

| LEVEL      | 0 | An NPN emitter output that provides a full-wave rectified signal from the DP, DN inputs. An external capacitor should be connected from LEVEL to VPG to set the hysteresis threshold time constant in conjunction with RTS and RTD. An internal current source provides 60 µA of pull-down current at this pin. |

| RR         | 0 | REFERENCE RESISTOR INPUT: An external 1% resistor is connected from this pin to VNA to establish a precise internal reference current for the data separator and time base generator.                                                                                                                           |