# XC2000L Low-Voltage Logic Cell Array Family

## **Preliminary Product Specification**

#### **Features**

- Part of the ZERO+ Family of 3.3 V FPGAs

- Low-power, low-supply-voltage FPGA family with two device types

- JEDEC-compliant 3.3 V version of the XC2000 LCA Family

- Logic densities from 1,000 to 1,500 gates

- Up to 74 user-definable I/Os

- Advanced, low power 0.8 μ CMOS static-memory technology

- Very low quiescent current consumption, ≤20 μA , 25 times less than XC2000

- Operating power consumption 66% less than previous generation 5 V FPGAs; 56% less than XC2000

- Identical to the basic XC2000 in structure, pin out, design methodology, and software tools

- 100% compatible with XC2000 bitstreams

- XC2000L-specific features

- Guaranteed over the 3.0 to 3.6 V V<sub>CC</sub> range

- TTL-equivalent input and output levels

- 4 mA output sink and source current

- Advanced packaging using thin and very thin quad flat packs

#### Description

The XC2000L family of FPGAs is optimized for operation from a 3.3 V (nominal) supply. Aside from the electrical and timing parameters listed in this data sheet, the XC2000L family is in all respects identical with the XC2000 family.

The operating power consumption of Xilinx FPGAs is almost exclusively dynamic; it changes with the square of the supply voltage. For a given complexity and clock speed, the XC2000L consumes, therefore, only 44% of the power used by the equivalent XC2000 device. Consistent with its use in battery-powered equipment, the XC2000L family was designed for the lowest possible power-down and quiescent current consumption.

| Device  | Logic<br>Capacity<br>(gates) | CLBs | User<br>VO<br>Max | Config.<br>bits |

|---------|------------------------------|------|-------------------|-----------------|

| XC2064L | 800 - 1,000                  | 64   | 58                | 12,038          |

| XC2018L | 1,200 - 1,500                | 100  | 74                | 17,878          |

LCA logic functions and interconnections are determined by data stored in internal static-memory cells. On-chip logic provides for automatic loading of configuration data at power-up. Program data can reside in an EEPROM, EPROM or ROM on the circuit board or on a floppy disk or hard disk. The program can be loaded in a number of modes to accommodate various system requirements. Xilinx maintains test specifications for each product as controlled documents. To insure the use of the most recently released device performance parameters, please request a copy of the current test-specification revision.

### **Absolute Maximum Ratings**

| Symbol           | Description                                     |                              | Units |

|------------------|-------------------------------------------------|------------------------------|-------|

| v <sub>cc</sub>  | Supply voltage relative to GND                  | -0.5 to +7.0                 | V     |

| V <sub>IN</sub>  | Input voltage with respect to GND               | -0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to 3-state output               | -0.5 to V <sub>CC</sub> +0.5 | ٧     |

| T <sub>STG</sub> | Storage temperature (ambient)                   | -65 to +150                  | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10 s @ 1/16 in.) | +260                         | °C    |

| _                | Junction temperature plastic                    | +125                         | °C    |

| T <sub>J</sub>   | Junction temperature ceramic                    | +150                         | °C    |

Note: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

### **Operating Conditions**

| Symbol          | Description                                              | Min | Max                  | Units |

|-----------------|----------------------------------------------------------|-----|----------------------|-------|

| V <sub>cc</sub> | Supply voltage relative to GND (Commercial 0°C to +70°C) | 3.0 | 3.6                  | V     |

| V <sub>IH</sub> | High-level input voltage                                 | 2.0 | V <sub>cc</sub> +0.3 | V     |

| V <sub>IL</sub> | Low-level input voltage                                  | 0.3 | 0.8                  | V     |

| T <sub>IN</sub> | Input signal transition time                             |     | 250                  | ns    |

Although the present (1993) devices operate over the full supply voltage range from 3.0 to 5.25 V, Xilinx reserves the right to restrict operation to the 3.0 to 3.6 V range later, when smaller device geometries might preclude operation at 5 V.

## **DC Characteristics Over Operating Conditions**

| Symbol            | Description                                                                 | Min                  | Max | Units |

|-------------------|-----------------------------------------------------------------------------|----------------------|-----|-------|

| V <sub>OH</sub>   | High-level output voltage (@ I <sub>OH</sub> = −2.0 mA V <sub>CC</sub> min) | 2.4                  |     | V     |

| V <sub>OL</sub>   | Low-level output voltage (@ I <sub>OL</sub> = 4.0 mA V <sub>CC</sub> max)   |                      | 0.4 | ٧     |

| V <sub>OH</sub>   | High-level output voltage (@ -100 μΑ V <sub>cc</sub> min)                   | V <sub>CC</sub> -0.2 |     | v     |

| V <sub>OL</sub>   | Low-level output voltage (@ 100 μA V <sub>CC</sub> min)                     |                      | 0.2 | V     |

| V <sub>CCPD</sub> | Power-down supply voltage (PWRDWN must be Low)                              | 2.3                  |     | V     |

| I <sub>cco</sub>  | Quiescent operating power supply current*                                   |                      | 20  | μА    |

| I <sub>CCPD</sub> | Power-down supply current (V <sub>CC(MAX)</sub> @ T <sub>MAX</sub> )        |                      | 10  | μА    |

| l <sub>IL</sub>   | Input Leakage Current, all I/O pins in parallel                             | -10                  | +10 | μА    |

| C <sub>IN</sub>   | Input capacitance (sample tested) All Pins except XTL1 and XTL2             |                      | 10  | pF    |

|                   | XTL1 and XTL2                                                               |                      | 15  | pF    |

<sup>\*</sup> With no output current loads, no active input or Longline pull-up resistors, all package pins at V<sub>CC</sub> or GND, and the LCA device configured with a MakeBits tie option. I<sub>CCD</sub> is in addition to I<sub>CCPD</sub>.

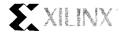

## **CLB Switching Characteristic Guidelines**

1104 30

## **CLB Switching Characteristic Guidelines (Continued)**

|                           | Spe                                                                                                                         | ed Gra       | de                                                                                              |  |    |   |  |                      |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------|--|----|---|--|----------------------|

|                           | Description                                                                                                                 | 9            | ymbol                                                                                           |  |    |   |  | Units                |

| Logic Input<br>to Output  | Combinatorial<br>Transparent latch<br>Additional for Q<br>through F or G to out                                             | 1 2          | T <sub>ILO</sub><br>T <sub>ITO</sub>                                                            |  |    |   |  | ns<br>ns             |

| K Clock                   | To output<br>Logic-input setup<br>Logic-input hold                                                                          | 9<br>3<br>4  | T <sub>CKO</sub><br>T <sub>ICK</sub><br>T <sub>CKI</sub>                                        |  |    | c |  | ns<br>ns<br>ns       |

| C Clock                   | To output<br>Logic-input setup<br>Logic-input hold                                                                          | 10<br>5<br>6 | T <sub>CCO</sub><br>T <sub>ICC</sub>                                                            |  |    |   |  | ns<br>ns<br>ns       |

| Logic Input<br>to G Clock | To output<br>Logic-input setup<br>Logic-input hold                                                                          | 11<br>7<br>8 | T <sub>CIO</sub><br>T <sub>ICI</sub><br>T <sub>CII</sub>                                        |  | Ž, |   |  | ns<br>ns<br>ns       |

| Set/Reset direct          | Input A or D to output x, y Through F or G to output Reset pad to output x, y Separation of set/reset Set/Reset pulse-width | 12<br>13     | T <sub>RIO</sub><br>T <sub>RLO</sub><br>T <sub>MRQ</sub><br>T <sub>RS</sub><br>T <sub>RPW</sub> |  |    |   |  | ns<br>ns<br>ns<br>ns |

| Flip-flop Toggle rate     | Q through F to flip-flop                                                                                                    |              | F <sub>CLK</sub>                                                                                |  |    |   |  | MHz                  |

| Clock                     | Clock High<br>Clock Low                                                                                                     | 14<br>15     | T <sub>CH</sub>                                                                                 |  |    |   |  | ns<br>ns             |

Notes: 1. All switching characteristics apply to all valid combinations of process, temperature and supply with a nominal chip power dissipation of 250 mW.

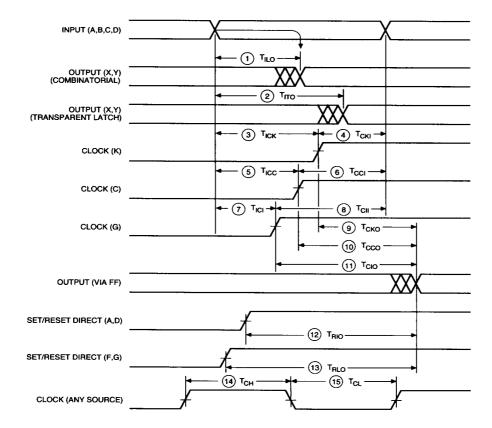

## **IOB Switching Guidelines**

|                      | s                                                                             | peed Gr          | ade                                                                      |   |       |    |     |        |      |                             |

|----------------------|-------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------|---|-------|----|-----|--------|------|-----------------------------|

|                      | Description                                                                   | Sy               | mbol                                                                     | - |       |    |     | . La l |      | Units                       |

| Pad<br>(package pin) | To input (direct)                                                             | 1                | T <sub>PID</sub>                                                         |   |       | .3 | 2.5 |        | 19/2 | ns                          |

| I/O Clock            | To input (storage) To pad-input setup To pad-input hold Pulse width Frequency | 5<br>2<br>3<br>4 | T <sub>L1</sub><br>T <sub>PL</sub><br>T <sub>LP</sub><br>T <sub>LW</sub> |   |       |    |     |        |      | ns<br>ns<br>ns<br>ns<br>MHz |

| Output               | To pad (output enabled)                                                       | 8                | T <sub>OP</sub>                                                          |   | (0.5) |    |     |        |      | ns                          |

| Three-state          | To pad begin hi-Z<br>To pad end hi-Z                                          | 9<br>10          | T <sub>THZ</sub>                                                         |   |       |    |     |        |      | ns<br>ns                    |

| RESET                | To input (storage) To input clock                                             | 6 7              | T <sub>RI</sub>                                                          |   |       |    |     |        |      | ns<br>ns                    |

Note: Timing is measured at 0.5 Vcc levels with 50 pF output load.

For a detailed description of the device architecture, see pages 2-179 through 2-187.

For a detailed description of the configuration modes and their timing, see pages 2-192 through 2-198.

For package physical dimensions, see Section 4.

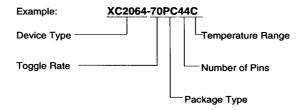

## **Ordering Information**

## **Component Availability**

| PINS    |      | 44             | 48            | 64             | 6              | 8             | 8              | 4             | 10             | ж.             |

|---------|------|----------------|---------------|----------------|----------------|---------------|----------------|---------------|----------------|----------------|

| TYPE    |      | PLAST.<br>PLCC | PLAST.<br>DIP | PLAST.<br>VQFP | PLAST.<br>PLCC | CERAM.<br>PGA | PLAST.<br>PLCC | CERAM.<br>PGA | PLAST.<br>TQFP | PLAST.<br>VQFP |

| CODE    |      | PC44           | PD48          | VQ64           | PC68           | PG68          | PC84           | PG84          | TQ100          | VQ100          |

|         | -50  |                | С             |                | CI             | CIM           |                |               |                |                |

| XC2064  | -70  | СI             |               |                | CI             | CIM           |                |               |                |                |

|         | -100 | С              |               |                | С              | С             |                |               |                |                |

|         | -33  |                |               |                |                |               |                | мв            |                |                |

| XC2018  | -50  |                |               | •              | СІ             |               | СI             | CIMB          | 1              |                |

| AC2018  | -70  | CI             |               |                | CI             |               | CI             | CIMB          |                |                |

|         | -100 | C              |               | С              | С              |               | С              | С             | С              |                |

| XC2064L |      |                |               | (C I)          | CI             |               |                |               |                |                |

| XC2018L |      |                |               | CI             |                |               | CI             |               |                | CI             |

C = Commercial = 0° to +70° C

I = Industrial = -40° to +85° C B = MIL-STD-883C Class B

$M = Mil Temp = -55^{\circ} to +125^{\circ} C$

Parentheses indicate future product plans