# **TOSHIBA**

# 8 Bit Microcontroller TLCS-870/C Series

TMP86FM48

**TOSHIBA CORPORATION**

The information contained herein is subject to change without notice. 021023\_D

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications.

Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).

These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.  $060106 \, \, \mathrm{O}$

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties. 070122\_C

The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

© 2007 TOSHIBA CORPORATION All Rights Reserved

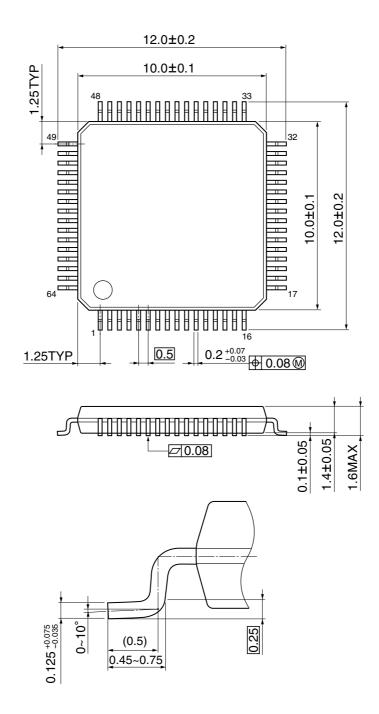

## CMOS 8-Bit Microcontroller TMP86FM48UG/FG

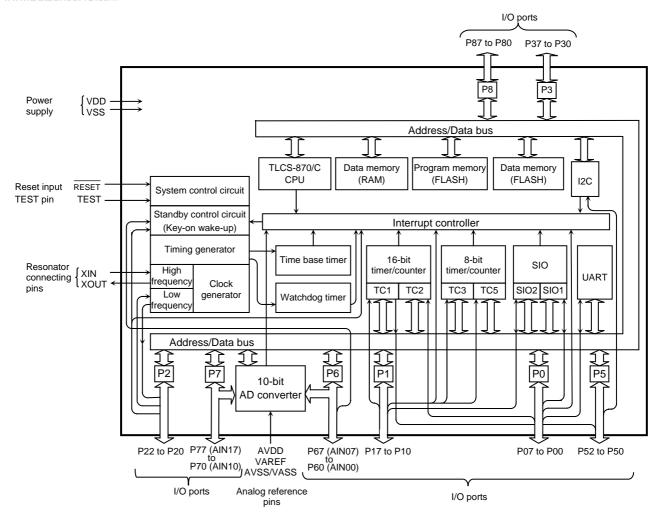

The TMP86FM48 is the high-speed, high-performance and low power consumption 8-bit microcomputer, including FLASH, RAM, multi-function timer/counter, serial interface (UART, SIO, I<sup>2</sup>C), a 10-bit AD converter and two clock generators on chip.

| Product No. | FLASH<br>(Program area) | FLASH<br>(Data area) | RAM            | Package             | Emulation Chip |

|-------------|-------------------------|----------------------|----------------|---------------------|----------------|

| TMP86FM48UG | 22256 0 hito            | 512 × 8 bits         | 2.0 K × 8 bits | LQFP64-P-1010-0.50E | TMD06C040VD    |

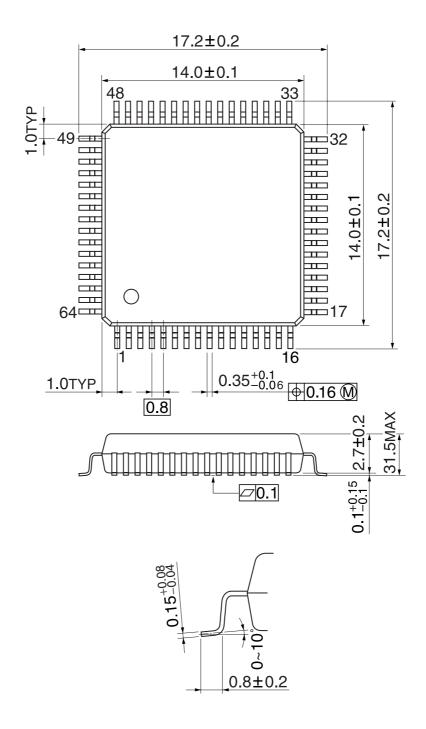

| TMP86FM48FG | 32256 × 8 bits          | 512 × 6 DIIS         | 2.0 K × 6 DIIS | QFP64-P-1414-0.80C  | TMP86C948XB    |

#### **Features**

- 8-bit single chip microcomputer TLCS-870/C series

- Instruction execution time: 0.25 µs (at 16 MHz) 122 µs (at 32.768 kHz)

- 132 types and 731 basic instructions

- 20 interrupt sources (External: 5, Internal: 15)

- Input/output ports (54 pins)

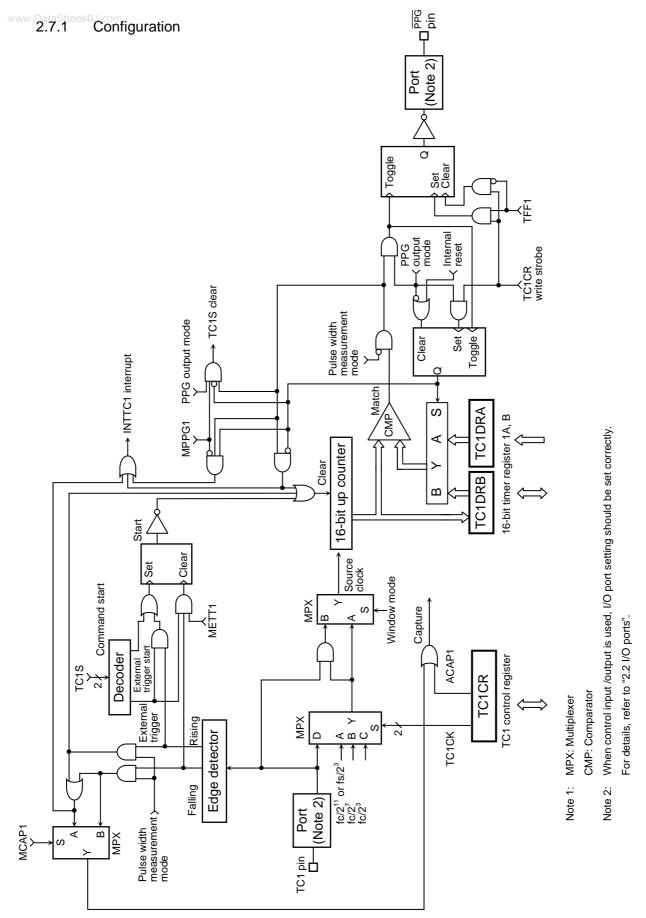

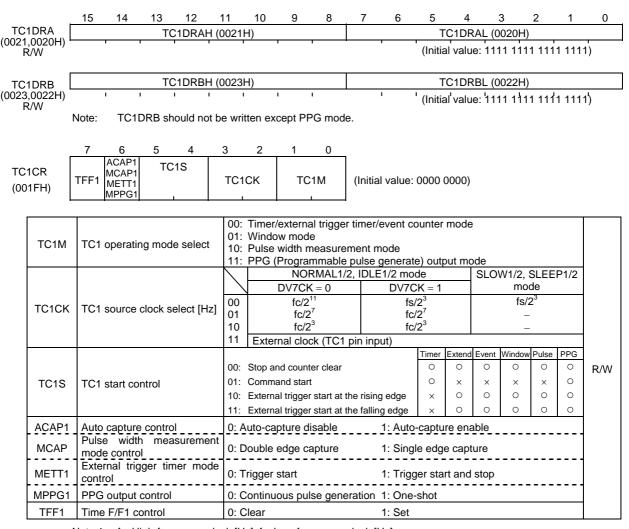

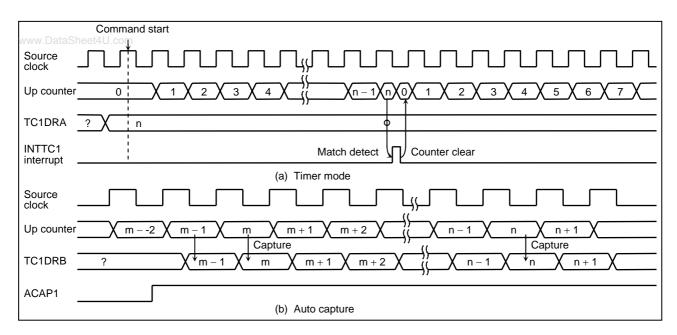

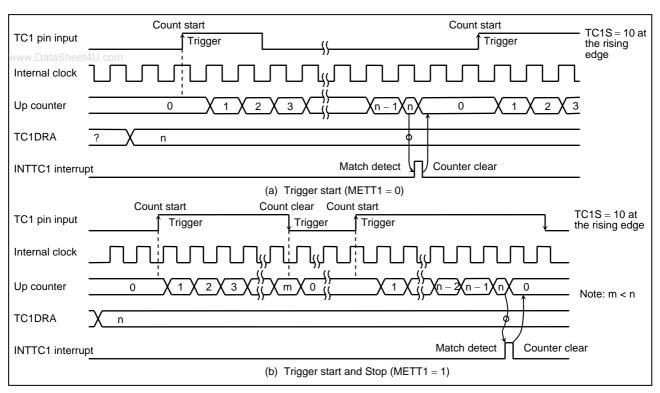

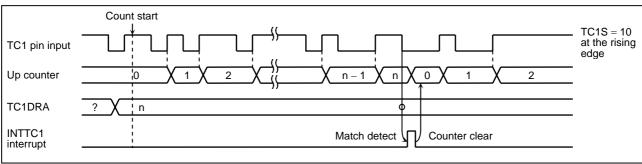

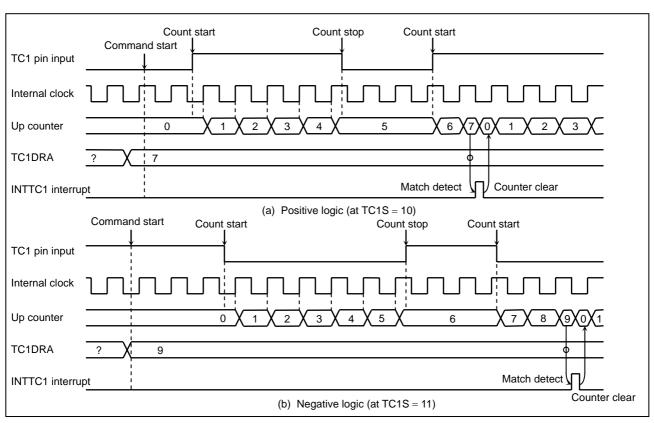

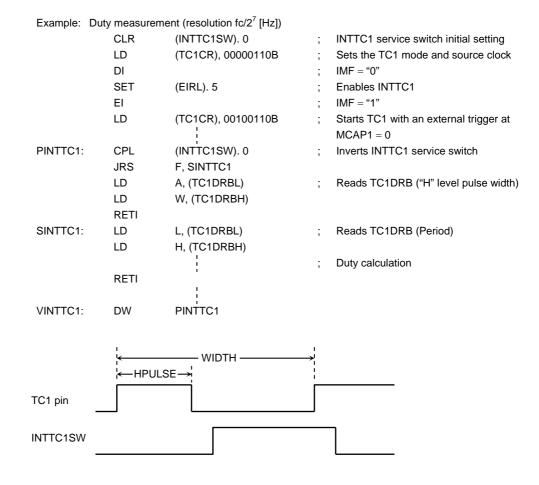

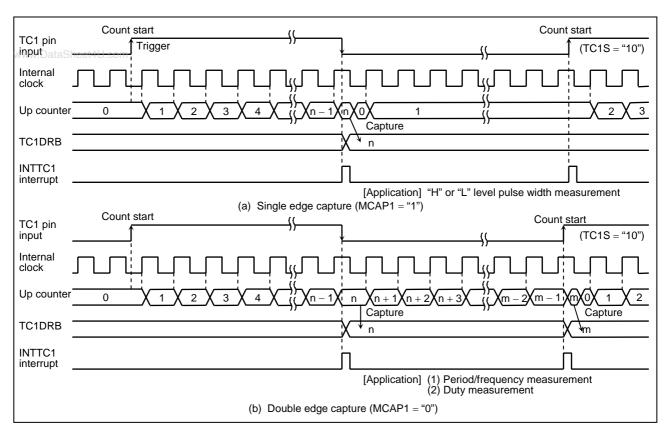

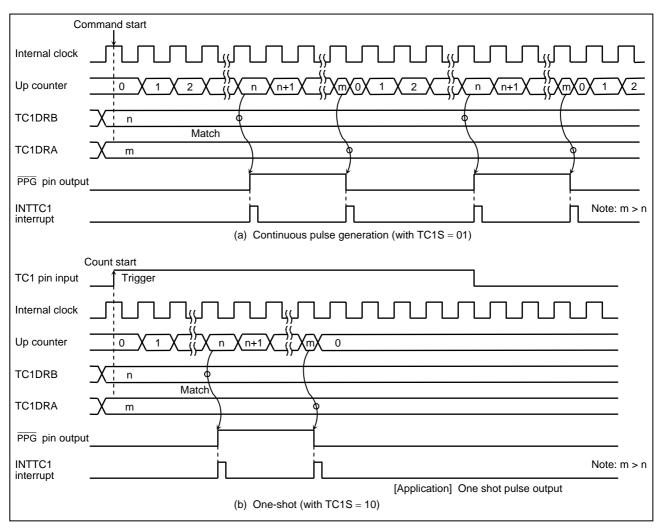

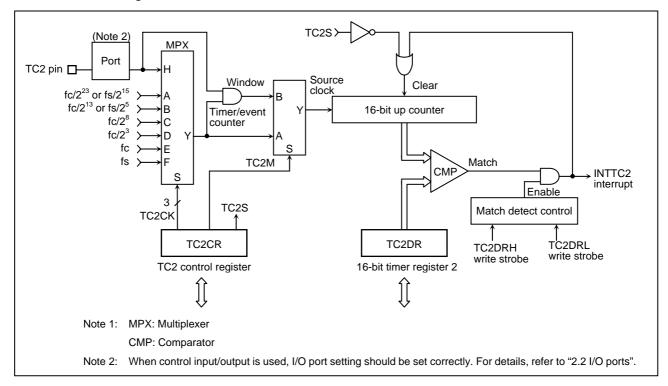

- 16-bit timer counter: 2 ch

- Timer, Event counter, Pulse width measurement, External trigger timer, Window, PPG output modes

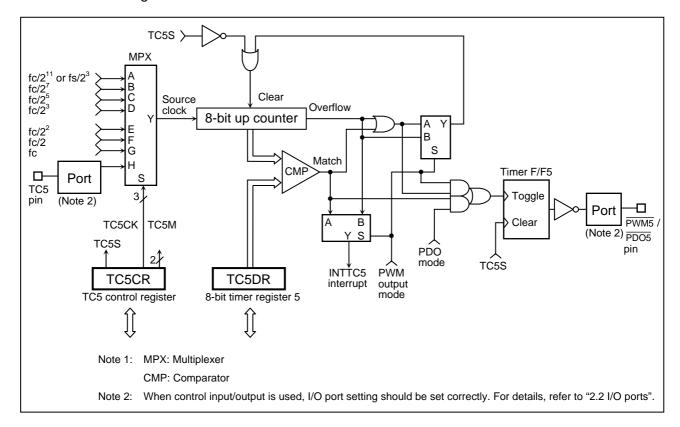

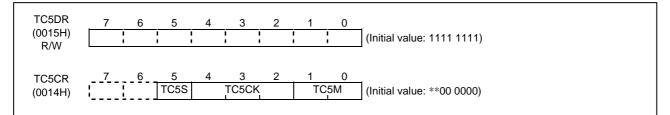

- 8-bit timer counter: 2 ch

- Timer, Event counter, PWM output, Programmable divider output, Capture modes

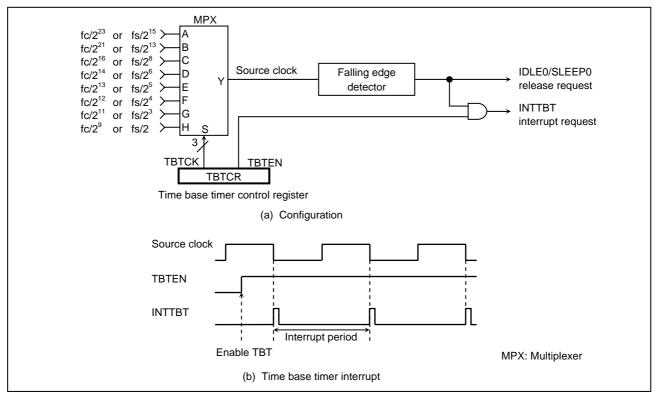

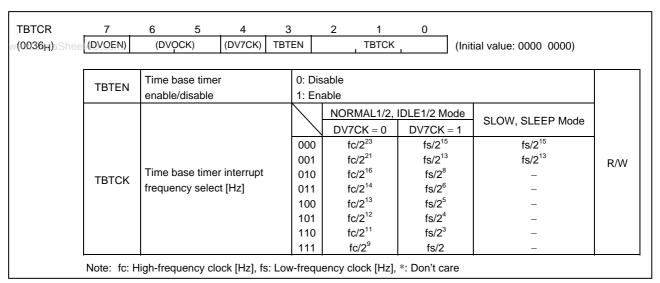

- Time base timer

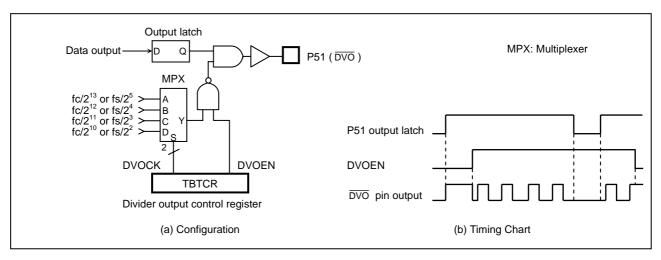

- Divider output function

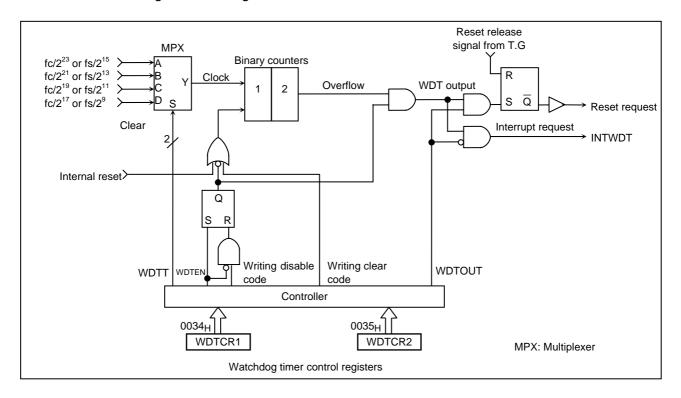

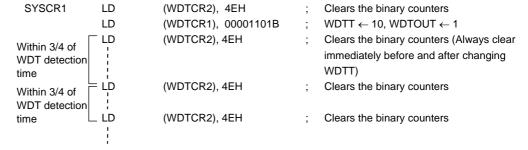

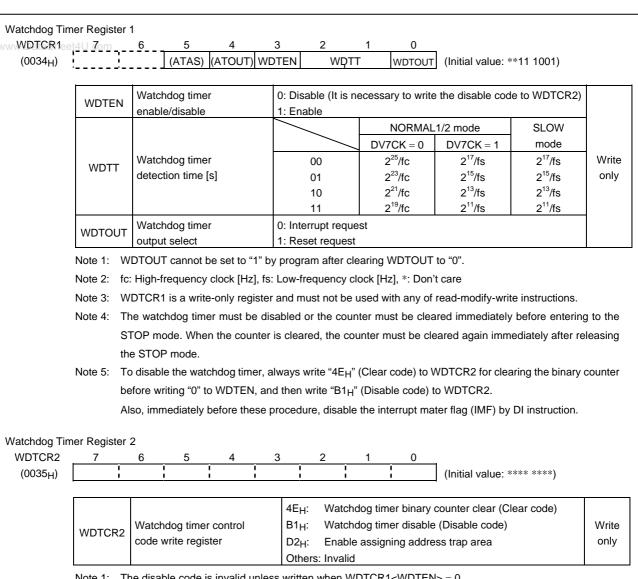

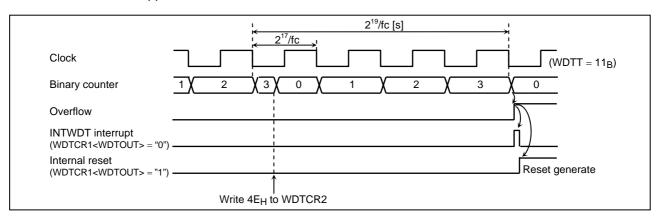

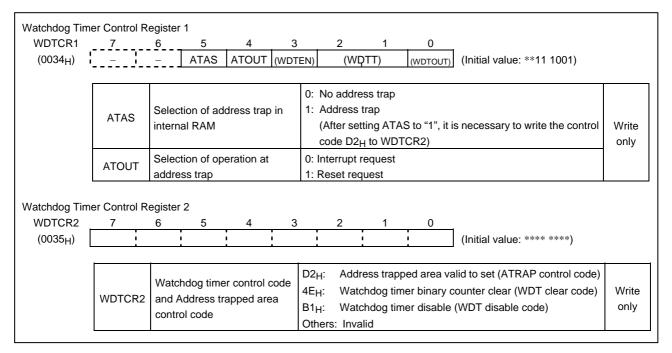

- Watchdog timer

- Interrupt source/internal reset generate (Programmable)

The information contained herein is subject to change without notice. 021023\_D

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or

damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are requipment, intest equipment, intestaining equipment, intustrial robotics, dornestic appliances, etc.). These TOSHBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties. 070122\_C

The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

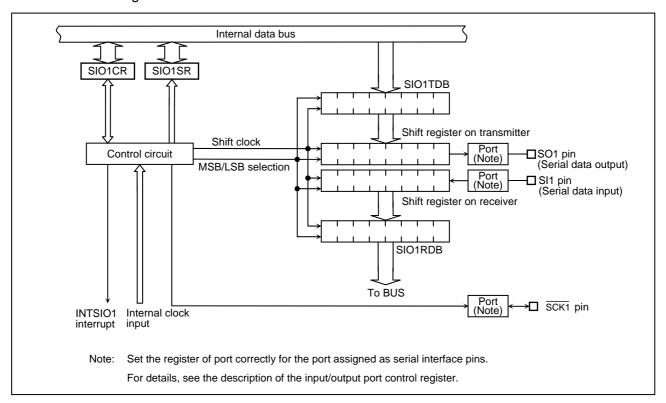

- ♦ Serial interface

- www.DataSUART/SIO: 1ch

- SIO: 1chI<sup>2</sup>C bus: 1ch

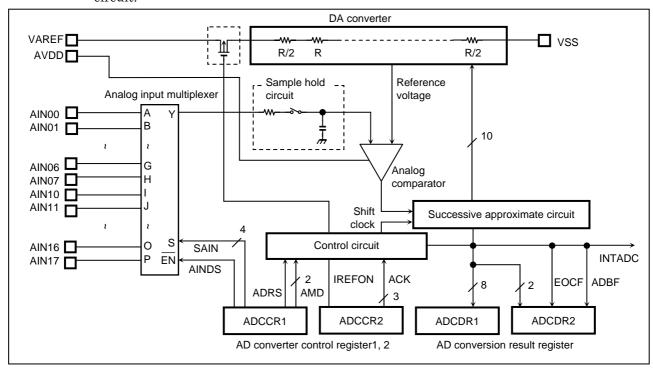

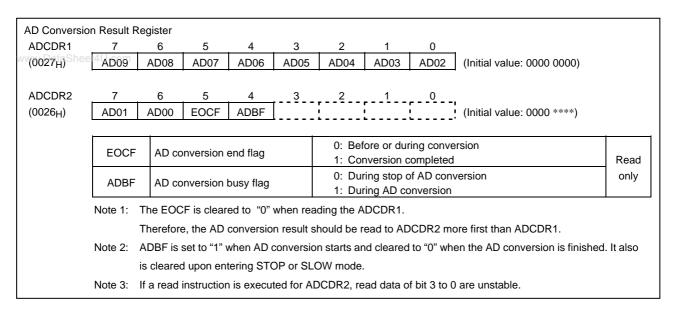

- ♦ 10-bit successive approximation type AD converter

- Analog input: 16 ch

- ♦ Four Key-on wake-up pins

- ♦ Dual clock operation

- Single/dual-clock mode

- ♦ Nine power saving operating modes

- STOP mode: Oscillation stops. Battery/capacitor back-up.

- Port output hold/High-impedance.

- SLOW 1, 2 mode: Low-power consumption operation using low-frequency clock (32.768 kHz)

- IDLE 0 mode: CPU stops, and peripherals operate using high-frequency clock of

- Time-Base-Timer. Release by falling edge of TBTCR<TBTCK> setting.

- IDLE 1 mode: CPU stops, and peripherals operate using high-frequency clock.

- Release by interruputs.

- $\bullet$  IDLE 2 mode: CPU stops, and peripherals operate using high and low-frequency clock.

- Release by interruputs.

- SLEEP 0 mode: CPU stops, and peripherals operate using low-frequency clock of

- time-base-timer. Release by falling edge of TBTCR<TBTCK> setting.

- SLEEP 1 mode: CPU stops, and peripherals operate using low-frequency clock.

- Release by interrupts.

- SLEEP 2 mode: CPU stops, and peripherals operate using high- and low-frequency clock.

- Release by interrupts.

- ♦ Wide operating voltage: 1.8 to 3.6 V at 8 MHz/32.768 kHz

- $2.7\ \text{to}\ 3.6\ \text{V}$  at  $16\ \text{MHz}/32.768\ \text{kHz}$

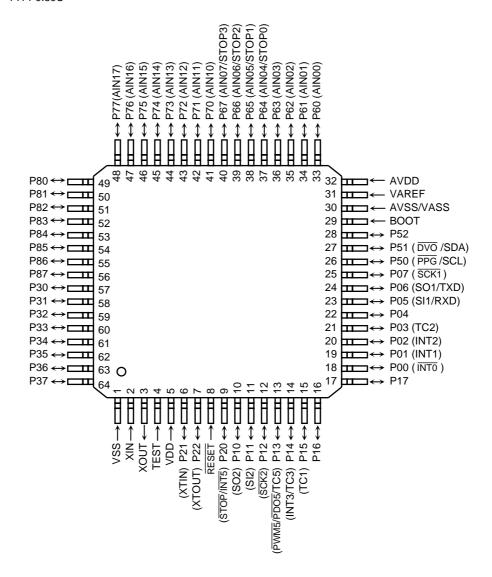

## Pin Assignments (Top view)

www.DataSheet4U.com

LQFP64-P-1010-0.50E QFP64-P-1414-0.80C

**TOSHIBA**

## **Block Diagram**

www.DataSheet4U.com

# Pin Functions (1/2)

| Pin Name             | Input/Output     | Fund                                                                                                                                                                                              | ctions                                                                            |                      |  |

|----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|--|

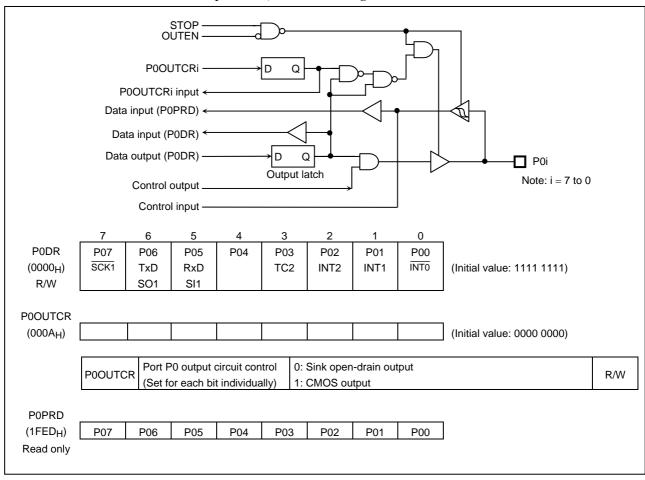

| P07 ( SCK1)          | I/O (I/O)        | 8-bit input/output port with latch.                                                                                                                                                               | Serial clock input/out                                                            | tput 1               |  |

| P06 (TXD, SO1)       | I/O (Output)     | When used as a serial interface output or UART output, respective output latch                                                                                                                    | UART data output, S                                                               | Serial data output 1 |  |

| P05 (RXD, SI1)       | I/O (Input)      | (P0DR) should be set to "1".                                                                                                                                                                      | UART data input, Se                                                               | rial data input 1    |  |

| P04                  | I/O              | When used as an input port, an serial                                                                                                                                                             |                                                                                   |                      |  |

| P03 (TC2)            | I/O (Input)      | interface input, UART input, timer counter input or an external interrupt                                                                                                                         | Timer counter 2 inpu                                                              | t                    |  |

| P02 (INT2)           | I/O (Input)      | input, respective output control                                                                                                                                                                  | External interrupt 2 in                                                           | •                    |  |

| P01 (INT1)           | I/O (Input)      | (P0OUTCR) should be cleared to "0"                                                                                                                                                                | External interrupt 1 in                                                           | •                    |  |

| P00 (INT0)           | I/O (Input)      | after setting P0DR to "1".                                                                                                                                                                        | External interrupt 0 in                                                           | nput                 |  |

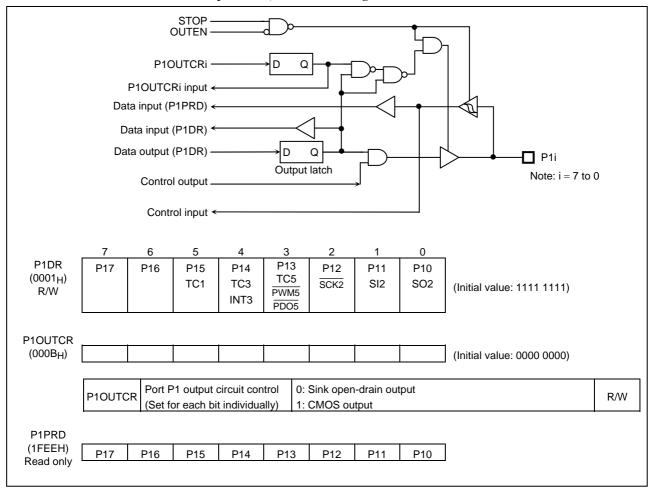

| P17                  | I/O              | 8-bit input/output port with latch. When used as a timer/counter output or                                                                                                                        |                                                                                   |                      |  |

| P16                  | I/O              | serial interface output, respective                                                                                                                                                               |                                                                                   |                      |  |

| P15 (TC1)            | I/O (Input)      | output latch (P1DR) should be set to                                                                                                                                                              | Timer counter 1 inpu                                                              |                      |  |

| P14 (TC3,INT3)       | I/O (Input)      | "1". When used as an input port, a timer counter input, an external interrupt input                                                                                                               | Timer counter 3 inpu<br>External interrupt 3 in                                   | ·                    |  |

| P13                  |                  | or serial interface input, respective                                                                                                                                                             | PWM5 output, PDO5                                                                 | •                    |  |

| ( PWM5 , PDO5 , TC5) | I/O (I/O)        | output control (P10UTCR) should be                                                                                                                                                                | Timer/counter 5 inpu                                                              | • •                  |  |

| P12 ( SCK2 )         | I/O (I/O)        | cleared to "0" after setting P1DR to "1".                                                                                                                                                         | Serial clock input/out                                                            |                      |  |

| P11 (SI2)            | I/O (Input)      |                                                                                                                                                                                                   | Serial data input 2                                                               | •                    |  |

| P10 (SO2)            | I/O (Output)     |                                                                                                                                                                                                   | Serial data output 2                                                              |                      |  |

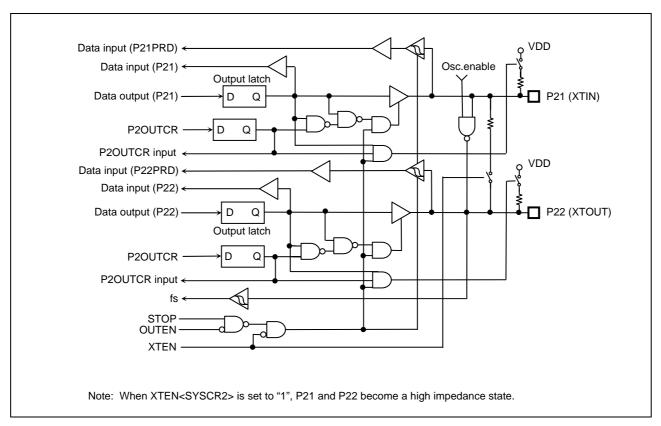

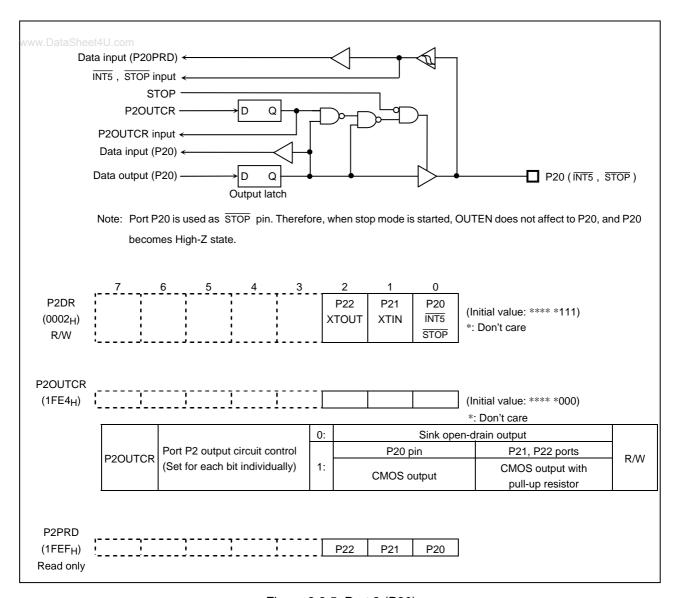

| P22 (XTOUT)          | I/O (Output)     | 3-bit input/output port with latch. When used as an input port or an                                                                                                                              | Resonator connecting pins (32.768 kHz) For inputting external clock, XTIN is used |                      |  |

| P21 (XTIN)           | I/O (Input)      | external interrupt input, respective output control (P2OUTCR) should be                                                                                                                           | and XTOUT is opene                                                                |                      |  |

| P20 (INT5, STOP)     | I/O (Input)      | cleared to "0" after setting output latch (P2DR) to "1".                                                                                                                                          | External interrupt input 5 or STOP mode release signal input                      |                      |  |

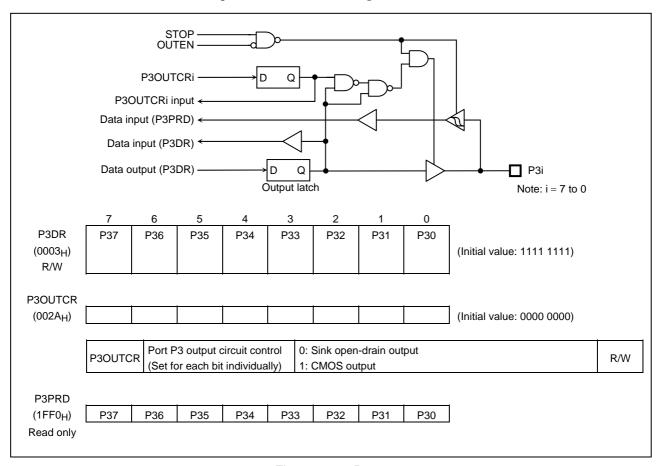

| P37 to P30           | I/O              | 8-bit input/output port with latch (N-ch high-current output). When used as an input port, respective output control (P3OUTCR) should be cleared to "0" after setting output latch (P3DR) to "1". |                                                                                   |                      |  |

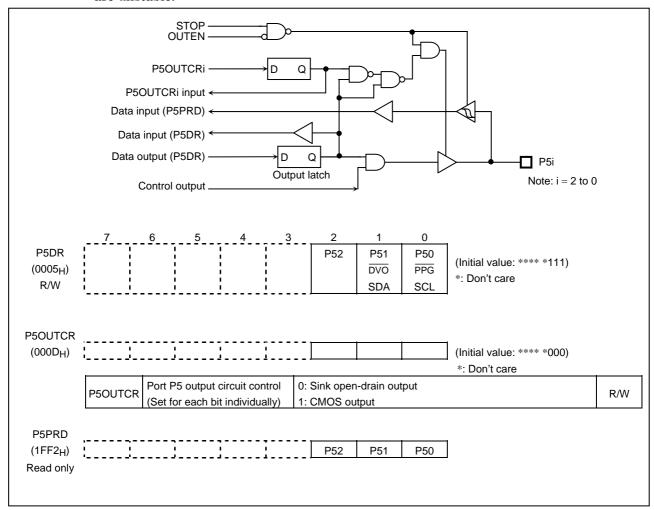

| P52                  | I/O              | 3-bit input/output port with latch (N-ch high-current output). When used as an input port or I <sup>2</sup> C bus interface                                                                       |                                                                                   |                      |  |

| P51 ( DVO , SDA)     | I/O (Output,I/O) | input/output, respective output control (P5OUTCR) should be cleared to "0" after setting output latch (P5DR) to "1".                                                                              | Divider Output/I <sup>2</sup> C bu                                                | us serial data       |  |

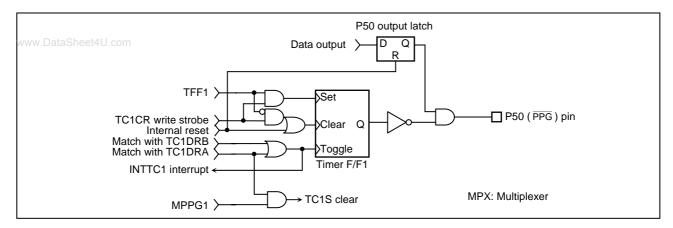

| P50 (PPG, SCL)       | I/O (Output,I/O) | When used as a PPG output or divider output, respective P5DR should be set to "1".                                                                                                                | PPG Output/l <sup>2</sup> C bus serial clock input/output                         |                      |  |

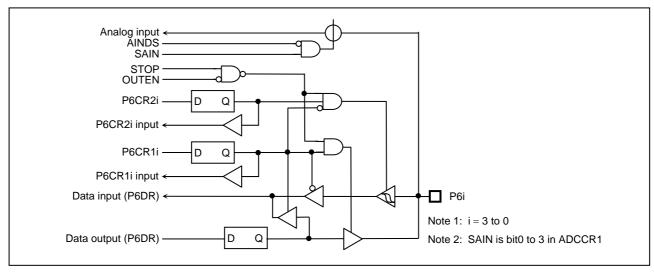

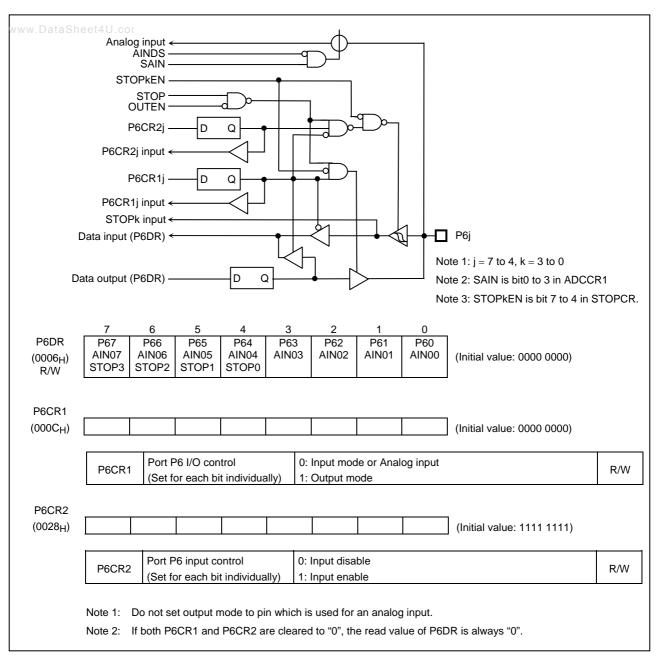

| P67 (AIN07, STOP3)   | I/O (Input)      | 8-bit programmable input/output port (tri-state). Each bit of this port can be                                                                                                                    | STOP 3 input                                                                      |                      |  |

| P66 (AIN06, STOP2)   | I/O (Input)      | individually configured as an input or an                                                                                                                                                         | STOP 2 input                                                                      |                      |  |

| P65 (AIN05, STOP1)   | I/O (Input)      | output under software control. When used as an input port, respective                                                                                                                             | STOP 1 input                                                                      |                      |  |

| P64 (AIN04, STOP0)   | I/O (Input)      | input/output control (P6CR1) should be cleared to "0" after setting input control                                                                                                                 | STOP 0 input                                                                      | AD converter         |  |

| P63 (AIN03)          | I/O (Input)      | (P6CR2) to "1". When used as an analog input or key on wake up input,                                                                                                                             |                                                                                   | analog inputs        |  |

| P62 (AIN02)          | I/O (Input)      | respective P6CR1 should be cleared to                                                                                                                                                             |                                                                                   |                      |  |

| P61 (AIN01)          | I/O (Input)      | "0" after clearing P6CR2 to "0". When used as a key on wake up input,                                                                                                                             |                                                                                   |                      |  |

| P60 (AIN00)          | I/O (Input)      | STOPCR <stopien> should be set to "1". (i = 0 to 3)</stopien>                                                                                                                                     |                                                                                   |                      |  |

## Pin Functions (2/2)

| ww.Datas <b>Pin:Name</b> | Input/Output | Functions                                                                                                                                                                                         | Pin Name                              |  |  |  |

|--------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|

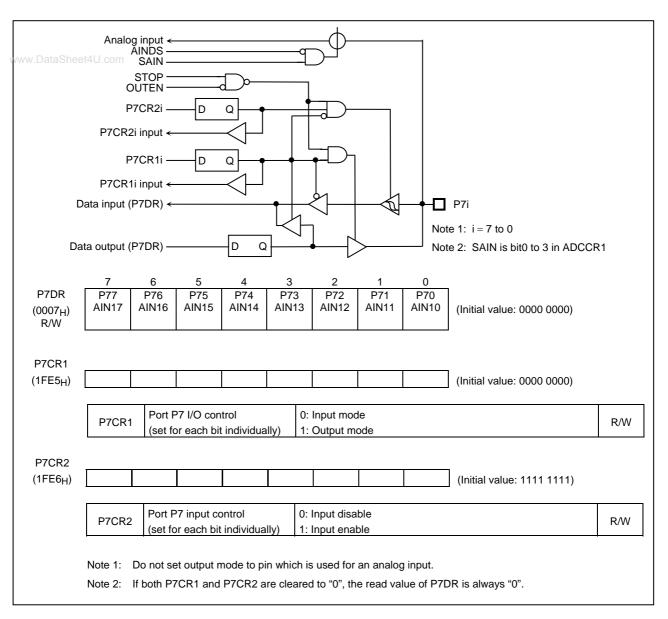

| P77 (AIN17)              | I/O (Input)  | 8-bit programmable input/output port                                                                                                                                                              |                                       |  |  |  |

| P76 (AIN16)              | I/O (Input)  | (tri-state). Each bit of this port can be individually configured as an input or an                                                                                                               |                                       |  |  |  |

| P75 (AIN15)              | I/O (Input)  | output under software control. When                                                                                                                                                               |                                       |  |  |  |

| P74 (AIN14)              | I/O (Input)  | used as an input port, respective input/output control (P7CR1) should be                                                                                                                          | AD converter analog inputs            |  |  |  |

| P73 (AIN13)              | I/O (Input)  | cleared to "0" after setting input control                                                                                                                                                        | AD converter arraing inputs           |  |  |  |

| P72 (AIN12)              | I/O (Input)  | (P7CR2) to "1". When used as an analog input, respective P7CR1 should be                                                                                                                          |                                       |  |  |  |

| P71 (AIN11)              | I/O (Input)  | cleared to "0" after clearing P7CR2 to                                                                                                                                                            |                                       |  |  |  |

| P70 (AIN10)              | I/O (Input)  | "0".                                                                                                                                                                                              |                                       |  |  |  |

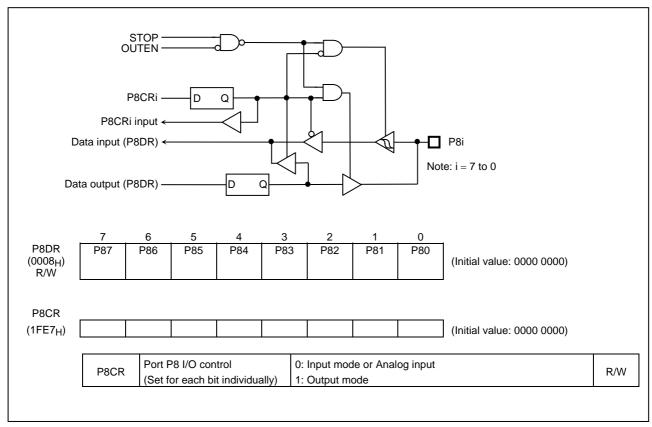

| P87 to P80               | I/O          | 8-bit input/output port with latch (N-ch high-current output). When used as an input port, respective output control (P8OUTCR) should be cleared to "0" after setting output latch (P8DR) to "1". |                                       |  |  |  |

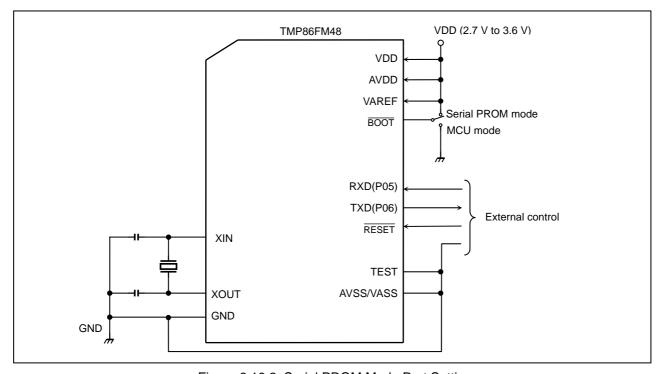

| XIN, XOUT                | Input Output | Resonator connecting pins for high-frequency clock. For inputting external clock, XIN is used and XOUT is opened.                                                                                 |                                       |  |  |  |

| RESET                    | Input        | Reset signal input                                                                                                                                                                                |                                       |  |  |  |

| TEST                     | Input        | Test pin for out-going test. Be fixed to low.                                                                                                                                                     |                                       |  |  |  |

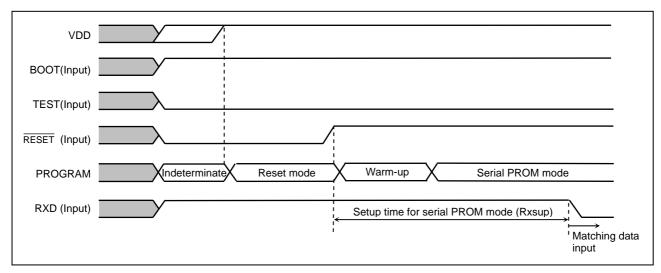

| воот                     | Input        | Serial prom mode control input. When wribe fixed to high level.                                                                                                                                   | ting to FLASH memory, BOOT pin should |  |  |  |

| VDD, VSS                 |              | Power supply for operation                                                                                                                                                                        |                                       |  |  |  |

| VAREF                    | Dawar Curati | Analog reference voltage for AD conversion                                                                                                                                                        | on                                    |  |  |  |

| AVDD                     | Power Supply | AD circuit power supply                                                                                                                                                                           |                                       |  |  |  |

| AVSS/VASS                |              | AD circuit power supply/Analog reference GND for AD conversion                                                                                                                                    |                                       |  |  |  |

TOSHIBA TMP86FM48

## **Operational Description**

#### 1 CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller.

This section provides a description of the CPU core, the program memory, the data memory, the external memory interface, and the reset circuit.

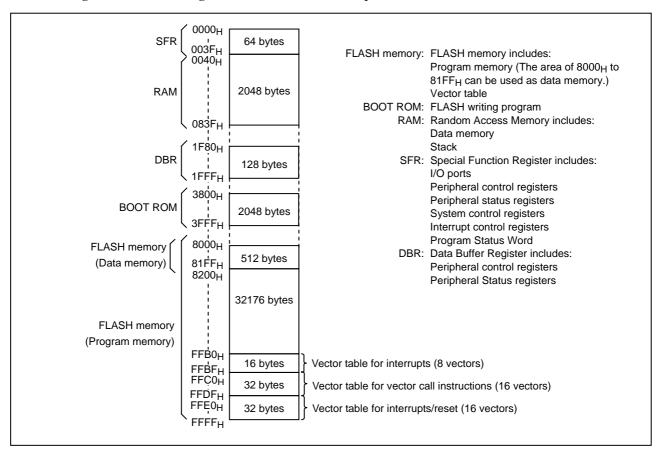

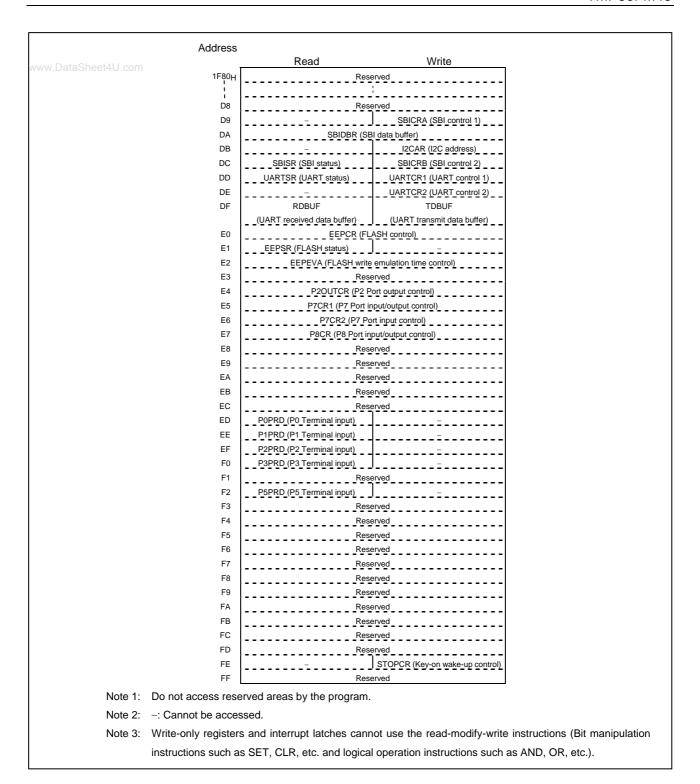

#### 1.1 Memory Address Map

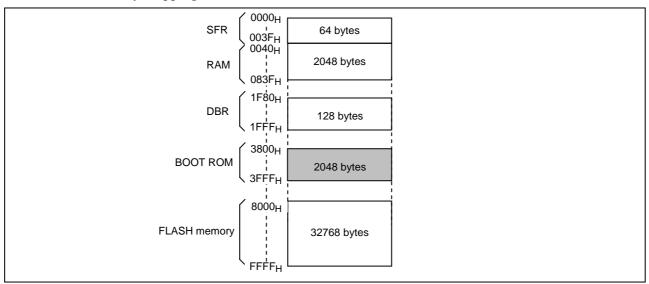

The TMP86FM48 memory consists of 5 blocks: FLASH memory, BOOT ROM, RAM, DBR (Data buffer register) and SFR (Special function register). They are all mapped in 64-Kbyte address space. Figure 1.1.1 shows the TMP86FM48 memory address map. The general-purpose registers are not assigned to the RAM address space.

Figure 1.1.1 Memory Address Maps

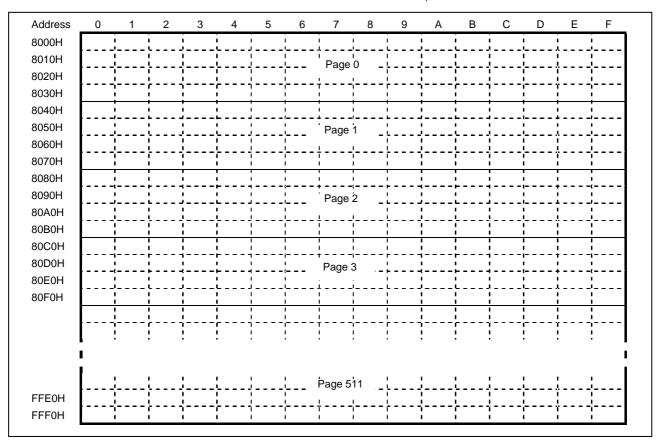

#### 1.2 Program Memory (FLASH)

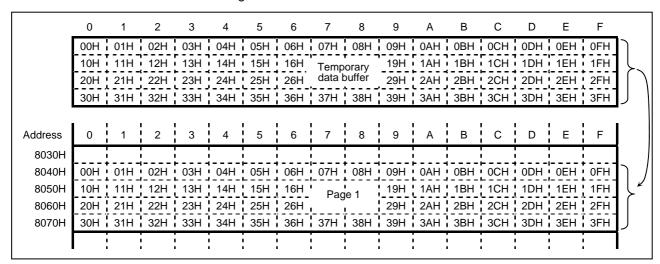

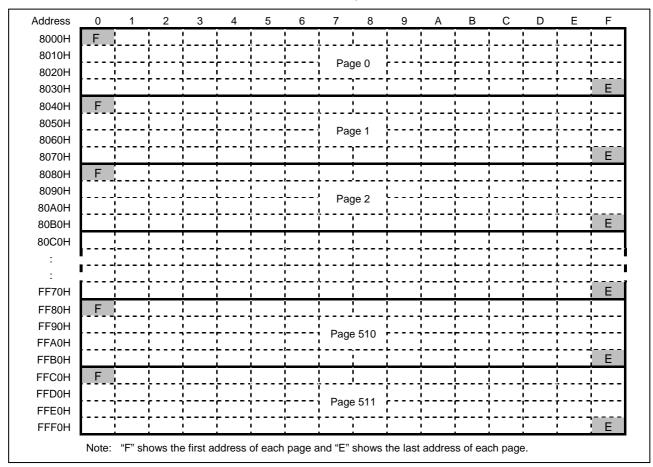

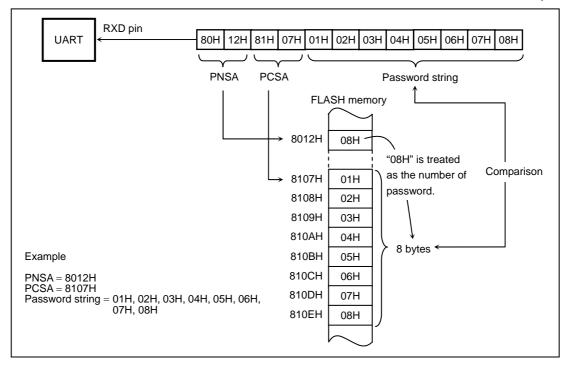

The TMP86FM48 has a 32 K  $\times$  8 bits (Address 8000H to FFFFH) of program memory (FLASH). The area of 8000H to 81FFH can be used as a  $512 \times 8$  bits data memory of FLASH.

## 1.3 Data Memory (RAM)

www.DataSheeTheeTMP86FM48 has 2048 bytes of internal RAM. The first 192 bytes (0040<sub>H</sub> to 00FF<sub>H</sub>) of the internal RAM are located in the direct area; instructions with shorten operations are available against such an area.

The data memory contents become unstable when the power supply is turned on; therefore, the data memory should be initialized by an initialization routine.

| Example: Cle | ars RAM to " | 00H".      |   |                           |

|--------------|--------------|------------|---|---------------------------|

|              | LD           | HL, 0040H  | ; | Start address setup       |

|              | LD           | A, H       | ; | Initial value (00H) setup |

|              | LD           | BC, 07FFH  | ; |                           |

| SRAMCLR:     | LD           | (HL), A    |   |                           |

|              | INC          | HL         |   |                           |

|              | DEC          | BC         |   |                           |

|              | JRS          | F, SRAMCLR |   |                           |

|              |              |            |   |                           |

TOSHIBA TMP86FM48

### 1.4 System Clock Controller

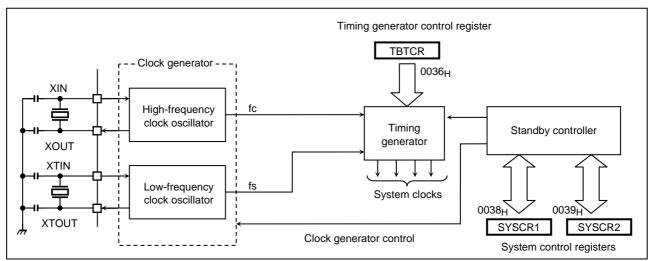

www.DataSheeThe system clock controller consists of a clock generator, a timing generator, and a standby controller.

Figure 1.4.1 System Clock Control

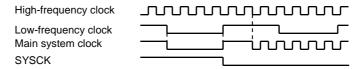

#### 1.4.1 Clock Generator

The clock generator generates the basic clock which provides the system clocks supplied to the CPU core and peripheral hardware. It contains two oscillation circuits: one for the high-frequency clock and one for the low-frequency clock. Power consumption can be reduced by switching of the standby controller to low-power operation based on the low-frequency clock.

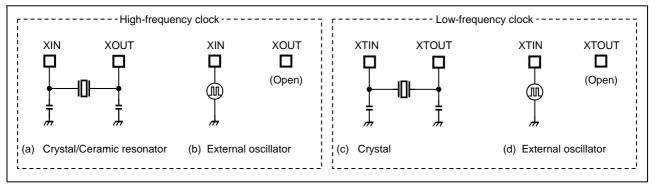

The high-frequency (fc) and low-frequency (fs) clocks can easily be obtained by connecting a resonator between the XIN/XOUT and XTIN/XTOUT pins respectively. Clock input from an external oscillator is also possible. In this case, external clock is applied to XIN/XTIN pin with XOUT/XTOUT pin not connected.

Figure 1.4.2 Examples of Resonator Connection

Note: The function to monitor the basic clock directly at external is not provided for hardware, however, with disabling all interrupts and watchdog timers, the oscillation frequency can be adjusted by monitoring the pulse which the fixed frequency is outputted to the port by the program.

The system to require the adjustment of the oscillation frequency should create the program for the adjustment in advance.

#### 1.4.2 Timing Generator

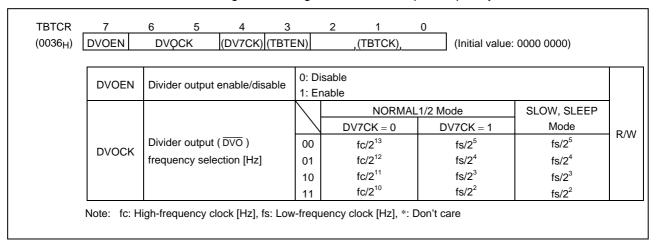

www.DataSheet4U.cThe timing generator generates the various system clocks supplied to the CPU core and peripheral hardware from the basic clock (fc or fs). The timing generator provides the following functions.

- a. Generation of main system clock

- b. Generation of divider output (DVO) pulses

- c. Generation of source clocks for time base timer

- d. Generation of source clocks for watchdog timer

- e. Generation of internal source clocks for timer/counters and serial interface

- f. Generation of warm-up clocks for releasing STOP mode

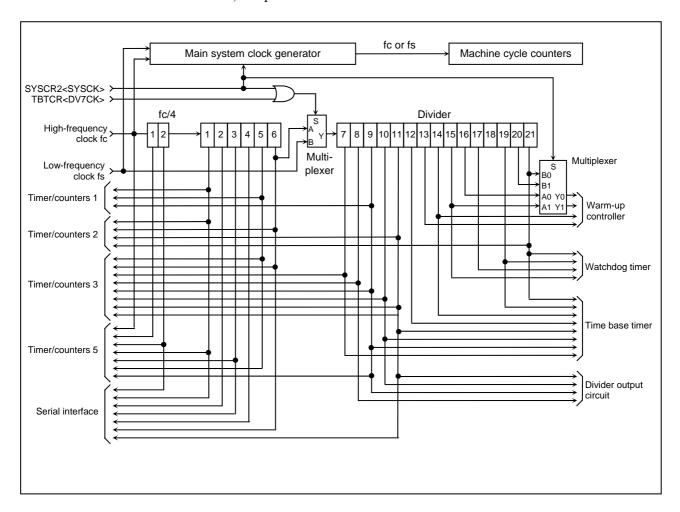

#### (1) Configuration of timing generator

The timing generator consists of a 2-stage prescaler, a 21-stage divider, a main system clock generator, and machine cycle counters.

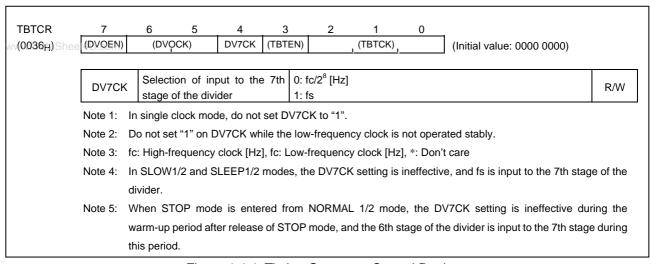

An input clock to the 7th stage of the divider depends on the operating mode, TBTCR<DV7CK>, that is shown in Figure 1.4.4. As reset and STOP mode started/canceled, the prescaler and the divider are cleared to "0".

Figure 1.4.3 Configuration of Timing Generator

Figure 1.4.4 Timing Generator Control Register

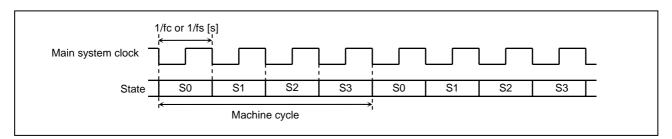

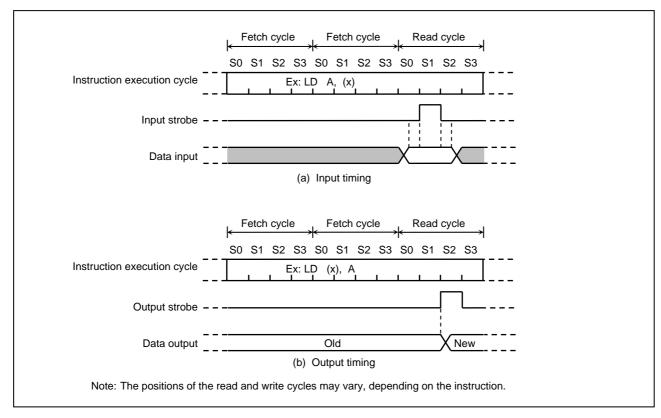

#### (2) Machine cycle

Instruction execution and peripheral hardware operation are synchronized with the main system clock.

The minimum instruction execution unit is called an "machine cycle". There are a total of 10 different types of instructions for the TLCS-870/C series: ranging from 1-cycle instructions which require one machine cycle for execution to 10-cycle instructions which require 10 machine cycles for execution.

A machine cycle consists of 4 states (S0 to S3), and each state consists of one main system clock.

Figure 1.4.5 Machine Cycle

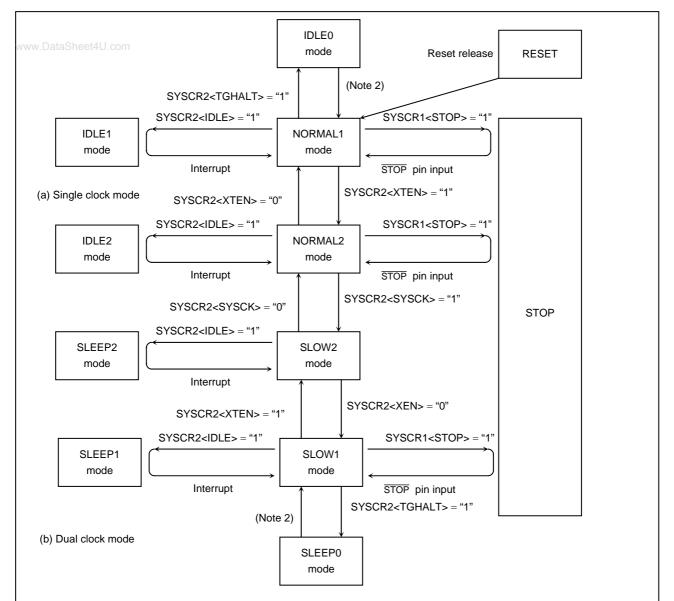

#### 1.4.3 Operation Mode Control Circuit

www.DataSheet4U.cThe operation mode control circuit starts and stops the oscillation circuits for the high-frequency and low-frequency clocks, and switches the main system clock. There are two operating modes: single-clock and dual-clock. These modes are controlled by the system control registers (SYSCR1 and SYSCR2).

Figure 1.4.6 shows the operating mode transition diagram and Figure 1.4.7 shows the system control registers.

#### (1) Single-clock mode

Only the oscillation circuit for the high-frequency clock is used, and P21 (XTIN) and P22 (XTOUT) pins are used as input/output ports. The main-system clock is obtained from the high-frequency clock. In the single-clock mode, the machine cycle time is 4/fc [s].

#### a. NORMAL1 mode

In this mode, both the CPU core and on-chip peripherals operate using the high-frequency clock.

The TMP86FM48 is placed in this mode after reset.

#### b. IDLE1 mode

In this mode, the internal oscillation circuit remains active. The CPU and the watchdog timer are halted; however on-chip peripherals remain active (Operate using the high-frequency clock).

IDLE1 mode is started by SYSCR2<IDLE>, and IDLE1 mode is released to NORMAL1 mode by an interrupt request from the on-chip peripherals or external interrupt inputs. When the IMF (Interrupt master enable flag) is "1" (Interrupt enable), the execution will resume with the acceptance of the interrupt, and the operation will return to normal after the interrupt service is completed. When the IMF is "0" (Interrupt disable), the execution will resume with the instruction which follows the IDLE1 mode start instruction.

#### c. IDLE0 mode

In this mode, all the circuit, except oscillator and the time-base-timer, stops operation.

This mode is enabled by setting "1" on bit TGHALT on the system control register 2 (SYSCR2).

When IDLE0 mode starts, the CPU stops and the timing generator stops feeding the clock to the peripheral circuits other than TBT. Then, upon detecting the falling edge of the source clock selected with TBTCR<TBTCK>, the timing generator starts feeding the clock to all peripheral circuits.

When returned from IDLE0 mode, the CPU restarts operating, entering NORMAL1 mode back again. IDLE0 mode is entered and returned regardless of how TBTCR<TBTEN> is set. When IMF = "1", EF7 (TBT interrupt individual enable flag) = "1", and TBTCR<TBTEN> = "1", interrupt processing is performed. When IDLE0 mode is entered while TBTCR<TBTEN> = "1", the INTTBT interrupt latch is set after returning to NORMAL1 mode.

#### (2) Dual-clock mode

Both the high-frequency and low-frequency oscillation circuits are used in this mode. P21 (XTIN) and P22 (XTOUT) pins cannot be used as input/output ports. The main system clock is obtained from the high-frequency clock in NORMAL2 and IDLE2 modes, and is obtained from the low-frequency clock in SLOW and SLEEP modes. The machine cycle time is 4/fc [s] in the NORMAL2 and IDLE2 modes, and 4/fs [s] (122  $\mu$ s at fs = 32.768 kHz) in the SLOW and SLEEP modes.

The TLCS-870/C is placed in the single-clock mode during reset. To use the dual-clock mode, the low-frequency oscillator should be turned on at the start of a program.

#### a. NORMAL2 mode

In this mode, the CPU core operates with the high-frequency clock. On-chip peripherals operate using the high-frequency clock and/or low-frequency clock.

#### b. SLOW2 mode

In this mode, the CPU core operates with the low-frequency clock, while both the high-frequency clock and the low-frequency clock are operated. On-chip peripherals are triggered by the low-frequency clock. As the SYSCK on SYSCR2 becomes "0", the hardware changes into NORMAL2 mode. As the XEN on SYSCR2 becomes "0", the hardware changes into SLOW1 mode. Do not clear XTEN to "0" during SLOW2 mode.

#### c. SLOW1 mode

This mode can be used to reduce power-consumption by turning off oscillation of the high-frequency clock. The CPU core and on-chip peripherals operate using the low-frequency clock.

Switching back and forth between SLOW1 and SLOW2 modes are performed by XEN bit on the system control register 2 (SYSCR2). In SLOW1 and SLEEP mode, the input clock to the 1st stage of the divider is stopped; output from the 1st to 6th stages is also stopped.

#### d. IDLE2 mode

In this mode, the internal oscillation circuit remain active. The CPU and the watchdog timer are halted; however, on-chip peripherals remain active (Operate using the high-frequency clock and/or the low-frequency clock). Starting and releasing of IDLE2 mode are the same as for IDLE1 mode, except that operation returns to NORMAL2 mode.

#### e. SLEEP1 mode

In this mode, the internal oscillation circuit of the low-frequency clock remains active. The CPU, the watchdog timer, and the internal oscillation circuit of the high-frequency clock are halted; however, on-chip peripherals remain active (Operate using the low-frequency clock). Starting and releasing of SLEEP mode are the same as for IDLE1 mode, except that operation returns to SLOW mode. In SLOW and SLEEP mode, the input clock to the 1st stage of the divider is stopped; output from the 1st to 6th stages is also stopped.

#### f. SLEEP2 mode

www.DataSheet4U.com

The SLEEP2 mode is the IDLE mode corresponding to the SLOW2 mode. The status under the SLEEP2 mode is same as that under the SLEEP1 mode, except for the oscillation circuit of the high-frequency clock.

#### g. SLEEP0 mode

In this mode, all the circuit, except oscillator and the time-base-timer, stops operation.

This mode is enabled by setting "1" on bit TGHALT on the system control register 2 (SYSCR2).

When SLEEP0 mode starts, the CPU stops and the timing generator stops feeding the clock to the peripheral circuits other than TBT. Then, upon detecting the falling edge of the source clock selected with TBTCR<TBTCK>, the timing generator starts feeding the clock to all peripheral circuits.

When returned from SLEEP0 mode, the CPU restarts operating, entering SLOW1 mode back again. SLEEP0 mode is entered and returned regardless of how TBTCR<TBTEN> is set. When IMF = "1", EF7 (TBT interrupt individual enable flag) = "1", and TBTCR<TBTEN> = "1", interrupt processing is performed. When SLEEP0 mode is entered while TBTCR<TBTEN> = "1", the INTTBT interrupt latch is set after returning to SLOW1 mode.

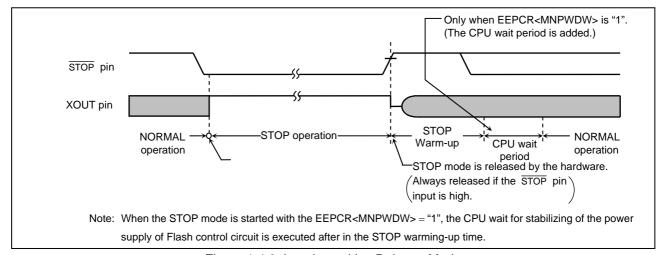

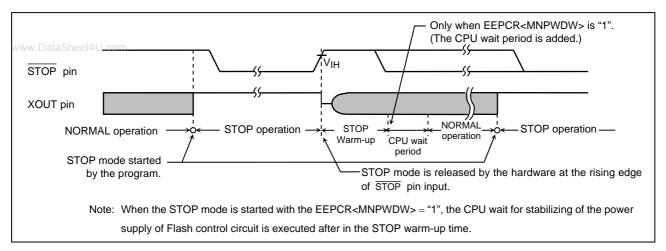

#### (3) STOP mode

In this mode, the internal oscillation circuit is turned off, causing all system operations to be halted. The internal status immediately prior to the halt is held with a lowest power consumption during STOP mode.

STOP mode is started by the system control register 1 (SYSCR1), and STOP mode is released by a inputting (either level-sensitive or edge-sensitive can be programmably selected) to the  $\overline{\text{STOP}}$  pin or key on wake up pin input which is enabled by STOPCR. After the warm-up period is completed, the execution resumes with the instruction which follows the STOP mode start instruction.

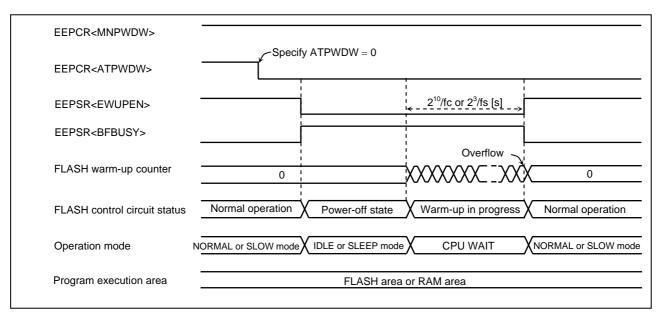

- Note 1: When the IDLE0/1/2 and SLEEP0/1/2 modes are started with the EEPCR<ATPWDW> = "0", the CPU wait period for stabilizing of the power supply of Flash control circuit is executed after being released from these mode.

- Note 2: When the STOP mode is started with the EEPCR<MNPWDW> = "1", the CPU wait period for stablizing of the power supply of Flash control circuit is executed after in the STOP warm-up time.

Note 1: NORMAL1 and NORMAL2 modes are generically called NORMAL; SLOW1 and SLOW2 are called SLOW; IDLE0, IDLE1 and IDLE2 are called IDLE; SLEEP0, SLEEP1 and SLEEP2 are called SLEEP.

Note 2: The mode is released by falling edge of TBTCR<TBTCK> setting.

| 0      | Operating Mode Oscilla |                |               |                             | TDT     | Other       | Machine    |

|--------|------------------------|----------------|---------------|-----------------------------|---------|-------------|------------|

| Oper   |                        | High Frequency | Low Frequency | CPU Core                    | TBT     | Peripherals | Cycle Time |

|        | RESET                  |                |               | Reset                       | Reset   | Reset       |            |

| Single | NORMAL1                | Oscillation    |               | Operate                     |         | Operate     | 4/fc [s]   |

| Clock  | IDLE1                  | Oscillation    | Stop          |                             | Operate | Operate     |            |

| Olock  | IDLE0                  |                |               | Halt                        |         | Halt        | _          |

|        | STOP                   | Stop           |               |                             | Halt    | Hait        | _          |

|        | NORMAL2                |                |               | Operate with high frequency |         | Operate     | 4/fc [s]   |

|        | IDLE2                  | Oscillation    |               | Halt                        |         |             | 4/10 [5]   |

|        | SLOW2                  | Oscillation    |               | Operate with low frequency  |         |             |            |

| Dual   | SLEEP2                 |                | Oscillation   | Halt                        | Operate |             | 4/fs [s]   |

| Clock  | SLOW1                  |                |               | Operate with low frequency  |         |             | 4/15 [5]   |

|        | SLEEP1                 | Ston           |               |                             |         |             |            |

|        | SLEEP0                 | Stop           |               | Halt                        |         | 1.1-14      |            |

|        | STOP                   |                | Stop          |                             | Halt    | Halt        | _          |

Figure 1.4.6 Operating Mode Transition Diagram

System Control Register 1

SYSCR1 7 6 5 4 3 2 1 0

(0038<sub>H</sub>) STOP RELM RETM OUTEN WUT (Initial value: 0000 00\*\*)

| STOP  | STOP mode start                              |                                  | 0: CPU core and peripherals remain active 1: CPU core and peripherals are halted (Start STOP mode)                                                                                                                      |                                                                                                                                                                                                 |  |  |

|-------|----------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RELM  | Release method for STOP pin (P20)            |                                  | 0: Edge-sensitive release 1: Level-sensitive release                                                                                                                                                                    |                                                                                                                                                                                                 |  |  |

| RETM  | Operating mode after STOP mode               |                                  | 0: Return to NORMAL1/2 mode 1: Return to SLOW1 mode                                                                                                                                                                     |                                                                                                                                                                                                 |  |  |

| OUTEN | Port output during STOP mode                 | 0: High impedance 1: Output kept |                                                                                                                                                                                                                         |                                                                                                                                                                                                 |  |  |

| WUT   | Warm-up time at releasing STOP mode (Note 8) | 00<br>01<br>10<br>11             | Return to NORMAL mode $3 \times 2^{16} / \text{fc} + (2^{10} / \text{fc})$ $2^{16} / \text{fc} + (2^{10} / \text{fc})$ $3 \times 2^{14} / \text{fc} + (2^{10} / \text{fc})$ $2^{14} / \text{fc} + (2^{10} / \text{fc})$ | Return to SLOW mode<br>$3 \times 2^{13}/\text{fs} + (2^3/\text{fs})$<br>$2^{13}/\text{fs} + (2^3/\text{fs})$<br>$3 \times 2^6/\text{fs} + (2^3/\text{fs})$<br>$2^6/\text{fs} + (2^3/\text{fs})$ |  |  |

- Note 1: Always set RETM to "0" when transiting from NORMAL mode to STOP mode. Always set RETM to "1" when transiting from SLOW mode to STOP mode.

- Note 2: When STOP mode is released with RESET pin input, a return is made to NORMAL1 regardless of the RETM contents.

- Note 3: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz], \*: Don't care

- Note 4: Bits 1 and 0 in SYSCR1 are read as undefined data when a read instruction is executed.

- Note 5: As the hardware becomes STOP mode under OUTEN = "0", input value is fixed to "0"; therefore it may cause interrupt request on account of falling edge.

- Note 6: When the key-on wake-up input (STOP0 to STOP3) is used, RELM should be set to "1".

- Note 7: Port P20 is used as \$\overline{STOP}\$ pin. Therefore, when stop mode is started, OUTEN does not affect to P20, and P20 becomes High-Z mode.

- Note 8: When the STOP mode is started with the EEPCR<MNPWDW> = "1", the CPU wait period for stabilizing of the power supply of Flash control circuit is executed after in the STOP warm-up time.

(The CPU wait period for FLASH is shown in parentheses)

#### System Control Register 2

SYSCR2 (0039<sub>H</sub>)

|   | 7   | 6    | 5     | 4    | 3 | 2      | 1 | 0 | _                          |

|---|-----|------|-------|------|---|--------|---|---|----------------------------|

| ĺ | XEN | XTEN | SYSCK | IDLE |   | TGHALT |   |   | (Initial value: 1000 *0**) |

| XEN    | High-frequency oscillator control                       | 0: Turn off oscillation 1: Turn on oscillation                                                                                      |     |  |  |

|--------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| XTEN   | Low-frequency oscillator control                        | 0: Turn off oscillation 1: Turn on oscillation                                                                                      |     |  |  |

| SYSCK  | Main system clock select (write)/main                   | 0: High-frequency clock                                                                                                             | 1   |  |  |

| STOCK  | system clock monitor (read)                             | 1: Low-frequency clock                                                                                                              |     |  |  |

| IDLE   | CPU and watchdog timer control (IDLE1/2, SLEEP1/2 mode) | 0: CPU and watchdog timer remain active 1: CPU and watchdog timer are stopped (start IDLE1/2, SLEEP1/2 mode)                        | R/W |  |  |

| TGHALT | TG control (IDLE0, SLEEP0 mode)                         | O: Feeding clock to all peripherals from TG     1: Stop feeding clock to peripherals except TBT from TG. (Start IDLE0, SLEEP0 mode) |     |  |  |

- Note 1: A reset is applied if both XEN and XTEN are cleared to "0", XEN is cleared to "0" when SYSCK = "0", or XTEN is cleared to "0" when SYSCK = "1".

- Note 2: \*: Don't care, TG: Timing generator

- Note 3: Bits 3, 1 and 0 in SYSCR2 are always read as undefined value.

- Note 4: Do not set IDLE and TGHALT to "1" simultaneously.

- Note 5: Because returning from IDLE0/SLEEP0 to NORMAL1/SLOW1 is executed by the asynchronous internal clock, the period of IDLE0/SLEEP0 mode might be shorter than the period setting by TBTCR<TBTCK>.

- Note 6: When IDLE1/2 or SLEEP1/2 mode is released, IDLE is automatically cleared to "0".

- Note 7: When IDLE0 or SLEEP0 mode is released, TGHALT is automatically cleared to "0".

- Note 8: Before setting TGHALT to "1", be sure to stop peripherals. If peripherals are not stopped, the interrupt latch of peripherals may be set after IDLE0 or SLEEP0 mode is released.

Figure 1.4.7 System Control Registers

#### 1.4.4 Operating Mode Control

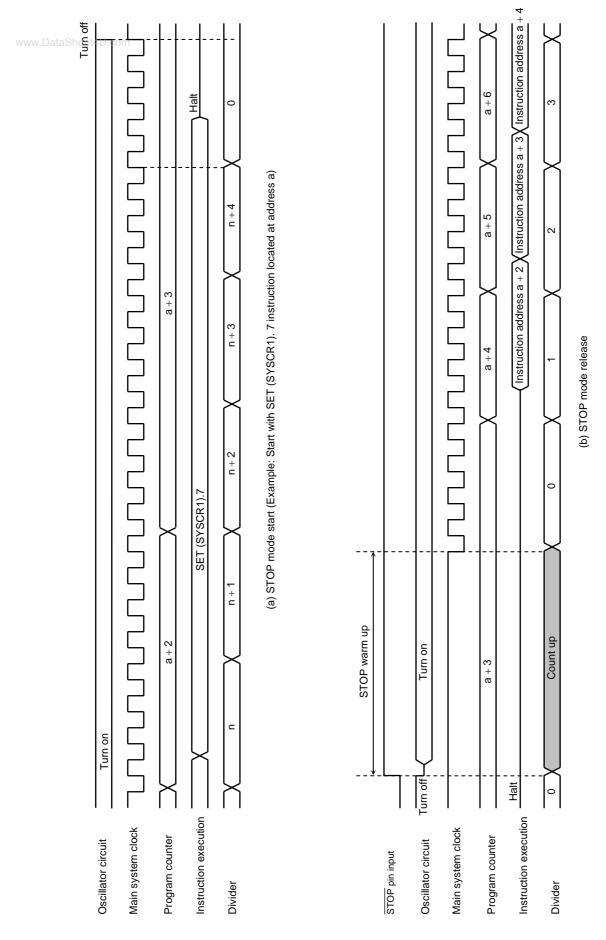

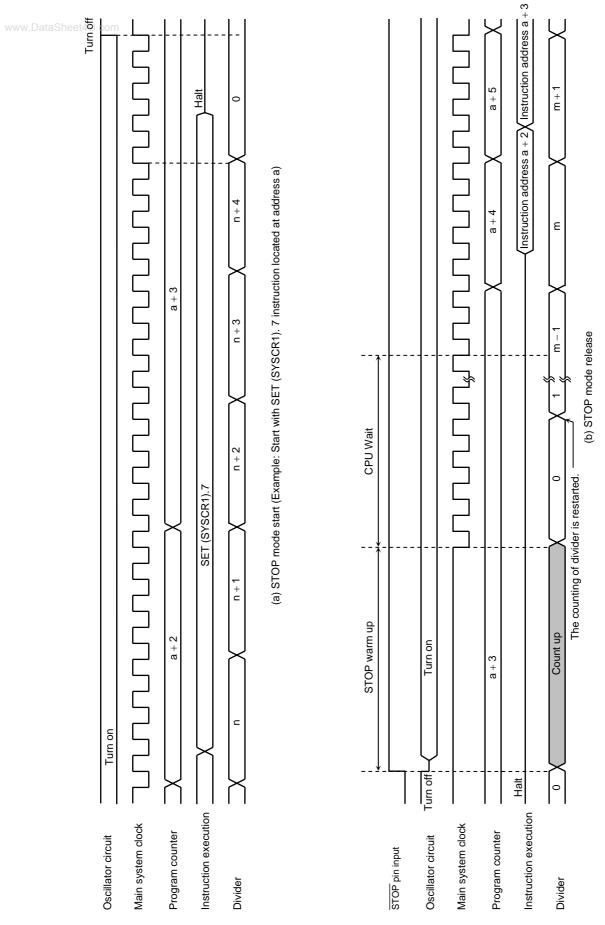

www.DataSheet41(1)onSTOP mode

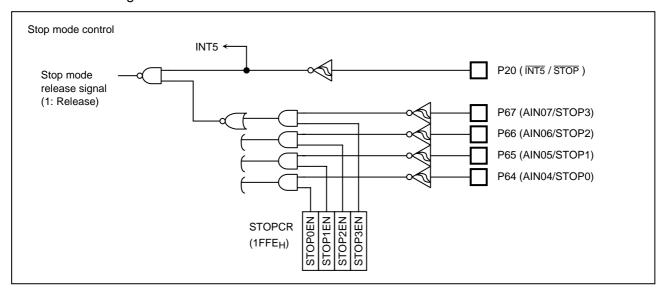

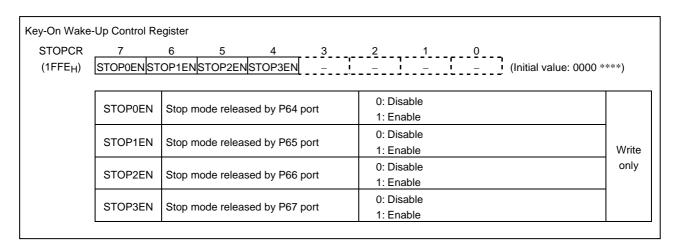

STOP mode is controlled by the system control register 1, the STOP pin input and key-on wake-up input (STOP0 to STOP3) which is controlled by the STOP mode release control register (STOPCR).

The  $\overline{STOP}$  pin is also used both as a port P20 and an  $\overline{INT5}$  (External interrupt input 5) pin.

STOP mode is started by setting SYSCR1<STOP> to "1". During STOP mode, the following status is maintained.

- a. Oscillations are turned off, and all internal operations are halted.

- b. The data memory, registers, the program status word and port output latches are all held in the status in effect before STOP mode was entered.

- c. The prescaler and the divider of the timing generator are cleared to "0".

- d. The program counter holds the address 2 ahead of the instruction (e.g. [SET (SYSCR1).7]) which started STOP mode.

STOP mode includes a level-sensitive mode and an edge-sensitive mode, either of which can be selected with the SYSCR1<RELM>. Do not use any STOPx (x: 0 to 3) pin input for releasing STOP mode in edge-sensitive mode.

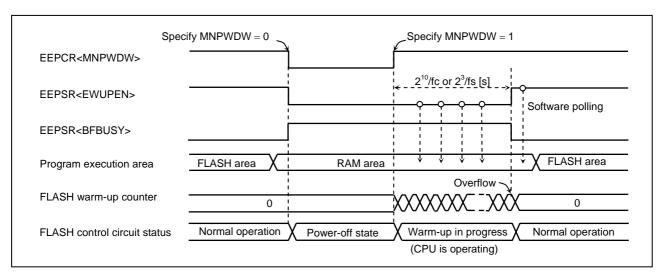

When the STOP mode is started with the EEPCR<MNPWDW> = "1", the CPU wait period for stabilizing of the power supply of Flash control circuit is executed after in the STOP warming-up time.

- Note 1: The STOP mode can be released by either the STOP or key-on wake-up pin (STOP0 to STOP3). However, because the STOP pin is different from the key-on wake-up and can not inhibit the release input, the STOP pin must be used for releasing STOP mode.

- Note 2: During stop period (from start of STOP mode to end of warm-up), due to changes in the external interrupt pin signal, interrupt latches may be set to "1" and interrupts may be accepted immediately after STOP mode is released. Before starting STOP mode, therefore, disable interrupts. Also, before enabling interrupts after STOP mode is released, clear unnecessary interrupt latches.

#### a. Level-sensitive release mode (RELM = "1")

In this mode, STOP mode is released by setting the  $\overline{\text{STOP}}$  pin high or setting the STOPx (x: 0 to 3) pin input which is enabled by STOPCR. This mode is used for capacitor back-up when the main power supply is cut off and long term battery back-up.

When the  $\overline{\text{STOP}}$  pin input is high, executing an instruction which starts STOP mode will not place in STOP mode but instead will immediately start the release sequence (Warm-up). Thus, to start STOP mode in the level-sensitive release mode, it is necessary for the program to first confirm that the  $\overline{\text{STOP}}$  pin input is low. The following two methods can be used for confirmation.

- a. Testing a port P20.

- b. Using an external interrupt input  $\overline{\text{INT5}}$  ( $\overline{\text{INT5}}$  is a falling edge-sensitive input).

|                     | Example 1: S  | tarting STOP | mode from NORMAL mode by | y tes | ting a port P20.                                                 |

|---------------------|---------------|--------------|--------------------------|-------|------------------------------------------------------------------|

|                     |               | LD           | (SYSCR1), 01010000B      | ;     | Sets up the level-sensitive release mode                         |

| www.DataSheet4U.com | SSTOPH:       | TEST         | (P2PRD). 0               | ;     | Wait until the STOP pin input goes low                           |

|                     |               |              |                          |       | level                                                            |

|                     |               | JRS          | F, SSTOPH                |       |                                                                  |

|                     |               | SET          | (SYSCR1).7               | ;     | Starts STOP mode                                                 |

|                     | Example 2: Si | tarting STOP | mode from NORMAL mode w  | ith a | n INT5 interrupt.                                                |

|                     | PINT5:        | TEST         | (P2PRD). 0               | ;     | To reject noise, STOP mode does not start if port P20 is at high |

|                     |               | JRS          | F, SINT5                 |       |                                                                  |

|                     |               | LD           | (SYSCR1), 01010000B      | ;     | Sets up the level-sensitive release mode.                        |

|                     |               | SET          | (SYSCR1). 7              | ;     | Starts STOP mode                                                 |

|                     | SINT5:        | RETI         |                          |       |                                                                  |

Figure 1.4.8 Level-sensitive Release Mode

Note 1: Even if the STOP pin input is low after warming up start, the STOP mode is not restarted.

Note 2: In this case of changing to the level-sensitive mode from the edge-sensitive mode, the release mode is not switched until a rising edge of the STOP pin input is detected.

#### b. Edge-sensitive release mode (RELM = "0")

In this mode, STOP mode is released by a rising edge of the  $\overline{\text{STOP}}$  pin input. This is used in applications where a relatively short program is executed repeatedly at periodic intervals. This periodic signal (For example, a clock from a low-power consumption oscillator) is input to the  $\overline{\text{STOP}}$  pin. In the edge-sensitive release mode, STOP mode is started even when the  $\overline{\text{STOP}}$  pin input is high level. Do not use any STOPx (x: 0 to 3) pin input for releasing STOP mode in edge-sensitive release mode.

Example: Starting STOP mode from NORMAL mode

LD (SYSCR1), 10010000B ; Starts after specified to the edge-sensitive

release mode

Figure 1.4.9 Edge-sensitive Release Mode

STOP mode is released by the following sequence.

- a. In the dual-clock mode, when returning to NORMAL2, both the high-frequency and low-frequency clock oscillators are turned on; when returning to SLOW1 mode, only the low-frequency clock oscillator is turned on. In the single-clock mode, only the high-frequency clock oscillator is turned on.

- b. A STOP warm-up period is inserted to allow oscillation time to stabilize. During STOP warm-up, all internal operations remain halted. Four different STOP warm-up times can be selected with the SYSCR1<WUT> in accordance with the resonator characteristics.

- c. When the EEPCR<MNPWDW> is "1", the CPU wait period is inserted to stabilize the power supply of Flash control circuit. During CPU wait, though CPU operations remain halted, the peripheral function operation is resumed, and the counting of the timing generator is restarted. After the CPU wait is finished, normal operation resumes with the instruction following the STOP mode start instruction.

- d. When the EEPCR<MNPWDW> is "0", normal operation resumes with the instruction following the STOP mode start instruction after the STOP Warm-up.

- Note 1: When the STOP mode is released, the start is made after the prescaler and the divider of the timing generator are cleared to "0".

- Note 2: STOP mode can also be released by inputting low level on the RESET pin, which immediately performs the normal reset operation.

- Note 3: When STOP mode is released with a low hold voltage, the following cautions must be observed.

The power supply voltage must be at the operating voltage level before releasing STOP mode. The RESET pin input must also be "H" level, rising together with the power supply voltage. In this case, if an external time constant circuit has been connected, the RESET pin input voltage will increase at a slower pace than the power supply voltage. At this time, there is a danger that a reset may occur if input voltage level of the RESET pin drops below the non-inverting high-level input voltage (Hysteresis input).

TOSHIBA TMP86FM48

Table 1.4.1 Warm-up Time Example (at fc = 16.0 MHz, fs = 32.768 kHz)

www DataSheet4U com

| WUT  | Warm-up Time [ms] (Note 2) |                     |  |  |  |  |  |

|------|----------------------------|---------------------|--|--|--|--|--|

| VVUI | Return to NORMAL Mode      | Return to SLOW Mode |  |  |  |  |  |

| 00   | 12.288 + (0.064)           | 750 + (0.244)       |  |  |  |  |  |

| 01   | 4.096 + (0.064)            | 250 + (0.244)       |  |  |  |  |  |

| 10   | 3.072 + (0.064)            | 5.85 + (0.244)      |  |  |  |  |  |

| 11   | 1.024 + (0.064)            | 1.95 + (0.244)      |  |  |  |  |  |

Note 1: The warm-up time is obtained by dividing the basic clock by the divider: therefore, the warm-up time may include a certain amount of error if there is any fluctuation of the oscillation frequency when STOP mode is released. Thus, the warm-up time must be considered an approximate value.

Note 2: The CPU wait period for FLASH is shown in parentheses.

Figure 1.4.10 STOP Mode Start/Release (When EEPCR<MNPWDW> = "0")

Figure 1.4.11 STOP Mode Start/Release (When EEPCR<MNPWDW> = "1")

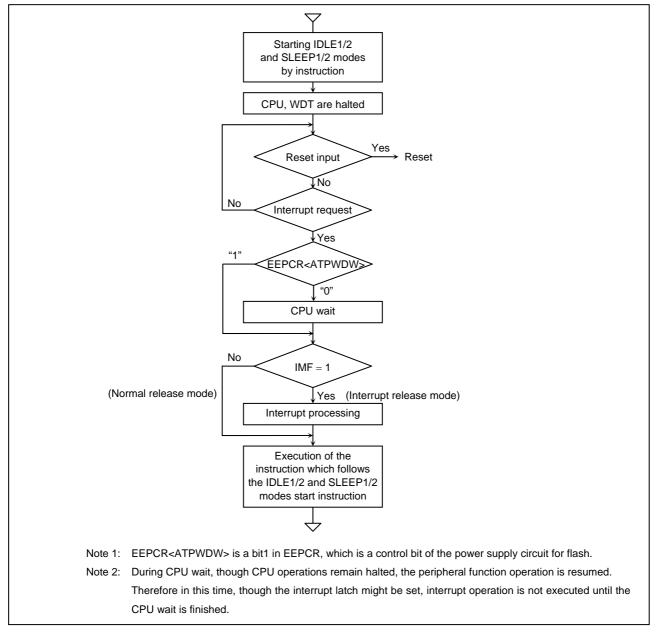

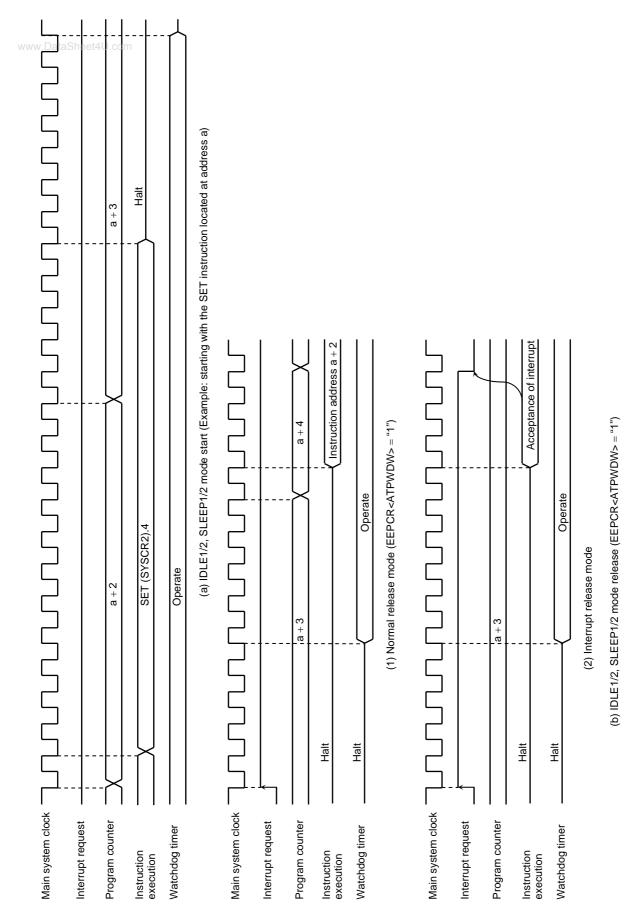

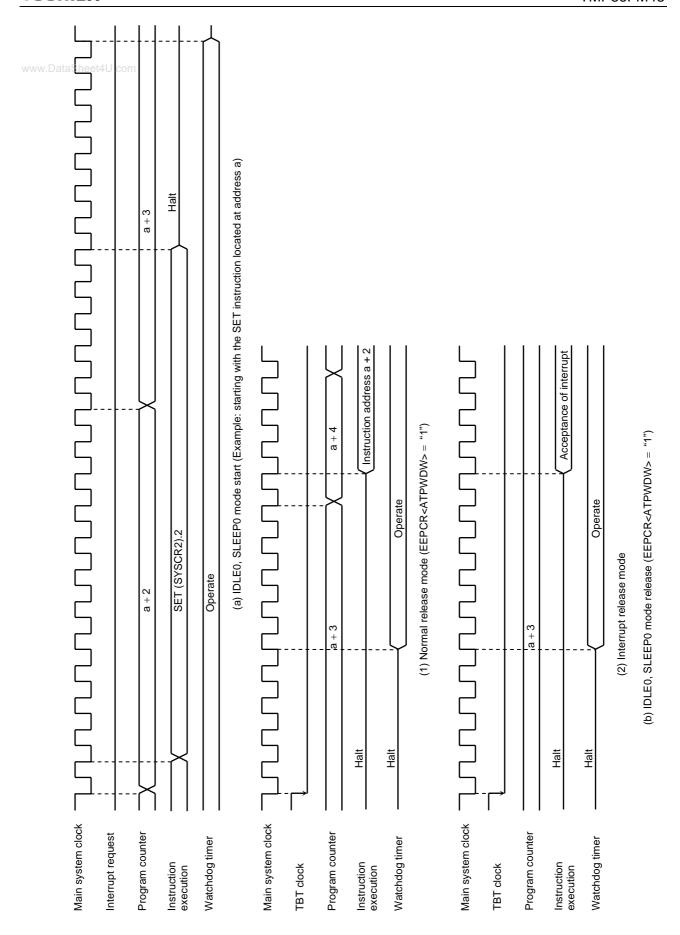

#### (2) IDLE1/2 mode, SLEEP1/2 mode

IDLE1/2 and SLEEP1/2 modes are controlled by the system control register 2 (SYSCR2) and maskable interrupts. The following status is maintained during these modes.

- a. Operation of the CPU and watchdog timer (WDT) is halted. On-chip peripherals continue to operate.

- b. The data memory, CPU registers, program status word and port output latches are all held in the status in effect before these modes were entered.

- c. The program counter holds the address 2 ahead of the instruction which starts these modes.

Figure 1.4.12 IDLE1/2, SLEEP1/2 Modes

• Start the IDLE1/2 and SLEEP1/2 modes

When IDLE1/2 and SLEEP1/2 modes start, set SYSCR2<IDLE> to "1".

www.DataSheet4U.com

#### • Release the IDLE1/2 and SLEEP1/2 modes

IDLE1/2 and SLEEP1/2 modes include a normal release mode and an interrupt release mode. These modes are selected by interrupt master enable flag (IMF).

After releasing IDLE1/2 and SLEEP1/2 modes, the SYSCR2<IDLE> is automatically cleared to "0" and the operation mode is returned to the mode preceding IDLE1/2 and SLEEP1/2 modes.

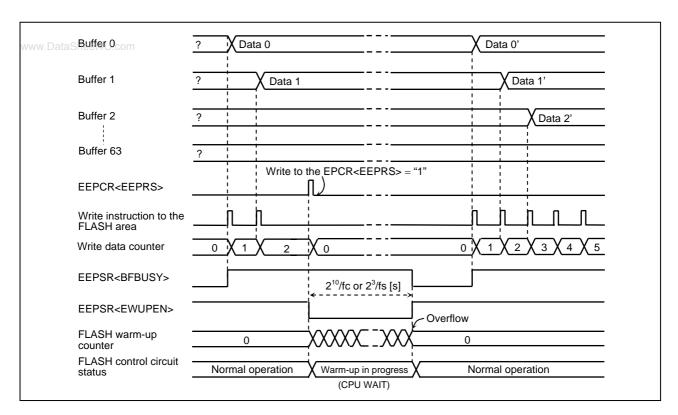

When the IDLE1/2 and SLEEP1/2 modes are started with the EEPCR<ATPWDW> = "0", the CPU wait period for stabilizing of the power supply of Flash control circuit is added before the operation mode is returned to the preceding modes. The CPU wait time of IDLE1/2 is  $2^{10}$ /fc [s] and that of SLEEP1/2 mode is  $2^{3}$ /fs [s].

IDLE1/2 and SLEEP1/2 modes can also be released by inputting low level on the  $\overline{\text{RESET}}$  pin. After releasing reset, the operation mode is started from NORMAL1 mode.

Note: During CPU wait, though CPU operations remain halted, but the peripheral function operation is resumed. Therefore in this time, though the interrupt latch might be set, interrupt operation is not executed until the CPU wait is finished.

#### (a) Normal release mode (IMF = "0")

IDLE1/2 and SLEEP1/2 modes are released by any interrupt source enabled by the individual interrupt enable flag (EF). After the interrupt is generated, the program operation is resumed from the instruction following the IDLE1/2 and SLEEP1/2 modes start instruction. Normally, the interrupt latches (IL) of the interrupt source used for releasing must be cleared to "0" by load instructions.

#### (b) Interrupt release mode (IMF = "1")

IDLE1/2 and SLEEP1/2 modes are released by any interrupt source enabled with the individual interrupt enable flag (EF). After the interrupt is processed, the program operation is resumed from the instruction following the instruction, which starts IDLE1/2 and SLEEP1/2 modes.

Note: When a watchdog timer interrupts is generated immediately before IDLE1/2 and SLEEP1/2 mode are started, the watchdog timer interrupt will be processed but IDLE1/2 and SLEEP1/2 mode will not be started.

Figure 1.4.13 IDLE1/2, SLEEP1/2 Mode Start/Release

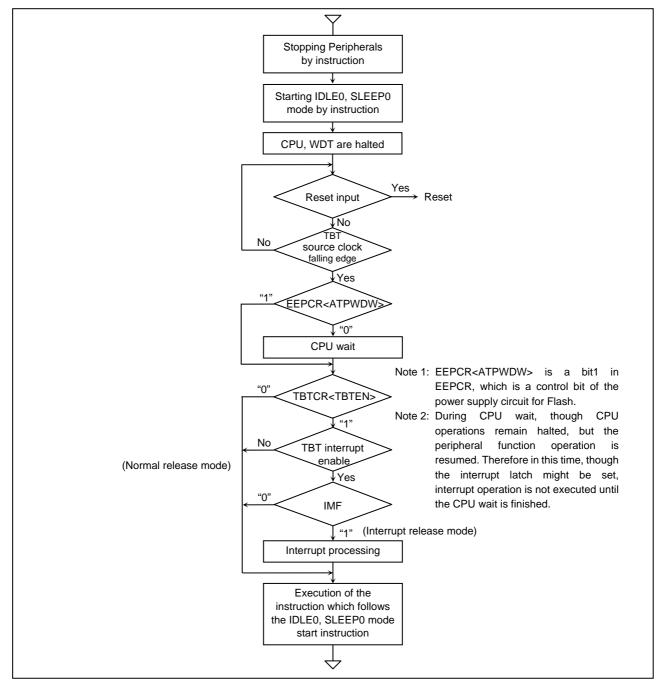

#### (3) IDLE0, SLEEP0 mode (IDLE0, SLEEP0)

IDLE0 and SLEEP0 modes are controlled by the system control register 2 (SYSCR2) and the time base timer control register (TBTCR). The following status is maintained during IDLE0 and SLEEP0 modes.

- a. Timing generator stops feeding clock to peripherals except TBT.

- b. The data memory, CPU registers, program status word and port output latches are all held in the status in effect before IDLE0 and SLEEP0 modes were entered.

- c. The program counter holds the address 2 ahead of the instruction which starts IDLE0 and SLEEP0 modes.

Note: Before starting IDLE0 or SLEEP0 mode, be sure to stop (Disable) periperals.

Figure 1.4.14 IDLE0, SLEEP0 Mode

• Start the IDLE0 and SLEEP0 modes

www DataSheet4U com

Stop (Disable) peripherals such as a timer counter.

When IDLE0 and SLEEP0 modes start, set SYSCR2<TGHALT> to "1".

#### • Release the IDLE0 and SLEEP modes

IDLE0 and SLEEP0 modes include a normal release mode and an interrupt release mode.

These modes are selected by interrupt master flag (IMF), individual interrupt enable-flag (EF7) for INTTBT and TBTCR<TBTEN>.

After releasing IDLE0 and SLEEP0 modes, the SYSCR2<TGHALT> is automatically cleared to "0" and the operation mode is returned to the mode preceding IDLE0 and SLEEP0 modes. Before starting the IDLE0 or SLEEP0 mode, when the TBTCR<TBTEN> is set to "1", INTTBT interrupt latch is set to "1".

When the IDLE0 and SLEEP0 modes are started with the EEPCR<ATPWDW> = "0", the CPU wait period for stabilizing of the power supply of Flash control circuit is added before the operation mode is returned to the preceding modes. The CPU wait time of IDLE0 is 210/fc [s] and that of SLEEP0 mode is 23/fs [s].

IDLE0 and SLEEP0 modes can also be released by inputting low level on the  $\overline{\text{RESET}}$  pin. After releasing reset, the operation mode is started from NORMAL1 mode.

- Note 1: IDLE0 and SLEEP0 modes start/release without reference to TBTCR<TBTEN> setting.

- Note 2: During CPU wait, though CPU operations remain halted, but the peripheral function operation is resumed. Therefore in this time, though the interrupt latch might be set, interrupt operation is not executed until the CPU wait is finished.

#### a. Normal release mode (IMF•EF7•TBTCR<TBTEN> = "0")

IDLE0 and SLEEP0 modes are released by the source clock falling edge, which is setting by the TBTCR<TBTCK>. After the falling edge is detected, the program operation is resumed from the instruction following the IDLE0 and SLEEP0 modes start instruction.

#### b. Interrupt release mode (IMF • EF7 • TBTCR < TBTEN > = "1")

IDLE0 and SLEEP0 modes are released by the source clock falling edge, which is setting by the TBTCR<TBTCK> and INTTBT interrupt processing is started.

- Note 1: Because returning from IDLE0, SLEEP0 to NORMAL1, SLOW1 is executed by the asynchronous internal clock, the period of IDLE0, SLEEP0 mode might be the shorter than the period setting by TBTCR<TBTCK>.

- Note 2: When a watchdog timer interrupt is generated immediately before IDLE0/SLEEP0 mode is started, the watchdog timer interrupt will be processed but IDLE0/SLEEP0 mode will not be started.

Figure 1.4.15 IDLE0, SLEEP0 Mode Start/Release

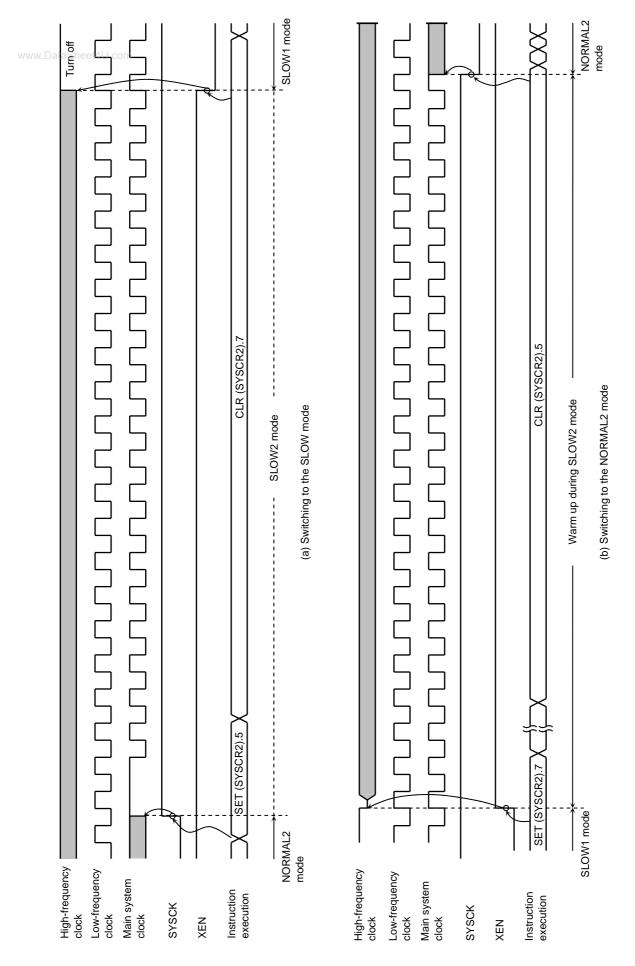

#### (4) SLOW mode

www.DataSheet4U.com

SLOW mode is controlled by the system control register 2 (SYSCR2).

The following is the methods to switch the mode with the warm-up counter (TC2).

#### a. Switching from NORMAL2 mode to SLOW1 mode

First, set SYSCR2<SYSCK> to switch the main system clock to the low-frequency clock for SLOW2 mode.

Next, clear SYSCR2<XEN> to turn off high-frequency oscillation.

Note: The high-frequency clock oscillation can be continued to return quickly to NORMAL2 mode. But starting STOP mode while SLOW mode, the high-frequency oscillation must be stopped.

When the low-frequency clock oscillation is unstable, wait until oscillation stabilizes before performing the above operations. The timer/counter 2 (TC2) can conveniently be used to confirm that low-frequency clock oscillation has stabilized.

Example 1: Switching from NORMAL2 mode to SLOW1 mode.

|               | SET           | (SYSCR2). 5                 | ;    | SYSCR2 <sysck> ← 1</sysck>                 |

|---------------|---------------|-----------------------------|------|--------------------------------------------|

|               |               |                             |      | (Switches the main system clock to the     |

|               |               |                             |      | low-frequency clock for SLOW2)             |

|               | CLR           | (SYSCR2). 7                 |      | $SYSCR2 < XEN > \leftarrow 0$              |

|               |               |                             |      | (Turns off high-frequency oscillation)     |

| Example2: Swi | tching to the | SLOW1 mode after low-freque | ency | clock has stabilized.                      |

| ·             | SET           | (SYSCR2). 6                 | ;    | SYSCR2 <xten> ← 1</xten>                   |

|               | LD            | (TC2CR), 14H                | ;    | Sets mode for TC2                          |

|               | LDW           | (TC2DRL), 8000H             | ;    | Sets warm-up time                          |

|               |               |                             |      | (Depend on oscillator accompanied)         |

|               | DI            |                             | ;    | $IMF \leftarrow 0$                         |

|               | SET           | (EIRE). 4                   | ;    | Enables INTTC2                             |

|               | El            |                             | ;    | IMF ← 1                                    |

|               | SET           | (TC2CR). 5                  | ;    | Starts TC2                                 |

| PINTTC2:      | CLR           | (TC2CR). 5                  | ;    | Stops TC2                                  |

|               | SET           | (SYSCR2). 5                 | ;    | SYSCR2 <sysck> ← 1</sysck>                 |

|               |               |                             |      | (Switches the main system clock to the     |

|               |               |                             |      | low-frequency clock)                       |

|               | CLR           | (SYSCR2). 7                 | ;    | ${\sf SYSCR2}{<}{\sf XEN}{>} \leftarrow 0$ |

|               |               |                             |      | (Turns off high-frequency oscillation)     |

|               | RETI          |                             |      |                                            |

|               |               |                             |      |                                            |

| VINTTC2:      | DW            | PINTTC2                     | ;    | INTTC2 vector table                        |

TOSHIBA

#### b. Switching from SLOW1 mode to NORMAL2 mode

Example: Switching from the SLOW1 mode to the NORMAL2 mode

PINTTC2

VINTTC2:

DW

www.DataSheet4U.com

First, set SYSCR2<XEN> to turn on the high-frequency oscillation. When time for stabilization (Warm-up) has been taken by the timer/counter 2 (TC2), clear SYSCR2<SYSCK> to switch the main system clock to the high-frequency clock.

Note 1: After SYSCK is cleared to "0", executing the instructions is continued by the low-frequency clock for the period synchronized with low-frequency and high-frequency clocks.

Note 2: SLOW mode can also be released by inputting low level on the RESET pin, which immediately performs the reset operation. After reset, the TMP86FM48 is placed in NORMAL1 mode.

(fc = 16 MHz, warm-up time is = 4.0 ms). (SYSCR2). 7 SET SYSCR2<XEN> ← 1 (Starts high-frequency oscillation) LD (TC2CR), 10H Sets mode for TC2 (Timer mode, fc for source) LD (TC2DRH), 0F8H Sets warm-up time (Depend on oscillator accompanied) DI  $IMF \leftarrow 0$ SET (EIRE). 4 Enables INTTC2 IMF ← 1 ΕI SET (TC2CR). 5 Starts TC2 PINTTC2: CLR (TC2CR). 5 Stops TC2 CLR (SYSCR2). 5 SYSCR2<SYSCK>  $\leftarrow 0$ (Switches the main system clock to the high-frequency clock) RETI

INTTC2 vector table

Figure 1.4.16 Switching between the NORMAL2 and SLOW Modes

Internal

Internal

External

INTTXD

INTTC2

Reserved

Reserved

INT5

(UART transmitted interrupt)

(TC2 interrupt)

(External interrupt 5)

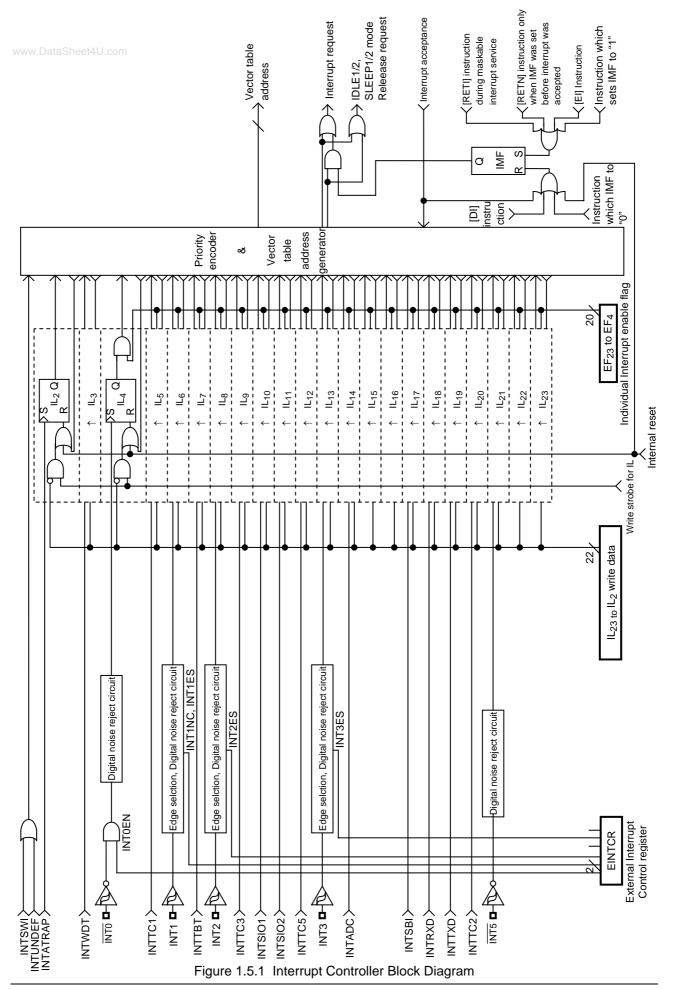

#### 1.5 Interrupt Control Circuit

www.DataSheeTheeTMP86FM48 has a total (Reset is excluded) of 20 interrupt source: 5 externals and 15 internals. 4 of the internal sources are non-maskable interrupts, and the rest of them are maskable interrupts.

Interrupt sources are provided with interrupt latches (IL), which hold interrupt requests, and independent vectors. The interrupt latch is set to "1" by the generation of its interrupt request which requests the CPU to accept its interrupts. Interrupts are enabled or disabled by software using the interrupt master enable flag (IMF) and interrupt enable flag (EF). If more than one interrupts are generated simultaneously, interrupts are accepted in order which is dominated by hardware. However, there are no prioritized interrupt factors among non-maskable interrupts.

Enable

$IMF \bullet EF_{19} = 1$

$IMF \cdot EF_{20} = 1$

$IMF \bullet EF_{21} = 1$

$IMF \cdot EF_{22} = 1$

$IMF^{\bullet}EF_{23}=1$

Interrupt

Vector

FFB8<sub>H</sub>

FFB6<sub>H</sub>

FFB4<sub>H</sub>

FFB2<sub>H</sub>

FFB0<sub>H</sub>

IL<sub>19</sub>

**IL**<sub>20</sub>

$IL_{21}$

$IL_{22}$

IL<sub>23</sub>

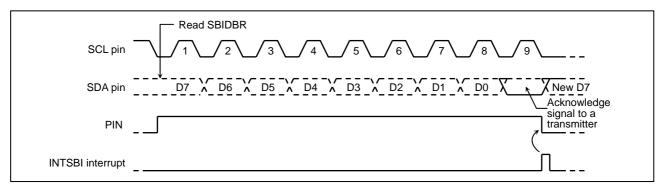

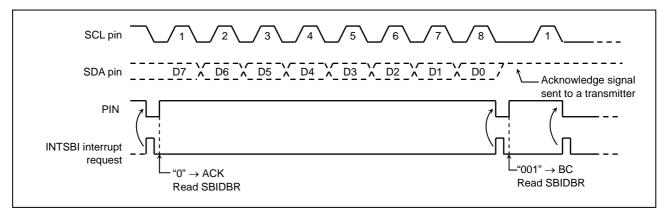

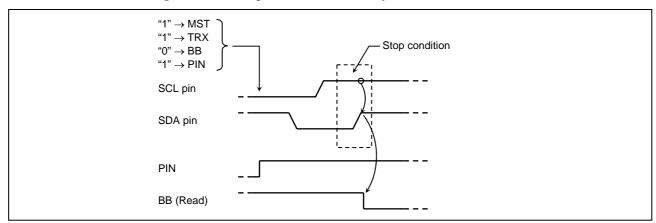

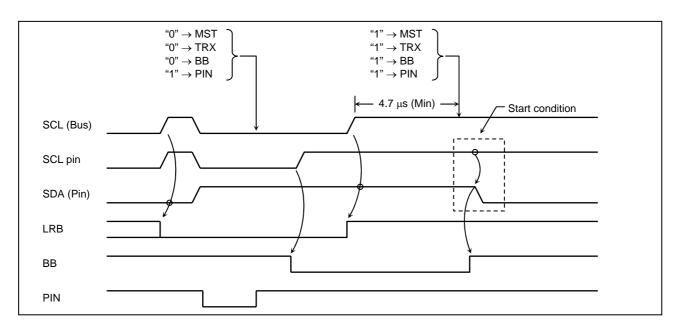

Interrupt Factors Priority Condition Address Latch Internal/External (Reset) Non-maskable FFFE<sub>H</sub> High Internal INTSWI (Software interrupt) Non-maskable **FFFCH**  $\mathsf{FFFC}_\mathsf{H}$ 2 Internal INTUNDEF (Executed the undefined instruction interrupt) Non-maskable  $FFFA_H$ 2 Internal INTATRAP (Address trap interrupt) Non-maskable IL<sub>2</sub> Internal **INTWDT** (Watchdog timer interrupt) Non-maskable  $IL_3$ FFF8<sub>H</sub> ĪNT0 (External interrupt 0) External  $IMF \bullet EF_4 = 1$ IL<sub>4</sub> FFF6<sub>H</sub>  $IMF \cdot EF_5 = 1$  $IL_5$ 6 Internal INTTC1 (TC1 interrupt) FFF4<sub>H</sub> 7 INT1  $IMF \bullet EF_6 = 1$ FFF2<sub>H</sub> External (External interrupt 1) IL<sub>6</sub> 8 Internal **INTTBT** (Time base timer interrupt)  $IMF \bullet EF_7 = 1$ IL<sub>7</sub> FFF0<sub>H</sub> External INT2 (External interrupt 2) IMF•EF<sub>8</sub> = 1 IL<sub>8</sub> **FFEEH** 9  $IMF \bullet EF_9 = 1$ 10 Internal INTTC3 (TC3 interrupt) IL<sub>9</sub> FFECH Internal INTSIO1 (Serial interface 1 interrupt)  $IMF \bullet EF_{10} = 1$ IL<sub>10</sub>  $\mathsf{FFEA}_\mathsf{H}$ 11 IL<sub>11</sub> 12 Internal INTSIO2 (Serial interface 2 interrupt)  $IMF \cdot EF_{11} = 1$ FFE8<sub>H</sub>  $IMF \cdot EF_{12} = 1$ 13 Internal INTTC5 (TC5 interrupt) IL<sub>12</sub> FFE6<sub>H</sub>  $IMF \cdot EF_{13} = 1$ External INT3 (External interrupt 3) IL<sub>13</sub> FFE4<sub>H</sub> 14 15 **INTADC**  $IMF^{\bullet}EF_{14}=1$ Internal (AD converter interrupt) IL<sub>14</sub> FFE2<sub>H</sub> IMF•EF<sub>15</sub> = 1 Reserved IL<sub>15</sub> FFE0<sub>H</sub> 16 17 Reserved  $IMF \cdot EF_{16} = 1$ IL<sub>16</sub> **FFBEH INTSBI**  $IMF \cdot EF_{17} = 1$ FFBCH 18 Internal (Serial bus interface interrupt) IL<sub>17</sub>  $IMF - EF_{18} = 1$ **INTRXD** (UART received interrupt) IL<sub>18</sub> **FFBAH** 19 Internal

Table 1.5.1 Interrupt Sources

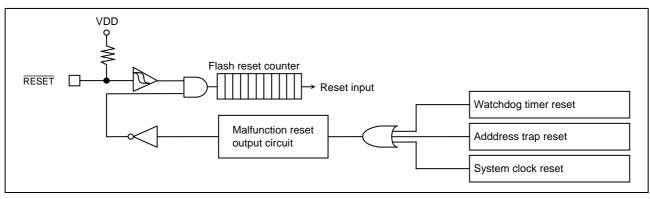

Note 1: To use the watchdog timer interrupt (INTWDT), clear WDTCR1<WDTOUT> to "0" (It is set for the "Reset request" after reset is released). For details, see 2.4 Watchdog Timer.

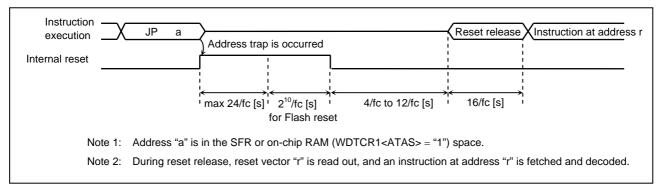

Note 2: To use the address trap interrupt (INTATRAP), clear WDTCR1<ATOUT> to "0" (It is set for the "Reset request" after reset is released). For details, see 2.4.5 Address Trap.

20

21

22

23

24

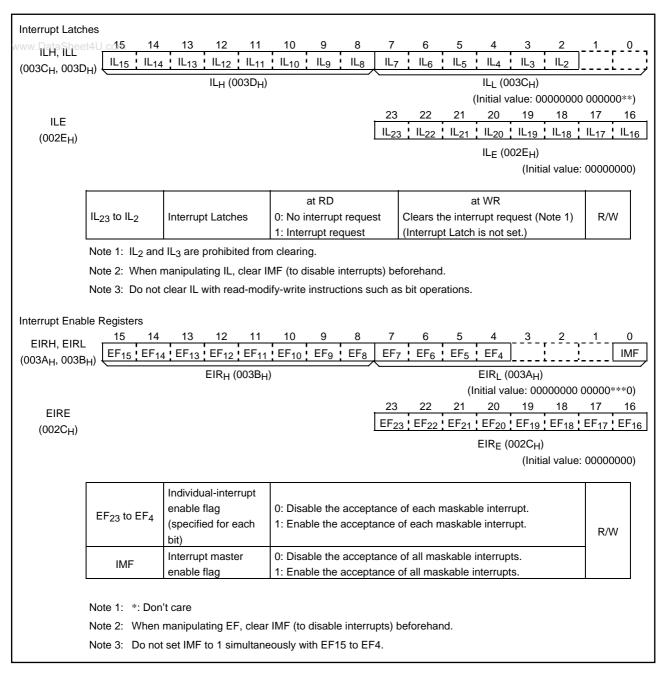

#### (1) Interrupt latches (IL<sub>24</sub> to IL<sub>2</sub>)

An interrupt latch is provided for each interrupt source, except for a software interrupt. When interrupt request is generated, the latch is set to "1", and the CPU is requested to accept the interrupt if its interrupt is enabled. All interrupt latches are initialized to "0" during reset.

The interrupt latches are located on address 002EH, 003CH and 003DH in SFR area. Except for IL<sub>3</sub> and IL<sub>2</sub>, each latch can be cleared to "0" individually by instruction. (However, the read-modify-write instructions such as bit manipulation or operation instructions cannot be used. Interrupt request would be cleared inadequately if interrupt is requested while such instructions are executed.) Thus interrupt request can be canceled/initialized by software.

Interrupt latches are not set to "1" by an instruction. Since interrupt latches can be read, the status for interrupt requests can be monitored by software.

Note: When manipulating IL, clear IMF (to disable interrupts) beforehand.

```

Example 1: Clears interrupt latches

```

Example 2: Reads interrupt latches

LD WA, (ILL) ;  $W \leftarrow ILH$ ,  $A \leftarrow ILL$

Example 3: Tests an interrupt latches

TEST (IL).7 ;  $IL_7 = 1$  then jump

JR F, SSET

#### (2) Interrupt enable register (EIR)

The interrupt enable register (EIR) enables and disables the acceptance of interrupts, except for the non-maskable interrupts (Software interrupt, undefined instruction interrupt, address trap interrupt and watchdog interrupt). Non-maskable interrupt is accepted regardless of the contents of the EIR.

The EIR consists of an interrupt master enable flag (IMF) and the individual interrupt enable flags (EF). These registers are located on address 002CH, 003AH and 003BH in SFR area, and they can be read and written by an instructions (Including read-modify-write instructions such as bit manipulation or operation instructions).

#### a. Interrupt master enable flag (IMF)

The interrupt enable register (IMF) enables and disables the acceptance of the whole maskable-interrupt. While IMF = "0", all maskable interrupts are not accepted regardless of the status on each individual interrupt enable flag (EF). By setting IMF to "1", the interrupt becomes acceptable if the individuals are enabled. When an interrupt is accepted, IMF is cleared to "0" after the latest status on IMF is stacked. Thus the maskable interrupts which follow are disabled. By executing return interrupt instruction [RETI/RETN], the stacked data, which was the status before interrupt acceptance, is loaded on IMF again.

The IMF is located on bit0 in EIRL (Address: 003A<sub>H</sub> in SFR), and can be read and written by an instruction. The IMF is normally set and cleared by [EI] and [DI] instruction respectively. During reset, the IMF is initialized to "0", and maskable interrupts are not accepted until it is set to "1".

b. Individual interrupt enable flags (EF<sub>23</sub> to EF<sub>4</sub>)

Each of these flags enables and disables the acceptance of its maskable interrupt. Setting the corresponding bit of an individual interrupt enable flag to "1" enables acceptance of its interrupt, and setting the bit to "0" disables acceptance. The individual interrupt enable flags (EF<sub>23</sub> to EF<sub>4</sub>) are located on EIRE, EIRL to EIRH (address: 002CH, 003AH to 003BH in SFR), and can be read and written by an instruction. During reset, all the individual interrupt enable flags (EF<sub>23</sub> to EF<sub>4</sub>) are initialized to "0" and all maskable interrupts are not accepted until they are set to "1".

Note: Before manipulating EF, be sure to clear IMF (Interrupt disabled). Then set IMF newly again after operating on the interrupt enables flag (EF). Normally, IMF is clear to "0" automatically on service routine. When IMF is set to "1" for using a multiple interrupt on service routine, be sure to process as is the case with EF.

```

Example 1: Enables interrupts individually and sets IMF

DΙ

IMF \leftarrow 0

LD

(EIRE), 00001100B

EF<sub>19</sub>, EF<sub>18</sub> ← "1"

LDW

(EIRL),

EF_{14}, EF_{13}, EF_{11}, EF_{7}, EF_{5} \leftarrow "1"

0110100010100000B

Note: IMF is not set.

IMF ← "1"

ΕĬ

Example 2: C compiler description example

/* 3AH shows EIRL address */

unsigned int _io (3AH) EIRL;

_DI ( );

EIRL = 10100000B;

_ĖI ( );

```

Figure 1.5.2 Interrupt Latch (IL), Interrupt Enable Registers (EIR)

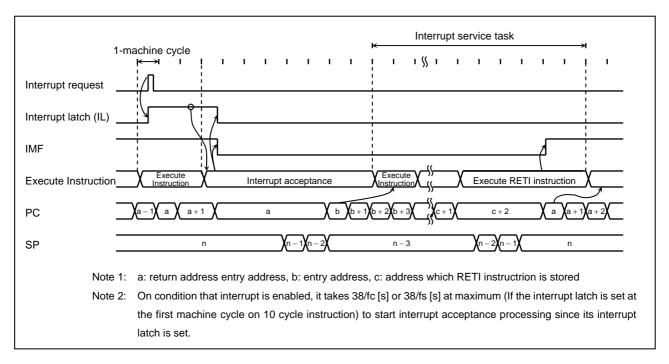

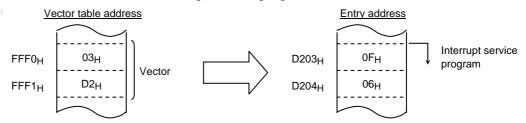

### 1.5.1 Interrupt Sequence

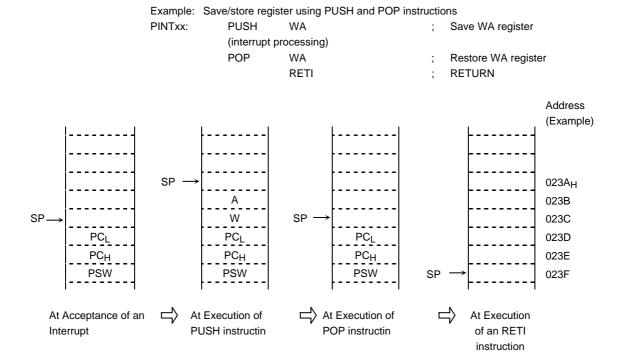

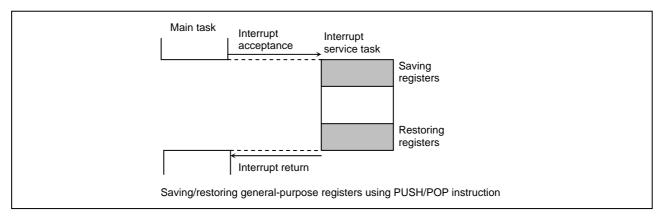

www.DataSheet4U.cAn interrupt request, which raised interrupt latch, is held, until interrupt is accepted or interrupt latch is cleared to "0" by resetting or an instruction. Interrupt acceptance sequence requires 8-machine cycles (4 µs at 8.0 MHz) after the completion of the current instruction. The interrupt service task terminates upon execution of an interrupt return instruction [RETI] (for maskable interrupts) or [RETN] (for non-maskable interrupts). Figure 1.5.3 shows the timing chart of interrupt acceptance processing.

- (1) Interrupt acceptance processing is packaged as follows.

- 1. The interrupt master enable flag (IMF) is cleared to "0" in order to disable the acceptance of any following interrupt.

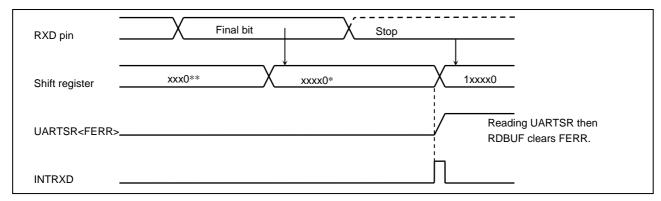

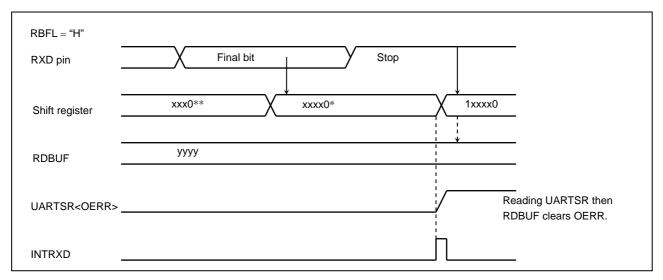

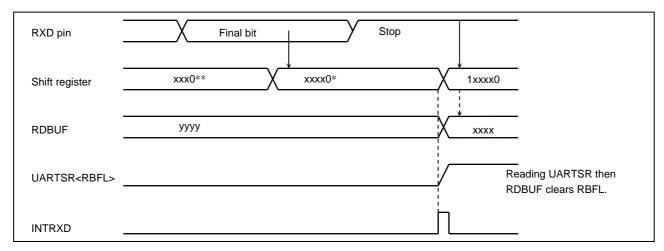

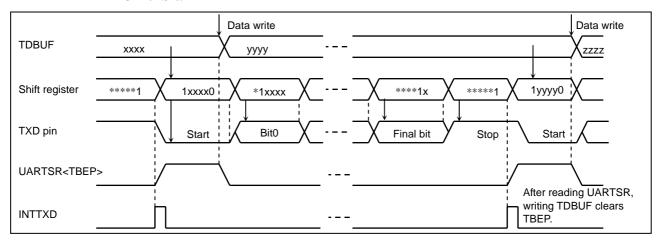

- 2. The interrupt latch (IL) for the interrupt source accepted is cleared to "0".