# MOS INTEGRATED CIRCUIT $\mu$ PD61051, 61052

# MPEG2 AUDIO/VIDEO ENCODER

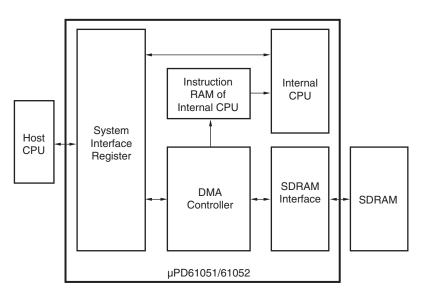

The  $\mu$ PD61051 and  $\mu$ PD61052 are LSIs of MPEG audio and video encoding, decoding and transcoding.

The  $\mu$ PD61051 has MPEG2 video encoder, MPEG audio encoding DSP, 32-bit RISC CPU, video input/output unit which contains a processing filter and a time base corrector (TBC), and MPEG system layer which contains the multiplexer and de-multiplexer. It combines with 64 M or 128 Mbit SDRAM and it uses. The  $\mu$ PD61052 has a Dolby<sup>TM</sup> Digital Consumer Encoder in addition to the  $\mu$ PD61051.

The  $\mu$ PD61051, 61052 are the optimal choice for consumer digital video recording replay equipment to process a MPEG.

#### **FEATURES**

Video encode

- Stream standard: MPEG2 video MP@ML, SP@ML standard, MPEG1 standard

Picture size: Horizontal: 720, 704, 544, 480, 352 dots/line

Vertical: 480, 240, 576, 288 line/frame

- Single pass variable bit rate (VBR), constant bit rate (CBR) encoding

- Transcoding: Bit rate conversion, VBR ⇔ CBR

- Video input/output

Format: 8-bit Y/Cb/Cr 4:2:2 (ITU-R BT.656)

Pre analysis: Film detect, scene changing detect, and motion estimation assist

TBC, VBI data slicer

Audio encoding

Bit length: 16 bits, 20 bits, 24 bitsSampling rate: 32 kHz, 44.1 kHz, 48 kHz

- MPEG1 audio layer 2 standard based

- Dolby Digital Consumer Encoder standard based (Only the  $\mu$ PD61052)

- Elementary stream and PCM audio input/output

- MPEG system processing

- Multiplex: MPEG2-PS, MPEG2-TS, DVD-Video, and DVD-VR

- De-multiplex: MPEG2-PS, MPEG2-TS

- Transcoding: MPEG2 format conversion (MPEG2-TS ⇔ MPEG2-PS)

- Partial TS generation

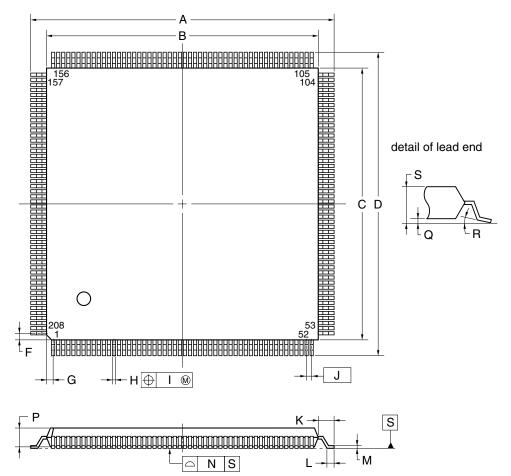

Package: 208-pin fine pitch QFP

Power supply: 1200 mW (Typ.)

Power supply voltage: 3.3±0.165 V, 2.5±0.2 V (Internal circuit power)

"Dolby" is a trademark of Dolby Laboratories.

To use the µPD61052, a license from Dolby Laboratories Licensing Corporation is necessary.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

# **APPLICATION**

D-VHS, DVD video recorder, HDD video recorder

# **ORDERING INFORMATION**

|   | Part Number                             | Package                                  |

|---|-----------------------------------------|------------------------------------------|

|   | $\mu$ PD61051GD-LML                     | 208-pin plastic QFP (Fine pitch) (28×28) |

| * | $\mu$ PD61051GD-LML-A $^{	extsf{Note}}$ | 208-pin plastic QFP (Fine pitch) (28×28) |

|   | $\mu$ PD61052GD-LML                     | 208-pin plastic QFP (Fine pitch) (28×28) |

| * | $\mu$ PD61052GD-LML-A $^{	exttt{Note}}$ | 208-pin plastic QFP (Fine pitch) (28×28) |

Note Lead-free product

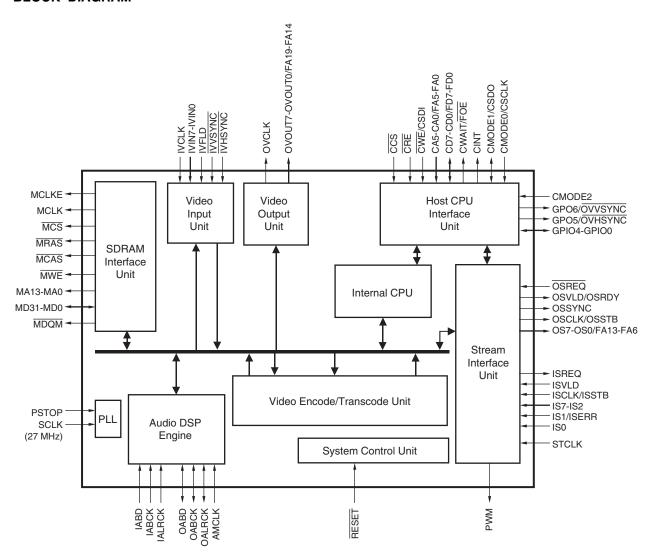

#### **BLOCK DIAGRAM**

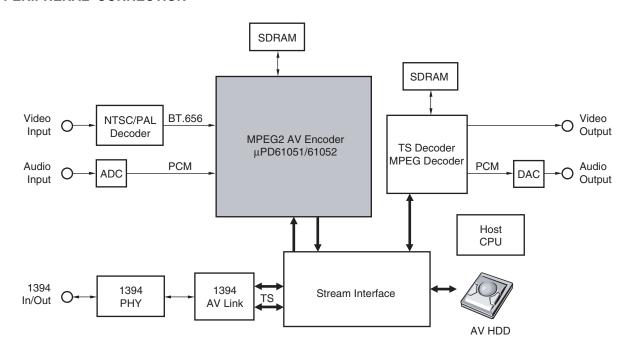

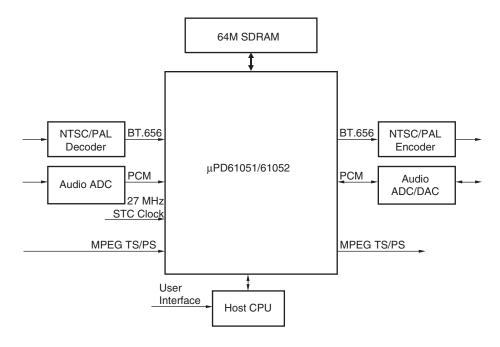

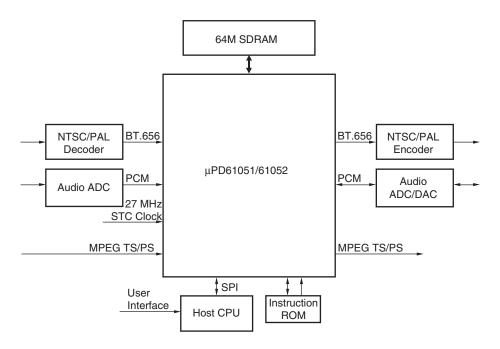

# PERIPHERAL CONNECTION

This LSI deals with two kinds of methods to connect a system controller.

# **Parallel Bus Interface**

# **Serial Bus Interface**

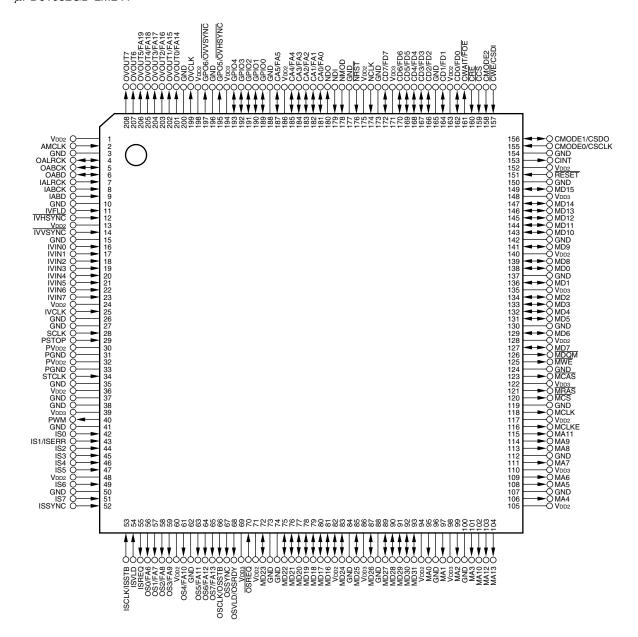

# PIN CONFIGURATION (TOP VIEW)

• 208-pin plastic QFP (Fine pitch) (28×28)

```

μPD61051GD-LML

μPD61051GD-LML-A

μPD61052GD-LML

μPD61052GD-LML-A

```

# PIN LIST

| AMCLK              | :Audio Main Clock                      | MA0 to MA13         | :Memory Address               |

|--------------------|----------------------------------------|---------------------|-------------------------------|

| CA0/FA0 to CA5/FA5 | :Host CPU Address/                     | MCAS                | :Memory Column Address Strobe |

|                    | Instruction ROM Address                | MCLK                | :Memory Clock                 |

| CCS                | :Host CPU Chip Select                  | MCLKE               | :Memory Clock Enable          |

| CD0/FD0 to CD7/FD7 | :Host CPU Data/                        | MCS                 | :Memory Chip Select           |

|                    | Instruction ROM Data                   | MD0 to MD31         | :Memory Data                  |

| CINT               | :Host CPU Interrupt                    | MDQM                | :Memory DQ Mask Enable        |

| CMODE0/CSCLK       | :Host CPU Mode/                        | MRAS                | :Memory Row Address Strobe    |

|                    | SPI Clock                              | MWE                 | :Memory Write Enable          |

| CMODE1/CSDO        | :Host CPU Mode/                        | NCLK                | :N-wire Clock                 |

|                    | SPI Data Output                        | NDI                 | :N-wire Data Input            |

| CMODE2             | :Host CPU Mode                         | NDO                 | :N-wire Data Output           |

| CRE                | :Host CPU Read Enable                  | NMOD                | :N-wire Mode                  |

| CWAIT/FOE          | :Host CPU Wait/                        | NRST                | :N-wire Reset                 |

|                    | Instruction ROM Output Enable          | OABCK               | :Output Audio Bit Clock       |

| CWE/CSDI           | :Host CPU Write Enable/                | OABD                | :Output Audio Bit Data        |

|                    | SPI Data Input                         | OALRCK              | :Output Audio LR Clock        |

| GND                | :Ground                                | OS0/FA6 to OS7/FA13 | :Output Stream Data/          |

| GPIO0 to GPIO4     | :General Purpose IO                    |                     | Instruction ROM Address       |

| GPO5/OVHSYNC       | :General Purpose Output/               | OSCLK/OSSTB         | :Output Stream Data Clock/    |

|                    | Output Video Horizontal Sync           |                     | Output Stream Data Strobe     |

| GPO6/OVVSYNC       | :General Purpose Output/               | OSREQ               | :Output Stream Data Request   |

|                    | Output Video Vertical Sync             | OSSYNC              | :Output Stream Data Sync      |

| IABCK              | :Input Audio Bit Clock                 | OSVLD/OSRDY         | :Output Stream Data Valid/    |

| IABD               | :Input Audio Bit Data                  |                     | Output Stream Data Ready      |

| IALRCK             | :Input Audio LR Clock                  | OVCLK               | :Output Video Clock           |

| IS0, IS2 to IS7    | :Input Stream Data                     | OVOUT0/FA14 to      | :Output Video Data/           |

| IS1/ISERR          | :Input Stream Data/ Input Stream Error | OVOUT5/FA19         | Instruction ROM Address       |

| ISCLK/ISSTB        | :Input Stream Data Clock/              | OVOUT6,OVOUT7       | :Output Video Data            |

|                    | Input Stream Data Strobe               | PGND                | :PLL Ground                   |

| ISREQ              | :Input Stream Data Request             | PSTOP               | :PLL Stop                     |

| ISSYNC             | :Input Stream Data Sync                | PV <sub>DD2</sub>   | :PLL 2.5 V Power Supply       |

| ISVLD              | :Input Stream Data Valid               | PWM                 | :PWM Output                   |

| IVCLK              | :Input Video Clock                     | RESET               | :Reset                        |

| IVFLD              | :Input Video Field Index               | SCLK                | :System Clock                 |

| IVHSYNC            | :Input Video Horizontal Sync           | STCLK               | :System Time Clock            |

| IVIN0 to IVIN7     | :Input Video Data                      | $V_{DD2}$           | :2.5 V Power Supply           |

| IVVSYNC            | :Input Video Vertical Sync             | V <sub>DD3</sub>    | :3.3 V Power Supply           |

|                    |                                        |                     |                               |

# **CONTENTS**

| 1. | PIN  | FUNC   | CTION                              | 9  |

|----|------|--------|------------------------------------|----|

|    | 1.1  | Video  | Input Interface                    | ç  |

|    | 1.2  | Video  | Output Interface                   | 9  |

|    | 1.3  | Audio  | Input Interface                    | ç  |

|    | 1.4  | Audio  | o Input/output Interface           | 10 |

|    | 1.5  | Stream | m Input Interface                  | 10 |

|    | 1.6  | Stream | m Output Interface                 | 11 |

|    | 1.7  | SDRA   | M Interface                        | 11 |

|    | 1.8  | Host   | CPU Interface                      | 12 |

|    |      | 1.8.1  | Parallel bus interface             | 12 |

|    |      | 1.8.2  | Serial bus interface               | 12 |

|    | 1.9  | Clock  | r, Reset                           | 13 |

|    | 1.10 | N-Wir  | e                                  | 13 |

|    | 1.11 | GPIO   |                                    | 14 |

|    | 1.12 | Powe   | r Supply                           | 14 |

|    | 1.13 | Reco   | mmended Connections of Unused Pins | 15 |

|    |      |        |                                    |    |

| 2. | FEA  | TURE   | OVERVIEW                           | 16 |

|    | 2.1  | Video  | )                                  | 16 |

|    |      | 2.1.1  | Encoding                           | 16 |

|    |      | 2.1.2  | Transcoding                        | 16 |

|    |      | 2.1.3  | Input/output processing            | 17 |

|    | 2.2  | Audio  | )                                  | 19 |

|    |      | 2.2.1  | Encoding                           | 19 |

|    |      | 2.2.2  | Transcoding (DEMUX, MUX)           | 19 |

|    |      | 2.2.3  | Input/output processing            | 19 |

|    | 2.3  | MPEG   | System Processing                  | 22 |

|    |      | 2.3.1  | System time clock                  | 22 |

|    |      | 2.3.2  | Multiplex                          | 23 |

|    |      | 2.3.3  | De-multiplex                       | 23 |

|    |      | 2.3.4  | Transcode                          | 24 |

|    | 2.4  | Stream | m Interface                        | 25 |

|    |      | 2.4.1  | Parallel steam data interface      | 25 |

|    |      | 2.4.2  | Serial stream data interface       | 29 |

|    | 2.5  | Host   | CPU Interface                      | 32 |

|    | 2.6  | SDRA   | M Interface                        | 33 |

|    | 2.7  | Memo   | pry Connection Diagram             | 34 |

|    | 2.8  | Memo   | ory Map                            | 36 |

|    |      |        |                                    |    |

| 3. | SYS  | TEM    | INTERFACE REGISTER                 | 38 |

|    | 3.1  | Regis  | ster Mapping (General Mapping)     | 39 |

|    | 3.2  | Regis  | ter Functions                      | 40 |

|    |      | 3.2.1  | Common register                    | 40 |

|    |      | 3.2.2  | Data transfer register             | 40 |

|    |      | 3.2.3  | Internal CPU interrupt register    | 47 |

|    |      | 3.2.4  | Interrupt mask register            | 47 |

|    |     | 3.2.5  | Download interrupt register                         | 47  |

|----|-----|--------|-----------------------------------------------------|-----|

|    |     | 3.2.6  | Interrupt register                                  | 48  |

|    |     | 3.2.7  | Reset register                                      | 48  |

|    |     | 3.2.8  | ROM access cycle register                           | 49  |

|    |     | 3.2.9  | Port setup register                                 | 49  |

| 4. | SYS | TEM I  | NTERFACE PROCEDURE                                  | 50  |

|    | 4.1 | Outlin | ıe                                                  | 51  |

|    | 4.2 | Firmw  | /are Download                                       | 52  |

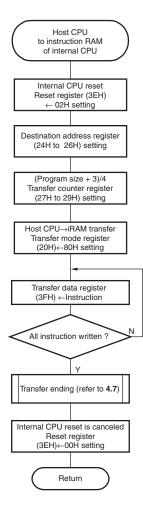

|    |     | 4.2.1  | Host CPU to instruction RAM of internal CPU         | 52  |

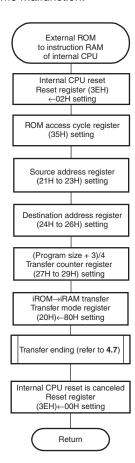

|    |     | 4.2.2  | External ROM to instruction RAM of internal CPU     | 53  |

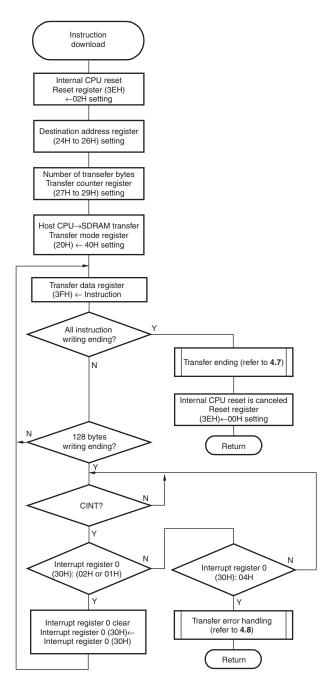

|    |     | 4.2.3  | Host CPU to SDRAM                                   | 54  |

|    |     | 4.2.4  | External ROM to SDRAM                               | 55  |

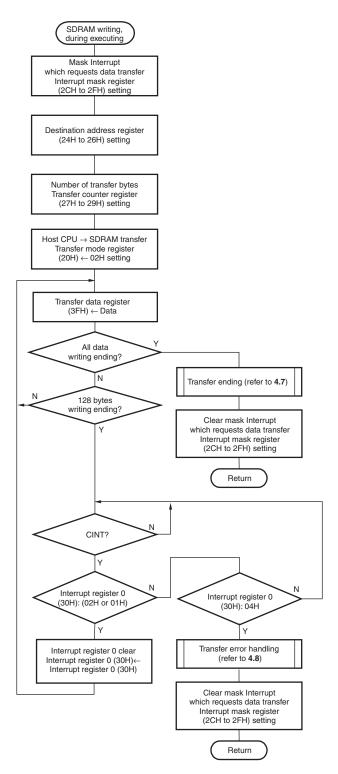

|    | 4.3 | SDRA   | .M Write during Executing                           | 56  |

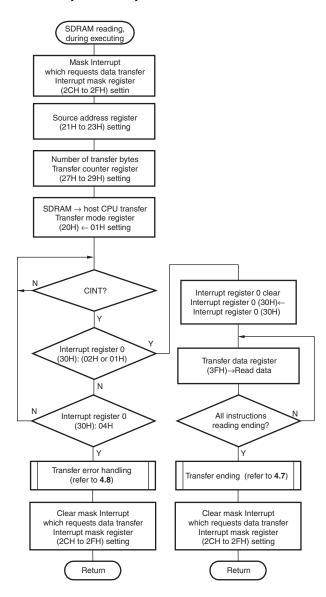

|    | 4.4 | SDRA   | .M Read during Executing                            | 57  |

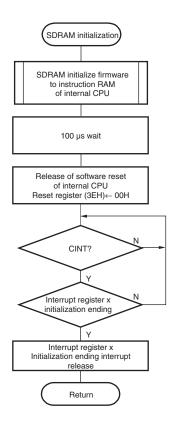

|    | 4.5 | SDRA   | M Initialization                                    | 58  |

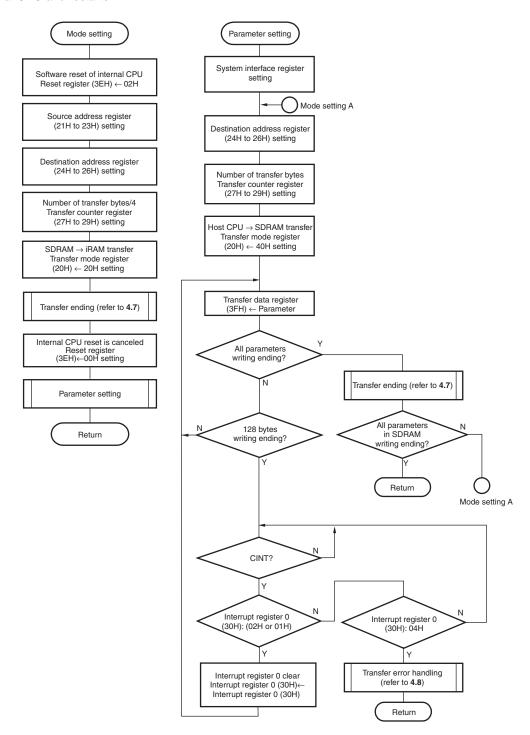

|    | 4.6 | Opera  | ation Mode Setting by Changing Firmware             | 59  |

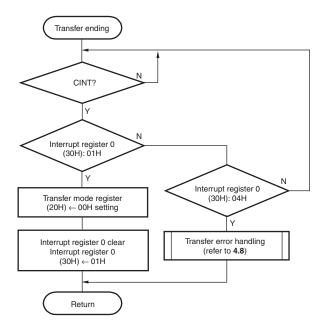

|    | 4.7 | Trans  | fer Ending                                          | 60  |

|    | 4.8 | Trans  | fer Error Handling                                  | 61  |

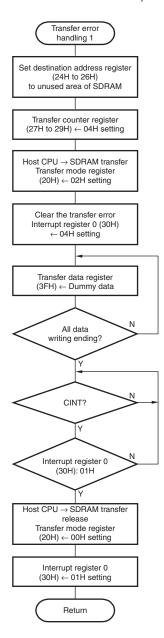

|    |     | 4.8.1  | Transfer error handling 1                           | 61  |

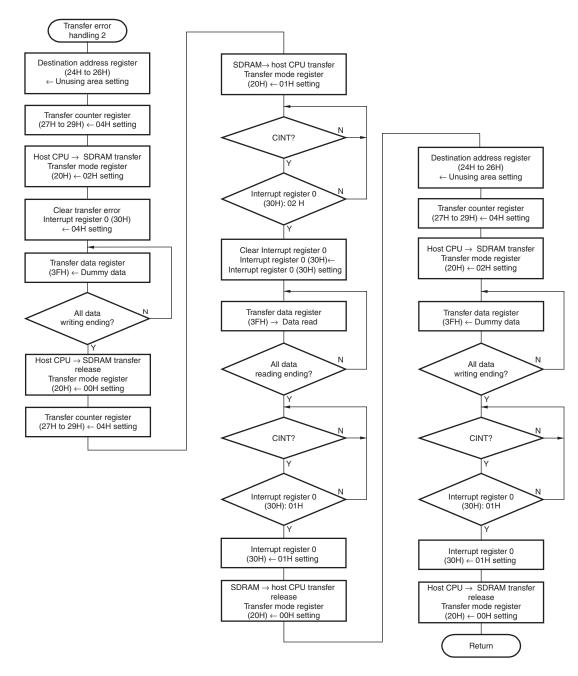

|    |     | 4.8.2  | Transfer error handling 2                           | 62  |

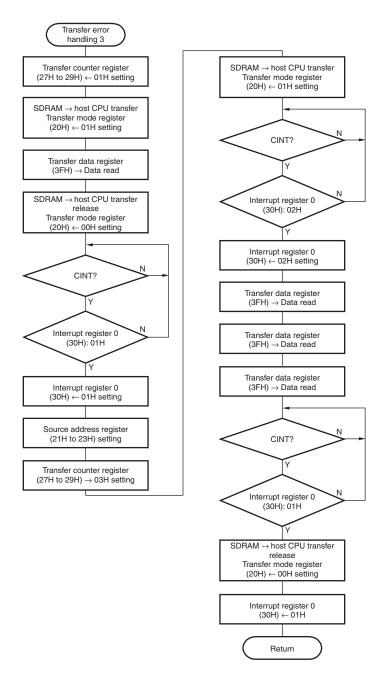

|    |     | 4.8.3  | Transfer error handling 3                           | 63  |

| 5. | EXA | MPLE   | FOR COMMON REGISTER USAGE                           | 64  |

|    | 5.1 | Regis  | ter Map Example                                     | 65  |

|    | 5.2 | Exam   | ple of the Common Register Which A Firmware Defines | 67  |

|    |     | 5.2.1  | COMCODE: Command code register                      | 66  |

|    |     | 5.2.2  | ESTS: Status register                               | 66  |

| 6. | ELE | CTRIC  | CAL CHARACTERISTICS                                 | 68  |

| 7. | PAC | KAGE   | DRAWING                                             | 102 |

| 8. | REC | СОММ   | ENDED SOLDERING CONDITIONS                          | 103 |

# 1. PIN FUNCTION

Sharing pin is bold faced in name and explains the feature shown.

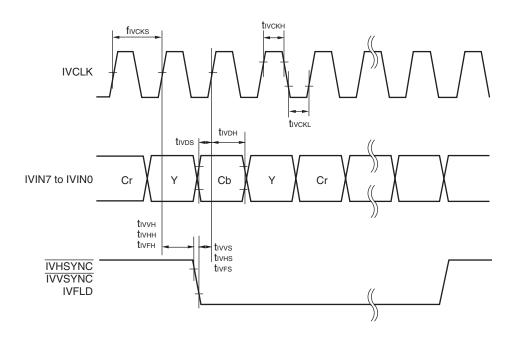

#### 1.1 Video Input Interface

The video input is based on the ITU-R BT.656 format. The horizontal synchronization signal, and the vertical synchronization signal, the field index can be used without using SAV and EAV to provide at ITU-R BT. 656, too.

| Name           | Ю | Pin<br>Number | Function                   | Active<br>Polarity |

|----------------|---|---------------|----------------------------|--------------------|

| IVIN7 to IVIN0 | ı | 23 to 16      | Video data                 |                    |

| IVCLK          | ı | 25            | Video clock (27 MHz)       | <b>↑</b>           |

| IVHSYNC        | ı | 12            | Horizontal synchronization | L                  |

| IVVSYNC        | I | 14            | Vertical synchronization   | L                  |

| IVFLD          | ı | 11            | Field index                |                    |

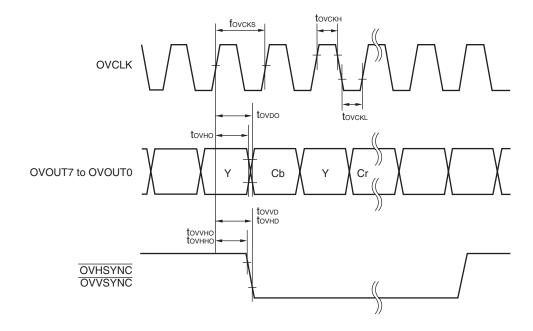

# 1.2 Video Output Interface

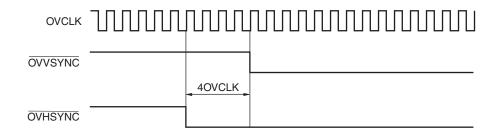

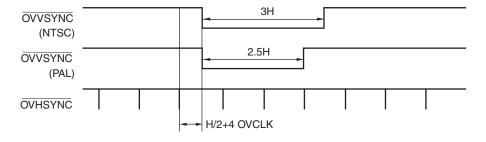

The video output is based on the ITU-R BT.656 format. It is able to output horizontal and vertical synchronization signals with SAV/EAV. These synchronization signals are chosen output by the firmware. These ports become GPO until the firmware initializes after hardware reset.

At the time of the odd field, OVVSYNC falls in the 4th clock after falling of OVHSYNC.

At the time of the even field, OVVSYNC falls in to the H/2+4th clock the OVHSYNC falling.

| Name                              | Ю | Pin<br>Number | Function                   | Active<br>Polarity |

|-----------------------------------|---|---------------|----------------------------|--------------------|

| OVOUT7, OVOUT6                    | 0 | 208, 207      | Video data                 |                    |

| OVOUT5 to OVOUT0/<br>FA19 to FA14 | 0 | 206 to<br>201 | Video data                 |                    |

| OVCLK                             | 0 | 199           | Video clock (27 MHz)       | 1                  |

| GPO5/OVHSYNC                      | 0 | 195           | Horizontal synchronization | L                  |

| GPO6/OVVSYNC                      | 0 | 197           | Vertical synchronization   | L                  |

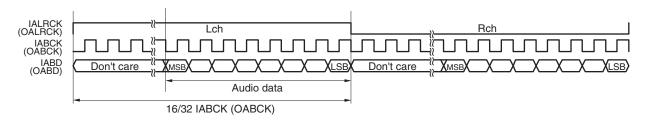

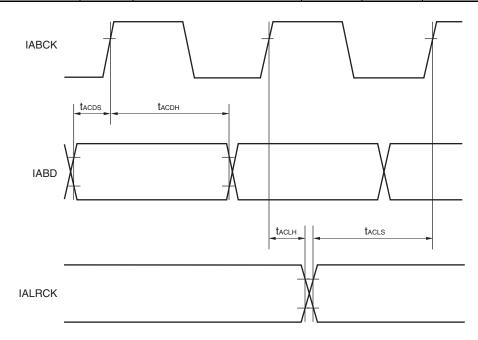

#### 1.3 Audio Input Interface

| Name   | Ю | Pin<br>Number | Function         | Active<br>Polarity |

|--------|---|---------------|------------------|--------------------|

| IALRCK | ı | 7             | Left/Right clock |                    |

| IABCK  | ı | 8             | Bit clock        | $\uparrow$         |

| IABD   | I | 9             | Bit data         |                    |

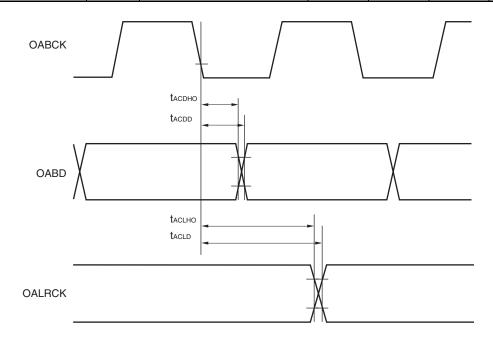

# 1.4 Audio Input/output Interface

After hardware reset, it becomes input. OALRCK, OABCK and OABD connect with 3.3 V  $V_{DD}$  through the 10  $k\Omega$  pull up resistance. Firmware controls input/output of those pins.

| Name   | Ю | Pin<br>Number | Function         | Active<br>Polarity |

|--------|---|---------------|------------------|--------------------|

| OALRCK | Ю | 4             | Left/Right clock |                    |

| OABCK  | Ю | 5             | Bit clock        | <b>↑</b>           |

| OABD   | Ю | 6             | Bit data         |                    |

| AMCLK  | I | 2             | Audio clock      | <b>↑</b>           |

#### 1.5 Stream Input Interface

Stream input corresponds to MPEG TS/PS stream. When slave mode (MPEG2-TS input with using valid signal), data input is possible to select 8 bits parallel data or serial data mode. When serial data mode, data input to IS0.

Active polarity of ISREQ is selected by the port setup register.

Active polarity of ISCLK/ISSTB, ISSYNC ISERR and ISVLD are selected by firmware. These are unsettled after the turning on.

| Name                | Ю | Pin                    | Function                                     | Active   |

|---------------------|---|------------------------|----------------------------------------------|----------|

|                     |   | Number                 |                                              | Polarity |

| ISREQ               | 0 | 55                     | Stream data request                          |          |

|                     |   |                        | Only parallel interface, this pin is active. |          |

|                     |   |                        | After reset, default is active low.          |          |

| ISCLK/ <b>ISSTB</b> | I | 53                     | Stream data strobe                           |          |

|                     |   |                        | After reset, default is ISCLK.               |          |

| ISCLK/ISSTB         | ı | 53                     | Stream data clock                            |          |

|                     |   |                        | After reset, default is active high edge.    |          |

| ISSYNC              | Ι | 52                     | Stream data synchronization                  |          |

|                     |   |                        | After reset, default is active high.         |          |

| ISVLD               | Ι | 54                     | Stream data valid                            |          |

|                     |   |                        | After reset, default is active low.          |          |

| IS1/ISERR           | Ι | 43                     | Stream error                                 |          |

|                     |   |                        | After reset, default is active high.         |          |

| IS1/ISERR           | I | 43                     | Stream data input                            |          |

| IS7 to IS2, IS0     | I | 51,49, 47<br>to 44, 42 | Stream data input                            |          |

|                     |   | 10 44, 42              |                                              |          |

**Remark** In this table, means of reset are hardware reset by the RESET pin and ALL RESET of the reset register.

# 1.6 Stream Output Interface

This interface outputs MPEG TS/PS stream. When in master mode (MPEG2-TS output with using valid signal), data output is possible to select 8bits parallel data or serial data mode. In serial mode, data output from OS0.

Active polarity of OSVLD is selected by the port setup register.

Active polarity of OSCLK/OSSTB and OSSYNC are selected by firmware. These are unsettled after the turning on.

| Name                | Ю | Pin<br>Number | Function                                  | Active<br>Polarity |

|---------------------|---|---------------|-------------------------------------------|--------------------|

| OSREQ               | I | 70            | Stream data request in slave mode         | L                  |

| OSCLK/ <b>OSSTB</b> | 0 | 66            | Stream data strobe                        |                    |

|                     |   |               | After reset, default is active high edge. |                    |

| OSCLK/OSSTB         | 0 | 66            | Stream data clock                         |                    |

|                     |   |               | After reset, default is OSSTB.            |                    |

| OSSYNC              | 0 | 67            | Stream data synchronization               |                    |

|                     |   |               | After reset, default is active high.      |                    |

| OSVLD/OSRDY O 68    |   | 68            | Stream data valid                         |                    |

|                     |   |               | After reset, default is OSRDY.            |                    |

| OSVLD/ <b>OSRDY</b> | 0 | 68            | Stream data ready prepared                |                    |

|                     |   |               | After reset, default is active low.       |                    |

| OS7 to OS0/         | 0 | 65 to 63,     | Stream data output                        |                    |

| FA13 to FA6         |   | 61, 59 to     |                                           |                    |

|                     |   | 56            |                                           |                    |

**Remark** In this table, means of reset are hardware reset by the RESET pin and ALL RESET of the reset register.

# 1.7 SDRAM Interface

| Name        | Ю | Pin Number                                                                                    | Function                                      | Active<br>Polarity |

|-------------|---|-----------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------|

| MA13 to MA0 | 0 | 104, 103, 115, 102, 114, 113, 111, 109, 108, 106, 101, 99, 97, 95                             | Address of row/column                         |                    |

| MD31 to MD0 | Ю | 93 to 89, 87, 85, 83, 72, 75 to 81, 149, 147 to 143, 141, 139, 127, 129, 131 to 134, 136, 138 | Data (Built-in 50 $k\Omega$ pull up resistor) |                    |

| MCLK        | 0 | 118                                                                                           | Clock                                         | <b>↑</b>           |

| MCKE        | 0 | 116                                                                                           | Clock enable                                  | Н                  |

| MCS         | 0 | 120                                                                                           | Chip selection                                | L                  |

| MRAS        | 0 | 121                                                                                           | Row address strobe                            | L                  |

| MCAS        | 0 | 123                                                                                           | Column address strobe                         | L                  |

| MWE         | 0 | 125                                                                                           | Write enable                                  | L                  |

| MDQM        | 0 | 126                                                                                           | Data input/output mask enable                 | L                  |

# 1.8 Host CPU Interface

It chooses a parallel bus connection and a serial bus connection by the setting of CMODE2.

| Name   | Ю | Pin<br>Number | Function                  | Active<br>Polarity |

|--------|---|---------------|---------------------------|--------------------|

| CMODE2 | ı | 158           | Host CPU interface select |                    |

|        |   |               | L: Parallel, H: Serial    |                    |

# 1.8.1 Parallel bus interface

| Name                      | Ю | Pin Number                                                             | Function                                                                                                 | Active<br>Polarity |

|---------------------------|---|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------|

| CA5 to CA0/<br>FA5 to FA0 | I | 187, 185 to 181                                                        | Address                                                                                                  |                    |

| CD7 to CD0/<br>FD7 to FD0 | Ю | 172, 170 to<br>166, 164, 162                                           | Data                                                                                                     |                    |

| CWE/CSDI                  | Ι | 157                                                                    | Write enable                                                                                             | L                  |

| CRE                       | I | 160                                                                    | Read enable                                                                                              | L                  |

| ccs                       | I | 159                                                                    | Chip selection                                                                                           | L                  |

| CINT                      | 0 | 153                                                                    | Interrupt                                                                                                | Н                  |

| CWAIT/FOE                 | 0 | 161                                                                    | Wait                                                                                                     |                    |

| CMODEO/CSCLK              | I | 155                                                                    | Setting of polarity of CWAIT  L: Low wait, H: High wait                                                  |                    |

| CMODE1/CSDO               | I | Setting of operation of CWAIT (Built-in 50 $k\Omega$ pull up resistor) |                                                                                                          |                    |

|                           |   |                                                                        | L: Wait operation.(after ready, pin continues ready) H: Ready operation.(after ready, pin turns to wait) |                    |

#### 1.8.2 Serial bus interface

When connecting a serial bus, it downloads instruction of internal CPU from instruction ROM.

# (1) Serial bus interface

| Name         | Ю | Pin<br>Number | Function                                                                   | Active<br>Polarity |

|--------------|---|---------------|----------------------------------------------------------------------------|--------------------|

| CMODE0/CSCLK | Ι | 155           | SPI serial interface clock                                                 |                    |

|              |   |               | Fix CSCLK to high level during CCS is disable (high level).                |                    |

| CWE/CSDI     | Ι | 157           | SPI serial interface data input                                            |                    |

| CMODE1/CSDO  | 0 | 156           | SPI serial interface data output (Built-in 50 k $\Omega$ pull up resistor) |                    |

| ccs          | I | 159           | Chip selection                                                             | L                  |

| CINT         | 0 | 153           | Interrupt                                                                  | Н                  |

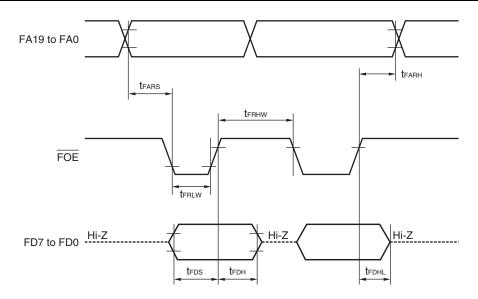

# (2) Instruction ROM interface

| Name                              | Ю | Pin Number                   | Function      | Active<br>Polarity |

|-----------------------------------|---|------------------------------|---------------|--------------------|

| CA5 to CA0/<br>FA5 to FA0         | 0 | 187, 185 to 181              | Address       |                    |

| OS7 to OS0/<br>FA13 to FA6        | 0 | 65 to 63, 61, 59<br>to 56    | Address       |                    |

| OVOUT5 to OVOUT0/<br>FA19 to FA14 | 0 | 206 to 201                   | Address       |                    |

| CD7 to CD0/<br>FD7 to FD0         | I | 172, 170 to<br>166, 164, 162 | Data          |                    |

| CWAIT/ <b>FOE</b>                 | 0 | 161                          | Output enable | L                  |

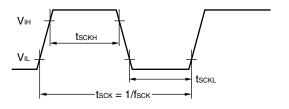

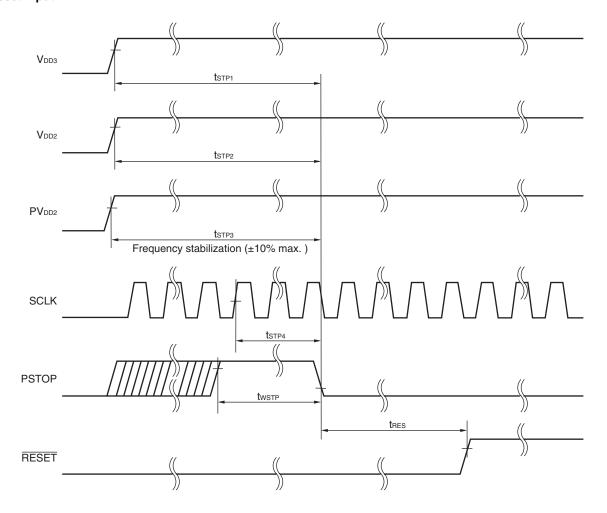

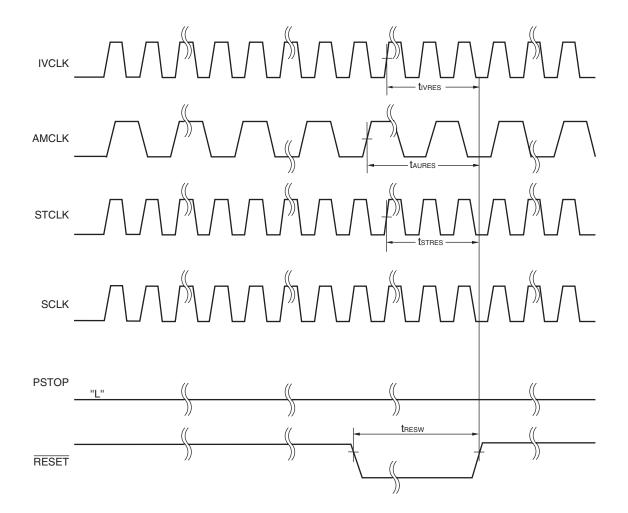

# 1.9 Clock, Reset

| Name  | Ю | Pin Number | Function                        | Active<br>Polarity |

|-------|---|------------|---------------------------------|--------------------|

| SCLK  | Ι | 28         | System clock                    | <b>↑</b>           |

| STCLK | Ι | 34         | System time clock               | <b>↑</b>           |

| PSTOP | - | 29         | Internal PLL operation control  | Н                  |

|       |   |            | L: Normal, H: Internal PLL stop |                    |

| PWM   | 0 | 40         | PWM output                      |                    |

| RESET | Ι | 151        | Reset                           | L                  |

# 1.10 N-Wire

IE Port for firmware of Internal CPU evaluation

When not connecting an in-circuit emulator, take countermeasures against noise by pulling up the NDI pin to avoid the pin becoming low level.

| Name | Ю | Pin Number | Function                    | Active<br>Polarity |

|------|---|------------|-----------------------------|--------------------|

| NMOD | ı | 178        | Pin used when connecting IE |                    |

|      |   |            | Pull up when connecting IE  |                    |

| NCLK | I | 174        | Serial clock                | <b>↑</b>           |

| NRST | I | 176        | N-wire reset                | L                  |

| NDI  | I | 179        | Data input                  |                    |

| NDO  | 0 | 180        | Data output                 |                    |

# 1.11 GPIO

GPIO becomes input after hardware reset by the  $\overline{\text{RESET}}$  pin and ALL RESET by the reset register. GPIO connect with 3.3 V V<sub>DD</sub> through the 10 k $\Omega$  pull up resistance.

| Name         | Ю | Pin<br>Number | Function         | Active<br>Polarity |

|--------------|---|---------------|------------------|--------------------|

| GPIO0        | Ю | 189           | Firmware use pin |                    |

| GPIO1        | Ю | 190           | Firmware use pin |                    |

| GPIO2        | Ю | 191           | Firmware use pin |                    |

| GPIO3        | Ю | 192           | Firmware use pin |                    |

| GPIO4        | Ю | 193           | Firmware use pin |                    |

| GPO5/OVHSYNC | 0 | 195           | Firmware use pin |                    |

| GPO6/OVVSYNC | 0 | 197           | Firmware use pin |                    |

# 1.12 Power Supply

| Name              | Ю | Pin Number                                                                                                                                    | Function                                    | Active<br>Polarity |

|-------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------|

| V <sub>DD3</sub>  | - | 39, 69, 86, 98, 110, 122, 135, 148, 171, 194                                                                                                  | 3.3 V power supply for interface            |                    |

| V <sub>DD2</sub>  | ı | 1, 13, 24, 36, 48, 60, 71, 82, 94, 105, 117, 128, 140, 152, 163, 175, 186, 198                                                                | 2.5 V power supply for the internal circuit |                    |

| GND               | - | 3, 10, 15, 26, 27, 35, 37, 38, 41, 50, 62, 73, 74, 84, 88, 96, 100, 107, 112, 119, 124, 130, 137, 142, 150, 154, 165, 173, 177, 188, 196, 200 | GND                                         |                    |

| PV <sub>DD2</sub> | - | 30, 32                                                                                                                                        | 2.5 V power supply for PLL                  |                    |

| PGND              | - | 31, 33                                                                                                                                        | GND for PLL                                 |                    |

# 1.13 Recommended Connections of Unused Pins

Connect unused pins as follows.

| Name                          | Ю | Connection                          |

|-------------------------------|---|-------------------------------------|

| IVIN7 to IVIN0                | ı | GND                                 |

| IVCLK                         | I | GND                                 |

| IVHSYNC                       | I | GND                                 |

| IVVSYNC                       | ı | GND                                 |

| IVFLD                         | 1 | GND                                 |

| OVOUT7, OVOUT6                | 0 | Open                                |

| OVOUT5 to OVOUT0/FA19 to FA14 | 0 | Open                                |

| OVCLK                         | 0 | Open                                |

| IALRCK                        | I | GND                                 |

| IABCK                         | 1 | GND                                 |

| IABD                          | ı | GND                                 |

| OALRCK                        | Ю | Pull up with 10 kΩ resistor         |

| OABCK                         | Ю | Pull up with 10 kΩ resistor         |

| OABD                          | Ю | Pull up with 10 kΩ resistor         |

| AMCLK                         | I | GND                                 |

| ISREQ                         | 0 | Open                                |

| ISCLK/ISSTB                   | I | GND                                 |

| ISSYNC                        | I | GND                                 |

| ISVLD                         | I | GND                                 |

| IS7 to IS0                    | I | GND                                 |

| OSREQ                         | I | GND                                 |

| OSSYNC                        | 0 | Open                                |

| CA5 to CA0/FA5 to FA0         | Ю | Open                                |

| CD7 to CD0/FD7 to FD0         | Ю | Pull up with 10 kΩ resistor         |

| CRE                           | I | GND                                 |

| CINT                          | 0 | Open                                |

| CWAIT/FOE                     | 0 | Open                                |

| PWM                           | 0 | Open                                |

| NMOD                          | I | Pull up with 4.7 kΩ resistor        |

| NCLK                          | I | Pull up with 4.7 kΩ resistor        |

| NRST                          | I | Pull down with 50 kΩ resistor       |

| NDI                           | I | Pull up with 4.7 kΩ resistor        |

| NDO                           | 0 | Pull up with 4.7 kΩ resistor        |

| GPIO4 to GPIO0                | Ю | Pull up with 10 k $\Omega$ resistor |

| GPO5/OVHSYNC                  | 0 | Open                                |

| GPO6/OVVSYNC                  | 0 | Open                                |

#### 2. FEATURE OVERVIEW

The functions and I/O interfaces are set using firmware. Supported functions differ depending on firmware.

#### 2.1 Video

This LSI can do flexible encoding and transcoding by using the firmware control of internal CPU and an exclusive use circuit. NTSC/PAL video format, which is possible of the encoding is as in **Table 2-1**. NTSC/PAL video format of the transcoding is under 720 dots by 480/576 line/frame.

MPEG2 MPEG1 Video format Yes No 720 dots by 480/576 line/frame Yes No 704 dots by 480/576 line/frame Yes No 544 dots by 480/576 line/frame Yes No 480 dots by 480/576 line/frame Yes No 352 dots by 480/576 line/frame Yes Yes 352 dots by 240/288 line/frame

Table 2-1. Video Format

#### 2.1.1 Encoding

It encodes the video that was converted from the 4:2:2 format into the 4:2:0 format in the video input/output unit with MPEG2 standard MP@ML, SP@ML and the MPEG1 standard. It is encoding in variable bit rate (single path VBR encoding) or constant bit rate (CBR). The pre analysis supports high quality picture encoding. Encode supports frame structure.

- Using the following, only 64 Mbits SDRAM is needed.

- Encoding with locally decoding and/or time base corrector (TBC)

- PAL encoding

- DVD encoding needs equal to 128 Mbits SDRAM area.

- The motion estimation size

- P picture:  $\pm 128$  dots (H) by  $\pm 64$  lines (V)

- B picture:  $\pm 96$  dots (H) by  $\pm 48$  lines (V),  $\pm 64$  dots (H) by  $\pm 32$  lines (V)

- I/P picture period in MP@ML :  $M \le 3$

- Dual prime estimate, only at the time of M = 1.

#### 2.1.2 Transcoding

It transcodes the stream of MPEG2 standard MP@ML based. It is possible for the bit rate conversion.

#### 2.1.3 Input/output processing

#### (1) Video input

The video input format is ITU-R BT.656 (8-bit Y/Cb/Cr the 4:2:2 format) and 8-bit Y/Cb/Cr which deals with the 4:2:0 format. The horizontal synchronization signal, the vertical synchronization signal and the field index can be used without using SAV and EAV. In this case, IVFLD can be used by taking with IVVSYNC or it judges a field judgment in the polarity of IVHSYNC behind the falling edge two clock of IVVSYNC. It judges that an odd field is 'H' and an even field is 'L'. IVVSYNC and IVHSYNC need the high / low period more than 3 IVCLK. The video-input unit watches over the synchronization signals and detects synchronous error.

#### (2) Picture size conversion filter

For adapting to the bit rate of the stream, the picture size of the encoding can be changed. In addition, picture size changed with the external filter to the 4:2:0 format can be inputted directly, too.

Format Line Data arrangement

4:2:2 Odd/even lines Cb0, Y0, Cr0, Y1, Cb1, Y2, Cr1, Y3, Cb2, Y4, Cr2, Y5, ...

4:2:0 Odd lines Cb0, Y0, Cr0, Y1, Cb1, Y2, Cr1, Y3, Cb2, Y4, Cr2, Y5, ...

Even lines (-), Y0, (-), Y1, (-), Y2, (-), Y3, (-), Y4, (-), Y5, ...

**Table 2-2. Input Video Data Arrangement**

# (3) Time base corrector (TBC)

It has a frame-type TBC. It is possible to make stable encoding of the channel changing and the nonstandard video signal such as VTR. When using TBC, it needs over 64 Mbits SDRAM. The following video signals can be corrected.

| Horizontal Sync | Vertical Sync |

| NTSC | 1626 to 1806 IVCLK/H | 246 to 278 H/V |

| PAL | 1628 to 1828 IVCLK/H | 294 to 330 H/V |

Table 2-3. Correctable Video Signals

Remark IVCLK: 27 MHz

#### (4) Noise reduction

Respectively the noise reduction of the luminance signal and the color signal can be set three levels

#### (5) Slicer

Slicer decodes the luminance signal to the vertical blanking data. It detects VBID, Closed Caption, and Wide Screen Signal. The host CPU can read, and stop encoding and re-write the copy control information in VBID and the Wide Screen Signal, on the host CPU interface.

Table 2-4. Slicer

| TV method | VBI data           | Detection line |

|-----------|--------------------|----------------|

| NTSC      | VBID               | 20, 283        |

|           | Closed caption     | 21, 284        |

| PAL       | Wide screen signal | 23 (336)       |

#### (6) Video output

It converts an input video or a local-decoded video into picture size of 720 dots by 480/576 line and outputs with the ITU-R BT.656 format.

Horizontal and vertical synchronization signals are switched from GPO.

Field detection is easy due to vertical synchronization signal delays 4VCLK since horizontal synchronization signal.

Figure 2-1. Video Output

(a) Odd Field

# OVVSYNC (NTSC) OVVSYNC (PAL) OVHSYNC

#### 2.2 Audio

This LSI encodes the MPEG audio encoding and transcode with the internal DSP.

#### 2.2.1 Encoding

It encodes MPEG1 audio layer 2 or Dolby Digital Consumer Encoder (only the  $\mu$ PD61052). In addition, it is possible to bypass internal audio encode DSP, when the audio elementary stream is encoded by an external audio encoder are inputted.

#### 2.2.2 Transcoding (DEMUX, MUX)

It is possible to multiplex two de-multiplexed audio streams. It analyzes MPEG1 audio stream, and extracts the information to multiplex and notify to the host CPU.

#### 2.2.3 Input/output processing

Two PCM audio signals can be inputted to the audio input interface and the audio input-output interface. When inputting two audio signals, an audio signal is encoded, and another one bypasses the audio encoding DSP, and transfers to the multiplexer. When inputting an audio elementary stream that has been encoded by the external audio encoder and PCM audio, it can multiplex two audio elementary streams.

The PCM audio or the audio elementary stream can be outputted from the audio input-output interface. The audio clock (AMCLK) types the clock by which a phase was locked up STC clock (STCLK).

Item

Input/output format

Data length

16 bits, 20 bits, 24 bits

Sampling frequency

32 kHz, 44.1 kHz, 48 kHz

Justification of transfer

MSB first

I'S Compatible/Left justified/Right justified

Format

PCM Audio, IEC60958 based

Table 2-4. Audio Input/output

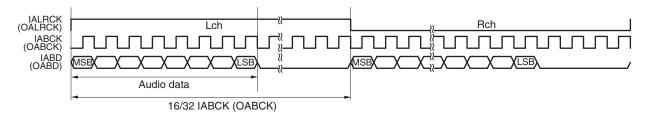

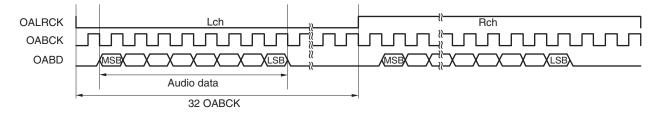

Figure 2-2. Audio Input

# (a) MSB First Right Justified Mode

# (b) MSB First Left Justified Mode

# (c) I<sup>2</sup>S Mode

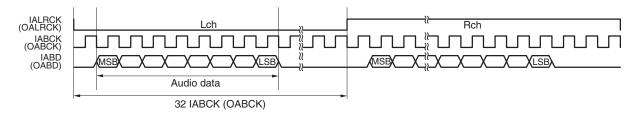

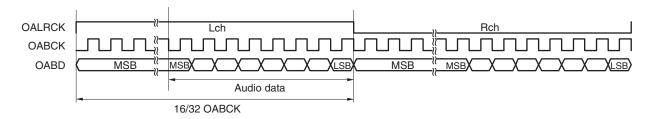

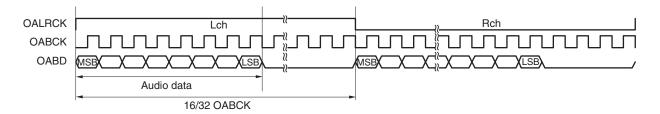

Figure 2-3. Audio Output

# (a) MSB First Right Justified Mode

# (b) MSB First Left Justified Mode

# (c) I2S Mode

# 2.3 MPEG System Processing

This LSI multiplexes and/or de-multiplexes Audio and video streams based on MPEG2-TS/PS and MPEG1. By combining the multiplexer and de-multiplexer, it does the transcode which is accompanied by MPEG2-TS⇔MPEG2 PS conversion.

#### 2.3.1 System time clock

# (1) Encoding system

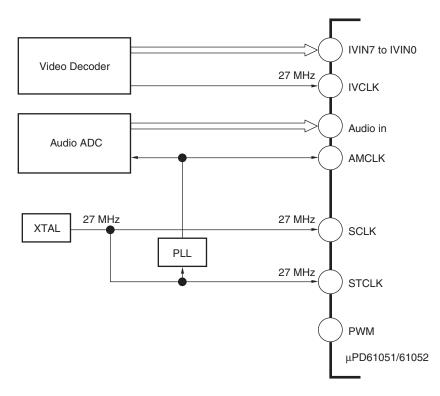

When the encoding system operates, it uses the clock input to STCLK that is generated with the 27 MHz oscillator.

Audio master clock is made with 27 MHz of STCLK, and then Audio synchronizes to STC.

Figure 2-4. System Time Clock Input (Encoding System)

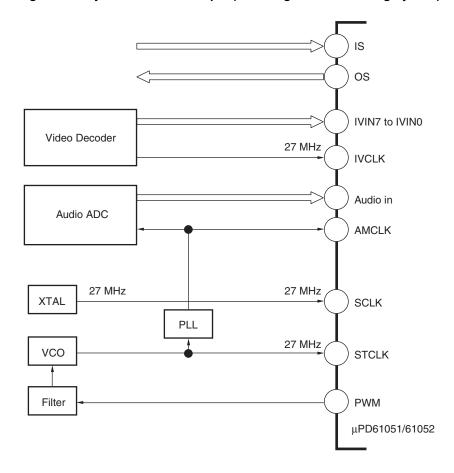

## (2) Encoding and Transcoding system

It can output the signal, which generates the pulse wide modulation (PWM) with comparing PCR/SCR of the stream and system time clock value, for making the reference clock of the system.

Figure 2-5. System Time Clock Input (Encoding and Transcoding System)

# 2.3.2 Multiplex

It stamps SCR, PCR, DTS and PTS after multiplexing streams that are from the video encoder and the audio encoder based on MPEG2-TS/PS.

Partial TS can be made by forming SIT packet from PSI and SI data of base on DVB.

It is possible to multiplex the packet that inputted from the host CPU interface.

# 2.3.3 De-multiplex

#### (1) MPEG2-TS

Using the PID filter corresponding to 16 PIDs, It separates MPEG2-TS to one video stream, two audio streams, and two user data streams. Internal CPU extracts section data in PSI and SI of base on DVB.

#### (2) MPEG2-PS

With the stream ID filter, it separates MPEG2-PS to one video stream, one audio stream, and two user data streams.

#### (3) VBI data

The user data stream, the wide screen signal, the closed caption, VBID and format of the video and the audio can be read from the host CPU interface.

#### 2.3.4 Transcode

The transcode is a combined multiplexer and de-multiplexer. MPEG2-TS/PS separates into a video stream, two audio streams, and two user data streams. The video stream and the audio stream are multiplexed to MPEG2-TS/PS after transcode on the elementary. PCR, SCR, PTS and DTS are corrected when multiplexing.

In the transcode of MPEG2-TS, it can generate partial TS using the data detected by the PID filter and the section filter.

Stream

MPEG2-TS/PS

De-multiplexer

Audio ES

Stream Buffer

Audio ES

Stream Buffer

Figure 2-6. Transcode

The change of the MPEG system layer is shown below.

$MPEG2-TS \Rightarrow MPEG2-TS$

MPEG2-TS ⇒ MPEG2-PS

$MPEG2-PS \Rightarrow MPEG2-TS$

$MPEG2-PS \Rightarrow MPEG2-PS$

MPEG1 ⇒ MPEG1

#### 2.4 Stream Interface

When it inputs MPEG2-TS, it is able to connect parallel data or serial data with the  $\mu$ PD61051/61052. When it inputs MPEG2-PS, it should connect parallel data with the  $\mu$ PD61051/61052.

#### 2.4.1 Parallel steam data interface

This LSI connects to external device by the master mode or the slave mode. When parallel interface, the maximum stream input rate is 100 Mbps, the maximum stream output rate is 30 Mbps. The stream of MPEG encoding and transcode is limited to 15 Mbps on MPEG MP@ML.

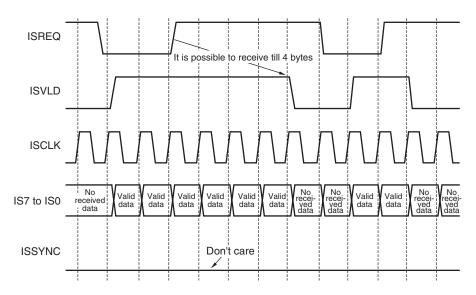

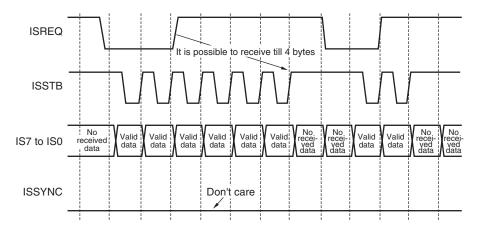

# (1) Stream Input

It is possible to receive 4 bytes data after invalid of ISREQ of the stream input.

Remark ISSTB and ISCLK are identical pins.

Figure 2-7. Parallel Stream Receiving Mode (1/2)

#

## (a) Example for Receiving of MPEG2-TS

ISCLK shall be under 13.5 MHz.

Figure 2-7. Parallel Stream Receiving Mode (2/2)

# (b) Example of Receiving MPEG2-PS, ES with Valid and Clock

# (c) Example of Receiving MPEG2-PS, MPEG2-ES with a Strobe

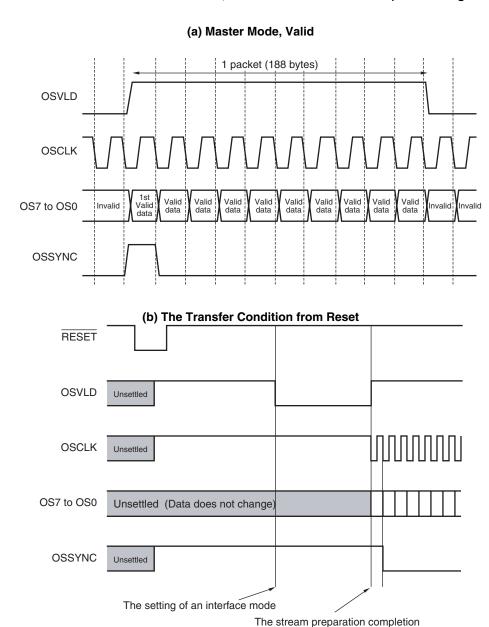

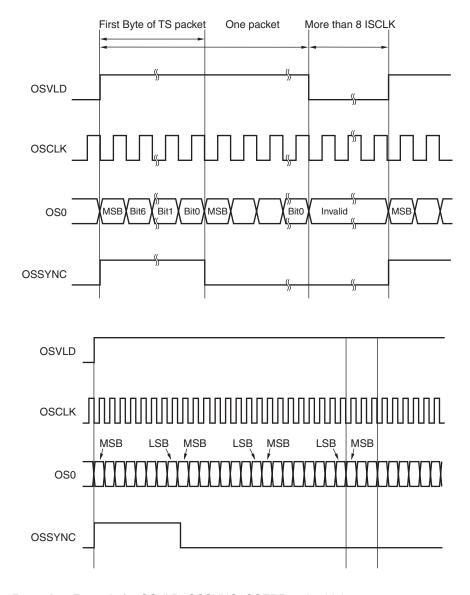

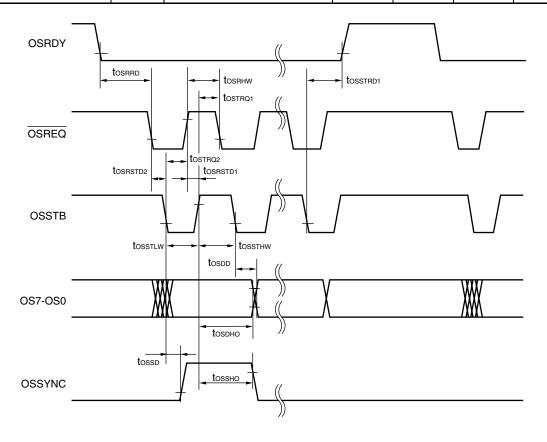

# ★ (2) Stream output

There are two modes: valid operation master mode and strobe operation byte transfer mode.

The appropriate transfer mode for the system can be selected by setting the two stream output mode and transfer rate.

**Remark** OSSTB and OSRDY are the same pins as OSCLK and OSVLD, respectively. Operation can be selected using combinations of OSSTB and OSRDY or OSCLK and OSVLD.

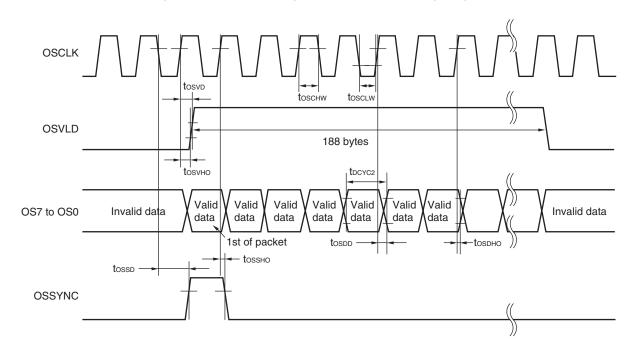

#### (a) Master Mode Valid

This is the MPEG2-TS dedicated output mode.

The period of OSCLK can be selected from n times 37 ns (1/27 MHz) ( $3 \le n \le 255$ , n is an integer). If using local decode or input video display, the period is  $4 \le n \le 255$  (n is an integer).

Figure 2-8. Parallel Stream Transmission Mode; Transmission of MPEG2-TS (Packet Length is 188 Bytes)

27

# (b) Bytes Transfer Mode, Strobe

In byte transfer mode, the transfer rate is determined by the handshake of OSREQ and OSSTB.

Figure 2-9. Parallel Stream Transmission Mode (Transmission of MPEG2-PS, MPEG2-ES)

# (a) Example for Transmission of Strobe Mode One Byte Transfer

# (b) The Transfer Condition from Reset

28

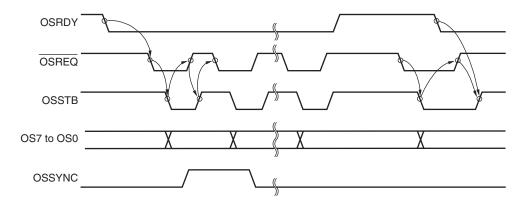

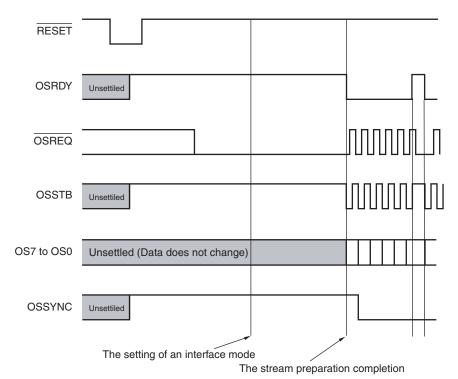

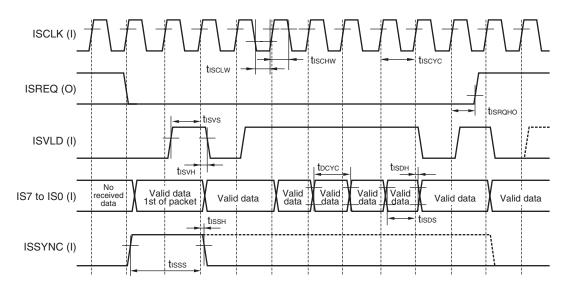

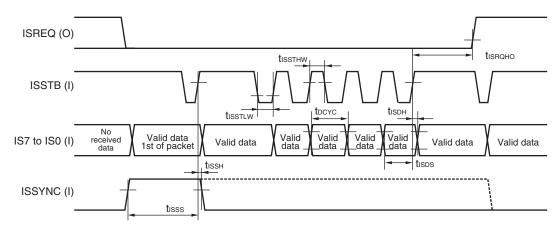

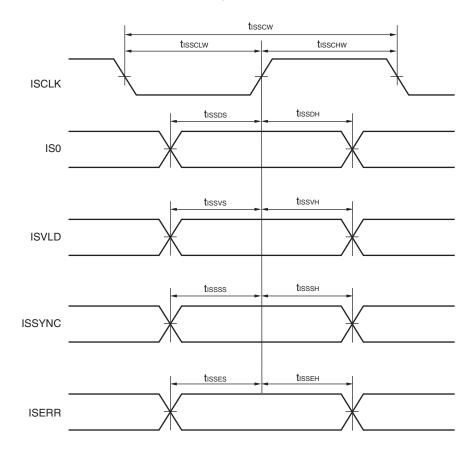

#### 2.4.2 Serial stream data interface

This LSI is able to input a serial stream. Bit rate of serial input is limited less than parallel interface. Serial Stream Interface can transfer only MPEG2-TS stream. Maximum bit rate of stream input is less then 64 Mbps. Bit rate of stream out is 27 Mbps. Additionally, encoding and transcoding bit rate is limited to 15 Mbps on MPEG2 MP@ML.

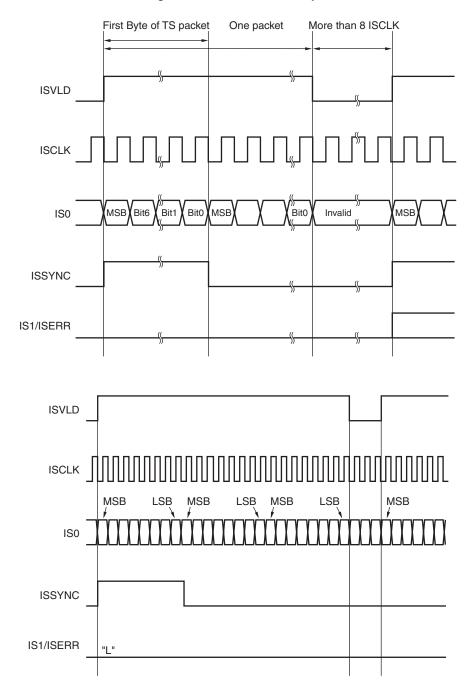

#### (1) Stream input

ISCLK is input by less than 64 MHz clock. Data is MSB first. ISSYNC should active while first byte each packet. If packet error occurred, ISERR should active from ISSYNC of the packet. ISVLD should valid while each byte. ISVLD shall invalid while 8 bits between each packets.

Figure 2-10. Serial Stream Input

**Remark** Example for ISVLD, ISSYNC, ISERR active high, ISCLK active high edge

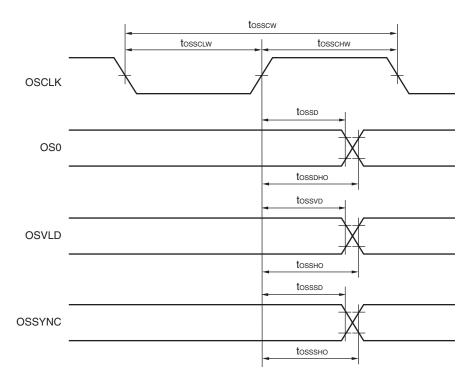

# (2) Stream Output

OSCLK is fixed 27 MHz OSSYNC active at first byte in each packet. OSVLD is active of 1 packet continuously. Data is the MSB first outputs. ISSYNC becomes active among 1 byte at the head of the packet.

Figure 2-11. Serial Stream Output

Remark Example for OSVLD, OSSYNC, OSERR active high

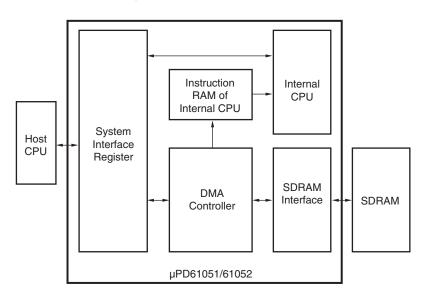

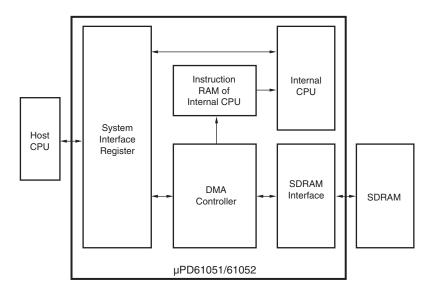

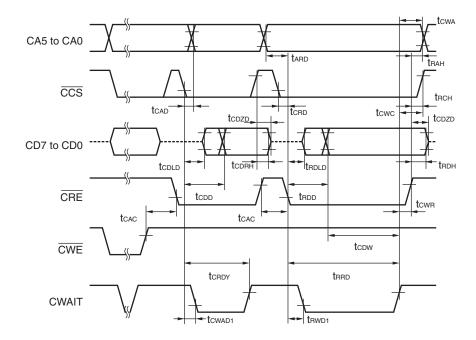

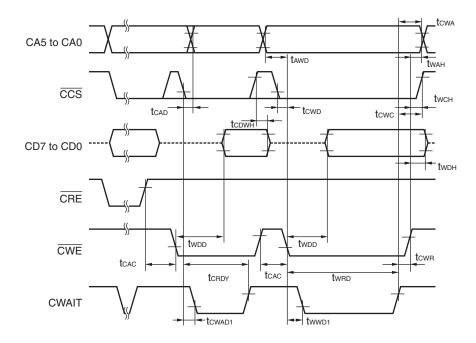

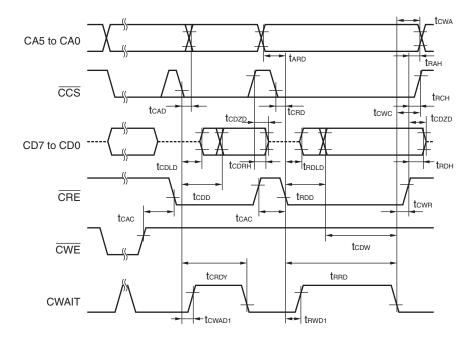

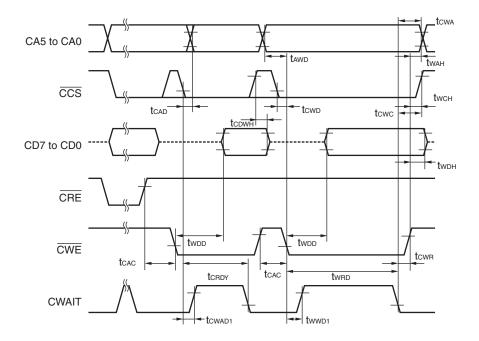

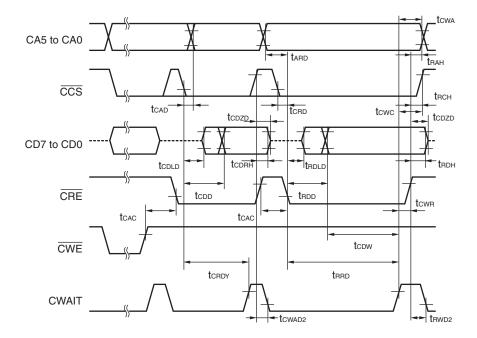

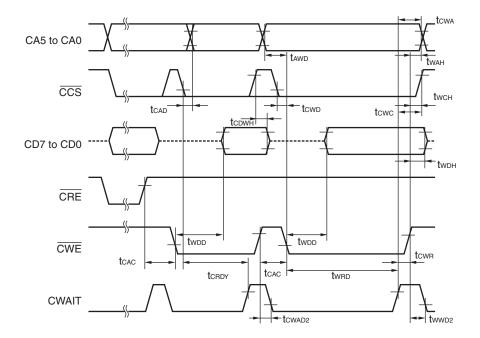

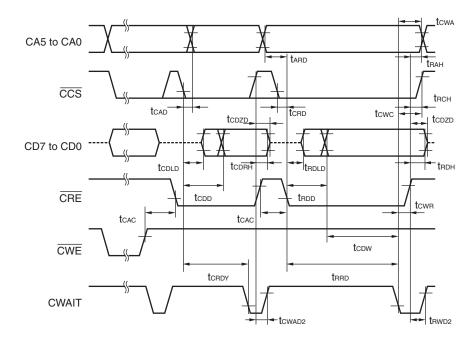

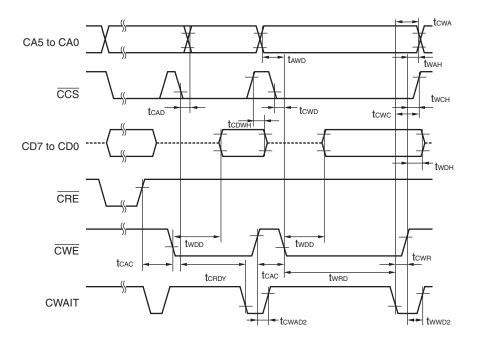

#### 2.5 Host CPU Interface

The connection of the host CPU can select the eight bits parallel data interface and serial interface (SPI). Internal CPU sends and receives command status through the System Interface Register, which is in the host CPU interface unit. In addition, to control an internal DMA controller through the system interface register, it loads an instruction for internal CPU to the instruction RAM and the transfer of the large-volume data can be sent to the data area on SDRAM.

Figure 2-12. Host CPU Interface

The following describes loading of internal CPU instruction.

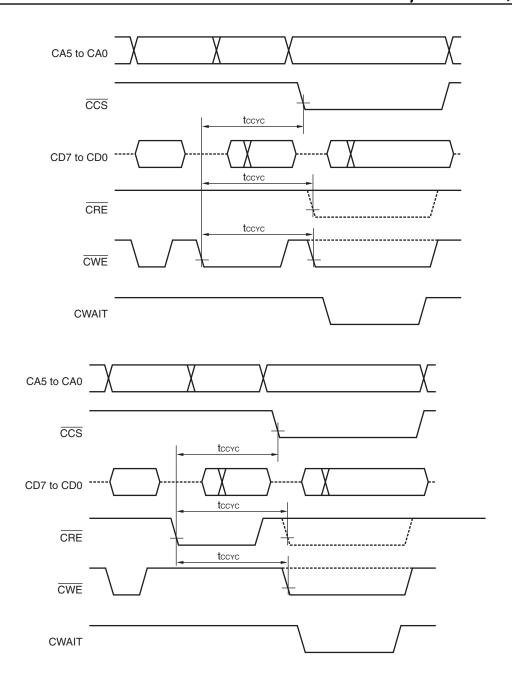

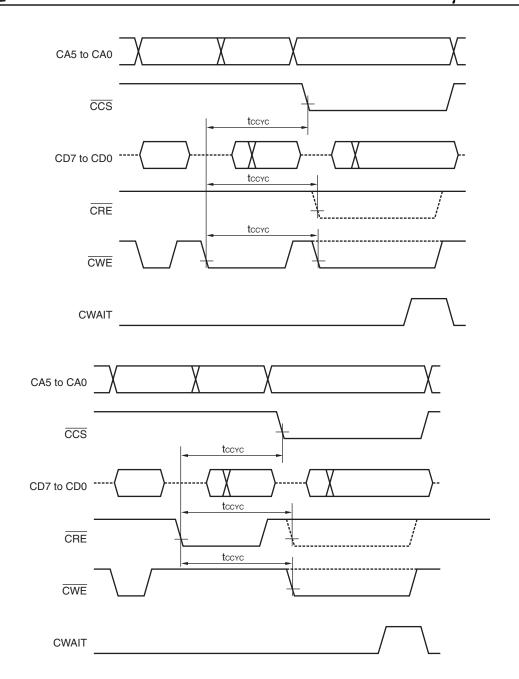

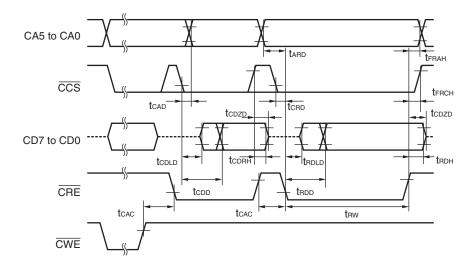

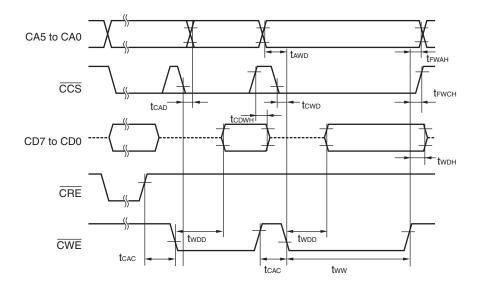

#### (1) Parallel interface

When parallel interface is selected, host interface has 6-bit address, 8-bit data bus and control ports.

CWAIT is selected with CMODE1 to wait on ready signal mode, CMODE1 selects active polarity of CWAIT.

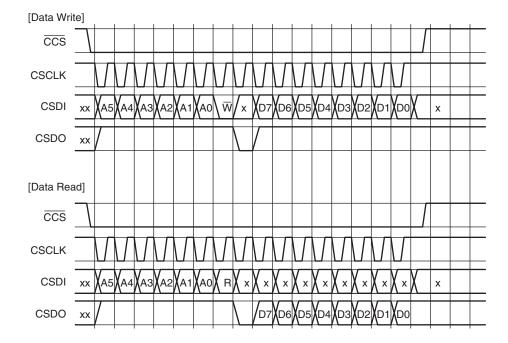

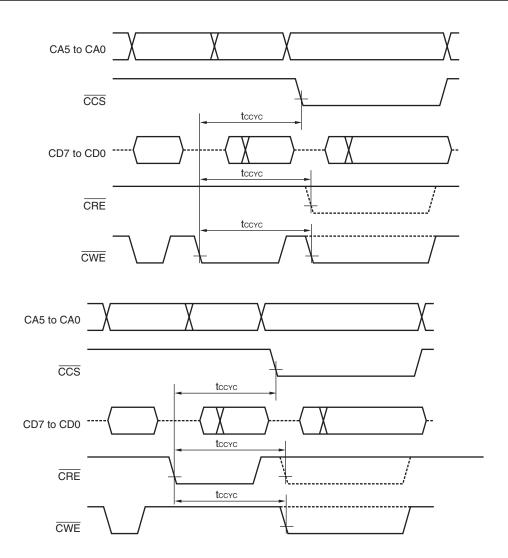

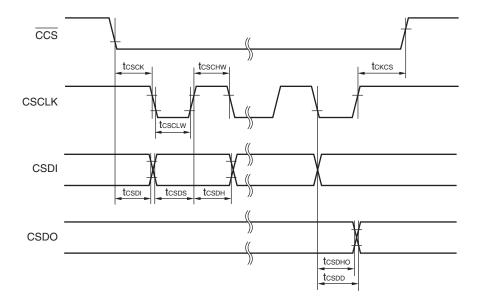

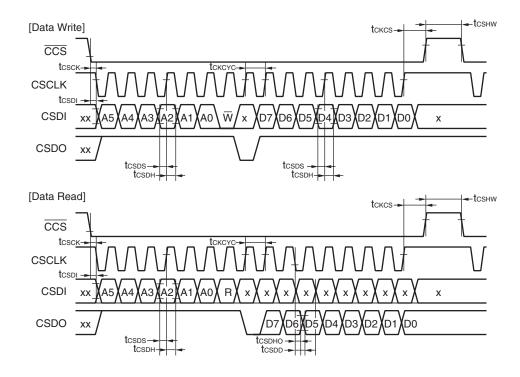

#### (2) Serial interface

The  $\mu$ PD61051/61052 communicates with the host CPU using the SPI (serial peripheral interface) serial bus. The host CPU becomes a bus master.

The low edge of the chip selection is communication beginning. Its high edge is communication ending. An address and the reading / writing mode are shown at the first byte after the chip selection becomes low. It is the MSB first of six bits of addresses, eight bits of data. Fix CSCLK to high level during  $\overline{CCS}$  is disabled (high level).

The  $\mu$ PD61051/61052 becomes a master and downloads the instruction of the internal CPU from external ROM.

CSCLK: The serial clock

CSDI: The data input

CSDO: The data output

CCS: The chip selection

Figure 2-13. Serial Interface

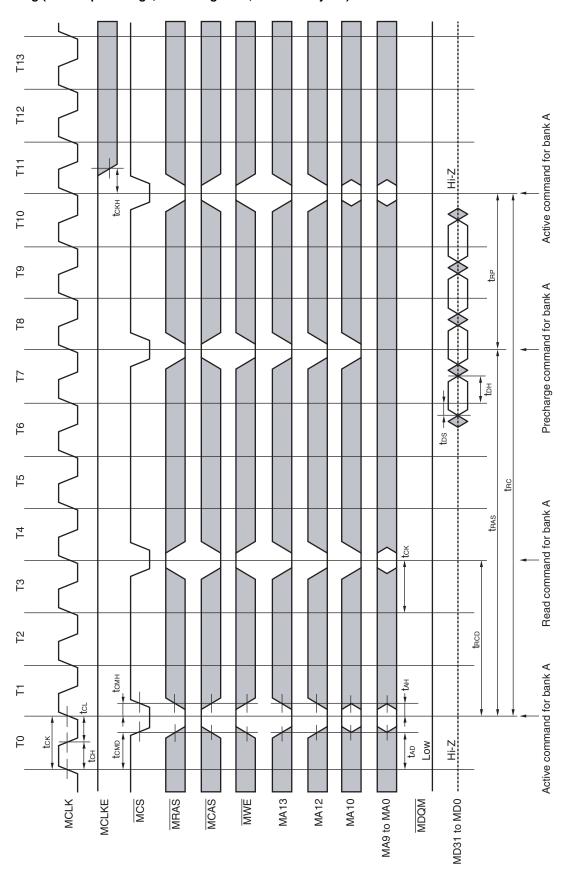

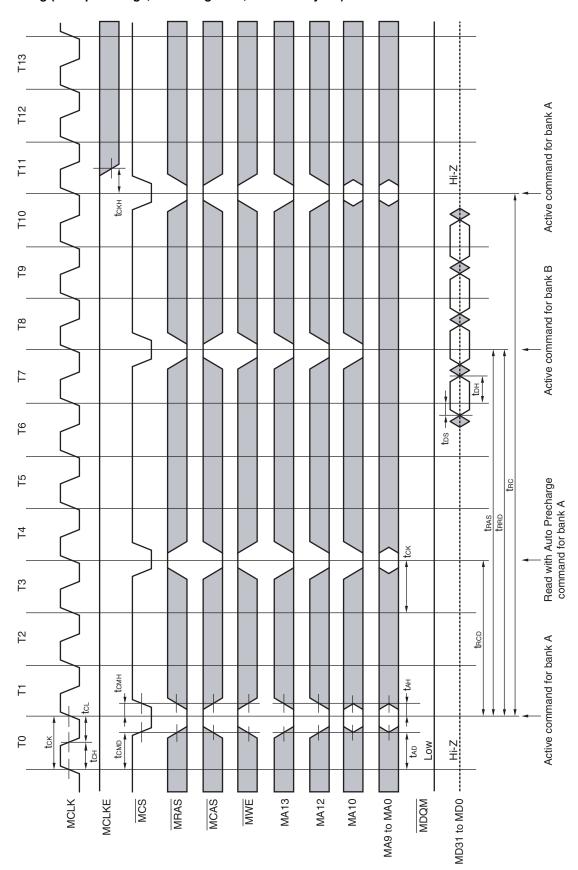

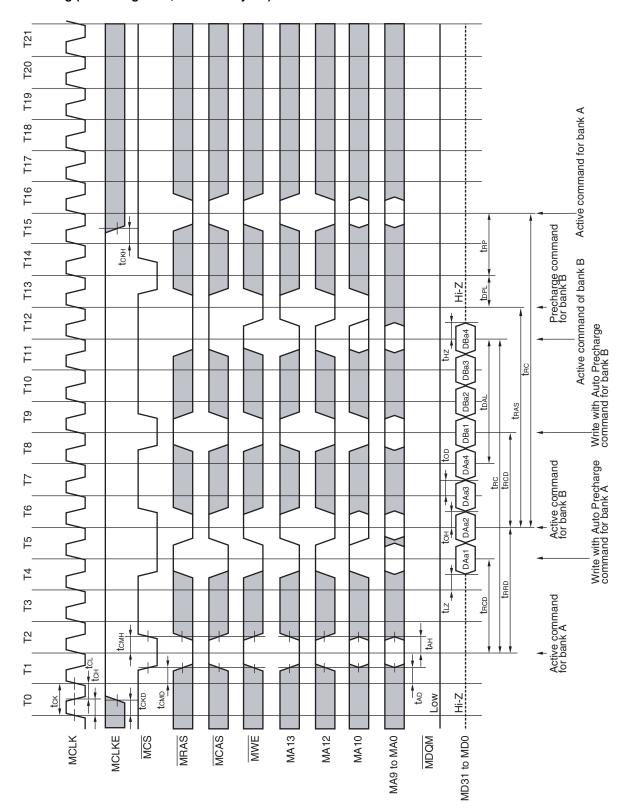

#### 2.6 SDRAM Interface

External memory is SDRAM. It is possible to use the following.

Memory Data bus width Quantity Use memory capacity 16 Mbit SDRAM 16 bits 2 32 Mbits 64 Mbit SDRAM 32 bits 1 64 Mbits 2 64 Mbit SDRAM 16 bits 128 Mbits 128 Mbit SDRAM 16 bits 2 128 Mbits 128 Mbit SDRAM 32 bits 1 128 Mbits

Table 2-6. Use Memory

The  $\mu$ PD61051/61052 preserves the part of the parameter that is necessary to generate the stream, entry video image, a video stream, an audio stream, a stream header, user data, and the instruction of the firmware at this memory.

This system uses only CAS latency = 3, burst length = 4.

When encode using time base corrector and/or displays local decoding picture, it needs equal to or more than 64 Mbits SDRAM.

When PAL encoding, it needs equal to or more than 64 Mbit SDRAM.

When transcoding, it needs equal to or more than 64 Mbit SDRAM.

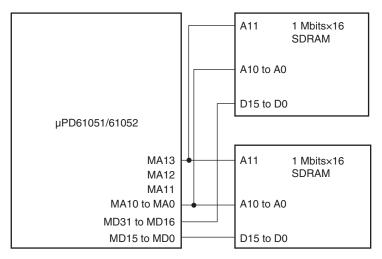

# 2.7 Memory Connection Diagram

Each memory connection is as follows.

Figure 2-14. Memory Connection Diagram (1/2)

# (a) 16 Mbit SDRAM by 2

Bank A: SDRAM address = 0x xxxx xxxx xxxxxB Bank B: SDRAM address = 1x xxxx xxxx xxxxxB

# (b) 64 Mbit SDRAM by 1

Bank A: SDRAM address = 00 xxxx xxxx xxxxxB Bank B: SDRAM address = 10 xxxx xxxx xxxxxB Bank C: SDRAM address = 01 xxxx xxxx xxxxxB Bank D: SDRAM address = 11 xxxx xxxx xxxxx

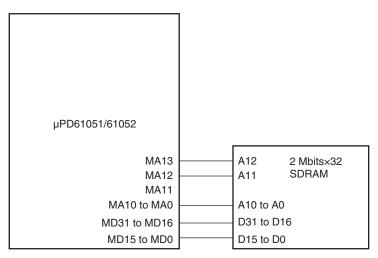

Figure 2-14. Memory Connection Diagram (2/2)

# (c) 64 Mbit SDRAM by 2 or 128 Mbit SDRAM by 2

Bank A: SDRAM address = 00 xxxx xxxx xxxxxB Bank B: SDRAM address = 10 xxxx xxxx xxxxxB Bank C: SDRAM address = 01 xxxx xxxx xxxxxB Bank D: SDRAM address = 11 xxxx xxxx xxxxx

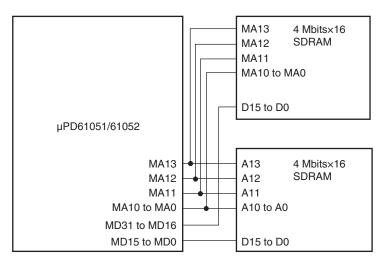

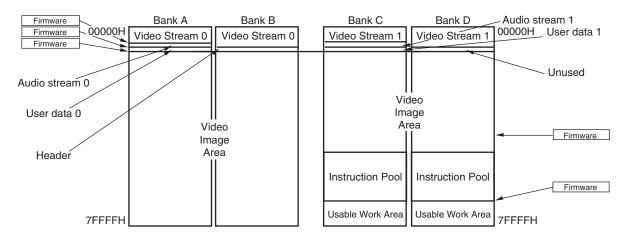

#### 2.8 Memory Map

Firmware sets memory map such as video image area and usable work area. Firmware cabinet (temporal buffered area) is the area which firmware does not use. Video Image area size is changed NTSC or PAL. Each area are changed by the firmware.

Figure 2-15. Memory Map (1/2)

# (a) 16 Mbit SDRAM by 2

# (b) Example for 64 Mbit SDRAM by 1

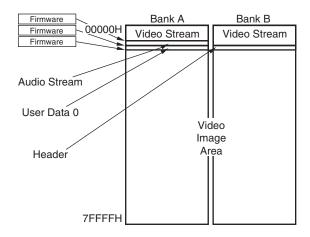

(c) Example for 64 Mbit SDRAM by 2 or 128 Mbit SDRAM by 2 Bank B Bank C 700000Н 00000H Video Stream Video Stream Unused

Figure 2-15. Memory Map (2/2)

| Tilliwale        | video Stream            | video Stream            | Unused                   | Unused                   |          |

|------------------|-------------------------|-------------------------|--------------------------|--------------------------|----------|

| Unused<br>Header | Ima                     | deo<br>age<br>ea        | Ima                      | deo<br>age ————ea        |          |

| Firmware         | Unused Instruction Pool | Unused Instruction Pool | Video Stream             | Video Stream             | 80000H   |

| Firmware         | Usable Work Area        | Usable Work Area        | Audio Stream User data 0 | Audio Stream User data 1 | Firmware |

| FFFFFH           |                         |                         |                          |                          | FFFFFH   |

## 3. SYSTEM INTERFACE REGISTER

This LSI corresponds to the various operation modes in exchange instruction of internal CPU from SDRAM to instruction RAM (iRAM).

This has 64 byte Registers. They are defined to common registers, interrupt registers and interrupt mask registers. When there is access in the same address from both of the internal CPU and the host CPU, the later data is left at the register.

Also, when the writing occurs to the same address at the same time about the common register, the data of the host CPU is left at the register

Figure 3-1. System Interface Register

# 3.1 Register Mapping (General Mapping)

| Address    | Bit7 | Bit6                | Bit5 | Bit4      | Bit3       | Bit2                | Bit1          | Bit0           | R/W |                      |

|------------|------|---------------------|------|-----------|------------|---------------------|---------------|----------------|-----|----------------------|

| 00H to 1FH |      |                     |      | Defined b | y firmware |                     |               |                | R/W |                      |

| 20H        | SI   | SSD                 | SDI  | MSD       | МІ         |                     | SDW           | SDR            | R/W | Download mode        |

| 21H        |      |                     |      |           |            | SA19 to             | o SA16        |                | R/W | Source address       |

| 22H        |      |                     |      | SA15      | to SA8     |                     |               |                | R/W | Source address       |

| 23H        |      |                     |      | SA7 t     | o SA0      |                     |               |                | R/W | Source address       |

| 24H        |      |                     |      |           |            |                     |               | DA16           | R/W | Destination address  |

| 25H        |      |                     |      | DA15      | to DA8     |                     |               |                | R/W | Destination address  |

| 26H        |      |                     |      | DA7 t     | o DA0      |                     |               |                | R/W | Destination address  |

| 27H        |      |                     |      |           |            | 7                   | TC18 to TC16  | 6              | R/W | Transfer data count  |

| 28H        |      |                     |      | TC15      | to TC8     |                     |               |                | R/W | Transfer data count  |

| 29H        |      |                     |      |           | R/W        | Transfer data count |               |                |     |                      |

| 2AH        | iCPU |                     |      |           |            |                     |               |                | R/W | Int. to internal CPU |

| 2BH        |      |                     |      |           |            | DMA-<br>ERR-M       | DMA-<br>RDY-M | DMA-<br>DONE-M | R/W | Interrupt mask0      |

| 2CH        |      |                     |      | Defined b | y firmware |                     |               |                | R/W | Interrupt mask1      |

| 2DH        |      |                     |      | Defined b | y firmware |                     |               |                | R/W | Interrupt mask2      |

| 2EH        |      |                     |      | Defined b | y firmware |                     |               |                | R/W | Interrupt mask3      |

| 2FH        |      |                     |      | Defined b | y firmware |                     |               |                | R/W | Interrupt mask4      |

| 30H        |      |                     |      |           |            | DMA-ERR             | DMA-RDY       | DMA-<br>DONE   | R/W | Interrupt0           |

| 31H        |      |                     |      | Defined b | y firmware |                     |               |                | R/W | Interrupt1           |

| 32H        |      |                     |      | Defined b | y firmware |                     |               |                | R/W | Interrupt2           |

| 33H        |      |                     |      | Defined b | y firmware |                     |               |                | R/W | Interrupt3           |

| 34H        |      | Defined by firmware |      |           |            |                     |               |                |     | Interrupt4           |

| 35H        |      |                     |      |           |            | iR                  | OM2 to iROM   | ΛО             | R/W | Mask ROM cycle       |

| 36H        |      |                     |      |           |            |                     | ISREQ         | OSVLD          | R/W | Port setup           |

| 37H to 3DH |      |                     |      |           |            |                     |               |                |     |                      |

| 3EH        |      |                     |      |           |            |                     | NBR           | ALL<br>RESET   | R/W | Reset                |

| 3FH        |      | •                   | 1    | TD7 t     | o TD0      | 1                   | 1             | 1              | R/W | Transfer data        |

## 3.2 Register Functions

## 3.2.1 Common register

| Address    | Bit7 | Bit6 | Bit5 | Bit4       | Bit3       | Bit2 | Bit1 | Bit0 | R/W |

|------------|------|------|------|------------|------------|------|------|------|-----|

| 00H to 1FH |      |      |      | Defined by | y firmware |      |      |      | R/W |

Each firmware defines these registers.

These registers are used to communicate with host CPU and internal CPU.

For the details of the register, refer to the application notebook.

The reset of the RESET pin or ALL RESET of the reset register initializes addresses 00H and 01H addresses to 0H. The original value of the other register is unsettled. It keeps a setting value before reset.

#### 3.2.2 Data transfer register

These registers are defined data transfer such as host CPU  $\rightarrow$  SDRAM, SDRAM  $\rightarrow$  host CPU, host CPU  $\rightarrow$  iRAM of internal CPU, SDRAM  $\rightarrow$  iRAM of internal CPU and instruction ROM  $\rightarrow$  iRAM of internal CPU.

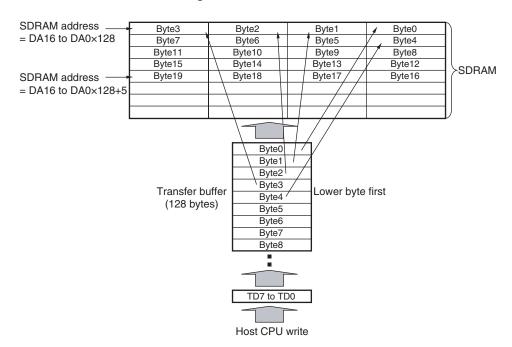

The host CPU transfers with SDRAM via had a transfer buffer of 128 bytes on this LSI.

The transfer with the instruction RAM becomes 4 bytes.

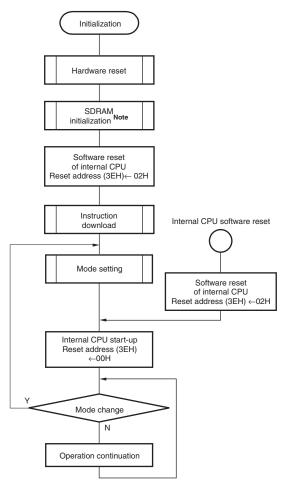

A transfer error occurs if the transfer mode register, source address register, destination address register, or transfer counter register is changed before releasing the transfer mode register following transfer completion after setting the transfer mode register and starting the transfer. When transferring data as follows: host CPU  $\rightarrow$  instruction RAM of internal CPU, host CPU  $\rightarrow$  SDRAM, SDRAM  $\rightarrow$  instruction RAM of internal CPU, instruction ROM  $\rightarrow$  SDRAM, instruction ROM  $\rightarrow$  instruction RAM of internal CPU, execute a software reset of the internal CPU (address 3EH  $\leftarrow$  02H) before transfer and release the reset after transfer.

## (1) Data transfer register

| Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | R/W |               |

|---------|------|------|------|------|------|------|------|------|-----|---------------|

| 20H     | SI   | SSD  | SDI  | MSD  | МІ   |      | SDW  | SDR  | R/W | Download mode |

| Bit | Field | Function                                        | Initial value |

|-----|-------|-------------------------------------------------|---------------|

| 7   | SI    | Host CPU→instruction RAM of internal CPU        | 0             |

|     |       | 0: Releasing of transfer, 1: Transfer Note      |               |

| 6   | SSD   | Host CPU→SDRAM                                  | 0             |

|     |       | 0: Releasing of transfer, 1: Transfer Note      |               |

| 5   | SDI   | SDRAM→instruction RAM of internal CPU           | 0             |

|     |       | 0: Releasing of transfer, 1: Transfer Note      |               |

| 4   | MSD   | Instruction ROM→SDRAM                           | 0             |

|     |       | 0: Releasing of transfer, 1: Transfer Note      |               |

| 3   | MI    | Instruction ROM→instruction RAM of internal CPU | 0             |

|     |       | 0: Releasing of transfer, 1: Transfer           |               |

| 2   |       | Reserved (set only 0)                           | 0             |

| 1   | SDW   | Host CPU→SDRAM                                  | 0             |

|     |       | 0: Releasing of transfer,1: Transfer            |               |

| 0   | SDR   | SDRAM→host CPU                                  | 0             |

|     |       | 0: Releasing of transfer, 1: Transfer           |               |

**Note** Set internal CPU reset (with Register 3EH←02H)

More than one bit cannot be set to 1 at the same time. It becomes a transfer error when writing at the transfer mode register while transferring. When canceling a transfer while transferring, it stops a transfer. At this time, the data in the transfer buffer becomes invalid. The transfer of SDR with once is to a maximum of 128 bytes. If host CPU stops the transfer, host CPU should operate transfer error handling.

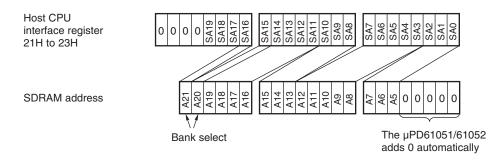

## (2) Source address register

| Address | Bit7 | Bit6        | Bit5 | Bit4 | Bit3           | Bit2   | Bit1 | Bit0           | R/W |  |  |  |

|---------|------|-------------|------|------|----------------|--------|------|----------------|-----|--|--|--|

| 21H     |      |             |      |      |                | SA19 t | R/W  | Source address |     |  |  |  |

| 22H     |      | SA15 to SA8 |      |      |                |        |      |                |     |  |  |  |

| 23H     |      |             |      | R/W  | Source address |        |      |                |     |  |  |  |

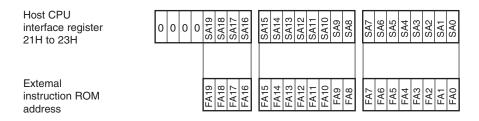

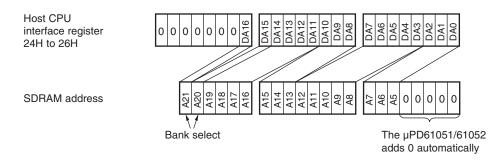

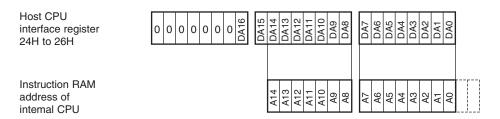

It sets the address of the data to transfer. It becomes effective in case of transfer from SDRAM or instruction ROM. Until it releases a transfer mode after setting a transfer mode register, it isn't possible to change. The transfer error occurs when rewriting this register before releasing a transfer mode. The relation with the address of SDRAM, external instruction ROM is shown in **Figure 3-2** and **3-3**. The addressing of SDRAM becomes a 32 address by 4-word unit (128 bytes).

The relation with the SDRAM bank and address is shown in **Table 3-1**.

Figure 3-2. Relation of Source Address and SDRAM Address

Figure 3-3. Relation of Source Address and External Instruction ROM Address

Table 3-1. Relation of SDRAM Bank and Address

| Memory              | Bank A             | Bank B             | Bank C             | Bank D             |

|---------------------|--------------------|--------------------|--------------------|--------------------|

| 16 Mbit SDRAM by 2  | 000000H to 07FFFFH | 200000H to 27FFFFH | -                  | -                  |

| 16 Mbit SDRAM by 1  | 000000H to 07FFFFH | 200000H to 27FFFFH | 100000H to 17FFFFH | 300000H to 37FFFFH |

| 64 Mbit SDRAM by 2  | 000000H to 0FFFFFH | 200000H to 2FFFFFH | 100000H to 1FFFFFH | 300000H to 3FFFFFH |

| 128 Mbit SDRAM by 1 |                    |                    |                    |                    |

| 128 Mbit SDRAM by 2 |                    |                    |                    |                    |

| 128 Mbit SDRAM by 1 | 000000H to 0FFFFFH | 200000H to 2FFFFFH | 100000H to 1FFFFFH | 300000H to 3FFFFFH |

## (3) Destination address register

| Address | Bit7 | Bit6 | Bit5 | Bit4                | Bit3                | Bit2 | Bit1 | Bit0 | R/W |                     |

|---------|------|------|------|---------------------|---------------------|------|------|------|-----|---------------------|

| 24H     |      |      |      |                     |                     |      |      | DA16 | R/W | Destination address |

| 25H     |      |      | R/W  | Destination address |                     |      |      |      |     |                     |

| 26H     |      |      |      | R/W                 | Destination address |      |      |      |     |                     |

It sets Destination address. It becomes effective in case of transfer to SDRAM or instruction RAM of internal CPU. It isn't possible to change until it cancels a transfer mode after setting a transfer mode register. It becomes a transfer error when rewriting before canceling a transfer mode. The relation of the address of SDRAM and instruction RAM of internal CPU is as in **Figure 3-4** and **3-5**. The addressing of SDRAM becomes a 32 address by 4-word unit (128 bytes).

Figure 3-4. Relation of Destination Address and SDRAM Address

Figure 3-5. Relation of Destination Address and Instruction ROM Address of Internal CPU

## (4) Transfer data counter register

| Address | Bit7 | Bit6            | Bit5 | Bit4 | Bit3 | Bit2 | Bit1        | Bit0 | R/W |                     |  |  |  |

|---------|------|-----------------|------|------|------|------|-------------|------|-----|---------------------|--|--|--|

| 27H     |      |                 |      |      |      | ٦    | ΓC18 to TC1 | 6    | R/W | Transfer data count |  |  |  |

| 28H     |      | TC15 to TC8 R/W |      |      |      |      |             |      |     |                     |  |  |  |

| 29H     |      | TC7 to TC0 R/W  |      |      |      |      |             |      |     |                     |  |  |  |

It sets the transfer data number of the bytes.

In case of transfer between host CPU and SDRAM, it sets the number of the transfer bytes by 4 bytes unit. In case of transfer from instructions ROM, SDRAM host CPU to the instruction RAM of internal CPU, it sets the number of the transfer bytes /4 by the 4 byte unit.

## (5) Transfer data register

| Address | Bit7 | Bit6       | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | R/W |  |  |

|---------|------|------------|------|------|------|------|------|------|-----|--|--|

| 3FH     |      | TD7 to TD0 |      |      |      |      |      |      |     |  |  |

This register is transfer data window.

Figure 3-6. SDRAM Write

#### **SDRAM** read

#### <1> Interrupt mask

Host CPU sets mask bit to interrupt mask register (2CH to 2FH) for the interrupt that needs a data transfer.

#### <2> Set source address

Host CPU sets the address of SDRAM to the source address register (21H to 23H) of the μPD61051/61052.

<3> Set the number (equal to or less than 128 bytes) of the data to read by 4 bytes unit

Host CPU sets the data number of the bytes to the transfer data counter register (27H to 29H) of the  $\mu$ PD61051/61052.

#### <4> Set the transfer of SDRAM $\rightarrow$ host CPU.

Host CPU sets 01H to the transfer mode register (20H) of the  $\mu$ PD61051/61052.

## <5> CINT interrupt (Interrupt pin)

## <6> Confirms that the interrupt factor and clear interrupt factor

Host CPU confirms that the interrupt register 0 (30H) of the  $\mu$ PD61051/61052 becomes 02H or 01H and clears writing a same value of the interrupt register 0 (30H) to the interrupt register 0 (30H) of the  $\mu$ PD61051/61052.

#### <7> Data read

Host CPU reads data from the number of times with the set number of bytes, the transfer data register (3FH) of the  $\mu$ PD61051/61052.

## <8> CINT interrupt (Interrupt pin)

## <9> Confirm the interrupt factor

Host CPU confirms that the interrupt register 0 (30H) of the  $\mu$ PD61051/61052 becomes 01H. (It clears a writing interrupt factor in 01H at the interrupt register 0 (30H) register of the  $\mu$ PD61051/61052.)

## <10> Release of SDRAM → host CPU mode

Host CPU clears a writing interrupt factor in 01H at the interrupt register 0 (30H) register of the  $\mu$ PD61051/61052 after setting 00H to the transfer mode register (20H) of the  $\mu$ PD61051/61052.

## <11> Release of interrupt mask

It releases the limitation on interrupt which set by <1>.

#### **SDRAM** write

## <1> Interrupt mask

Host CPU sets mask bit to interrupt mask register (2CH to 2FH) for the interrupt that needs a data transfer.

#### <2> Set destination address

Host CPU sets the address of SDRAM to the destination address register (24H to 26H) of the μPD61051/61052.

## <3> Set the number of the data to write by a 4 byte unit

Host CPU sets the data number of the bytes by 4 bytes unit to the transfer data counter register (27H to 29H) of the  $\mu$ PD61051/61052.

# <4> Set the transfer of host CPU $\rightarrow$ SDRAM

Host CPU sets 02H to the transfer mode register (20H) of the  $\mu$ PD61051/61052.

#### <5> Data write

Host CPU writes data to the transfer data register (3FH) of the  $\mu$ PD61051/61052 at times with more few 128 bytes or transfer data count register setting value.

## <6> CINT interrupt (Interrupt pin)

#### <7> Confirm the interrupt factor

When the number of the transfer data is less then 128 bytes, host CPU confirms that the interrupt register 0 (30H) of the  $\mu$ PD61051/61052 becomes 01H, and go to <9>.

## <8> Confirm that next data transfer prepare completed

Host CPU confirms that the interrupt register 0 (30H) of the  $\mu$ PD61051/61052 becomes 02H or 01H and clears a writing sane value of the interrupt register 0 (30H) to the interrupt register 0 (30H) of the  $\mu$ PD61051/61052. Return to <5> and next data write.

#### <9> Release of SDRAM $\rightarrow$ host CPU

Host CPU clears a writing interrupt factor in 01H at the interrupt register 0 (30H) register of the  $\mu$ PD61051/61052 after setting 00H to the transfer mode register (20H) of the  $\mu$ PD61051/61052.

#### <10> Release of interrupt mask

It releases the limitation on interrupt which is set by <1>.

## <11> In the case of an interrupt to internal CPU, it is necessary

Host CPU sets a data bank number and the number of the bytes to the address that defined with the firmware. It sets 01H to the 2AH address of the  $\mu$ PD61051/61052 and it notifies an interrupt to internal CPU.

## 3.2.3 Internal CPU interrupt register

| Addre | ss Bit | it7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0     | R/W |                      |

|-------|--------|-----|------|------|------|------|------|------|----------|-----|----------------------|

| 2AH   |        |     |      |      |      |      |      |      | iCPU-INT | R/W | Int. to internal CPU |

Host CPU set interrupt to internal CPU. Internal CPU clears this bit after interrupt operation. The reset of the RESET pin or ALL RESET of the reset register initializes this address to 0H.

#### 3.2.4 Interrupt mask register

| Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3            | Bit2          | Bit1          | Bit0           | R/W |                 |

|---------|------|------|------|------|-----------------|---------------|---------------|----------------|-----|-----------------|

| 2BH     |      |      |      |      |                 | DMA-ERR<br>-M | DMA-RDY<br>-M | DMA-DON<br>E-M | R/W | Interrupt mask0 |

| 2CH     |      |      |      | R/W  | Interrupt mask1 |               |               |                |     |                 |

| 2DH     |      |      |      | R/W  | Interrupt mask2 |               |               |                |     |                 |

| 2EH     |      |      |      | R/W  | Interrupt mask3 |               |               |                |     |                 |

| 2FH     |      |      |      | R/W  | Interrupt mask4 |               |               |                |     |                 |

These registers are interrupt masks for next interrupt. Interrupt mask can be set bit by bit. When setting an interrupt mask, CINT does not become high even if the interrupt register becomes 1.

The reset of the RESET pin or ALL RESET of the reset register initializes this address to 0H.

## 3.2.5 Download interrupt register

| Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2    | Bit1    | Bit0    | R/W |            |

|---------|------|------|------|------|------|---------|---------|---------|-----|------------|

| 30H     |      |      |      |      |      | DMA-ERR | DMA-RDY | DMA-DON | R/W | Interrupt0 |

|         |      |      |      |      |      |         |         | Е       |     |            |

It is set for 1 when the interrupt factor occurs.

The interrupt bit clears when host CPU writes to this register after the interrupt processing.

The reset of the RESET pin or ALL RESET of the reset register initializes this address to 0H.

Clear processing continues until interrupt registers is cleared.

| Bit    | Field    | Function                     | Initial value |

|--------|----------|------------------------------|---------------|

| 7 to 3 |          | Reserved (set 0)             |               |

| 2      | DMA-ERR  | Data transfer error          | 0             |

|        |          | 0: Normal, 1: Error          |               |

| 1      | DMA-RDY  | Data transfer prepared       | 0             |

|        |          | 0: Normal, 1: Transfer       |               |

| 0      | DMA-DONE | Data transfer ended          | 0             |

|        |          | 0: Normal, 1: Transfer ended |               |

It outputs DMA-RDY or DMA-DONE every 128-byte transfer. DMA-DONE is output when the transfer ends.

## 3.2.6 Interrupt register

| Address | Bit7 | Bit6                | Bit5 | Bit4      | Bit3       | Bit2 | Bit1 | Bit0 | R/W |            |  |  |

|---------|------|---------------------|------|-----------|------------|------|------|------|-----|------------|--|--|

| 31H     |      |                     |      | Defined b | y firmware |      |      |      | R/W | Interrupt1 |  |  |

| 32H     |      | Defined by firmware |      |           |            |      |      |      |     |            |  |  |

| 33H     |      | Defined by firmware |      |           |            |      |      |      |     |            |  |  |

| 34H     |      | Defined by firmware |      |           |            |      |      |      |     |            |  |  |

It is set for 1 when the interrupt factor occurs.

The interrupt bit clears when host CPU writes 1 in the bit of the interrupt after the interrupt processing.

When the other interrupt (which isn't masked) is set to 1 when clearing a interrupt, CINT becomes high 1  $\mu$ s later.

The reset of the RESET pin or ALL RESET of the reset register initializes this address to 0H.

Clear processing continues until interrupt registers is cleared.

| Address | Bit    | Field | Function                | Initial value |

|---------|--------|-------|-------------------------|---------------|

| 31H to  | 7 to 0 |       | Firmware define         | 0H            |

| 34H     |        |       | 0: Normal, 1: Interrupt |               |

## 3.2.7 Reset register

| Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  | R/W |      |

|---------|------|------|------|------|------|------|------|-------|-----|------|

| 3EH     |      |      |      |      |      |      | NBR  | ALL   | R/W | Rese |

|         |      |      |      |      |      |      |      | RESET |     |      |