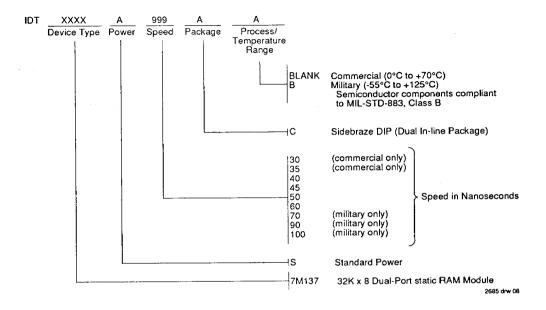

# 32K X 8 CMOS DUAL-PORT STATIC RAM MODULE

PIN NAMES

Vcc

**GND**

CSL

R/WL

ŌĒL

NC

A0L-14L

1/OoL-7L

#### **FEATURES:**

- · High-density 256K CMOS Dual-Port static RAM module

- · 32K x 8 organization

- · Fully asynchronous read/write operation from either port

- · Fast access time

- commercial: 30ns (max.)

- military: 40ns (max.)

- · Low power consumption

- Dual Vcc and GND pins for maximum noise immunity

- · Inputs and outputs directly TTL-compatible

- Single 5V (±10%) power supply

#### **DESCRIPTION:**

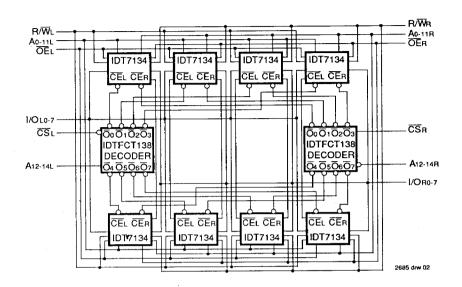

The IDT7M137 is a 256K high-speed CMOS Dual-Port static RAM module constructed on a multi-layered ceramic substrate using eight IDT7134 dual-port static RAMs in leadless chip carriers. The full 32K bytes of dual-port static RAM are directly addressable by utilization of the two on-board IDT54/IDT74FCT138 decoder circuits that interpret

the higher order addresses AL12-14 and AR12-14 to select one of the eight 4K x 8 dual-port static RAMs. Extremely high speeds are achieved in this fashion due to the use of the IDT7134 dual-port static RAM, fabricated in IDT's high-performance CEMOS™ technology.

The IDT7M137 provides two ports with separate control, address and I/O pins that permit independent, asynchronous access for reads or writes to any location in the memory. The IDT7M137 is designed to be used in systems where on-chip hardware port arbitration is not needed. It is the user's responsibility to ensure data integrity when simultaneously accessing the same memory location from both ports.

The IDT7M137 is available with access times as fast as 30ns commercial and 40ns military temperature range. The module fits into a 58-pin sidebrazed DIP (Dual In-line Package).

All IDT7M137 military module semiconductor components are manufactured in compliance to the latest revision of MIL-STD-883, Class B, making them ideally suited to applications demanding the highest level of performance and reliability.

RIGHT PORT

Vcc

GND

CSR

R/WR

ŌĒR

NC

A0R-14R

I/OoR-7R

| DIN | CONF | CHD   | ATIO    | M(1) |

|-----|------|-------|---------|------|

| PIN | CONF | אנונו | A 111.3 |      |

|--|

2685 drw 01

DIP TOP VIEW

NOTE:

For module dimensions, please refer to module drawing M12 in the packaging section.

CEMOS is a trademark of Integrated Device Technology, Inc.

| MILITARY AND COMMERCIAL T | EMPERATURE RANGES |

|---------------------------|-------------------|

|---------------------------|-------------------|

SEPTEMBER 1990

NAMES

Read/Write Enable

Data Input/Output

2685 tbl 01

Output Enable

No Connect

Power

Ground

Address

Chip Select

@1990 Integrated Device Technology, Inc

8.3-1

DSC-7024/1

#### **FUNCTIONAL DESCRIPTION:**

The IDT7M137 provides two ports with separate controls, address and I/O that permit independent access for reads or writes to any location in memory. The IDT7M137 has an automatic power down feature controlled by  $\overline{CS}$ . The  $\overline{CS}$  controls on-chip power down circuitry that permits

the respective port to go into a standby mode when not selected ( $\overline{CS}$  high). When a port is enabled, access to the entire memory array is permitted. Each port has its own Output Enable control ( $\overline{OE}$ ). In the read mode, the port's  $\overline{OE}$  turns on the output drivers when set LOW.

### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Rating                               | Commercial   | Military     | Unit |

|--------|--------------------------------------|--------------|--------------|------|

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to +7.0 | -0.5 to +7.0 | V    |

| TA     | Operating<br>Temperature             | 0 to +70     | -55 to +125  | °C   |

| TBIAS  | Temperature<br>Under Bias            | -55 to +125  | -65 to +135  | °C   |

| Tstg   | Storage<br>Temperature               | -55 to +125  | -65 to +150  | °C   |

| lout   | DC Output<br>Current                 | 50           | 50           | mA   |

2685 tbl 02

2685 tol 09

### RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade      | Ambient<br>Temperature | GND | Vcc        |

|------------|------------------------|-----|------------|

| Military   | -55°C to +125°C        | oV  | 5.0V ± 10% |

| Commercial | 0°C to +70°C           | 0V  | 5.0V ± 10% |

2685 tbl 03

#### RECOMMENDED DC **OPERATING CONDITIONS**

| Symbol | Parameter          | Min.                | Тур. | Max. | Unit       |

|--------|--------------------|---------------------|------|------|------------|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5  | ٧          |

| GND    | Supply Voltage     | 0                   | 0    | 0    | ٧          |

| VIH    | Input High Voltage | 2.2                 | _    | 6.0  | ٧          |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> | _    | 0.8  | ٧          |

| IOTE:  |                    |                     |      |      | 2685 tol 0 |

1. VIL = -3.0V for pulse width less than 20ns.

CAPACITANCE (1)  $(TA = +25^{\circ}C, f = 1, 0MHz)$

| Symbol | Parameter          | Conditions | Тур. | Unit |

|--------|--------------------|------------|------|------|

| Cout   | Output Capacitance | VIN = OV   | 120  | pF   |

| CIN    | Input Capacitance  | Vout = 0V  | 50   | рF   |

NOTE:

### 1. This parameter is guaranteed by design, but not tested.

## DC ELECTRICAL CHARACTERISTICS (4)

$(Vcc = 5.0V \pm 10\%, Ta = -55^{\circ}C \text{ to } +125^{\circ}C \text{ and } 0^{\circ}C \text{ to } +70^{\circ}C)$

|             |                                                   |                                                                  |                     | IDT7M137 | i          |      |  |  |

|-------------|---------------------------------------------------|------------------------------------------------------------------|---------------------|----------|------------|------|--|--|

| Symbol      | Parameter                                         | Test Conditions                                                  | Min.                | Тур.     | Max.       | Unit |  |  |

| <b>İ</b> LI | Input Leakage Current                             | Vcc = 5.5V, Vin = 0V to Vcc                                      |                     |          | 20         | μΑ   |  |  |

| llo         | Output Leakage Current                            | CS = VIH, VOUT = 0V to VCC                                       |                     |          | 20         | μΑ   |  |  |

| ViH         | Input High Voltage                                |                                                                  | 2.2                 |          | 6.0        | ٧    |  |  |

| VIL         | Input Low Voltage                                 |                                                                  | -1.0 <sup>(2)</sup> |          | 0.8        | ٧    |  |  |

| lcc         | Dynamic Operating Current<br>(Both Ports Active)  | CS= VIL, Outputs Open                                            |                     | 275      | 730        | mA   |  |  |

| ISB         | Standby Current<br>(Both Ports Standby)           | CSL and CSR ≥ VIH, VCC = Max.,<br>Both Ports Outputs Open        | _                   | 560      | mA         |      |  |  |

| ISB1        | Standby Current<br>(One Port Standby)             | CSL or CSR ≥ VIH, Vcc = Max.,<br>Active Port Outputs Open        |                     | 225      | 650        | mA   |  |  |

| ISB2        | Full Standby Current<br>(Both Ports Full Standby) | Both Ports CSL and CSR ≥ Vcc -0.2V ViN ≥ Vcc -0.2V or ViN ≤ 0.2V | _                   | 8        | 240(3)     | mA   |  |  |

| VOL         | Output Low Voltage                                | IOL = 8mA<br>IOL = 10mA                                          | =                   |          | 0.4<br>0.5 | V    |  |  |

| Voн         | Output High Voltage                               | IOH = -4mA                                                       | 2.4                 |          |            | V    |  |  |

2685 tbl 05

#### NOTES:

- 1. Vcc = 5V, TA = +25°C

- VIL min. = -3.0V for pulse width less than 30ns.

- 3. ISB2 max, of IDTM137 at commercial temperature = 150mA.4.

For tAA = 30, 35, 40, 45ns versions all DC parameters are preliminary only.

8.3-3

NOTE: 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

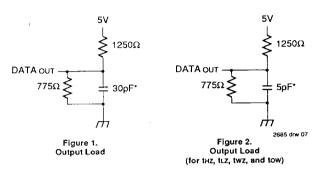

#### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V           |

|-------------------------------|-----------------------|

| Input Rise/Fall Times         | 10ns                  |

| Input Timing Reference Levels | 1.5V                  |

| Output Reference Levels       | 1.5V                  |

| Output Load                   | See Figures 1,2 and 3 |

2685 tol 08

\* Including scope and jig.

#### **AC ELECTRICAL CHARACTERISTICS**

$(Vcc = 5.0V + 10\%. TA = -55^{\circ}C \text{ to } + 125^{\circ}C \text{ and } 0^{\circ}C \text{ to } +70^{\circ}C)$

|          |                                   |      | 37530 |      | 37\$35   |          | 7540 | 7M13     | 37545 |     |

|----------|-----------------------------------|------|-------|------|----------|----------|------|----------|-------|-----|

|          |                                   | 4.   |       |      | l. Only) |          |      |          |       | l   |

| Symbol   | Parameter                         | Min. | Max.  | Min. | Max.     | Min.     | Max. | Min.     | Max.  | Uni |

| READ CY  | /CLE                              |      |       |      |          |          |      |          |       |     |

| trc      | Read Cycle Time                   | 30   |       | 35   |          | 40       |      | 45       |       | ns  |

| taa      | Address Access Time               |      | 30    | _    | 35       |          | 40   |          | 45    | ns  |

| tacs     | Chip Select Access Time           |      | 30    |      | 35       |          | 40   |          | 45    | ns  |

| toE      | Output Enable Access Time         |      | 15    |      | 20       |          | 25   |          | 30    | ns  |

| ton      | Output Hold From Address Change   | 0    |       | 0    |          | 0        |      | 0        |       | ns  |

| tCLZ (1) | Chip Select to Output in Low Z    | 5    |       | 5    |          | 5        |      | 5        |       | ns  |

| tCHZ(1)  | Chip Select to Output in High Z   |      | 10    |      | 15       |          | 15   |          | 25    | ns  |

| toHZ(1)  | Output Enable to Output in High Z |      | 10    |      | 15       | <u> </u> | 15   | <u></u>  | 25    | ns  |

| tOLZ (1) | Output Enable to Output in Low Z  | 5    | _     | 5    |          | 5        |      | 5        |       | ns  |

| tPU(1)   | Chip Select to Power Up Time      | 0    |       | 0    |          | 0        |      | 0        |       | ns  |

| tPD(1)   | Chip Deselect to Power Down Time  |      | 50    | _    | 50       |          | 50   | <u>L</u> | 60    | ns  |

| WRITE C  | YCLE                              |      |       |      |          |          |      |          |       |     |

| twc      | Write Cycle Time                  | 30   | _     | 35   |          | 40       |      | 45       |       | ns  |

| tcw      | Chip Select to End of Write       | 25   |       | 30   |          | 35       |      | 40       |       | ns  |

| taw      | Address Valid to End of Write     | 25   |       | 30   |          | 35       |      | 40       |       | ns  |

| tas      | Address Set-up Time               | 0    |       | 0    |          | 0        |      | 0        |       | ns  |

| twp      | Write Pulse Width                 | 20   |       | 25   |          | 30       |      | 40       |       | ns  |

| twr      | Write Recovery Time               | 0    | _     | 0_   |          | 0        |      | 0        |       | ns  |

| tDW      | Data Valid to End of Write        | 20   |       | 20   |          | 22       |      | 22       |       | n:  |

| tDH      | Data Hold Time                    | 0    |       | 0    |          | 0        |      | 0        |       | ns  |

| toHZ(1)  | Output Enable to Output in High Z |      | 10    |      | 15       |          | 15   |          | 20_   | ns  |

| twHZ(1)  | Write Enabled to Output in High Z |      | 10    | I —  | 15       |          | 15   |          | 20    | l n |

| tow(1)   | Output Active From End of Write   | 0    |       | 0    | _        | 0        |      | 0        |       | n:  |

NOTES:

2685 tol 06

<sup>1.</sup> This parameter is guaranteed by design, but not tested.

### **AC ELECTRICAL CHARACTERISTICS**

|          |                                   | IDTM: | 137555 | IDTM: | 37560 |               | 37570         |               |               | IDTM13          |      | l        |

|----------|-----------------------------------|-------|--------|-------|-------|---------------|---------------|---------------|---------------|-----------------|------|----------|

| Symbol   | Parameter                         | Min.  | Max.   | Min.  | Max.  | (Mil.<br>Min. | Only)<br>Max. | (Mil.<br>Min. | Only)<br>Max. | (Mil. (<br>Min. | Max. | Unit     |

| READ CY  | CLE                               |       |        |       |       |               |               |               |               | <u> </u>        |      |          |

| tRC      | Read Cycle Time                   | 55    |        | 60    |       | 70            |               | 90            | _             | 100             | _    | ns       |

| taa      | Address Access Time               | 1     | 55     | _     | 60    | _             | 70            | -             | 90            | I —             | 100  | ns       |

| tacs     | Chip Select Access Time           | 1 -   | 55     | T —   | 60    | _             | 70            | _             | 90            |                 | 100  | ns       |

| toe      | Output Enable Access Time         | T -   | 35     | _     | 35    | _             | 40            |               | 40            |                 | 40   | ns       |

| ton      | Output Hold From Address Change   | 0     |        | 0     |       | . 0           |               | 10            | _             | 10              |      | ns       |

| tcLZ (1) | Chip Select to Output in Low Z    | 15    | _      | 15    | -     | 15            |               | 15            |               | 15              | _    | ns       |

| tcHZ (1) | Chip Select to Output in High Z   |       | 35     |       | 40    | _             | 40            |               | 40            |                 | 40   | ns       |

| tolz (1) | Output Enable to Output in Low Z  | 5     | _      | 5     | _     | 5             | _             | 5             |               | 5               |      | ns       |

| tonz (1) | Output Enable to Output in High Z | 1 -   | 30     | _     | 35    | <u> </u>      | 40            |               | 40            |                 | 40   | ns       |

| tpu (1)  | Chip Select to Power Up Time      | 0     | _      | 0     |       | 0             |               | 0             |               | 0               |      | ns       |

| tPD (1)  | Chip Deselect to Power Down Time  |       | 60     |       | 60    |               | 60            | I —           | 60            |                 | 60   | ns       |

| WRITE C  | YCLE                              |       |        |       |       |               |               |               |               |                 |      | - T F. , |

| twc      | Write Cycle Time                  | 55    | _      | 60    |       | 70            |               | 90            |               | 100             |      | ns       |

| tcw      | Chip Select to End of Write       | 50    |        | 55    |       | 60            |               | 80            |               | 90_             |      | ns       |

| taw      | Address Valid to End of Write     | 50    |        | 55    |       | 60            |               | 80            |               | 90              |      | ns       |

| tas      | Address Set-up Time               | , 0   |        | 0.    | _     | 0             | _             | 0             |               | 0               |      | ns       |

| twp      | Write Pulse Width                 | 45    |        | 50    |       | 55            |               | 70            |               | 80              |      | ns       |

| twn      | Write Recovery Time               | 5     |        | 5     |       | 5             |               | 10            |               | 10              |      | ns       |

| tDW      | Data Valid to End of Write        | 25    |        | 30    |       | 35            | ··· —         | 45            |               | 50              |      | ns       |

| tDH      | Data Hold Time                    | - 5   |        | 5     |       | 5             |               | 10            |               | 10              |      | ns       |

| tonz (1) | Output Enable to Output in High Z | _     | 35     | _     | 40    | _             | 40            |               | 40            |                 | 50   | ns       |

| twHZ (1) | Write Enabled to Output in High Z | 0     | 35     | 0     | 40    | 0             | 40            | 0             | 40            | 0               | 50   | ns       |

| tow (1)  | Output Active From End of Write   | 0     |        | 0     | _     | 0             | _             | 0             |               | 0               | -    | ns       |

NOTES:

5

This parameter is guaranteed by design, but not tested.

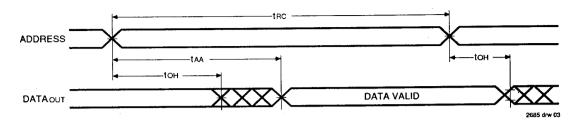

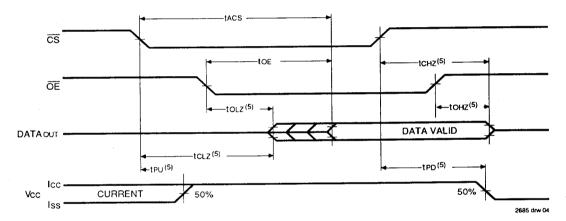

## TIMING WAVEFORM OF READ CYCLE NO. 1, EITHER SIDE $^{(1,\,2,\,4)}$

## TIMING WAVEFORM OF READ CYCLE NO. 2, EITHER SIDE (1, 3)

#### NOTES:

- R/W is High for Read Cycles.

- Device is continuously enabled,  $\overline{CS} = VIL$

- Addresses valid prior to or coincident with  $\overline{CS}$  transition low.  $\overline{OE} = V_{IL}$ .

- 5. This parameter is guaranteed by design, but not tested.

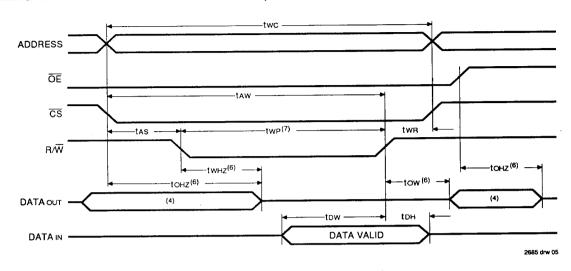

## TIMING WAVEFORM OF WRITE CYCLE NO. 1 (R/W CONTROLLED TIMING)1, 2, 3, 7)

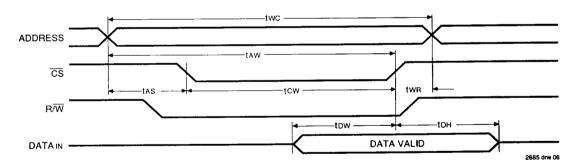

## TIMING WAVEFORM OF WRITE CYCLE NO. 2 (CS CONTROLLED TIMING) (1, 2, 3, 5)

#### NOTES:

- RVW or CS must be high during all address transitions.

- A write occurs during the overlap (twe) of a low CS and a low R/W.

twn is measured from the earlier of CS or R/W going high to the end of write cycle.

- 4. During this period, I/O pins are in the output state, and input signals must not be applied.

- 5. If the CS low transition occurs simultaneously with or after the R/W low transition, the outputs remain in a high impedance state.

- 6. Transition is measured ±200mV from steady state with a 5pF load (including scope and ijg). This parameter is guaranteed by design, but not tested.

7. During a P/W controlled write cycle, write pulse (twp) > (twz + tbw) to allow the I/O drivers to turn off and data to be placed on the bus for the required tow. If OE is high during a RW controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.