# A64E06161

## Preliminary

## 1M X 16 Bit Low Voltage Super RAM

## Document Title

## 1M X 16 Bit Low Voltage Super RAM

## **Revision History**

| Rev. No. | <u>History</u>                                            | Issue Date        | <u>Remark</u> |

|----------|-----------------------------------------------------------|-------------------|---------------|

| 0.0      | Initial issue                                             | October 12, 2003  | Preliminary   |

| 0.1      | Change VCC range and VCCQ range                           | November 30, 2004 |               |

|          | Change page access time from 20ns to 25ns                 |                   |               |

|          | Change operation current (Icc1) from 25mA to 15mA(-70)    |                   |               |

|          | Change operation current (Icc1) from 20mA to 12mA(-85)    |                   |               |

|          | Change standby current (Ise1) from 80uA to 100uA          |                   |               |

|          | Delete reduce memory size 16M, partial array refresh 16M  |                   |               |

|          | Change operation current (Icc2) form 5mA to 3mA(-70, -85) |                   |               |

|          | Change PAR current 12Mb=90uA, 8Mb=80uA, 4Mb=70uA          |                   |               |

|          | Change TCR current +85°C=100uA +70°C=90uA                 |                   |               |

|          | Change TCR current +45°C=85uA +15°C=75uA                  |                   |               |

# A64E06161

## Preliminary

## 1M X 16 Bit Low Voltage Super RAM

### Features

- Operating voltage: VCC: 1.7V to 1.95V VCCQ: 1.7V to VCC

- Access times: tAA = 70ns (max.)

- Page Access times: tPAA = 25ns (max)

- Current: A64E06161 series: Operating Current (lcc1) : 15mA (max.) Standby Current (lsb1) : 100uA (max)

Dean Dewor Dewo Standby Current (lsc) : 1

- Deep Power Down Standby Current (Izz) : 10µA (max.) 4-word page length

#### **General Description**

The A64E06161 is a low operating current 16,777,216-bit super RAM organized as 1,048,576 word by 16bit and operated on low power supply voltage from 1.7V to 1.95V. It is built using AMIC's high performance CMOS DRAM process.

Using hidden refresh technique, the A64E06161 provides a compatible asynchronous interface and data can be read in 4-word page mode for fast access times. The A64E06161 has an internal register named the Configuration Register

#### **Pin Configuration**

Support 4 distinct operation modes for reducing standby power : Deep Power Down (DPD) mode

Reduce Memory Size (RMS) mode (4M, 8M, 12M) Partial Array Refresh (PAR) mode (4M,8M,12M) Temperature Compensated Refresh (TCR) mode

- Industrial operating temperature range: -25°C to +85°C for I

- Available in 48-ball Mini BGA (6X8) package.

(CR) that controls the operation. The A64E06161 is designed for reducing current consumption during hidden self refresh and operating through following mode: Deep Power Down (DPD) mode, Reduce Memory Size (RMS) mode, Partial Array Refresh (PAR) mode and Temperature Compensated refresh (TCR) mode.

This A64E06161 is suited for low power application such as mobile phone and PDA or other battery-operated handheld device.

|   | 1     | 2     | 3   | 4   | 5    | 6    |

|---|-------|-------|-----|-----|------|------|

| A | LB    | ŌĒ    | A0  | A1  | A2   | ZZ   |

| В | I/O8  | ΗB    | A3  | A4  | CE   | I/O₀ |

| С | I/O9  | I/O10 | A5  | A6  | I/O1 | I/O2 |

| D | VSSQ  | I/O11 | A17 | A7  | I/O3 | VCC  |

| Е | VCCQ  | I/O12 | NC  | A16 | I/O4 | VSS  |

| F | I/O14 | I/O13 | A14 | A15 | I/O5 | I/O6 |

| G | I/O15 | A19   | A12 | A13 | WE   | I/O7 |

| Н | A18   | A8    | A9  | A10 | A11  | NC   |

#### ■ Mini BGA (6X8) Top View

#### A64E06161G

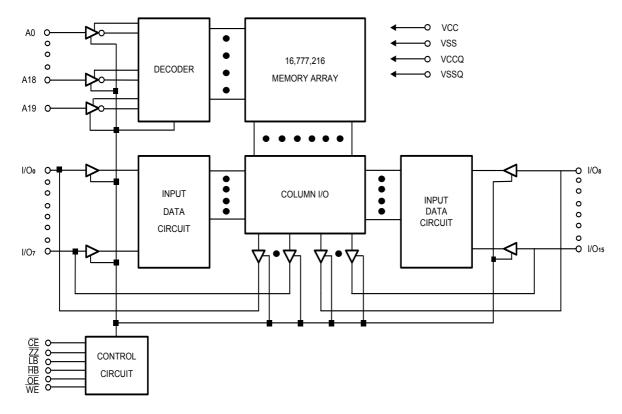

## **Block Diagram**

#### **Pin Description**

| Symbol       | Description                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|

| A0 - A19     | Address Inputs                                                                                                                         |

| CE           | Chip Enable Input                                                                                                                      |

| ZZ           | Sleep Enable Input<br>(When $\overline{ZZ}$ is low, the CR register can be<br>loaded or the device can enter DPD mode or<br>PAR mode). |

| I/O0 - I/O15 | Data Input/Outputs                                                                                                                     |

| WE           | Write Enable Input                                                                                                                     |

| ĹВ           | Byte Enable Input (I/O₀ to I/O⁊)                                                                                                       |

| HB           | Byte Enable Input (I/O <sub>8</sub> to I/O <sub>15</sub> )                                                                             |

| ŌĒ           | Output Enable Input                                                                                                                    |

| VCC          | Power                                                                                                                                  |

| VSS          | Ground                                                                                                                                 |

| VCCQ         | Provide isolated power to I/O for improved noise immunity                                                                              |

| VSSQ         | Provide isolated / Ground to I/O for improved noise immunity                                                                           |

| NC           | No Connection or VSSQ                                                                                                                  |

### **Recommended DC Operating Conditions** (T<sub>A</sub> = $0^{\circ}$ C to + $70^{\circ}$ C or $-25^{\circ}$ C to $85^{\circ}$ C)

| Symbol | Parameter               | Min. | Max.       | Unit |

|--------|-------------------------|------|------------|------|

| VCC    | Supply Voltage          | 1.7  | 1.95       | V    |

| VSS    | Ground                  | 0    | 0          | V    |

| VCCQ   | Supply Voltage I/O only | 1.7  | VCC        | V    |

| VSSQ   | Ground I/O only         | 0    | 0          | V    |

| Vih    | Input High Voltage      | 1.4  | VCCQ + 0.2 | V    |

| VIL    | Input Low Voltage       | -0.2 | +0.4       | V    |

| CL     | Output Load             | -    | 30         | pF   |

#### **Absolute Maximum Ratings\***

| VCC to VSS                 | 0.3V to VCC+0.3V    |

|----------------------------|---------------------|

| VCCQ to VSSQ               | 0.3V to VCCQ+0.3V   |

| IN, IN/OUT Volt to GND     | 0.3V to VCCQ + 0.3V |

| Storage Temperature, Tstg. | 55°C to +125°C      |

| Power Dissipation, PT      | 0.7W                |

| Soldering Temp. & Time     | 260°C, 10 sec       |

#### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol | Parameter                       | -70      |      | -85      | -85  |    | Conditions                                                                                                                                                                |

|--------|---------------------------------|----------|------|----------|------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                 | Min.     | Max. | Min.     | Max. |    |                                                                                                                                                                           |

| ப      | Input Leakage Current           | -        | 1    | -        | 1    | μA | VIN = GND to VCCQ                                                                                                                                                         |

| ILO    | Output Leakage<br>Current       | -        | 1    | -        | 1    | μA | $\overline{CE} = V_{IH} \text{ or } \overline{ZZ} = V_{IL} \text{ or}$<br>$\overline{OE} = V_{IH} \text{ or } \overline{WE} = V_{IL}$<br>$V_{IVO} = GND \text{ to } VCCQ$ |

| lcc1   | Dynamic Operating               | -        | 15   | -        | 12   | mA |                                                                                                                                                                           |

| lcc2   | Current                         | -        | 3    | -        | 3    | mA | $\overline{CE} = V_{IL}, \overline{ZZ} = V_{IH} \qquad V_{IH}$ $= VCCQ, V_{IL} = 0V,$ $f = 1MHz, I_{IVO} = 0mA$                                                           |

| ISB1   | Standby Power<br>Supply Current | -        | 100  | -        | 100  | μΑ | $\label{eq:cell} \begin{split} \overline{CE} &\geq VCCQ - 0.2V \\ \overline{ZZ} &\geq VCCQ - 0.2V \\ V_{IN} &\geq 0V \end{split}$                                         |

| Vol    | Output Low Voltage              | -        | 0.2  | -        | 0.2  | V  | loL = 0.2 mA                                                                                                                                                              |

| Vон    | Output High Voltage             | VCCQ-0.2 | -    | VCCQ-0.2 | -    | V  | loн = -0.2mA                                                                                                                                                              |

### **Deep Power Down Specifications and Conditions**

| Symbol | Description     | Conditions                                                                         | Тур. | Max. | Units |

|--------|-----------------|------------------------------------------------------------------------------------|------|------|-------|

| lzz    | Deep Power-Down | $V_{IN} = VCCQ \text{ or } 0V; +25^{\circ}C$<br>$\overline{ZZ} = LOW$<br>CR[4] = 0 |      | 10   | μΑ    |

### **Partial Array Refresh Specifications Conditions**

| Symbol | Description                      | Conditions                                              | Density | Array<br>Partition | Тур. | Max. | Units |

|--------|----------------------------------|---------------------------------------------------------|---------|--------------------|------|------|-------|

| IPAR   | Partial Array Refresh<br>Current | $V_{IN} = VCCQ \text{ or } 0V$<br>$\overline{ZZ} = LOW$ | 12Mb    | 3/4                |      | 90   | μA    |

|        |                                  | CR[4] = 1                                               | 8Mb     | 1/2                |      | 80   | μA    |

|        |                                  |                                                         | 4Mb     | 1/4                |      | 70   | μA    |

Note: IPAR (MAX) values measured with TCR set to 85°C

## **Temperature Compensated Refresh Specifications Conditions**

| Symbol | Description                            | Conditions                     | Density | Max Case<br>Temperatures | Тур.  | Max. | Units |

|--------|----------------------------------------|--------------------------------|---------|--------------------------|-------|------|-------|

| ITCR   | Temperature                            | $V_{IN} = VCCQ \text{ or } 0V$ | 16Mb    | +85°C                    |       | 100  | μA    |

|        | Compensated Refresh<br>Standby Current | sh Chip Disabled               |         | +70°C                    |       | 90   | μA    |

|        |                                        |                                |         |                          | +45°C |      | 80    |

|        |                                        |                                |         | +15°C                    |       | 70   | μA    |

Note: 1. ITCR (MAX) values measured with FULL ARRAY refresh.

2. This device assumes a standby mode if the chip is disabled ( $\overline{CE}$  HIGH).

#### **Truth Table**

| CE | ZZ | OE | WE | LB | HB | I/Oo to I/O7 Mode | I/O8 to I/O15 Mode | VCC Current       |

|----|----|----|----|----|----|-------------------|--------------------|-------------------|

| Н  | Н  | Х  | Х  | Х  | Х  | Not selected      | Not selected       | ISB1              |

| Н  | L  | Х  | Х  | Х  | Х  | Not selected      | Not selected       | Izz <sup>*2</sup> |

| Н  | L  | Х  | Х  | Х  | Х  | Not selected      | Not selected       | IPAR*2            |

| L  | L  | Х  | L  | Х  | Х  | Not selected      | Not selected       | Load CR Register  |

|    |    |    |    | L  | L  | Read              | Read               | Icc1, Icc2        |

| L  | н  | L  | н  | L  | Н  | Read              | High - Z           | Icc1, Icc2        |

|    |    |    |    | Н  | L  | High - Z          | Read               | Icc1, Icc2        |

|    |    |    |    | L  | L  | Write             | Write              | Icc1, Icc2        |

| L  | Н  | х  | L  | L  | Н  | Write             | Not Write/Hi - Z   | Icc1, Icc2        |

|    |    |    |    | Н  | L  | Not Write/Hi - Z  | Write              | Icc1, Icc2        |

| L  | Н  | Н  | Н  | Х  | Х  | High - Z          | High - Z           | ICC1, ICC2        |

#### Note: 1. X = H or L

2. DPD is enable when CR register A4 is "0"; otherwise, PAR is enable

#### Capacitance (T<sub>A</sub> = 25°C, f = 1.0MHz)

| Symbol | Symbol Parameter         |   | Max. | Unit | Conditions |

|--------|--------------------------|---|------|------|------------|

| Cin*   | Input Capacitance        | - | 6    | pF   | Vin = 0V   |

| Cı/o*  | Input/Output Capacitance | - | 6    | pF   | Vvo = 0V   |

\* These parameters are sampled and not 100% tested.

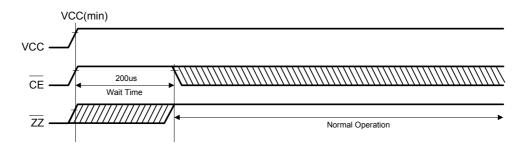

#### Initialization

The A64E06161 is initialized in the power-on sequence according to the following.

To stabilize internal circuits, after turning on the power, a 200µs or longer wait time must precede any signal toggling.

After the wait time, it can be normal operation.

#### **Power on Chart**

Notes: 1. Following power application, make  $\overline{CE}$  high level during the wait time 200us interval.

2. After power on sequence, the normal operating  $\overline{ZZ}$  must keep at high.

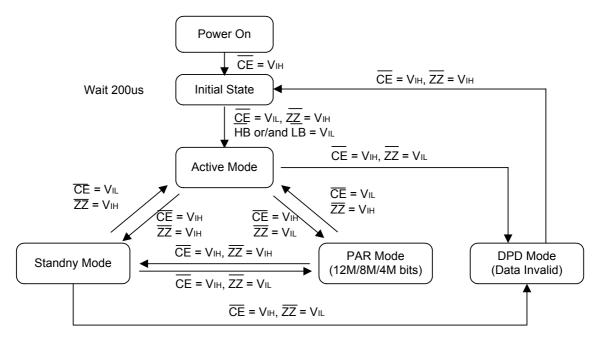

#### **Standby Mode State Machines**

Note: DPD is enable when CR register A4 is "0"; otherwise, PAR is enable.

## **Configuration Register**

The configuration register (CR) defines how the A64E06161 operates and whether page mode read accesses are permitted. The register is automatically

loaded with default setting during power on and can be updated anytime while the device is operating in a normal state.

## **CR Register Description**

| Reserved | PAGE | E TCR |    | ZZ Enable Deep Sleep Array On/Off on ZZ |    | PAR Top/Bottom<br>Selection |    |    |

|----------|------|-------|----|-----------------------------------------|----|-----------------------------|----|----|

| A19 - A8 | A7   | A6    | A5 | A4                                      | A3 | A2                          | A1 | A0 |

| Bit(s)   | Name                                        | Deserved                                                           |

|----------|---------------------------------------------|--------------------------------------------------------------------|

| A19 - A8 | Reserved                                    | Reserved, All must be set to "0"                                   |

| 7        | Page Mode on/off                            | 0 - Page Mode Disabled (Default)                                   |

|          |                                             | 1 - Page Mode Enabled                                              |

| 6, 5     | Temperature Compensated Register<br>Section | 11 - +85°C (Default)<br>00 - +70°C<br>01 - +45°C<br>10 - +15°C     |

| 4        | ZZ Enable Deep Sleep                        | 0 - DPD Mode Enabled<br>1 - DPD Mode Disabled (Default)            |

| 3        | Array On/Off on ZZ                          | 0 - PAR Mode (Default)<br>1 - RMS Mode                             |

| 2        | PAR Top/Bottom Half Selection               | 0 - Bottom (Default)<br>1 - Top                                    |

| 1 - 0    | PAR Memory Selection                        | 01 - 3/4 Array (12M)<br>10 - 1/2 Array (8M)<br>11 - 1/4 Array (4M) |

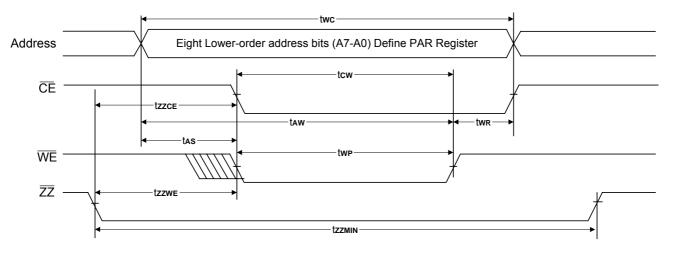

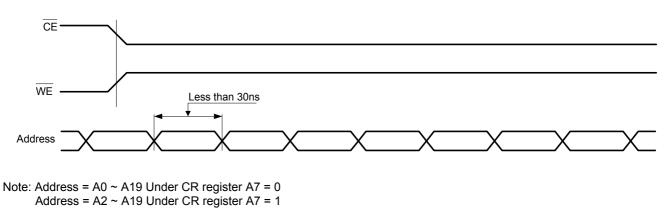

## CR Register Update – Timing Waveform

#### Figure 1: CR register update-Timing waveform

#### Notes:

- 1. VIH(MAX) = Vccq + 0.2V for pulse durations less than 20ns.

- 2.  $V_{IL(MIN)} = -1V$  for pulse duration less than 20ns.

- 3. Overshoot and undershoot specifications are characterized and are not 100% tested.

- 4. Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at Vcc = Vcc(typ.) and T<sub>A</sub> = 25°C.

- 5. The timing values for the CR Register Update are shown in the "Partial Array Mode Timing" table and "AC Characteristics" table.

#### **Page Mode Description**

The Page Mode operation takes advantage of the fact that adjacent address can be read in shorter period of time than random addresses. Write operations do not support comparable page mode functionality. The Page Mode operation can be enabled and disabled in the CR register. If the CR register bit A7 is set to a "1", Page Mode operation is enabled.

The A64E06161 provides following operation mode for reducing power:

- 1. Deep Power Down (DPD) mode

- 2. Reduce Memory Size (RMS) mode

- 3. Partial Array Refresh (PAR) mode

- 4. Temperature Compensated Refresh (TCR) mode

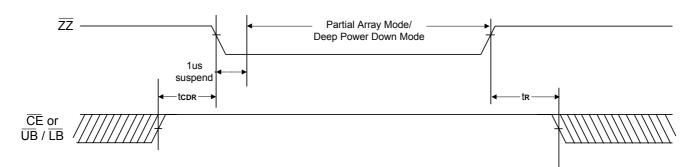

#### 1. Deep Power Down (DPD) mode

In this mode, the internal refresh is turned off and all data integrity of the array is lost. Deep Power Down (DPD) mode

is entered by ZZ low and keep 10us with A4 register bit set

to a "0". The device stays in the Deep Power Down (DPD)

mode until ZZ is driven High. If the A4 register bit is set equal to "1", Deep Power Down (DPD) mode will not be activated. Once the A64E06161 exits the Deep Power Down (DPD) mode, the content of the CR register is destroyed and the CR register would go into the default state upon normal operation.

#### 2. Reduce Memory Size (RMS) mode

In this mode, the A64E06161 can be operated as a reduced size device. For example, one can operate the 16M A64E06161 as a 4M or 8M memory block. Reduce Memory Size (RMS) mode can be enabled by having the appropriate

setting in the CR register. The mode is effective once ZZ goes high and remains in the Reduce Memory Size (RMS) mode until full array restored by setting the CR register again. At power on, all four section of the device are activated and the A64E06161 enter into its default state of full memory size and refresh space.

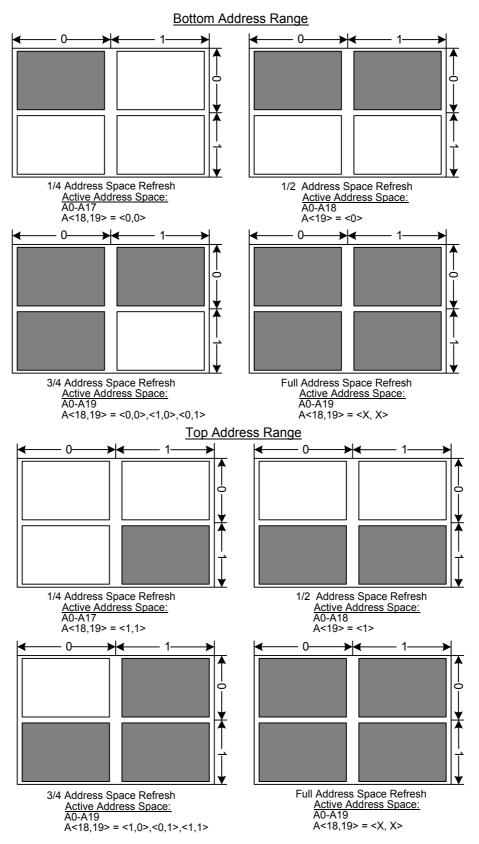

|    | Partial Array Refresh Mode (A3 =0, A4 = 1) |                          |                                         |           |         |  |  |  |

|----|--------------------------------------------|--------------------------|-----------------------------------------|-----------|---------|--|--|--|

| A2 | A1, A0                                     | Refresh Section          | Address                                 | Size      | Density |  |  |  |

| 0  | 11                                         | One-fourth of the Die    | 00000h - 3FFFFh (A19 = A18 = 0)         | 256K × 16 | 4M      |  |  |  |

| 0  | 10                                         | Half of the Die          | 00000h - 7FFFFh (A19 = 0)               | 512K × 16 | 8M      |  |  |  |

| 0  | 01                                         | Three-fourths of the Die | 00000h - BFFFFh (A19 : A18 ≠ 11)        | 768K × 16 | 12M     |  |  |  |

| 1  | 11                                         | One-fourth of the Die    | C0000h - FFFFh (A19 = A18 = 1)          | 256K × 16 | 4M      |  |  |  |

| 1  | 10                                         | Half of the Die          | 80000h - FFFFFh (A19 = 1)               | 512K × 16 | 8M      |  |  |  |

| 1  | 01                                         | Three-fourths of the Die | 40000h - FFFFFh (A19: A18 ≠ 00)         | 768K × 16 | 12M     |  |  |  |

|    |                                            | Re                       | duced Memory Size Mode (A3 = 1, A4 = 1) |           |         |  |  |  |

| 0  | 11                                         | One-fourth of the Die    | 00000h - 3FFFFh (A19 = A18 = 0)         | 256K × 16 | 4M      |  |  |  |

| 0  | 10                                         | Half of the Die          | 00000h - 7FFFFh (A19 = 0)               | 512K × 16 | 8M      |  |  |  |

| 0  | 01                                         | Three-fourths of the Die | 00000h - BFFFFh (A19 : A18 ≠ 11)        | 768K × 16 | 12M     |  |  |  |

| 1  | 11                                         | One-fourth of the Die    | C0000h - FFFFh (A19 = A18 = 1)          | 256K × 16 | 4M      |  |  |  |

| 1  | 10                                         | Half of the Die          | 80000h - FFFFFh (A19 = 1)               | 512K × 16 | 8M      |  |  |  |

| 1  | 01                                         | Three-fourths of the Die | 40000h - FFFFFh (A19 : A18 ≠ 00)        | 768K × 16 | 12M     |  |  |  |

#### Variable Address Space – Address Patterns

## **Memory Block Spilt**

#### 3. Partial Array Refresh (PAR) mode

In this mode, customers can turn off section of A64E06161 in stand-by mode to save standby current. The A64E06161 is divided into four 4M sections allowing certain section to be active. The array partition to be refreshed is determined by the respective bit in the CR register. When  $\overline{ZZ}$  is active low, only the portion of the array that is set in the CR register is refreshed and the data is keep at a certain section of memory. The Partial Array Refresh (PAR) mode is only available during standby time ( $\overline{ZZ}$  low). Once  $\overline{ZZ}$  is turned

high, the A64E06161 goes back to operating in full array refresh. For Partial Array Refresh (PAR) mode to be activated, the register bit, A4 must be set to a "1" value. To change the address space of the Partial Array Refresh (PAR) mode, the CR register must be updated using the CR register description. If the CR register is not updated after power on, the A64E06161 will be in its default state and the whole memory array will be refreshed.

#### Partial Array Refresh – Entry/Exit

#### Figure 2: Partial Array refresh – Entry/Exit

#### **Partial Array Mode Timings**

| Parameter | Description                                         | Min. | Max. | Unit |

|-----------|-----------------------------------------------------|------|------|------|

| tzzwe     | ZZ LOW to WE LOW                                    |      | 1    | μs   |

| tCDR      | Chip Deselect to ZZ LOW                             | 0    |      | μs   |

| tR        | Operation Recovery Time (Deep Power Down Mode only) |      | 200  | μs   |

| tzzmin    | Deep Power Down Mode Time                           | 10   |      | μs   |

| tzzce     | ZZ LOW to CE LOW                                    | 0    | 1    | μs   |

| tzzbe     | ZZ LOW to UB/LD LOW                                 | 0    | 1    | μs   |

Notes:

1.  $\overline{OE}$  and the data pins are in a "don't care" state while the device is in Partial Array Mode.

2. All other timing parameters are as shown in the switching characteristics section.

3. tr applies only in the Deep Power Down Mode.

#### 4. Temperature Compensated Refresh (TCR) mode

In this mode, the hidden refresh rate can be optimized for the operating temperature. At higher temperature, the DRAM cell must be refreshed more often than at lower temperature. By setting the temperature of operation in CR register, the refresh rate can be optimized to meet the low standby

current at given operating temperature. There are four selections (+15°C, +45°C, +70°C, +85°C) in the CR register description.

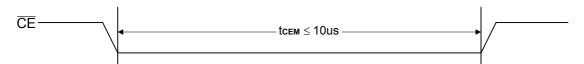

## **Avoid Timing**

Following Figure 3 is show you an abnormal timing which is not supported on Super RAM.

#### **Operation When Page Mode is Enabled**

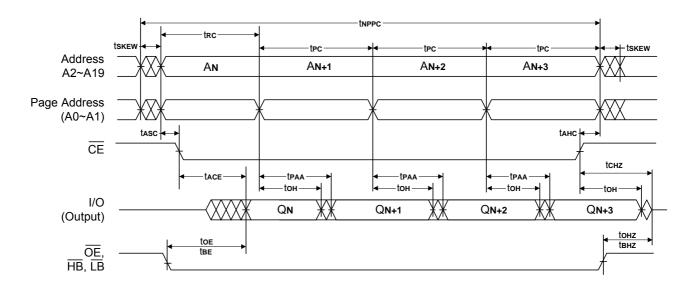

The maximum  $\overline{CE}$  pulse width should not exceed 10µs to accommodate orderly scheduling of refresh (Figure 4).

Note: Timing constraints when page mode is enabled.

Figure 4: Timing constraint for tCEM

| Symbol       | Parameter                          | -    | -70   |      | -85   |    |

|--------------|------------------------------------|------|-------|------|-------|----|

|              |                                    | Min. | Max.  | Min. | Max.  |    |

| Read Cycle   |                                    | ·    |       |      |       |    |

| trc          | Read Cycle Time                    | 70   | 10000 | 85   | 10000 | ns |

| tskew        | Address Skew                       | -    | 10    | -    | 10    | ns |

| taa          | Address Access Time                | -    | 70    | -    | 85    | ns |

| TACE         | Chip Enable Access Time            | -    | 70    | -    | 85    | ns |

| tве          | Byte Enable Access Time            | -    | 35    | -    | 45    | ns |

| to⊨          | Output Enable to Output Valid      | -    | 35    | -    | 45    | ns |

| tc∟z         | Chip Enable to Output in Low Z     | 5    | -     | 5    | -     | ns |

| tв∟z         | Byte Enable to Output in Low Z     | 5    | -     | 5    | -     | ns |

| to∟z         | Output Enable to Output in Low Z   | 5    | -     | 5    | -     | ns |

| tснz         | Chip Disable to Output in High Z   | 0    | 14    | 0    | 14    | ns |

| tвнz         | Byte Disable to Output in High Z   | 0    | 14    | 0    | 14    | ns |

| tонz         | Output Disable to Output in High Z | 0    | 14    | 0    | 14    | ns |

| toн          | Output Hold from Address Change    | 10   | -     | 10   | -     | ns |

| tasc         | Address Setup to CE Low            | 0    | -     | 0    | -     | ns |

| tанс         | Address Hold Time from CE High     | 0    | -     | 0    | -     | ns |

| tсен         | CE High Pulse With                 | 10   | -     | 10   | -     | ns |

| tPC          | Page Read Cycle Time               | 25   | -     | 25   | -     | ns |

| <b>TPAA</b>  | Page access Time                   | -    | 25    | -    | 25    | ns |

| <b>tnppc</b> | Normal to Page Read Cycle Time     | -    | 10    | -    | 10    | μs |

| Write Cycle  |                                    |      |       |      |       |    |

| twc          | Write Cycle Time                   | 70   | 10000 | 85   | 10000 | ns |

| tskew        | Address Skew                       | -    | 10    | -    | 10    | ns |

| tcw          | Chip Enable to End of Write        | 70   | -     | 85   | -     | ns |

| tвw          | Byte Enable to End of Write        | 60   | -     | 70   | -     | ns |

| tas          | Address Setup Time                 | 0    | -     | 0    | -     | ns |

| taw          | Address Valid to End of Write      | 70   | -     | 85   | -     | ns |

| twp          | Write Pulse Width                  | 50   | -     | 60   | -     | ns |

| twr          | Write Recovery Time                | 0    | -     | 0    | -     | ns |

| twнz         | Write to Output in High Z          | -    | 14    | -    | 14    | ns |

| tow          | Data to Write Time Overlap         | 30   | -     | 35   | -     | ns |

| tdн          | Data Hold from Write Time          | 0    | -     | 0    | -     | ns |

| tow          | Output Active from End of Write    | 5    | -     | 5    | -     | ns |

| tasc         | Address Setup to CE Low            | 0    | -     | 0    | -     | ns |

| tанс         | Address Hold Time from CE High     | 0    | -     | 0    | -     | ns |

| tсен         | CE High Pulse With                 | 10   | -     | 10   | -     | ns |

| tweн         | WE High Pulse With                 | 10   | -     | 10   | -     | ns |

| tсем         | Maximum CE Pulse width             | -    | 10    | -    | 10    | μS |

## AC Characteristics (TA = 0°C to + 70°C or -25°C to 85°C, VCC = 1.7V to 1.95V, VCCQ = 1.7V to VCC GND = 0V)

Note: tchz, tbhz and tohz and twhz are defined as the time at which the outputs achieve the open circuit condition and are not referred to output voltage levels.

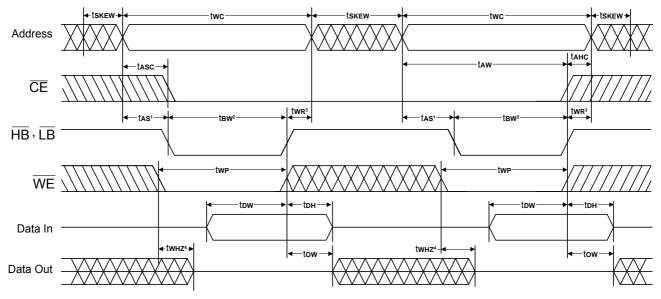

## **Timing Waveforms**

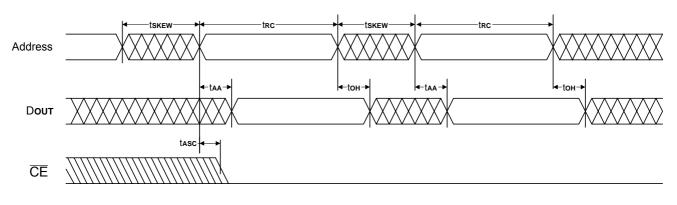

## Read Cycle 1<sup>(1, 2, 4, 6)</sup>

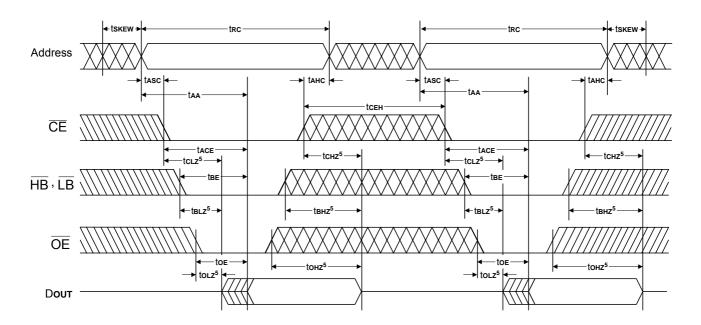

## Read Cycle 2-1<sup>(1, 3, 6)</sup>

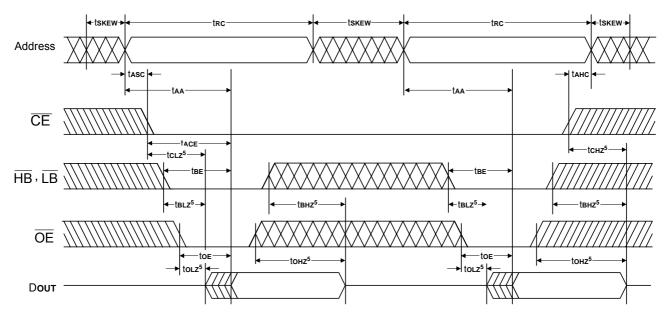

## Read Cycle 2-2<sup>(1, 3, 6)</sup>

Notes: 1. WE is high for Read Cycle.

- 2. Device is continuously enabled  $\overline{CE}$  = V<sub>IL</sub>,  $\overline{HB}$  = V<sub>IL</sub> and, or  $\overline{LB}$  = V<sub>IL</sub>.

- 3. Address valid prior to or coincident with  $\overline{CE}$  and ( $\overline{HB}$  and, or  $\overline{LB}$ ) transition low.

- 4.  $\overline{OE} = VIL$ .

- 5. Transition is measured  $\pm$ 500mV from steady state. This parameter is sampled and not 100% tested.

- 6.  $\overline{ZZ}$  is high for Read Cycle.

## **Timing Waveforms**

#### Words Page Read Cycle Timing Chart

## Timing Waveforms (continued)

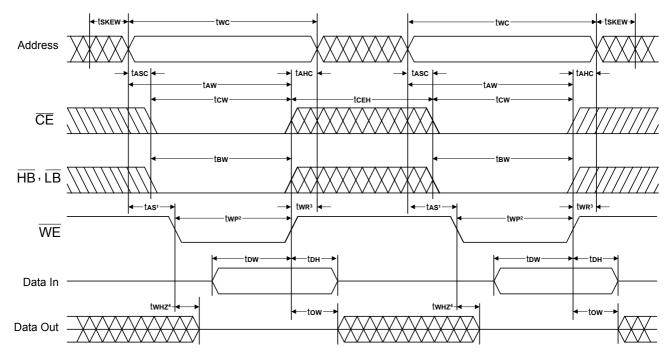

## Write Cycle 1-1<sup>(6)</sup> (Write Enable Controlled)

Write Cycle 1-2<sup>(6)</sup> (Write Enable Controlled)

## Timing Waveforms (continued)

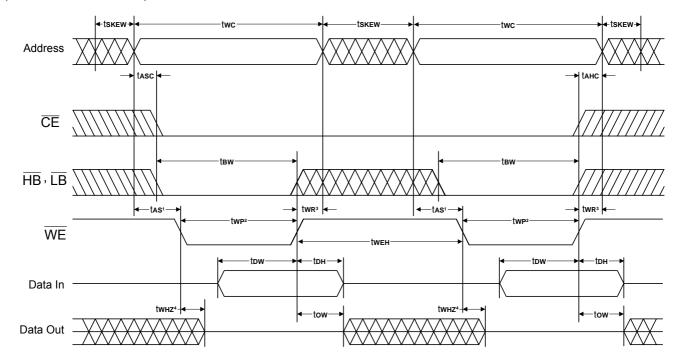

#### Write Cycle 2-1<sup>(6)</sup> (Chip Enable Controlled)

## **Timing Waveforms**

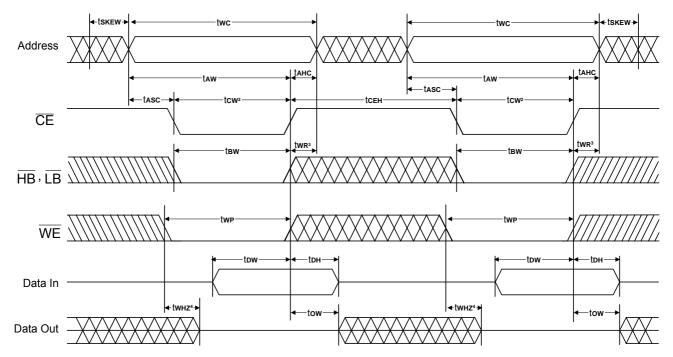

Write Cycle 3-1<sup>(6)</sup> (Byte Enable Controlled)

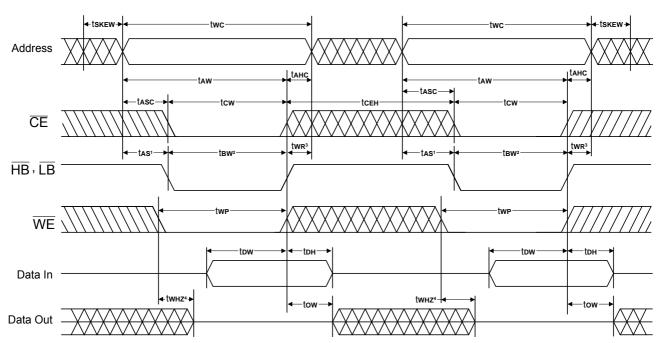

#### Write Cycle 3-2<sup>(6)</sup> (Byte Enable Controlled)

- Notes: 1. tas is measured from the address valid to the beginning of Write.

- 2. A Write occurs during the overlap (twp, tBw) of a low  $\overline{CE}$ ,  $\overline{WE}$  and ( $\overline{HB}$  and, or  $\overline{LB}$ ).

- 3. <u>twr</u> is measured from the earliest of  $\overline{CE}$  or  $\overline{WE}$  or ( $\overline{HB}$  and, or  $\overline{LB}$ ) going high to the end of the Write cycle. 4.  $\overline{OE}$  level is high or low.

- 5. Transition is measured ±500mV from steady state. This parameter is sampled and not 100% tested.

- 6.  $\overline{ZZ}$  is high for Write Cycle.

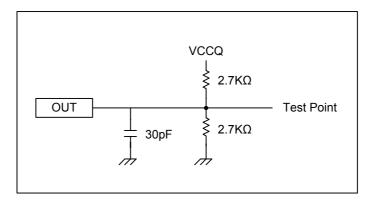

## **AC Test Conditions**

| Input Pulse Levels                       | VCCQ * 0.2 to VCCQ * 0.8 |

|------------------------------------------|--------------------------|

| Input Rise And Fall Time                 | 2 ns (10% to90%)         |

| Input and Output Timing Reference Levels | 0.5 * VCCQ               |

| Output Load                              | See Figures 5            |

## **Ordering Information**

| Part No.       | Access Time (ns) | Operating Current<br>Max. (mA) | Deep Power Down<br>Mode Standby<br>Current Max. (μA) | Package      |

|----------------|------------------|--------------------------------|------------------------------------------------------|--------------|

| A64E06161G-70  | 70               | 15                             | 10                                                   | 48B Mini BGA |

| A64E06161G-85  | 85               | 12                             | 10                                                   | 48B Mini BGA |

| A64E06161G-70I | 70               | 15                             | 10                                                   | 48B Mini BGA |

| A64E06161G-85I | 85               | 12                             | 10                                                   | 48B Mini BGA |

Note: -I is for industrial operating temperature range

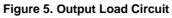

unit: mm

#### **Package Information**

48LD CSP (6 x 8 mm) Outline Dimensions (48TFBGA)

6.00

8.00

3.75

5.25

0.75

0.35

5.90

7.90

----

\_\_\_

0.30

#### Note:

D

Е

Dı

Еı

е

b

1. THE BALL DIAMETER, BALL PITCH, STAND-OFF & PACKAGE THICKNESS ARE DIFFERENT FROM JEDEC SPEC MO192 (LOW PROFILE BGA FAMILY).

6.10

8.10

----

\_\_\_

0.40

- 2. PRIMARY DATUM C AND SEATING PLANE ARE DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

- DIMENSION b IS MEASURED AT THE MAXIMUM.

THERE SHALL BE A MINIMUM CLEARANCE OF 0.25mm BETWEEN THE EDGE OF THE SOLDER BALL AND THE BODY EDGE.

- 4. BALL PAD OPENING OF SUBSTRATE IS  $\Phi$  0.3mm (SMD) SUGGEST TO DESIGN THE PCB LAND SIZE AS  $\Phi$  0.3mm (NSMD)