# **MOTOROLA**

# 32K x 9 Bit Synchronous Static RAM

### **ELECTRICALLY TESTED PER:** MPG62S950A

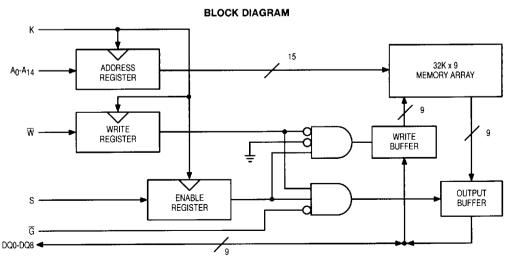

The 62S950A is a 294.912 bit synchronous static random access memory organized as 32,768 words of 9 bits, fabricated using Motorola's high-performance silicon-gate CMOS technology. The device integrates input registers, high-speed SRAM, and high drive capability outputs onto a single monolithic circuit for reduced parts count implementation of cache data RAM applications. Synchronous design allows precise cycle control with the use of external clock (K). Asynchronous control consist of output enable (G). CMOS circuitry reduces the overall power consumption and provides for greater reliability.

Address  $(A_0-A_{14})$  and control signals, except output enable  $(\overline{G})$ , are sampled through positive-edge triggered noninverting registers. Data outputs are asynchronously controlled by  $(\overline{G})$ .

Write cycles are differentiated from read cycles by the state of the synchronous write enable pin  $(\overline{W})$  at the rising edge of (K). Data for the write may be delayed until the latter half of the write cycle.

The 62S950A is packaged in a 32-pin ceramic leadless chip carrier (LCC). Multiple ground pins have been utilized to minimize effects induced by output noise.

- Single 5.0 V ± 10% Power Supplies for Output Level Compatibility

- Fast Access Times 15, 25, 35 ns and Cycle Times 15, 25, 35 ns

- Internal Input Register (Address Control)

- Output Enable Controlled Three-State Outputs

- · Common Data Inputs and Data Outputs

- High Output Drive Capability 85 pF per I/O

- High Board Design LCC Package

- Active High Chip Select Input for Easy Depth Expansion

Note: All power supply and ground pins must be connected for proper operation of the device

# 62S950A

# **Commercial Plus** and Mil/Aero Applications

#### **AVAILABLE AS**

1) JAN: N/A 2) SMD: N/A

3) 883: 62S950A - XX/BXAJC

X = CASE OUTLINE AS FOLLOWS:

PACKAGE: LCC: U

XX = Speed in ns (15, 25, 35)

# PIN ASSIGNMENT AND FUNCTION TABLE

| Pin | Symbol | Name              |

|-----|--------|-------------------|

| 1   | A13    | Address Input     |

| 2   | A12    | Address Input     |

| 3   | A11    | Address Input     |

| 4   | A10    | Address Input     |

| 5   | A9     | Address Input     |

| 6   | A8     | Address Input     |

| 7   | A7     | Address Input     |

| 8   | VCC    | +5 V Power Supply |

| 9   | К      | Clock             |

| 10  | VSS    | Ground            |

| 11  | A0     | Address Input     |

| 12  | A1     | Address Input     |

| 13  | A2     | Address Input     |

| 14  | A3     | Address Input     |

| 15  | A4     | Address Input     |

| 16  | A5     | Address Input     |

| Pin | Symbol          | Name              |

|-----|-----------------|-------------------|

| 17  | A6              | Address Input     |

| 18  | DQ0             | Data Input/Output |

| 19  | DQ1             | Data Input/Output |

| 20  | V <sub>SS</sub> | Ground            |

| 21  | DQ2             | Data input/Output |

| 22  | DQ3             | Data Input/Output |

| 23  | SW              | Synchronous Write |

| 24  | VSS             | Ground            |

| 25  | G               | Output Enable     |

| 26  | S0              | Chip Select       |

| 27  | DQ8             | Data Input/Output |

| 28  | DQ4             | Data Input/Output |

| 29  | DQ5             | Data Input/Output |

| 30  | DQ6             | Data Input/Output |

| 31  | DQ7             | Data Input/Output |

| 32  | A14             | Address Input     |

| S0 | SW | G | K   | Operation      | I/O Status |

|----|----|---|-----|----------------|------------|

| L  | X  | X | L-H | Deselected     | High-Z     |

| Н  | L  | X | L-H | Write          | High-Z     |

| Н  | L  | X | L   | Write          | Data-In    |

| Н  | н  |   | L-H | Read Initiated |            |

| Н  | Н  | Н | х   | Read           | High-Z     |

| Н  | Н  | L | ×   | Read           | Data-Out   |

### Notes:

- 1. X = Don't Care.

- 2. S0 and SW must meet setup and hold times for the low-to-high transition of clock (K).

- 3.  $\overline{W} = L$  for the last clock transition from low to high. Similarly for S = H.

Figure 1A.

Figure 1B.

Figure 1C.

| Rating                                                                                         | Symbol                             | Value                          | Unit | protect the inputs against damaged due to high static voltages |  |  |

|------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------|------|----------------------------------------------------------------|--|--|

| Power Supply Voltage                                                                           | Vcc                                | - 0.5 to + 7.0                 | ٧    | electric fields; however, it advised that normal precaution    |  |  |

| Voltage Relative to VSS                                                                        | V <sub>IN</sub> , V <sub>OUT</sub> | – 0.5 to V <sub>CC</sub> + 0.5 | V    | be taken to avoid application of a                             |  |  |

| Output Current (per I/O)                                                                       | lout                               | ± 20                           | mA   | voltages higher than maximurated voltages to this hi           |  |  |

| Power Dissipation<br>(T <sub>A</sub> = 25°C, V <sub>CC</sub> = 5 V, t <sub>KHKH</sub> = 20 ns) | PD                                 | 1.0                            | w    | impedance circuit.  This CMOS memory circuit h                 |  |  |

| Temperature Under Bias                                                                         | T <sub>bias</sub>                  | - 55 to +125                   | °C   | been designed to meet the do a                                 |  |  |

| Storage Temperature Range                                                                      | T <sub>stg</sub>                   | - 65 to +150                   | °C   | ac specifications shown in tables, after thermal equilibri     |  |  |

| Operating Temperature Range                                                                    | TA                                 | - 55 to +125                   | °C   | has been established.                                          |  |  |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

## MOTOROLA SC {MEMORY/ASI 65E D

### DC OPERATING CONDITIONS AND CHARACTERISTICS

(VCC = 5.0 V  $\pm$  10%, TA = -55 to + 125°C, Unless Otherwise Noted)

# RECOMMENDED OPERATING CONDITIONS (Voltages referenced to VSS = 0 V)

| ACCOMMENDED OF ENAMENCE OF THE CONTROL OF THE STREET | - 00 /           |                |     |                       |      |

|------------------------------------------------------|------------------|----------------|-----|-----------------------|------|

| Parameter                                            | Symbol           | Min            | Тур | Max                   | Unit |

| Supply Voltage (Operating Voltage Range)             | Vcc              | 4.5            | 5.0 | 5.5                   | V    |

| Input High Voltage                                   | VIH              | 2.2            | 3.0 | V <sub>CC</sub> + 0.3 | ٧    |

| Input Low Voltage                                    | V <sub>1</sub> L | - 0.5 <b>*</b> | 0.0 | 0.8                   | ٧    |

<sup>\*</sup>  $V_{1L}$  (min) = -3.0 V ac (pulse width  $\leq$  20 ns)

#### DC CHARACTERISTICS

| Parameter                                                                                                                                                                                                                    | Symbol               | Min | Max   | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|-------|------|

| Input Leakage Current (All Inputs, V <sub>in</sub> = 0 to V <sub>CC</sub> )                                                                                                                                                  | likg(I)              | _   | ± 1.0 | μА   |

| Output Leakage Current (G, S1 = V <sub>IH</sub> , S0 = V <sub>IL</sub> , V <sub>out</sub> = 0 to V <sub>CCQ</sub> )                                                                                                          | I <sub>lkg</sub> (O) | _   | ± 1.0 | μА   |

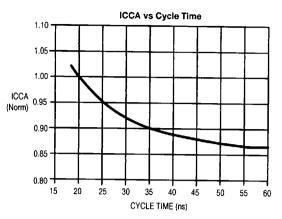

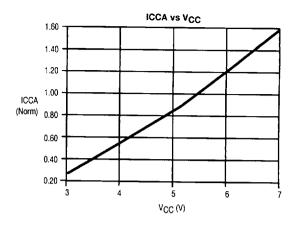

| AC Supply Current ( $\overline{G}$ , S0 = V <sub>IH</sub> , All Inputs = V <sub>IL</sub> = 0 V and V <sub>IH</sub> $\geq$ 3.0 V, I <sub>out</sub> = 0 mA, Cycle Time $\geq$ t <sub>KHKH</sub> min) t <sub>KHKH</sub> = 15 ns | ICCA                 | _   | 170   | mA   |

| Standby Current (S0 = V <sub>IL</sub> , All Inputs = V <sub>IL</sub> and V <sub>IH</sub> )                                                                                                                                   | I <sub>SB1</sub>     | _   | 40    | mA   |

| CMOS Standby Current (S0 $\leq$ 0.2 V, All Inputs $\geq$ V <sub>CC</sub> $-$ 0.2 V or $\leq$ 0.2 V, Cycle Time $\geq$ t <sub>KHKH</sub> min)                                                                                 | I <sub>SB2</sub>     | _   | 30    | mA   |

| Output Low Voltage (I <sub>OL</sub> = + 8.0 mA)                                                                                                                                                                              | VOL                  | 0.1 | 0.4   | ν    |

| Output High Voltage (IOH = - 4.0 mA)                                                                                                                                                                                         | Voн                  | 2.4 |       | ν    |

NOTE: Good decoupling of the local power supply should always be used. DC characteristics are guaranteed for all possible i486 bus cycles.

# CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, TA = 25°C, Periodically Sampled Rather Than 100% Tested)

| Characteristic                              | Symbol           | Тур | Max | Unit |

|---------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (ali Pins Expect DQ0-DQ8) | C <sub>in</sub>  | 2   | 3   | ρF   |

| Input/Output Capacitance (DQ0-DQ8)          | C <sub>I/O</sub> | 7   | 8   | рF   |

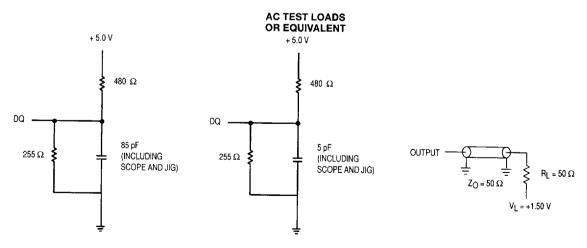

### **AC OPERATING CONDITIONS AND CHARACTERISTICS**

$(VCC = 5.0 \text{ V} \pm 10\%, T_A = -55 \text{ to} + 125^{\circ}\text{C}, \text{Unless Otherwise Noted})$

| Input Timing Measurement Reference Level 1.5 V | Output Measurement Timing Level 1.5 V            |

|------------------------------------------------|--------------------------------------------------|

| Input Pulse Levels 0 to 3.0 V                  | Output Load See Figure 1A Unless Otherwise Noted |

| Input Rise/Fall Time                           | •                                                |

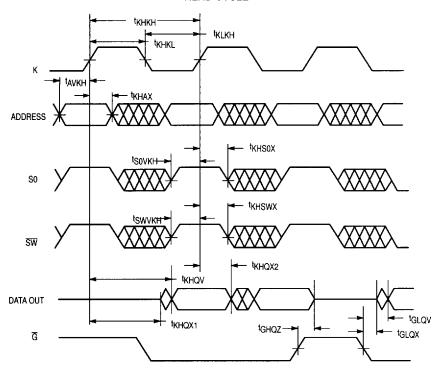

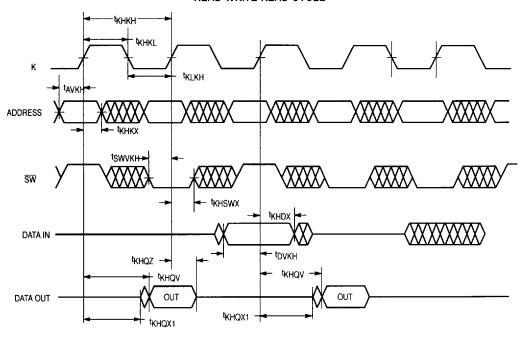

### Read/Write Cycle Timing (See Note 1, 2, and 3)

| Parameter                                                                                                             | Cumbal                                                                            | 62S950A-15   |             | 62\$950A-25    |                   | 62S950A-35     |                   |                |       |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------|-------------|----------------|-------------------|----------------|-------------------|----------------|-------|

| Farameter                                                                                                             | Symbol                                                                            | Min          | Max         | Min            | Max               | Min            | Max               | Unit           | Notes |

| Clock<br>Cycle Time<br>Clock High Pulse Width<br>Clock Low Pulse Width                                                | †KHKH<br>†KHKL<br>†KLKH                                                           | 15<br>7<br>7 |             | 25<br>11<br>11 | _<br>_<br>_       | 35<br>20<br>20 | _<br>_<br>_       | ns<br>ns<br>ns | 6     |

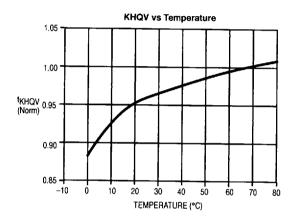

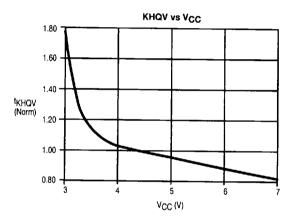

| Read Access Times:<br>Clock Access Time<br>Output Enable to Output Valid                                              | <sup>†</sup> KHQV<br><sup>†</sup> GLQV                                            | _            | 15<br>6     | _              | 25<br>10          | _              | 35<br>15          | ns<br>ns       |       |

| Write Cycles: Data-In Valid to Clock High (Transparent Data) Clock High to Data Invalid (Transparent Data)            | <sup>†</sup> DVKH                                                                 | 6<br>2       | _<br>_      | 6              | _                 | 6              | _                 | ns<br>ns       |       |

| Output Buffer Control:<br>Clock High to Output Low-Z after<br>Write                                                   | <sup>t</sup> KHQX1                                                                | 6            | _           | 6              | _                 | 6              |                   | ns             |       |

| Clock High to Output Change<br>Output Enable to Output Active<br>Output Disable to Q High-Z<br>Clock High to Q High-Z | <sup>†</sup> KHQX2<br><sup>†</sup> GLQX<br><sup>†</sup> GHQX<br><sup>†</sup> KHQZ | 3<br>0<br>—  | -<br>8<br>8 | 3<br>0<br>—    | —<br>—<br>10<br>8 | 3<br>0<br>—    | —<br>—<br>12<br>8 | ns<br>ns<br>ns | 4     |

| Register Setup Times for: Address Synchronous Write Chip Select                                                       | tavkh<br>twvkh<br>tsovkh                                                          | 2            | _           | 2              | _                 | 2              | _                 | ns             | 5     |

| Register Hold Times for: Address Synchronous Write Chip Select                                                        | tKHAX<br>tKHWX<br>tKHS0X                                                          | 2            | _           | 2              | _                 | 2              | -                 | ns             | 5     |

#### NOTES:

- 1. A read cycle is defined by SW high for the setup and hold times. A write cycle is defined by SW low for the setup and hold times.

- 2. All read and write cycle timings are referenced from K or G.

- 3. G is a don't care when SW is sampled low.

- 4. Transition is measured ± 500 mV from steady-state voltage with output load of Figure 1B. At any given voltage and temperature, tGHQZmax is less than tGLQXmin, for a given device and from device to device.

- This is a synchronous device. All address inputs must meet the specified setup and hold times with stable logic levels for ALL rising edges of clock (K) when the device is selected. All synchronous inputs must meet the specified setup and hold times with stable logic levels for ALL rising edges of the clock (K) when the device is selected.

- 6. See Figure 1C.

### **READ CYCLE**

### **READ-WRITE-READ CYCLE**

MOTOROLA SC {MEMORY/ASI 65E D

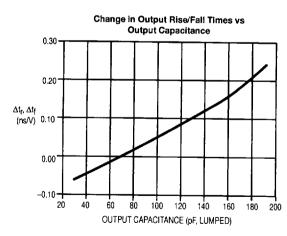

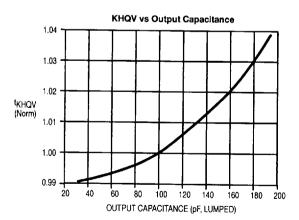

### **Derating Curves**

NOTE: Derating curves are based on component typical values

# MOTOROLA SC {MEMORY/ASI LSE D