# VM118/VM118R

6-CHANNEL, CENTER-TAPPED THIN-FILM HEAD, READ/WRITE PREAMPLIFIER

April, 1990

#### **FEATURES**

- Operates on +5V and +12V Power Supplies

- Programmable Write-Current Source

- TTL-Compatible Control Lines

- Write-Unsafe Detection Circuitry

- Low Input Noise

- For Use With Center-Tapped Thin-Film Heads

- Power-Up/Power-Down Write Protection

- Optional Internal Head Damping Resistors

- Available in 2, 4 and 6 Channels

#### DESCRIPTION

The VM118/VM118R is a bipolar, monolithic read/write preamp circuit designed for use with center-tapped thin-film recording heads. The circuit provides a low-noise read data path for signals from the disk in the read mode and provides write-current control for data written on the disk in the write mode.

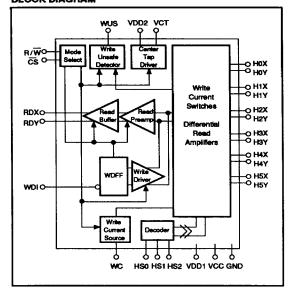

#### BLOCK DIAGRAM

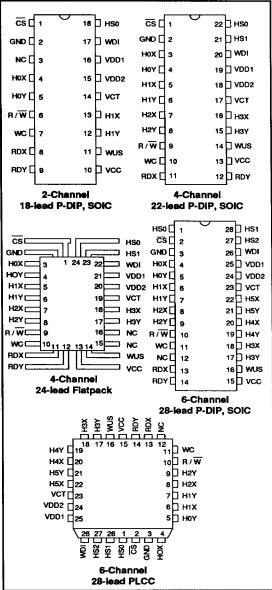

# CONNECTION DIAGRAMS

| ABSOLUTE MAXIMUM RATINGS                              |

|-------------------------------------------------------|

| Power Supply Voltages:                                |

| V <sub>DD1</sub> 0.3 to 14V                           |

| V <sub>DD2</sub> 0.3V to 14V                          |

| VCC0.3V to 6V                                         |

| Pin Voltages:                                         |

| Head Select (HS)0.3V to V <sub>CC</sub> + 0.3V        |

| Write Unsafe (WUS)0.3V to VCC + 0.3V                  |

| Write Data Input (WDI)0.3V to V <sub>CC</sub> + 0.3V  |

| Read/Write Select (R/W)0.3V to V <sub>CC</sub> + 0.3V |

| Output Current:                                       |

| Write Current (IW)                                    |

| Read Data (RDX, RDY) 10mA                             |

| Center Tap Current (ICT)                              |

| Write Unsafe (WUS)                                    |

| Storage Temperature Range65 to 150°C                  |

| Lead Temperature (Soldering 60 Seconds) 300°C         |

| Junction Temperature                                  |

| Thermal Characteristics, $\Theta_{JA}$ :              |

| 18-lead P-DIP                                         |

| 18-lead SOIC                                          |

| 22-lead P-DIP                                         |

| 22-lead SOIC 80°C/W                                   |

| 24-lead Flatpack                                      |

| 28-lead P-DIP                                         |

| 28-lead SOIC 70°C/W                                   |

| 28-lead PLCC                                          |

## RECOMMENDED OPERATING CONDITIONS

| DC Power Supply Voltage:           |                     |

|------------------------------------|---------------------|

| V <sub>DD1</sub>                   | 12V ± 10%           |

| V <sub>DD2</sub> 7.                | .0V to VDD1         |

| V <sub>CC</sub>                    | . 5V ± 10%          |

| Head Inductance (LH)               |                     |

| Damping Resistance (RD) (Note 1)   | 750Ω                |

| RCT Resistor at Iw = 50mA (Note 2) | $.68\Omega \pm 5\%$ |

| RDX,RDY Output Current (Read Mode) |                     |

| Write Current                      | 10 to 50mA          |

| Operating Temperature Range        |                     |

| Junction Temperature               | 25° to +125°        |

Note 1: VM118R has head damping resistors placed on the chip; the standard value is  $750\Omega \pm 20\%$ .

Note 2: Resistor (R<sub>CT</sub>) used to limit power dissipation. R<sub>CT</sub>( $\Omega$ )  $\leq$  3.4/I w (A)

#### **CIRCUIT OPERATION**

The VM118/VM118R operates as a write-current switch in the write mode and as a low-noise differential amplifier in the read mode. Channel selection is controlled by HSO, HS1 and HS2 lines, and mode select is controlled by the CS and R/W select lines. Both CS and R/W have internal pull-up resistors to prevent accidental write conditions. Unsafe write conditions are indicated by the WUS line.

#### Write Mode

In the write mode, the VM118/VM118R operates as a write-current switch. Write current is supplied by an internal current source. The magnitude of the write current is determined by an external resistor connected between WC and ground. The head current is switched between the X and Y side of a selected head by falling transitions on WDI (write data input). When switching to the write mode from the read mode, the write data flip-flop is initialized to pass head current through the X side of the head.

The write unsafe (WUS), open collector output, will give a high level for any of the following unsafe conditions:

- Open Head

- No Write Current

- Read Mode

- Idle Mode

- Write Data Frequency Too Low

- Head Center-Tapped Open

After the fault condition is corrected, it takes two negative transitions on WDI to clear the WUS line.

#### Read Mode

In the read mode, the circuit operates as a low-noise differential amplifier. The write current source is turned off and the write data flip-flop is set. The selected head provides a differential input. The RDX and RDY pins provide differential emitter follower outputs which are in phase with the X and Y inputs.

Write current is deactivated for both the read and the idle mode so that external gating is not required.

#### **Head Select**

One of the six or eight heads may be selected in both the read and write modes. The selected head is determined by the voltage level of the head select inputs as shown below:

| HSO | HS1 | HS2 | HEAD |

|-----|-----|-----|------|

| L   | L   | L   | 0    |

| Н   | L   | L   | 1    |

| L   | Н   | ٦   | 2    |

| Н   | Н   | Ļ   | 3    |

| L   | L   | Н   | 4    |

| H   | Ĺ   | Н   | 5    |

| X   | Н   | Н   | None |

#### **Mode Select**

This circuit has three modes of operation: read, write and idle. The state of the chip select ( $\overline{CS}$ ) and the Read/Write select ( $\overline{R/W}$ ) inputs determine the mode of operation as shown below:

| <u>cs</u> | R/W | MODE  |

|-----------|-----|-------|

| L         | L   | Write |

| L         | Н   | Read  |

| H         | Х   | ldle  |

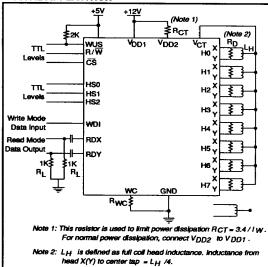

### TYPICAL APPLICATION

DC CHARACTERISTICS Unless otherwise specified,  $V_{DD1} = V_{DD2} = 12V \pm 10\%$ ,  $V_{CC} = 5V \pm 10\%$ ,  $T_A = 25^{\circ}C$ .

| PARAMETER                | SYM             | CONDITIONS                                               | MIN  | TYP | MAX       | UNITS |

|--------------------------|-----------------|----------------------------------------------------------|------|-----|-----------|-------|

| POWER SUPPLY             |                 |                                                          |      |     |           |       |

| Y                        | I <sub>DD</sub> | Read Mode                                                |      |     | 40        |       |

| Positive Supply Current  |                 | Write Mode                                               |      |     | 26 + IW   | mA    |

|                          |                 | Idle Mode                                                |      |     | 25        |       |

|                          | Icc             | Idle/Read Mode                                           |      |     | 15        |       |

|                          |                 | Write Mode                                               |      |     | 18        | mA    |

|                          | P <sub>D</sub>  | Read Mode                                                |      | 325 | 610       |       |

| Power Supply Dissipation | "               | Idle Mode                                                |      | 200 | 412       |       |

| Power Supply Dissipation |                 | Write Mode I <sub>W</sub> = 50mA, $R_{CT}$ = 75 $\Omega$ |      | 675 | 850       | mW    |

|                          |                 | Write Mode I <sub>W</sub> = 50mA, R <sub>CT</sub> = 0Ω   |      | 850 | 1100      |       |

| DIGITAL TTL INPUTS: CS   | , R/W, HS       | , WD1                                                    |      |     | -         |       |

| Input High Voltage       | VIH             |                                                          | 2    |     | VCC + 0.3 | ٧     |

| Input Low Voltage        | VIL             |                                                          | -0.3 |     | 0.8       | ٧     |

| Input High Current       | HH              | V <sub>IH</sub> = 2.0V VCC = 5.5V                        | -400 |     | 100       | μΑ    |

| Input Low Current        | l IIL           | V <sub>IL</sub> = 0.4V V <sub>CC</sub> = 5.5V            | -0.4 |     |           | mA    |

| WUS OUTPUT               |                 |                                                          |      |     |           |       |

| Low Voltage              | VOL             | I OL = 8mA (Safe)                                        |      |     | 0.5       | ٧     |

| High Current             | IOH             | VOH = 5V (Unsafe)                                        |      |     | 100       | μΑ    |

| HEAD CENTER TAP VOL      | TAGES           |                                                          |      |     |           |       |

| Read Mode                | VCT             | Read Mode                                                |      | 4.2 |           | ٧     |

| Write Mode               | Vст             | Write Mode                                               |      | 6.6 |           | V     |

**READ CHARACTERISTICS** Unless otherwise specified,  $V_{DD1} = V_{DD2} = 12V \pm 10\%$ ,  $V_{CC} = 5V \pm 10\%$ ,  $T_A = 25^{\circ}C$ .

| PARAMETER                         | SYM              | CONDITIONS                                                                                              | MIN      | TYP | MAX | UNITS  |

|-----------------------------------|------------------|---------------------------------------------------------------------------------------------------------|----------|-----|-----|--------|

| Differential Voltage Gain         | A <sub>V</sub>   | $V_{IN} = 1 \text{mVrms}, f = 500 \text{KHz}$ $R_L(RDX,RDY) = 1 \text{K}\Omega$                         | 80       |     | 120 | V/V    |

| Dynamic Range                     | DR               | DC input Voltage where AC Gain<br>Falls 10%, V <sub>IN</sub> = V <sub>DC</sub> + 0.5mVp-p<br>f = 500KHz | -2       |     | 2   | mV     |

| Bandwidth (-3dB)                  | BW               | $V_{IN} = 1 \text{mVrms}, Z_S < 5\Omega$                                                                | 30       |     |     | MHz    |

| Input Noise Voltage               | e <sub>in</sub>  | L <sub>H</sub> = 0, R <sub>H</sub> = 0, BW = 15MHz                                                      |          | 0.8 | 1.1 | nV/√Hz |

| Differential Input<br>Capacitance | CIN              | f = 5MHz                                                                                                |          |     | 35  | pF     |

| Differential Input                | RiN              | VM118                                                                                                   | 1.5      |     |     | ΚΩ     |

| Resistance                        | IIN              | VM118R                                                                                                  |          | 750 |     | Ω      |

| Input Current                     | IIN              |                                                                                                         | <u> </u> |     | 45  | μA     |

| Common Mode Rejection Ratio       | CMRR             | $V_{CM} = V_{CT} + 100 \text{mVp-p}, f = 5 \text{MHz}$                                                  | 50       |     |     | dB     |

| Power Supply Rejection Ratio      | PSRR             | $V_{DD}$ or $V_{CC} = 100$ m $V_{P-P}$ , $f = 5$ M $Hz$                                                 | 45       |     |     | dB     |

| Channel Separation                | cs               | V <sub>IN</sub> = 100mVp-p, f = 5MHz<br>Three Channel Driven, Selected<br>Channel Measured              | 45       |     |     | dB     |

| Output Offset Voltage             | Vos              |                                                                                                         | -400     |     | 400 | mV     |

| Common Mode Output Voltage        | Vосм             |                                                                                                         | 5        |     | 7   | ٧      |

| Head Center Tap Voltage           | VCT              |                                                                                                         |          | 4.2 | L   | ٧      |

| Single-Ended Output<br>Resistance | R <sub>SEO</sub> |                                                                                                         |          |     | 30  | Ω      |

WRITE CHARACTERISTICS Unless otherwise specified,  $V_{DD1} = V_{DD2} = 12V \pm 10\%$ ,  $V_{CC} = 5V \pm 10\%$ ,  $T_A = 25^{\circ}C$ ,  $I_W = 45$ mA,  $L_H = 0.72$ µH,  $R_H = 20\Omega$ ,  $R_D = 750\Omega$ ,  $I_{DATA} = 5$ MHz. Note: The peak differential head voltage must be limited to 6V maximum i.e. at  $I_W = 5$ 0mA,  $L_{MAX} = 1.2$ µH.  $L_{MAX}$  varies inversely with  $I_{MAX}$ .

| PARAMETER                         | SYM             | CONDITIONS                                                 | MIN   | TYP | MAX   | UNITS  |

|-----------------------------------|-----------------|------------------------------------------------------------|-------|-----|-------|--------|

| Write-Current Range               | ۱w              | (see table and note on next page)                          | 10    |     | 50    | mA     |

| Differential Head Voltage         | VDH             |                                                            |       | 3.5 |       | Vpk    |

| Unselected Head Current           | IUH             |                                                            |       |     | 2     | mA p-p |

| Current Gain                      | Aı              |                                                            |       | 20  |       | mA/mA  |

| Head-Center Tap Voltage           | Vст             |                                                            |       | 6.5 |       | V      |

| Head-Current<br>Propagation Delay | <sup>t</sup> PD | $L_H$ = 0 $\mu$ H, R $_H$ = 0 $\Omega$ , 50% WDI to 50% IW |       |     | 30    | ns     |

| Rise/Fall Time                    | tr,tf           | L <sub>H</sub> = 0μH, R <sub>H</sub> = 0Ω, 10% to 90%      |       | 5   | 20    | ns     |

| Symmetry                          | s               | (t <sub>f</sub> - t <sub>f</sub> )/2                       |       | 0.3 | 2     | ns     |

| Write Current Tolerance           | ΔIW             | R <sub>WC</sub> = 3111Ω                                    | 42.75 | 45  | 47.25 | mA     |

| Differential Output Resistance    | ROUT            | VM118                                                      | 10    |     |       | ΚΩ     |

| Differential Output Resistance    | 1.001           | VM118R                                                     |       |     | 750   | Ω      |

| Differential Output Capacitance   | COUT            | f = 5MHz                                                   |       |     | 15    | pF     |

#### **EXTERNAL RESISTOR vs WRITE CURRENT**

| ly Into the selected Head terminal X or Y with VCT shorted only to the respective X or Y terminal. |                          |  |  |  |

|----------------------------------------------------------------------------------------------------|--------------------------|--|--|--|

| External Resistor<br>R wc (KΩ)                                                                     | Write Current<br>Iw (mA) |  |  |  |

| 14.810                                                                                             | 10                       |  |  |  |

| 7.205                                                                                              | 20                       |  |  |  |

| 4.753                                                                                              | 30                       |  |  |  |

| 3.517                                                                                              | 40                       |  |  |  |

| 3.111                                                                                              | 45                       |  |  |  |

| 2.786                                                                                              | 50                       |  |  |  |

Note: The effective current  $I_{FLUX}$  generated in the magnetic head is related to  $I_W$  by the following expression:

$$I_{FLUX} = I_W \left( \frac{R_D}{R_H + R_D} \right)$$

Where  $R_H$  equals the full coil resistance of a center tapped ferrite head and  $R_D$  is the damping resistor connected internally or externally between the X and Y terminals.

SWITCHING CHARACTERISTICS Unless otherwise specified,  $V_{DD1}$  =  $V_{DD2}$  =  $12V \pm 10\%$ ,  $V_{CC}$  =  $5V \pm 10\%$ ,  $T_A$  =  $25^{\circ}$ C,  $T_{W}$  = 45mA,  $T_{H}$  = 0.72 $\mu$ H,  $T_{H}$  =  $20\Omega$ ,  $T_{D}$  =  $750\Omega$ ,  $T_{D}$

| PARAMETER                            | SYM             | CONDITIONS                                                                         | MIN | TYP | MAX | UNITS |

|--------------------------------------|-----------------|------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Read-to-Write Switching<br>Delay     | <sup>t</sup> RW | 50% of R/W to<br>90% of Write Output Envelope                                      |     |     | 1   | μs    |

| Write-to-Read Switching<br>Delay     | twR             | 50% of R/W to<br>90% of 100mVp-p RDX, RDY<br>Envelope                              |     |     | 1   | μѕ    |

| Idle-to-Write Switching<br>Delay     | tıw             | 50% of CS to<br>90% of Write Output Envelope                                       |     |     | 1   | μs    |

| Idle-to-Read Switching<br>Delay      | <sup>t</sup> IR | 50% of CS to<br>90% of 100mVp-p RDX, RDY<br>Envelope                               |     |     | 1   | μs    |

| Write-to-idle Switching<br>Delay     | twi             | 50% of CS to<br>10% of Write Output Envelope                                       |     |     | 1   | μs    |

| Read-to-Idle Switching<br>Delay      | <sup>t</sup> RI | 50% of CS to<br>10% of RDX, RDY Envelope                                           |     |     | 1   | μs    |

| Head Select Switching<br>Delay       | <sup>t</sup> HS | 50% of HS Transition to 90% of<br>100mVp-p RDX, RDY Envelope<br>from Selected Head |     |     | 1   | μs    |

| Write Unsafe Delay<br>Safe-to-Unsafe | <sup>t</sup> D1 | Gate WDI. Measure from 50% of Last Data Pulse to 50% WUS                           | 1.6 |     | 8   | μs    |

| Write Unsafe Delay<br>Unsafe-to-Safe | t <sub>D2</sub> | Gate WDI. Measure from 50% of Falling Edge of First Data Pulse to 50% WUS          |     |     | 1   | μs    |