# MT32018 MT32028

**ENCODER/DECODER**

/ww.DataSheet4U.com

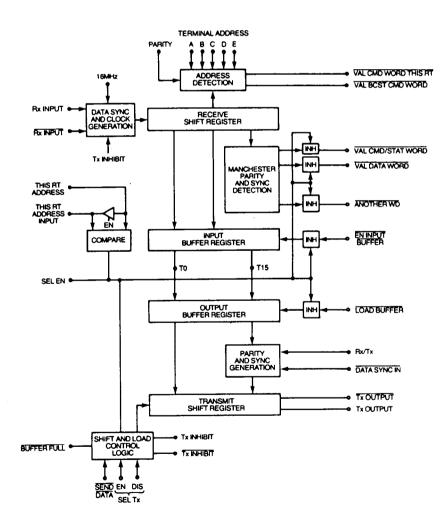

### SIMPLIFIED BLOCK SCHEMATIC

#### **FEATURES**

- COMPLIANT TO 1553

- COMPLETE WORD VALIDATION

- OPTIONAL WATCHDOG TIMER

- PARALLEL DATA INTERFACE

- LOW POWER CMOS TECHNOLOGY

#### **GENERAL**

The decoder half of this single monolithic device handles all the word validation required by 1553. It receives serial data via a transceiver, checks for valid Manchester bi-phase, parity, sync field and terminal address and provides a 16 bit parallel data output

The encoder takes a 16-bit parallel input, converts it to Manchester bi-phase, adds sync and parity and transmits via a transceiver

The MT32018 inhibits the receiver during transmission.

The MT32028 can receive its own transmissions provided the receive half of the transceiver is not inhibited

#### RECEIVE MODE

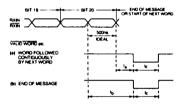

The device requires an active low signal of 250ns minimum applied to RESET with POWER ON. Command/status words or data words consisting of 20 bits (Manchester code) are senally received at the RXIN and RXIN inputs (RXIN is the inverse of RXIN) via transceiver at a bit rate of 1MHz. The data chronised with a 16MHz free-running clock and shifted into a 40 bit shift register (2 bits of shift register for 1 Manchester code bit). The first 3 bits to be received contain either the command/status sync Or data sync which are invalid Manchester code

The first 6 hits of the shift register (3 data bits) are being continually monitored detecting either command/status sync or data sync. When a command/status sync or data sync is detected, the data in the shift register is checked for correct Manchester coding and odd parity. If there are no errors (i.e. valid word) the 16 data bits in the shift r (bits 4-19) are transferred to the input buffer register

When a command word is received the most significant 5 bits of the command are compared with the hard-wired terminal address (ADDR E being the most significant bit). The 5 bit hard-wired terminal address pins and address parity pin are checked for odd parity. If the parity is correct and the address compares then a "valid RT address" has been

If the most significant 5 bits of the command are all at a "I" then a "valid broadcast address" has been

Output signal VAL CMD WORD THIS RT becomes valid for 500ns if a command sync has b vawo rur ovuns if a command sync has been detected along with valid word and valid RT address. If valid broadcast address was detected instead of valid RT address then the signal VALID BCST CMD WORD becomes valid for 500ns.

When VALID CMD WORD THIS RT or VALID BCST CMD WORD becomes valid the hard-wired bus address (THIS RT ADDR) is enabled to the I/O pin THIS RT ADDR IP for the same period of 500ns.

The I/O pin (THIS RT ADDR IP) is being continuously compared with the hard-wired bus address (THIS RT ADDR). If equal then SEL EN

To select which bus is to be used for transmitting and receiving, the input (THIS RT ADDR IP) must be set to the same logical state as the hard-wired bus address (THIS RT ADDR).

Output signal VAL CMD/STAT WORD become Couput signal water Colley's IAT WORD becomes valid for 500ns if a command/stabus sync has been detected along with valid word, provided SEL EN is valid. If a data sync was detected instead of a command/status sync then the signal VALID DATA WORD becomes valid for 500ns.

The last 12 bits of the shift register are being continuously monitored to give early warning of a new word being received, i.e. a command/status/ data sync plus 3 bits of correct Manchester coding. If this has been detected the output ANOTHER WORD becomes valid for 500ns providing SEL EN is valid.

With SEL EN valid the contents of the input buffe register can be enabled onto the 16 bit I/O highw T0-T15 (T15 being the most significant) via signal EN INPUT BUFFER being active low.

Also with SEL EN valid the transmit circuitry is

#### TRANSMIT MODE

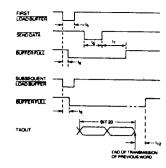

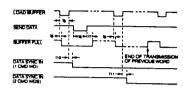

To transmit data from the device the signal SELEN must be valid. Data present on the 16 bit I/O highway to be transmitted is loaded into the output buffer register with input signal LOAD BUFFER.

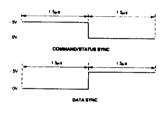

The command/status sync or data sync is internally generated and is also loaded into the register to be the first 3 bits of transmission. The status sync waveform is the same as the command sync waveform. From this register a parity bit is generated

The only exception to the automatic sync generation is for a Bus Controller to issue an RT to RT transfer command (i.e. two consecutive command words) This is achieved by setting RX/TX to a zero and the type of sync is determined by the signal DATA SYNC IN ('1' = CMD SYNC, '0' = DATA SYNC) during LOAD BUFFER

To initialise transmission an active low signal on SEND DATA is required. Data will be transferred from the output buffer register, converted to Manchester code, and loaded into the 40 bit shift register and shifted out via TXOUT and TXOUT (TXOUT is the inverse of TXOUT during transmission, and both are high with no transmission) to the transceiver. If LOAD BUFFER is applied before the end of transmission, then the transmit sequence will be repeated when the full 20 bit word has been transmitted with no inter-word gap.

When transmission is taking place and there is another word waiting in the output buffer for transmission, the output signal BUFFER FULL becomes valid. If COAD BUFFER becomes valid the contents of the buffer are overwritten

In an RT the first word for transmission v the status word and the top 5 bits of status are the remote terminal address. There are two methods of loading this address along with status into the buffe register

- register.

(a) The terminal address may be applied to the highway (T11-T15, T15 being MSB terminal address E) along with the rest of the status word and loaded into the buffer with LOAD BUFFER. To initiate transmission, SEND DATA is applied along with LOAD BUFFER or any time after LOAD BUFFER. (The terminal address being the same artifless as the transmitting desired.) same address as the transmitting device)

- (b) If bits T11-T15 are left high impedance with the II ons 111-115 are left high impedance with the status enabled onto To-T10 then the hard-wired terminal address will be internally enabled onto T11-T15 with signal SEND DATA. Therefore COAD BUFFER must be applied during SEND DATA.

There are 2 other inputs to the device, SEL TX EN and SEL TX DIS. When SEL EN is valid, a pulse on SEL TX DIS disables transmission and a pulse on SEL TX EN enables transmission. (Min pulse width 250ns).

An active low signal on RESET will set the transmitter in the enable mode.

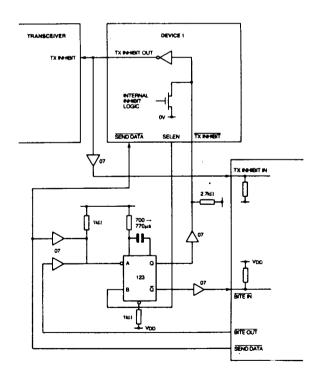

During a message transmission the output TX INHIBIT is also available to connect an external Watchdoo Timer. If the Timer is not required this pin may be left open circuit.

#### DETAILED TIMING

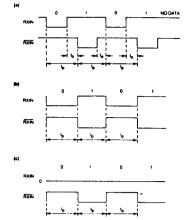

RXIN Waveform Requirements There are three variations of waveform requirements required at the RXIN and RXIN inputs.

Waveform (a) is the ideal, With waveform (b) applied, the device is less immune to noise on these nputs than waveform (a). With waveform (c) applied, the device is less immune to noise on these inputs than waveform (b).

The device will accept waveforms with to varying from the ideal (including rise and fall times) of  $\pm$  180ns (i.e.  $2.0 \pm 0.18\mu s$ ,  $1.5 \pm 0.18\mu s$ ,  $1.0 \pm$ 0.18μs, 0.5 ± 0.18μs) (The tolerance required by the 1553B standard is ±0.15µ8.)

Overlap period (to) 10ns minimum 400ns maximum.

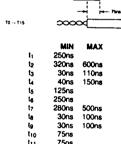

Propagation Delays Propagation delays over free air temperature range V<sub>DD</sub> = 5 Volts. Propagation delays do not include rise and fall time of outputs.

Propagation delay time RXIN or RXIN to VALID DATA WORD, VALID CMD WD THIS RT, VALID ECST CMD WORD, VALID CMD/STATUS

- ta 300ns minimum 480ns maximum

- 800ns minimum 980ns maximum. 460ns minimum 540ns maximum: for ideal RXIN

#### Propagation delay time

|                                       | MIN  | MAX  |

|---------------------------------------|------|------|

| EN IP BUFFER to T0 - T15              | 20ns | 75ns |

| VAL WORD to T0 - T15                  | 15ns | 50ns |

| VALID CMD WD THIS RT/BCST to          |      |      |

| THIS RT ADDR IP                       | 25ns | 150n |

| (remains enabled for half bit period, |      |      |

| COOnsides!                            |      |      |

THIS RT ADDR IP to SEL EN 65ns 200ns

### 16 MHz Clock Requirement

40% 60% of cycle Frequency 16MHz ± 0.01%

## Propagation delay time SEND DATA to TXOUT, TX INH.

Propagation delay time LOAD BUFFER to BUFFER FULL.

Propagation delay times for LOAD BUFFER ations (external sync generation).

DATA SET OF THE

The first load buffer may occur any time before SEND DATA but no later than SEND DATA i.e.

112

230ns

370ns

tset up MIN = Ons

In a BC if RXTX is high (internal sync generation then LDBF must occur before SEND DATA and teet up will apply to rising edge of LD BF

If the device is required to internally load its own RT address to be transmitted with status, then the send data and load buffer signals must be as shown.

#### **OPERATING CONDITIONS Absolute Maximum Ratings**

Supply voltage V<sub>DO</sub> Supply voltage V<sub>SS</sub> Low level input voltage High level i nput voltage Operating free air te

+ 7 Volts 0 Volts Vss -0.5 Volts V<sub>DO</sub> +0.5 Volts

range Storage temperature range

-55℃ to +125℃ 65°C to +150°C

MAX UNIT Supply voltage V<sub>DD</sub> Volts 5.5 Operating free air -55 +125 www.DataSheet4U.com

#### DYNAMIC ELECTRICAL CHARACTERISTICS

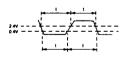

Over free air temperature range  $V_{00}$  = 5 Volts Rise time of output Vss to 3 Volts into 20pF load = 50ns maximum. Fall time of output  $V_{00}$  to 0.4 Volts into 20pF load = 50ns maximum.

#### STATIC ELECTRICAL CHARACTERISTICS

Over recommended free air temperature range  $V_{DO} = 5$  volts

| CARL LECTRIFICATION LINE WY TO           | inperatore range v <sub>00</sub> = .    | J 1010 |                                 |                 |

|------------------------------------------|-----------------------------------------|--------|---------------------------------|-----------------|

|                                          | MIN                                     | NOM    | MAX                             | UNIT            |

| Input Type 'A'                           |                                         |        |                                 |                 |

| V <sub>M</sub> High level input voltage  | 2.4                                     |        | Voo                             | Volts           |

| Vs. Low level input voltage              | ∨ <sub>ss</sub>                         |        | 0.8                             | Volts           |

| C <sub>IN</sub> Input capacitance        |                                         |        | 10                              | pf              |

| Input Type 'B'                           |                                         |        |                                 |                 |

| V <sub>M</sub> High level input voltage  | 2.4 or OC if unused                     |        | V <sub>DO</sub> or OC if unused | Volts           |

| V <sub>II</sub> Low level input voltage  | Vss                                     |        | 0.8                             | Volts           |

| le Low level input current               |                                         |        | 0.8                             | mA              |

| C <sub>H</sub> Input capacitance         |                                         |        | 10                              | pf              |

| •                                        |                                         |        |                                 |                 |

| Input Type 'C'                           |                                         |        | Vno or OC if unused             | Volts           |

| V <sub>BH</sub> High level input voltage | 2.4 or OC if unused                     |        | 0.8                             | Volts           |

| V <sub>IL</sub> Low level input voltage  | V <b>s</b> s                            |        | 0.8                             | mA.             |

| I <sub>IL</sub> Low level input current  |                                         |        | 10                              | of.             |

| C <sub>IN</sub> Input capacitance        |                                         |        | 10                              | ρı              |

| Input Type 'D'                           |                                         |        |                                 |                 |

| V <sub>IH</sub> High level input voltage | 2.4                                     |        | Voo                             | Volts           |

| V <sub>IL</sub> Low level input voltage  | Vss or OC if unused                     |        | 0.8 or OC if unused             | Volts           |

| In High level input current              |                                         |        | 0.4                             | mA              |

| C <sub>IN</sub> Input capacitance        |                                         |        | 10                              | ρf              |

| Output Type 'E'                          |                                         |        |                                 |                 |

| Von High level output voltage            | 4.5                                     |        | VDO                             | Volts           |

| Vol. Low level output voltage            |                                         |        | 0.4                             | Volts           |

| IOH High level output current            | 1.0                                     |        |                                 | mA              |

| lot Low level output current             | -3.2                                    |        |                                 | mΑ              |

| 0 4 4 5 - 45 ( decis)                    |                                         |        |                                 |                 |

| Output Type 'F' (open drain)             |                                         |        | oc                              |                 |

| Von High level output voltage            | · • • • • • • • • • • • • • • • • • • • |        | 0.4                             | Volts           |

| Vol. Low level output voltage            | -3.2                                    |        | 0.4                             | mA              |

| IoL Low level output current             | -3.2                                    |        |                                 | 1745            |

| Input/Output Type 'G'                    |                                         |        |                                 |                 |

| V <sub>IH</sub> High level input voltage | 2.4                                     |        | Vpo                             | Volts           |

| Vil. Low level input voltage             | Vss                                     |        | 0.8                             | Volts           |

| Von High level output voltage            | 4.5                                     |        | Voo                             | Volts           |

| Vol. Low level output voltage            |                                         |        | 0.4                             | Volts           |

| IOH High level output current            | 1.0                                     |        |                                 | mĄ              |

| lor Low level output current             | -3.2                                    |        |                                 | mΑ              |

| C <sub>IO</sub> I/O Capacitance          |                                         |        | 10                              | pt <sub>.</sub> |

| Supply current                           |                                         | 2.5    | 5.0                             | mA              |

|                                          |                                         |        |                                 |                 |

#### WATCHDOG TIMER

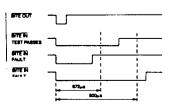

If a device fails in such a way as to continuously transmit, the Watchdog Timer will inhibit the transceiver from transmitting the data onto the bus. The function of the Watchdog Timer may be test by the use of the BITEOUT and BITEIN signals.

#### MNEMONICS

| T0→ T15              | 16 bit bi-directional highway                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------|

| ADDR A → E           | Hard wired RT address (ADDR E is MSB)                                                                          |

| ADDR PARITY          | Hard wired address parity (odd)                                                                                |

| AXIN }               | Manchester bi-phase input from transceiver                                                                     |

| SEL EN               | Watchdog Timer control                                                                                         |

| RESET                | General reset                                                                                                  |

| TXOUT }              | Manchester bi-phase output to transceiver                                                                      |

| TX INHIBIT           | Transmit inhibit to transceiver                                                                                |

| TXINHIBIT            | Watchdog Timer input                                                                                           |

| SEL TX DIS           | Disable transmitter                                                                                            |

| SEL TX EN            | Enable transmitter                                                                                             |

| 16MHz                | 16MHz Crystal Oscillator                                                                                       |

| THIS RT ADDR         | Hard-wired bus address                                                                                         |

| DATA SYNC IN         | External control of sync generation                                                                            |

| VAL CMD WORD THIS RT | Signal from Encoder/Decoder – received valid command word with terminal's address.                             |

| VAL BOST CMD WORD    | Signal from Encoder/Decoder – received valid command word with broadcast address.                              |

| VAL CMD/STAT WORD    | Signal from Encoder/Decoder – received valid command/status word on selected bus.                              |

| VAL DATA WORD        | Signal from Encoder/Decoder - received valid data word on selected bus.                                        |

| ANOTHER WORD         | Signal from Encoder/Decoder – received early warning of another word on selected bus.                          |

| THIS RT ADDR IP      | Bi-directional signal to/from encoder/decoder – sets up bus selection.                                         |

| EN IP BUFFER         | Control signal to encoder/decoder to enable received data onto highway.                                        |

| SEND DATA            | Control signal to encoder/decoder to initiate transmission.                                                    |

| LOAD BUFFER          | Control signal to encoder/decoder to load data ready for transmission.                                         |

| BUFFER FULL          | Control signal from encoder/decoder indicating that the transmit buffer register is full. $\label{eq:control}$ |

|                      |                                                                                                                |

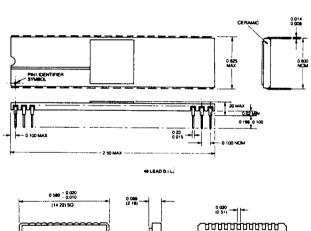

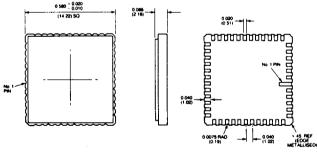

#### MECHANICAL CHARACTERISTICS

### PIN ASSIGNMENTS

| PIN NO. | SIGNAL          | IO TYPE | PIN NO.    | SIGNAL               | Ю ТҮРЕ |

|---------|-----------------|---------|------------|----------------------|--------|

| 1       | T1              | G       | 25         | T10                  | G      |

| 2       | T2              | G       | 26         | T11                  | G      |

| 3       | Т3              | G       | 27         | T12                  | G      |

| 4       | T4              | G       | 28         | T13                  | Ġ      |

| 5       | T5              | G       | 29         | T14                  | G      |

| 6       | Т6              | G       | 30         | T15                  | G      |

| 7       | 17              | Ğ       | 31         | TERM ADDR E          | Č      |

| 8       | RESET           | A       | 32         | TERM ADDR D          | Ċ      |

| 9       | LOAD BUFFER     | A       | 33         | TERM ADDR C          | Č      |

| 10      | BUFFER FULL     | F       | 34         | TERM ADDR B          | С      |

| 11      | SEL EN          | Ε       | 35         | TERM ADDR A          | Ċ      |

| 12      | SEND DATA       | A       | 36         | VAL CMD/STAT WORD    | F      |

| 13      | TXOUT           | Ε       | 37         | ANOTHER WORD         | F      |

| 14      | TX OUT          | E       | 38         | VAL BCST CMD WORD    | F      |

| 15      | TX INHIBIT      | В       | 39         | VAL CMD WORD THIS RT | F      |

| 16      | TX INHIBIT      | E       | 40         | ADDR PARITY          | С      |

| 17      | THIS RT ADDR    | A       | 41         | PEXIN                | A      |

| 18      | RX/TX           | С       | 42         | RXIN                 | A      |

| 19      | DATA SYNC IN    | С       | 43         | 16MHz                | A      |

| 20      | THIS RT ADDR IP | G       | 44         | VALID DAYA WORD      | F      |

| 21      | EN IP BUFFER    | A       | 45         | SELTX EN             | A      |

| 22      | Vss             |         | 46,,,,     | Dat SEUJX DISALLA    | n ma A |

| 23      | T8              | G       | 12/52/17/1 | ı.DataS∜∦ĕef4U.cı    | וווע   |

| 24      | T9              | G       | 48         | TO                   | G      |

|         |                 |         |            |                      |        |

MANAY DataShoot411 cor

Micro Circuit Engineering Limited

Alexandra Way, Ashchurch, Tewkesbury

Gloucestershire GL20 8TB

Telephone Tewkesbury (0684) 297777

Telex 437233 Fax (0684) 299435

BSI Approval No. 1267/M