## **STV0117**

### PAL/NTSC DIGITAL ENCODER

- NTSC-M, PAL-M, PAL-B, D, G, H, I, PAL-N EASILY PROGRAMMABLE VIDEO OUTPUTS

- U/V AND Q/I MATRIXING FOR RESPEC-TIVELY PAL AND NTSC ENCODING

- DIGITAL FRAME SYNC INPUT/OUTPUT (ODDEVEN)

- DIGITAL FRAME SYNC EXTRACTION FROM MULTIPLEXED 8-BIT INPUT PORT

- DIGITAL FIELD SYNC OUTPUT (FSYNC)

- DIGITAL COMPOSITE SYNC OUTPUT (VCS/HSYNC = VCS)

- DIGITAL HORIZONTAL SYNC INPUT/OUT-PUT (VCS/HSYNC = HSYNC)

- 3 SLAVE OR 2 MASTER OPERATION MODES

- DUAL MODE CCIR601/SQUARE\_PIXEL EN-CODING WITH EASILY PROGRAMMABLE COLOR SUBCARRIER FREQUENCIES

- INTERLACED OR NON-INTERLACED OPERATION MODE

- 625LINES/50Hz or 525LINES/60Hz 8-BIT MULTIPLEXED CB-Y-CR DIGITAL INPUT

- OSD INSERTION INTERFACE AND 3 x 8 x 6-BIT CLUT

- CLOSED CAPTIONING

- MACROVISION<sup>™</sup> COPY PROTECTION PROCESS (**VERSION 6.0/6.1**) ALLOWED ON CVBS, YS & C

- LUMINANCE FILTERING WITH 2 TIMES OVERSAMPLING AND SINX/X CORREC-TION

- PROGRAMMABLE DELAY ON LUMINANCE PATH TO DIGITALLY COMPENSATE C/L DE-LAYS

- CHROMINANCE FILTERING WITH 4 TIMES OVERSAMPLING

- SWITCHABLE DEDICATED FILTER FOR Q COMPONENT

- 22-BIT DIRECT DIGITAL FREQUENCY SYN-THESIZER FOR COLOR SUBCARRIER MODULATION

- SERIAL INPUT FOR COLOR SUBCARRIER FREQUENCY CONTROL (CFC)

- CVBS, YS AND C SIMULTANEOUS ANALOG OUTPUTS THROUGH 9-BIT DACS

- CONTROLLED RISE/FALL TIMES OF ANA-LOG SYNCHRONIZATION OUTPUT

- POWER-DOWN MODE AVAILABLE INDE-PENDENTLY ON EACH DAC

- 9-BIT DIGITAL INPUT FOR DIGITIZED ANA-LOG VIDEO WITH DIRECT ACCESS TO CVBS DAC

- EASILY CONTROLLED VIA I<sup>2</sup>C BUS

- 2 HARDWARE I<sup>2</sup>C CHIP ADDRESSES

- ON-CHIP COLOR BAR PATTERN GENERATOR

- HIGH TESTABILITY WITH FULL SCAN METHODOLOGY (FAULT COVERAGE 98%)

- PIN COMPATIBILITY WITH STV0116 (PAL/NTSC DIGITAL ENCODER WITH R, G, B OUTPUTS)

- APPLICATIONS : SATELLITE & CABLE DE-CODERS, MULTIMEDIA TERMINALS

#### **DESCRIPTION**

The STV0117 is a digital video device implemented in pure CMOS technology for multimedia, digital TV and computer applications.

The STV0117 converts the digital output of a Video MPEG Decoder into a standard analog baseband NTSC/PAL signal with color subcarrier modulation. The STV0117 can handle interlaced mode (with 525 or 625 line standards), or non-interlaced mode (with 524 or 624 line standards), with square or rectangular pixels encoding. The STV0117 performs closed captions encoding and allows MACROVISION™ 6.0/6.1 copy protection process. Both composite and SVHS format video signals are simultaneously issued to three analog outputs, respectively CVBS, YS and C.

Note: This device is protected by US patent numbers 4631603, 4577216 and 4819098 and other intellectual property rights. This device is protected by U.S. patent numbers 4,631,603, 4,577,216 and 4,819,098 and other intellectual property rights. The use of Macrovision's copy protection technology in the device must be authorized by Macrovision and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is prohibited. Please contact your nearest SGS-THOMSON Microelectronics sales office for more information.

May 1996 1/45

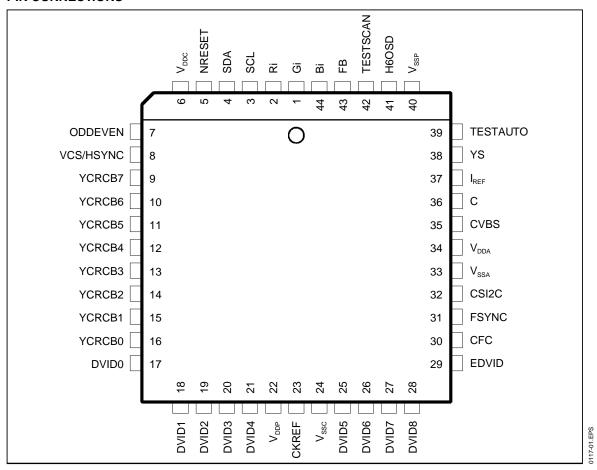

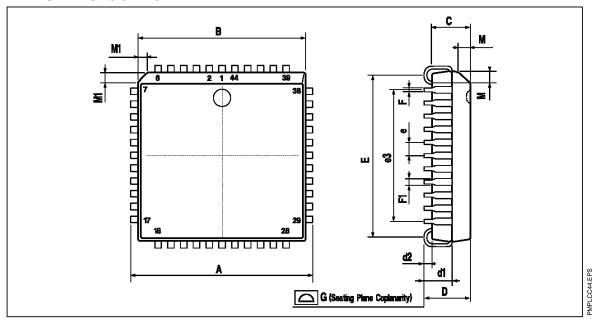

### **PIN CONNECTIONS**

### **PIN DESCRIPTION**

| Pin                                         | Symbol                                                                       | Type            | Function                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                           | Gi                                                                           | Input           | Second pixel index for 3 x 1-bit OSD input.  Minimum OSD_pixel width is one H6OSD period.                                                                                                                                                                                                                                                                                                                                |

| 2                                           | Ri                                                                           | Input           | First pixel index (MSB) for 3 x 1-bit OSD input.  Minimum OSD_pixel width is one H6OSD period.                                                                                                                                                                                                                                                                                                                           |

| 3                                           | SCL                                                                          | Triggered Input | I <sup>2</sup> C serial clock line (internal 5-bit majority logic).                                                                                                                                                                                                                                                                                                                                                      |

| 4                                           | SDA                                                                          | I/O             | I <sup>2</sup> C serial data line triggered input (internal 5-bit majority logic).<br>Open drain output, minimum LOW level duration 200ns.                                                                                                                                                                                                                                                                               |

| 5                                           | NRESET                                                                       | Input           | Asynchronous reset, active LOW. It has priority over software reset (see I <sup>2</sup> C REGISTER4). NRESET imposes default states (see I <sup>2</sup> C REGISTERS DESCRIPTION and reset procedure in FUNCTIONAL DESCRIPTION).  Minimum LOW level required duration is 5 CKREF periods.                                                                                                                                 |

| 6                                           | VDDC                                                                         | Supply          | Digital positive supply voltage for core (+5V).                                                                                                                                                                                                                                                                                                                                                                          |

| 7                                           | ODDEVEN                                                                      | I/O             | ODDEVEN video frame signal: - input in slave modes, except when SYNC is extracted from YCRCB data, - output in master modes and when SYNC is extracted from YCRCB data. Synchronous to rising edge of CKREF. Default polarity: - odd(top) field: HIGH level, - even(bottom) field: LOW level. Default mode is slave by ODDEVEN and HSYNC, both with rising active edge.                                                  |

| 8                                           | VCS/HSYNC                                                                    | I/O             | Composite or horizontal synchronization signal: - input in one slave mode: HSYNC input (defined by sym2 = 1), - output in other modes: VCS or HSYNC. Synchronous to rising edge of CKREF. Default polarity: leading edge of the pulse is rising Default mode is slave by ODDEVEN and HSYNC, both with rising active edge.                                                                                                |

| 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | YCRCB7<br>YCRCB6<br>YCRCB5<br>YCRCB4<br>YCRCB3<br>YCRCB2<br>YCRCB1<br>YCRCB0 | Input           | Time multiplexed 4:2:2 luminance and chrominance data as defined in CCIR Rec601-2 and Rec656 (except for TTL input levels). Timing Rec656-partII for CCIR rectangular pixels; for square pixels data see chapter DATA INPUT FORMAT in FUNCTIONAL DESCRIPTION. This bus interfaces with MPEG video decoder output port.                                                                                                   |

| 17<br>18<br>19<br>20<br>21                  | DVID0<br>DVID1<br>DVID2<br>DVID3<br>DVID4                                    | I/O             | Input (default mode): 5 LSBs of digitized analog video for direct access to CVBS 9-bit DAC inputs. Enabled by software or/and by hardware. Tristate output for test purpose only.                                                                                                                                                                                                                                        |

| 22                                          | V <sub>DDP</sub>                                                             | Supply          | Digital positive supply voltage for pad ring (+5V).                                                                                                                                                                                                                                                                                                                                                                      |

| 23                                          | CKREF                                                                        | Input           | Clock reference signal: rising edge is the reference for setup and hold times of all inputs, and for propagation delay of all outputs (except for SDA output). Frequency is 27MHz in CCIR601 and in square pixel mode: 24.5454MHz or 29.50MHz.                                                                                                                                                                           |

| 24                                          | V <sub>SSC</sub>                                                             | Supply          | Digital ground for core.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 25<br>26<br>27<br>28                        | DVID5<br>DVID6<br>DVID7<br>DVID8                                             | I/O             | Input (default mode): 4 MSBs of digitized analog video for direct access to CVBS 9-bit DAC inputs.  Enabled by software or/and by hardware.  Tristate output for test purpose only.                                                                                                                                                                                                                                      |

| 29                                          | EDVID                                                                        | Input           | Hardware control signal for DVID inputs select when this control is allowed by software:  - if EDVID is HIGH level, then DVID data is enabled and DVID data is an input for CVBS 9-bit DAC,  - if EDVID is LOW level, then DVID data is disabled and DVID data is ignored for CVBS 9-bit DAC.  When this control is disabled by software: DVID[8:0] inputs are controlled by software whatever the level on EDVID input. |

### PIN DESCRIPTION (continued)

| Pin | Symbol           | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

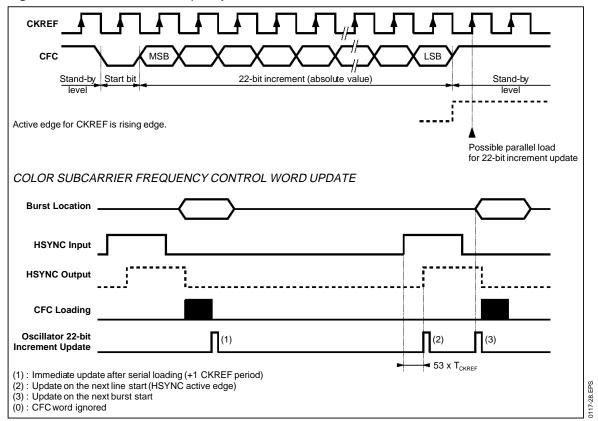

| 30  | CFC              | Input  | Color subcarrier frequency control line: 23-bit stream line, synchronous to CKREF.  In standby mode, CFC must be at HIGH level.  Reception starts with one LOW level bit and then a 22-bit word is received for increment of color subcarrier direct digital frequency synthesizer, and then line returns to standby mode i.e at HIGH level.  This real time control is enabled by software and is a color lock interface. This line is ignored by default. |

| 31  | FSYNC            | Output | Field synchronization signal, synchronous to CKREF. It is a horizontal sync signal generated every field beginning. Default polarity is positive (like HSYNC).                                                                                                                                                                                                                                                                                              |

| 32  | CSI2C            | Input  | Hardware I <sup>2</sup> C chip address select: - when LOW, I <sup>2</sup> C chip addresses are 40 and 41 hexadecimal, - when HIGH, I <sup>2</sup> C chip addresses are 42 and 43 hexadecimal.                                                                                                                                                                                                                                                               |

| 33  | V <sub>SSA</sub> | Supply | Analog ground for 3 DACs.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 34  | $V_{DDA}$        | Supply | Analog positive supply voltage for 3 DACs (+5V).                                                                                                                                                                                                                                                                                                                                                                                                            |

| 35  | CVBS             | Output | Current analog video composite signal : CVBS must be connected to analog ground over a load resistor (R <sub>L</sub> ).  Between the load resistor and the video equipment, an analog low pass filter may be necessary to suppress the alias signal.  CVBS amplitude is typically 2.48V <sub>PP</sub> on R <sub>L</sub> and is proportional to I <sub>REF</sub> .                                                                                           |

| 36  | O                | Output | Current analog chrominance signal : S-VHS output for a VCR or a TV set. C must be connected to analog ground over a load resistor (R <sub>L</sub> ). Between the load resistor and the video equipment, an analog low pass filter may be necessary to suppress the alias signal. C amplitude is typically 1.6V <sub>PP</sub> on R <sub>L</sub> and is proportional to I <sub>REF</sub> .                                                                    |

| 37  | I <sub>REF</sub> | Input  | Reference current source for the 3 x 9-bit DACs CVBS,YS,C.  IREF must be connected to analog ground over a reference resistor (R <sub>REF</sub> ).  IREF range is from 2 up to 6mA.                                                                                                                                                                                                                                                                         |

| 38  | SY               | Output | Current analog luminance with composite synchronization signal : S-VHS output for a VCR or a TV set. YS must be connected to analog ground over a load resistor (R <sub>L</sub> ). Between the load resistor and the video equipment, an analog low pass filter may be necessary to suppress the alias signal. YS amplitude is typically 2.0V <sub>PP</sub> on R <sub>L</sub> and is proportional to I <sub>REF</sub> .                                     |

| 39  | TESTAUTO         | Input  | Hardware autotest mode control, active HIGH. TESTAUTO input forces the master mode with color bar pattern outputs.                                                                                                                                                                                                                                                                                                                                          |

| 40  | V <sub>SSP</sub> | Supply | Digital ground for pad ring.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 41  | H6OSD            | Output | CKREF/4 clock signal for external OSD generator clock output stage. Synchronous to CKREF and controlled by software : inactive by default (LOW level).                                                                                                                                                                                                                                                                                                      |

| 42  | TESTSCAN         | Input  | Full scan test mode control, active HIGH. TESTSCAN must be grounded for normal operation.                                                                                                                                                                                                                                                                                                                                                                   |

| 43  | FB               | Input  | Fast blanking signal to control 3x1bit OSD inputs, active HIGH. Synchronous to H6OSD or CKREF. FB must be LOW level in autotest mode.                                                                                                                                                                                                                                                                                                                       |

| 44  | Bi               | Input  | Third pixel index (LSB) for 3 x 1-bit OSD input.  Minimum OSD_pixel width is one H6OSD period.                                                                                                                                                                                                                                                                                                                                                              |

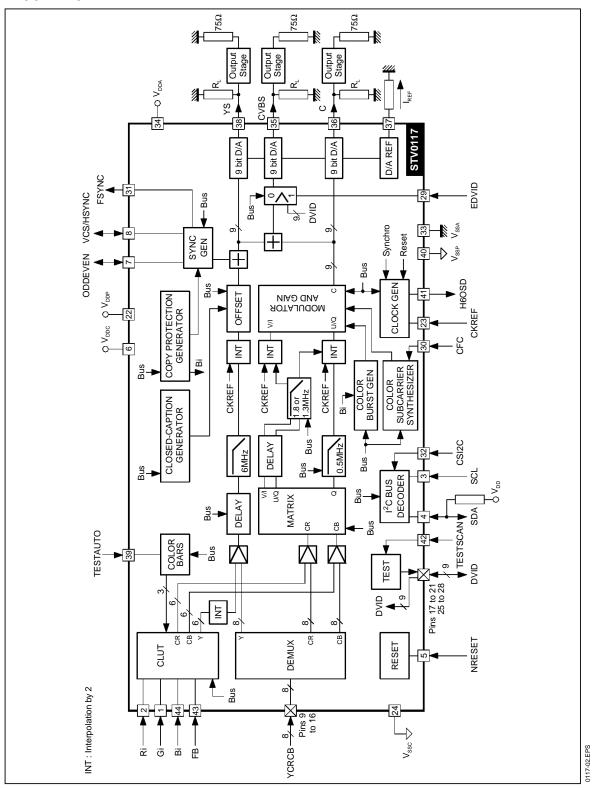

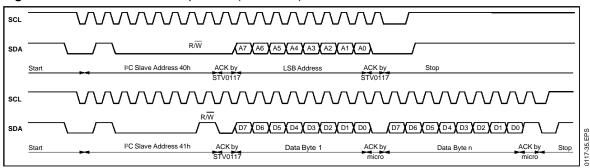

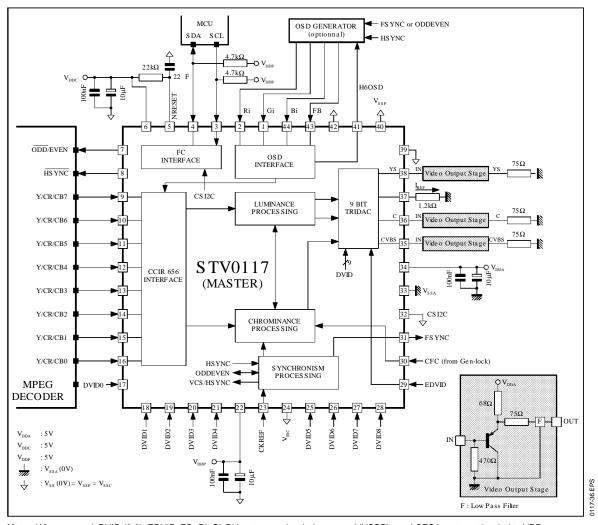

### **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

The STV0117 can operate either in slave mode by locking onto a vertical parity synchronization signal received from MPEG video decoder, or in master mode by supplying the sync signal to this device.

By using an I<sup>2</sup>C bus, it is allowed to control the following main functions:

- selection of the standard,

- synchronization mode and polarity,

- CCIR601 or square pixel data format,

- interlaced or non-interlaced mode,

- reset of the synchronization,

- luminance delay adjustment,

- chrominance filter selection,

- reset of the oscillator,

- subcarrier phase and frequency adjustment,

- color killer,

- closed captions encoding,

- MACROVISION™ 6.0/6.1 copy protection processing,

- OSD insertion,

- power-down mode for each DAC.

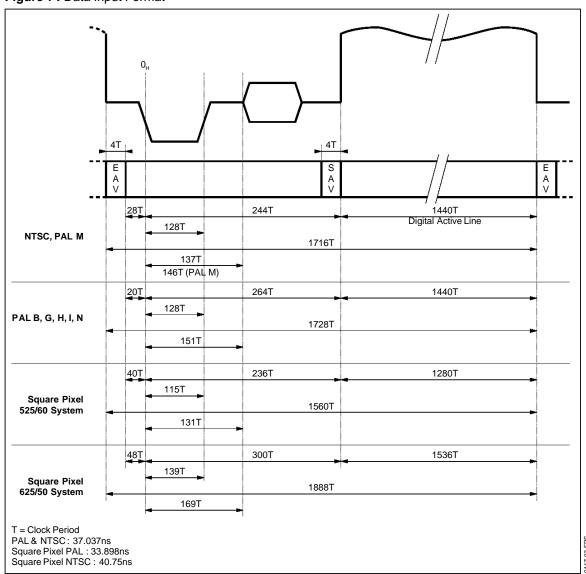

#### 1 - Data Input Format

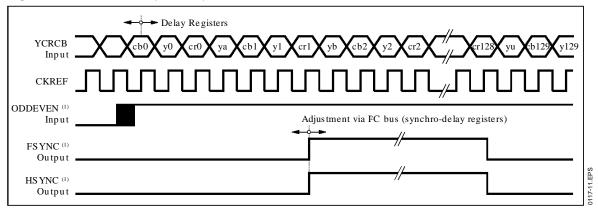

The digital input is a time multiplexed [[CB,Y,CR], Y], 8-bit stream. Input samples are taken into account on the rising edge of CKREF clock input signal (see Figure 1).

Dual mode CCIR601/square\_pixelencoding is performed with semi-automatic programmation of subcarrier frequencies from master clock (CKREF) as shown in Table 1.

Table 1

| Standard                       | Application             | CKREF<br>Frequency<br>(MHz) | Pixel Rate<br>(MHz) | Field Rate<br>(Hz) | Vertical<br>Resolution |

|--------------------------------|-------------------------|-----------------------------|---------------------|--------------------|------------------------|

| PAL-B, D,<br>G, H, I,<br>PAL-N | CCIR601                 | 27                          | 13.5                | 50                 | 625                    |

| NTSC-M,<br>PAL-M               | CCIR601                 | 27                          | 13.5                | 60                 | 525                    |

| PAL-B, D,<br>G, H, I,<br>PAL-N | Square Pixel (graphics) | 29.50                       | 14.75               | 50                 | 625                    |

| NTSC-M,<br>PAL-M               | Square Pixel (graphics) | 24.5454                     | 12.2727             | 60                 | 525                    |

The input pixel data for STV0117 has an integer relationship to the number of clock cycles per horizontal line as detailed in Table 2.

Table 2

| Standard                    | Application             | Pixel Clock<br>(MHz) | Total Pixels per Line | Active Pixels per Line |

|-----------------------------|-------------------------|----------------------|-----------------------|------------------------|

| PAL-B, D, G, H, I,<br>PAL-N | CCIR601                 | 13.5                 | 864                   | 720                    |

| NTSC-M, PAL-M               | CCIR601                 | 13.5                 | 858                   | 720                    |

| PAL-B, D, G, H, I,<br>PAL-N | Square Pixel (graphics) | 14.75                | 944                   | 768                    |

| NTSC-M, PAL-M               | Square Pixel (graphics) | 12.2727              | 780                   | 640                    |

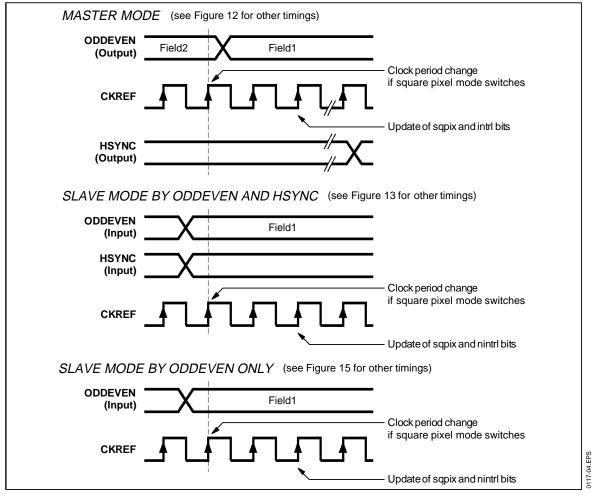

Square pixel and/or non-interlaced modes are updated on the beginning of the frame (see Figure 2).

In non-interlaced mode, it is a 624/2 = 312 line mode or a 524/2 = 262 line mode with waveforms like the first field of CCIR or SMPTE specifications (see Figures 3 to 10).

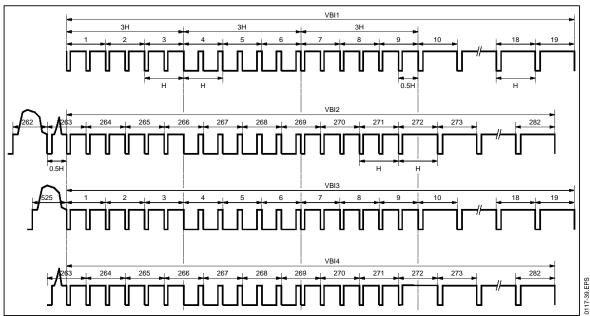

#### 2 - Video Timing

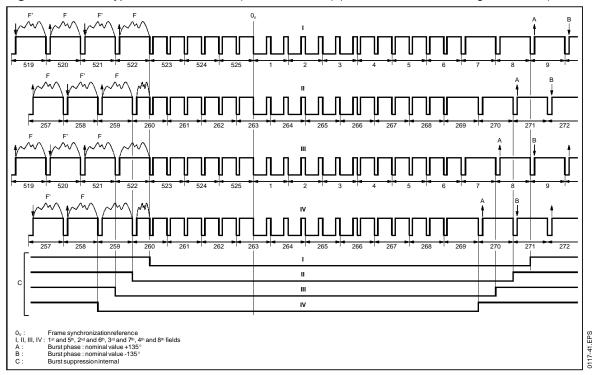

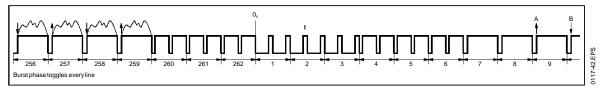

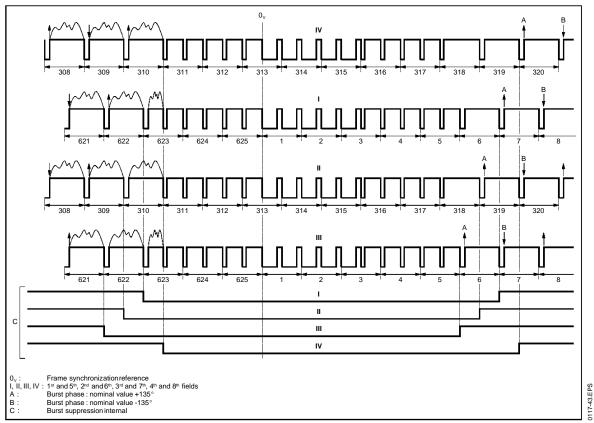

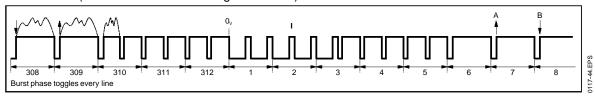

The STV0117 outputs interlaced or non-interlaced video in PAL-B, D, G, H, I, PAL-N, PAL-M or NTSC-M standards.

The 8 field (for PAL) or 4 field (for NTSC) burst sequences are internally generated, with CKREF as reference.

Rise and fall times of synchronization tip, blanking and burst envelope are internally controlled according to the composite video specification.

Lines inside Vertical Interval are blanked and others included in Blanking Interval can be blanked via  $I^2C$  controls (not assumed by default).

Vertical Blanking Interval corresponds to the following lines:

- in 525/60 system: lines 1-19 and 2nd half of line 263 to line 282 (SMPTE line number convention),

- in 625/50 system: 2nd half of line 623 to line 22 and lines 311-335 (CCIR line number convention).

Video half lines are assumed only when preceding Vertical Interval. This is the case for the following lines:

- in 525/60 system: line 263 (SMPTE line number convention),

- in 625/50 system : line 623 (CCIR line number convention).

In a CCIR656 compliant digital TV line, the "active" portion of the line is the portion included between the SAV (Start of Active Video) and EAV (End of Active Video) words.

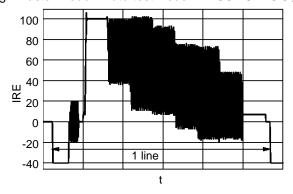

However, this digital active line starts somewhat earlier than the active line usually defined by analogue standards. The approach retained in the STV0117 is to encode the full digital line. Thus, the output waveform will reflect the full YCRCB stream included between SAV and EAV as Figure 1 re-

flects. Should it be absolutely necessary to obtain an analogue active line that starts later than the digital active line, a solution is to input a YCRCB stream that starts with samples at black level after the SAV word.

Autotest mode is operating when allowed by TESTAUTO Pin (HIGH level) or by I<sup>2</sup>C programming. This mode is a master mode which encodes a color bar pattern in the appropriate selected standard (see Figure 11).

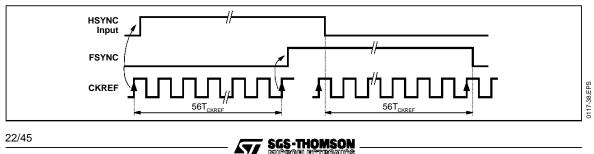

Figure 1 : Data Input Format

Note: The burst envelope shown here indicates the location from which the first subcarrier positive zero crossing is seeked (with respect to the 0H reference). The burst always start with such a positive zero crossing.

#### **FUNCTIONAL DESCRIPTION** (continued)

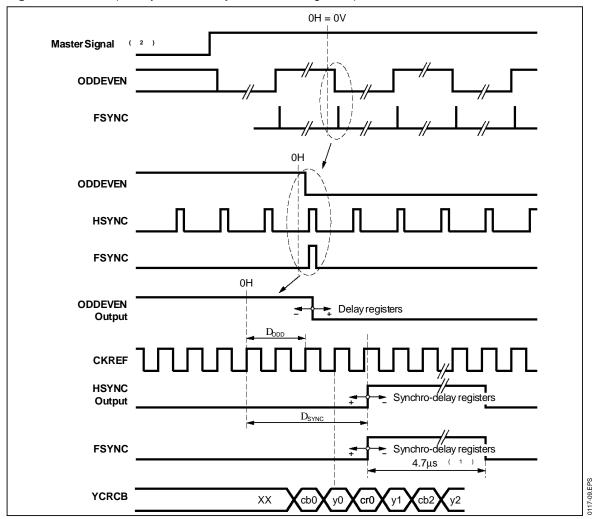

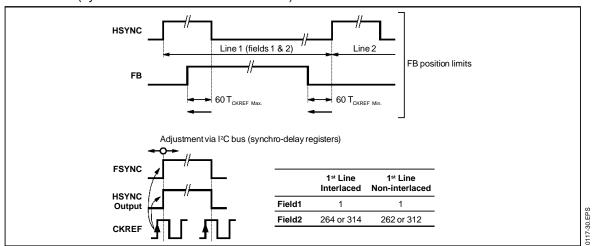

Figure 2: Square Pixel and/or Non-interlaced Mode Switch

Notes: 1. These diagrams are valid with contents of "delay" and "synchro-delay" registers equal to default value.

2. If on-the-fly format changing is required, clock switching must be synchronized onto the start of frame as shown in the above waveforms. Internally, "sqpix" and "nintrl" bits update is taken into account on beginning of new frame.

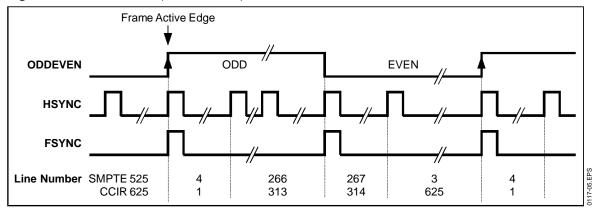

Figure 3: Interlaced Mode (nintrl =  $0 - I^2C$ ) - Master Mode

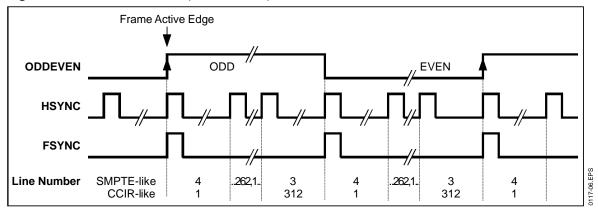

Figure 4: Non-interlaced Mode (nintrl = 1 - I<sup>2</sup>C) - Master Mode

Notes: 1. These diagrams are valid for sys0 = 1 and sys1 = 0 in Register 0 (i.e. synchro active edges defined as rising).

In slave mode, only one edge (the "active edge") of the incoming ODDEVEN is taken into account for synchronization. The "non-active edge" is not critical and its position may differ by up to half a line from the location shown in master mode.

Figure 5: NTSC-M Typical VBI Waveforms (interlaced mode) (SMPTE-525 line numbering convention)

**Figure 6 :** NTSC-M Typical VBI Waveforms (non-interlaced mode) ("SMPTE-like" line numbering convention)

Figure 7: PAL-M Typical VBI Waveforms (interlaced mode) (CCIR-525 line numbering convention)

Figure 8 : PAL-M Typical VBI Waveforms (non-interlaced mode) ("CCIR-like" line numbering convention)

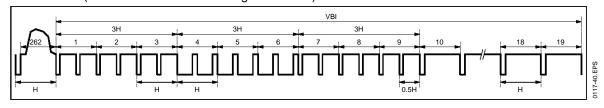

### **FUNCTIONAL DESCRIPTION** (continued)

Figure 9: PAL-BGHI Typical VBI Waveforms (interlaced mode) (CCIR-625 line numbering convention)

Figure 10: PAL-BGHI Typical VBI Waveforms (non-interlaced mode) ("CCIR-like" line numbering convention)

Figure 11: Video Timing - Master Mode = Auto-test Mode - NTSC - CVBS Signal

17-07.EPS

12/45

#### 3 - Reset Procedure

A hardware reset is performed by grounding the Pin NRESET. This will set the STV0117 in slave mode driven by ODDEVEN and HSYNC input Pins, in NTSC-M standard, with CCIR601 rectangular pixel and interlaced mode encoding.

After power-on reset, MACROVISION™ copy protection process is disabled and no closed captions are encoded; then, any I<sup>2</sup>C bus programming and/or software reset will set the STV0117 in a customized operation mode in a partially or fully automatic way. A few I<sup>2</sup>C registers are never reset, their contents is unknown until the first loading (see I<sup>2</sup>C REGISTERS DESCRIPTION).

During reset hardware operation and after reset released, all digital I/O stages are set to input mode. This is the case for ODDEVEN, HSYNC signals and DVID[8:0] data.

It is also possible to perform a software reset by setting bit "softrst" in register 4. The IC's response in that case is similar to its response after a hardware reset, except that control and configuration registers are not altered (register 0 to 4).

**Note** that after writing a "1" into bit "softrst" (register 4), it is necessary to stop the I<sup>2</sup>C sequence after register 4 and start a new I<sup>2</sup>C transfer sequence to send the data for next registers.

#### 4 - Master Mode

After a software reset, the synchronization generator starts counting the CKREF clock pulses and provides a complete repetitive composite synchronization pulse sequence. In that mode, the time base of the circuit runs continuously.

This is a 4 field sequence in NTSC-M and a 8 field sequence in PAL.

Whatever the standard, ODDEVEN signal and composite or horizontal synchronization signal (VCS/HSYNC Pin) are delivered to control an MPEG video decoder.

Non-interlaced and/or square pixel encoding is performed when selected by programmation.

The timings of sync signals depend on whether or not square pixel or non-interlaced modes have been selected and are also affected by the "delayregisters" and "synchro-delay-registers" (see Figure 12).

#### 5 - Slave Modes

Three slave modes are selectable by the I<sup>2</sup>C bus, bit "mod" (register 0) should be set to "0" to enable slave mode.

#### 5.1 - Line-locked Sync

(sym2 = sym1 = "1" in register 0)

After a sofware reset, the synchronization counter waits for the rising edge of ODDEVEN and HSYNC signals sent by a video source.

In slave mode by ODDEVEN and HSYNC, the first active transition of ODDEVEN initializes the internal line counter and the simultaneous or first following active transition of HSYNC intializes a sample counter.

- If line length is shorter or equal to nominal value: sample counter is reinitialized and all internal active signals depending on sample counter are set inactive. The last pixels of the digital line are not output in that case; however the encoded video is within the analog video requirements.

- If line length is longer than nominal value: sample counter is stopped when reaching nominal end of line and is waiting for next HSYNC active edge to reinitialize itself.

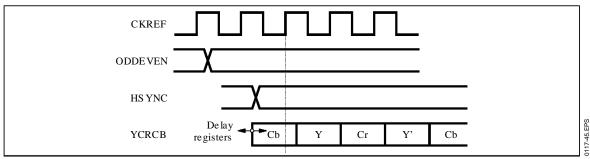

Note that the phase relationship between HSYNC and the incoming YCRCB data should be such that the first clock rising edge following the HSYNC active edge always samples "Cb" (see Figure 13).

Field count is incremented on each ODDEVEN transition. Line counter is reset on each active edge of ODDEVEN.

#### 5.2 - Frame-locked Sync

(sym2 = sym1 = "0" in register 0)

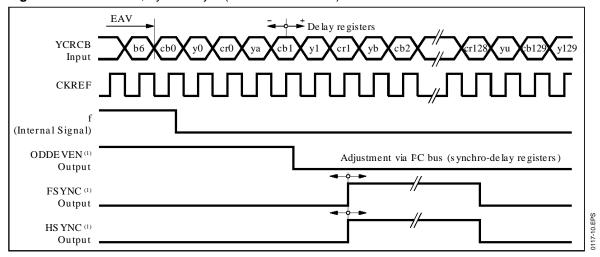

Alternatively, slave mode can be performed with ODDEVEN input only, or STV0117 can be set to extract the synchronization from YCRCB input data sequence (F: ODDEVEN signal from EAV sequence (see Figure 14)).

After a sofware reset, the synchronization counter waits for the first active edge of ODDEVEN or F first falling edge sent by a digital video source. Once the appropriate sync signals have been selected, a sequence identical to that in master mode can start and is repeated until 3 consecutive checks on ODDEVEN location fail. In the latter case, the IC stops outputting HSYNC and, if applicable, ODDEVEN, and blanks the video outputs until a new rising edge occurs on ODDEVEN onto which it locks again (see Figure 15).

Note that the phase relationship between ODD-EVEN and the incoming YCRCB data should be such that the first clock rising edge following the ODDEVEN active edge always samples "Cb".

### **FUNCTIONAL DESCRIPTION** (continued)

Figure 12: Master (with sys0 = 0 and sys1 =  $0 - I^2C$  Register 0)

Notes: 1. These diagrams are valid when delay registers not loaded (default values):

If delay register value < 0, then ODDEVEN edge is shifted left, else ODDEVEN edge is shifted right.

If synchro\_delay register value < 0, then HSYNC and FSYNC edges are shifted right, else they are shifted left.

- 2. Master signal goes to 1 when soft/hard autotest mode or master mode is selected.

- 3. To keep the CB, Y, CR sequence correct, synchro-delay register must be changed four steps by four steps.

### **FUNCTIONAL DESCRIPTION** (continued)

Figure 13: HSYNC + ODDEVEN Based Slave Mode Sync Signals

Notes: 1. Diagram valid for contents of "delay" and "synchro-delay" register = default.

Figure 14: Slave Mode, Synchro by F (extracted from EAV) (1)

Note: 1. Diagram valid if both registers delay and synchro-delay are not loaded (default values).

Figure 15: Slave Mode, Synchro by ODDEVEN

Note: 1. Diagram valid if both registers delay and synchro-delay are not loaded (default values).

In ODDEVEN + HSYNC synchronization mode, ODDEVEN and HSYNC may change level at the same time, alternatively ODDEVEN can change first and the next HSYNC flags the start of the first line of the frame.

### 6 - Chrominance Encoding

CKREF clock rate. This processing makes easier the rate encoding.

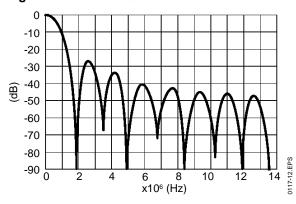

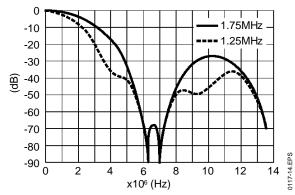

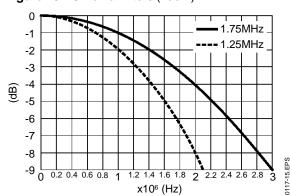

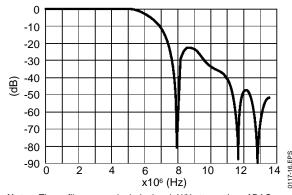

Figure 16: Chroma Q Filter

Figure 18: Chroma Filters

Note: Those filter curves include the sinX/X attenuation of DACs.

The demultiplexed CB, CR samples feed a chromi- For modulation with the color subcarrier signal, the nance Q/I matrix for NTSC-M (or a U/V matrix U/V or Q/I components are band limited to 1.3MHz for PAL). The Q/I or U/V signals are then band limited for U/V and I, and to 0.5MHz for Q. In case of data according to CCIR Rec624 and interpolated at issued from a graphics source, bandwidth can be extended to 1.8MHz for all components (see Figfiltering for D/A conversion and allows a more accu- ures 16, 17, 18 and 19 for curves of the different filters).

Figure 17: Chroma Q Filter (zoom)

Figure 19: Chroma Filters (zoom)

#### 7 - Color Subcarrier Generator

A Direct Digital Frequency Synthesizer (DDFS), using a 22-bit phase accumulator, generates the required color subcarrier frequency. This oscillator feeds a quadrature modulator which modulates the baseband chrominance signal components.

Color subcarrier frequency is computed according to the following equation:

Fsc = (22-bit increment word/2<sup>22</sup>) x CKREF

The phase and frequency of the color subcarrier can be adjusted by software.

The external clock is considered to be sufficiently stable to ensure correct encoding.

When performing external Gen-locking, the frequency reference of the generated clock may slightly deviate depending on the line length measurement. To prevent this drift from corrupting the colors, the color subcarrier frequency control line (CFC Pin) can be used to update the 22-bit increment of the DDFS and keep the color subcarrier stable (see Figure 20).

Internal I<sup>2</sup>C options provide a reset of color subcarrier phase every 2, 4 or 8 fields to compensate for any drift introduced by the finite accuracy of the calculations.

#### 8 - Burst Insertion

The start time of the color burst is at the positive zero crossing of the color subcarrier sinusoïdal waveform that follows a burst window. This window location is given in Table 3.

The first and last half cycles have a reduced amplitude so that the burst envelope starts and ends smoothly.

Table 3

| Standard                    | Application             | CKREF<br>Frequency<br>(MHz) | Burst<br>Window<br>Location<br>from 0H |

|-----------------------------|-------------------------|-----------------------------|----------------------------------------|

| PAL-B, D, G, H, I,<br>PAL-N | CCIR601                 | 27                          | +151 CKREF<br>periods                  |

| NTSN-M                      | CCIR601                 | 27                          | +137 CKREF<br>periods                  |

| PAL-M                       | CCIR601                 | 27                          | +146 CKREF<br>periods                  |

| PAL-B, D, G, H, I,<br>PAL-N | Square Pixel (Graphics) | 29.50                       | +169 CKREF<br>periods                  |

| NTSN-M,<br>PAL-M            | Square Pixel (Graphics) | 24.5454                     | +131 CKREF<br>periods                  |

The burst is inserted for 9 (M and PAL-N standards) or 10 (PAL-B, D, G, H, I) subcarrier cycles.

Phase shift is directly performed within the DDFS during the burst insertion as specified in Table 4.

Table 4

| Standard          | Subcarrier<br>Freq. (MHz)<br>CCIR601/<br>Square Pixel | Phase Shift<br>per Line<br>(Degrees) |  |  |  |  |

|-------------------|-------------------------------------------------------|--------------------------------------|--|--|--|--|

| PAL-B, D, G, H, I | 4.43361875                                            | -90 (plus line alternance)           |  |  |  |  |

| PAL-N             | 3.5820558                                             | +90 (plus line alternance)           |  |  |  |  |

| NTSC-M            | 3.5795452                                             | +180                                 |  |  |  |  |

| PAL-M             | 3.57561149                                            | +90 (plus line alternance)           |  |  |  |  |

Note that except in square pixel mode, subcarrier frequencies can readily be customized with the following procedure:

- Program the required increment in registers 10 to 12.

- Set bit "selrst" to "1" in register 2.

- Perform a software reset (register 5).

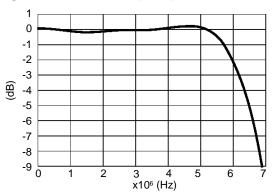

#### 9 - Luminance Encoding

The demultiplexed Y samples are band limited and are interpolated at CKREF clock rate. Then a gain and offset compensation is applied to the luminance signal before inserting closed captions data, Macrovision copy protection signals and synchronization pulses.

A 7.5 IRE pedestal is selected automatically in the 60Hz field rate mode and may be added in 50Hz field rate mode to distinguish 2 PAL-N standards (see I<sup>2</sup>C REGISTERS DESCRIPTION).

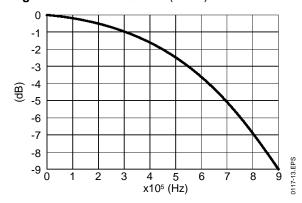

The interpolation filter compensates the sinx/x attenuation of D/A conversion and greatly simplifies the external output stage filter (see Figures 21 and 22 for curves).

A programmable delay is inserted on the luminance data path to offset any chroma/luma delay introduction by off-chip filtering (see I<sup>2</sup>C REGISTERS DESCRIPTION).

By default, luminance and chrominance transitions are aligned on analogue outputs.

Figure 20: Color Subcarrier Frequency Control Word Transmission Format

Figure 21: Luma Filters

$\textbf{Note:} \ \ \text{Those filter curves include the sinX/X attenuation of DACs.}$

Figure 22: Luma Filters (zoom)

#### 10 - Closed Captions Encoding

Data, according to the closed caption specifications, or extended data service can be encoded by the circuit. The closed caption data is delivered to the circuit through the I<sup>2</sup>C bus control interface. Two dedicated pairs of bytes (two bytes per field), each pair preceded by a clock run-in and a start bit can be encoded and inserted on the luminance path on a selected line. The serial I<sup>2</sup>C loading should be performed odd-parity bit first, then MSB of the US-ASCII 7-bit character and LSB last. I'C Register 39 (resp. register 41) is the first byte sent (LSB first) after the start bit on the appropriate TV line in field1 (resp. field2), and register 40 (resp. register 42) is the second byte. The TV line number where data is to be encoded is programmable (see I<sup>2</sup>C REGISTERS DESCRIPTION). A Direct Digital Frequency Synthesizer (DDFS), using a phase accumulator, generates the required run-in frequency. The phase and frequency of the run-in oscillator are generated for different standards. The nominal instantaneous data rate is 503496.5Hz (i.e. 32 times the NTSC line frequency). Should closed-

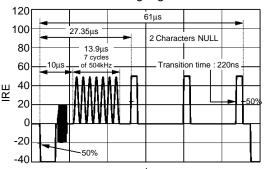

Figure 23: Closed Caption Line CKREF = 27MHz - NTSC-M CVBS Analog Signal

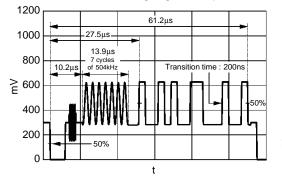

Figure 25: Closed Caption Line CKREF = 24.5454MHz - NTSC-M CVBS Analog Signal - Square Pixel

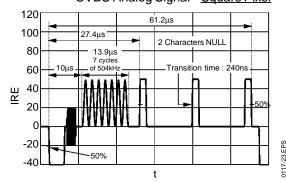

captioning be needed in conjunction with PAL, this same data clock frequency would still be used, and all closed-caption absolute timings would be unchanged. Closed captions can also be encoded in square pixel mode and the nominal data rate keeps the same. Data LOW corresponds nominally to 0 IRE, data HIGH corresponds to 50 IRE at the DAC outputs. When closed-captioning is on, the microcontroller should load the relevant registers (reg. 39 and 40, or 41 and 42) once every frame (possibly less) in average. The closed caption encoder considers that the closed caption data has been loaded and is valid on completion of the write operation into register 40 for field1, into register 42 for field 2. If closed caption encoding is on and no new data bytes have been written into the closed caption data registers when the closed caption data slot starts on the appropriate TV line, then the circuit outputs two US-ASCII NULL characters with odd parity after the start bit (see Figures 23, 24, 25 and 26).

Figure 24: Closed Caption Line CKREF = 27MHz - PAL/CCIR CVBS Analog Signal

Figure 26: Closed Caption Line CKREF = 29.5MHz - PAL 625 Lines CVBS Analog Signal - Square Pixel

19/45

0117-21.EPS

0117-22.EPS

#### **FUNCTIONAL DESCRIPTION** (continued)

### 11 - CVBS and SVHS Outputs

No luminance band-stop filter is implemented to remove chrominance from the luminance part of the composite video channel.

Each digital video signal drives a 9-bit D/A converter operating at CKREF clock rate.

The outputs are current sources and are propor-

tional to the current reference source ( $I_{REF}$  Pin). The integrated oversampling stages make the external antialiasing low pass filters simpler (see Figures 27, 28 and 29).

Unused DAC must be connected to ground and disabled via I<sup>2</sup>C control (separate power-down modes).

Table 5

| Signal | Resolution | Maximum Voltage (IREF = 2mA, RL= 300Ω)                                        |

|--------|------------|-------------------------------------------------------------------------------|

| CVBS   | 9 bits     | 1.24V <sub>PP</sub>                                                           |

| С      | 9 bits     | 1.24V <sub>PP</sub> (0.8V <sub>PP</sub> nominal for 100/0/100 625l color bar) |

| YS     | 9 bits     | 1.24VPP (1.0VPP nominal for 100/0/100 625l color bar)                         |

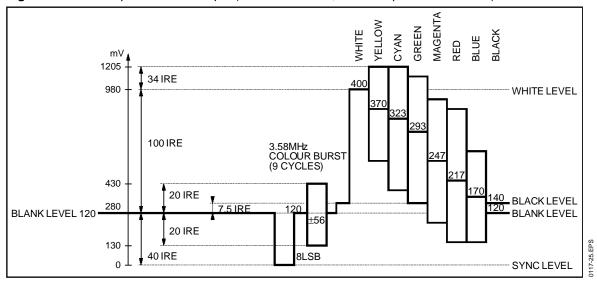

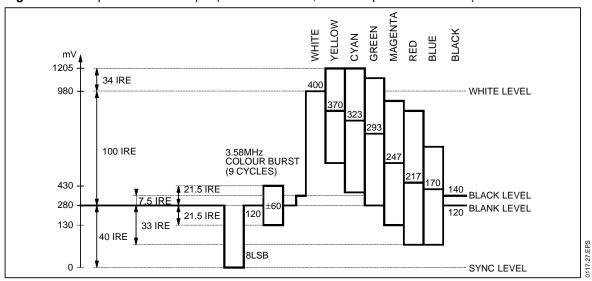

Figure 27: M Composite NTSC Output (100% Saturation, 100% Amplitude Color Bars)

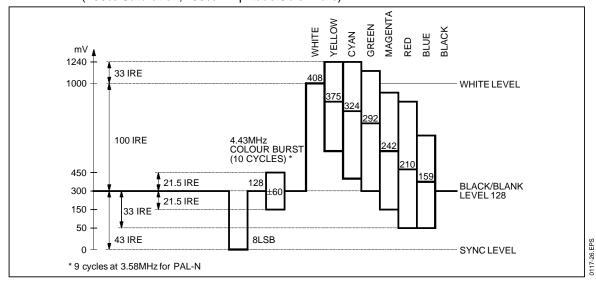

**Figure 28:** Composite PAL-B, G, D, H, I, PAL-N (if no setup) Output (100% Saturation, 100% Amplitude Color Bars)

Figure 29: Composite PAL-M Output (100% Saturation, 100% Amplitude Color Bars)

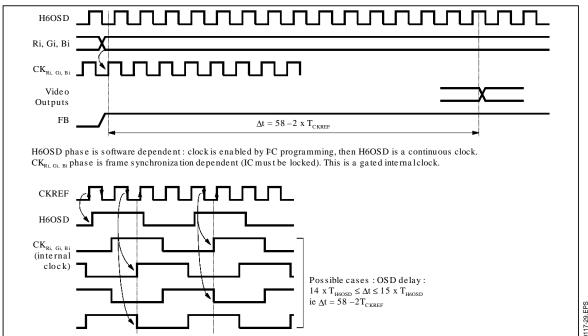

#### 12 - OSD Inputs

FB (Fast Blanking) input controls the switching from YCRCB normal input data to Ri, Gi, Bi transcoded inputs. These inputs must be locked to HSYNC, ODDEVEN and CKREF or H6OSD signals. They are latched on the rising edge of CKREF clock signal.

Ri, Gi, Bi inputs allow 8 color combinations that will address a 3  $\times$  8  $\times$  6-bit CLUT. Each of the 8 values will address 3  $\times$  6-bit samples CB, Y, CR that will

be extended to 8-bit samples to fit with normal input samples. Y samples will be filtered to make sure that their bandwith is similar to YCRCB input samples. Mixing between OSD data and YCRCB normal input is performed before filtering stages.

H6OSD output clock signal is dedicated to output stage of external OSD generator. The latter is synchronized with HSYNC and ODDEVEN (or FSYNC) signals (see Figures 30, 31 and 32).

Figure 30: OSD Data Insertion

Figure 31: OSD Synchronization Timing: Master Mode or Slave Mode (by ODDEVEN or F from YCRCB data)

Figure 32: OSD Synchronization Timing: Slave Mode (ODDEVEN and HSYNC)

#### 13 - Hamming Decoding

If the timing reference sequence is present in YCRCB input data, then EAV and SAV are Hamming decoded. Only F signal is extracted from EAV and can be used in slave mode as the frame synchronization input signal.

Hamming decoding on EAV and SAV words give an information on signal transmission; multiples errors are detected and a flag is set to inform the microcontroller if it is interested in Hamming decoding results (see STATUS I<sup>2</sup>C REGISTER).

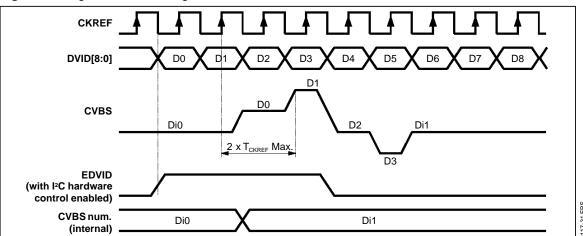

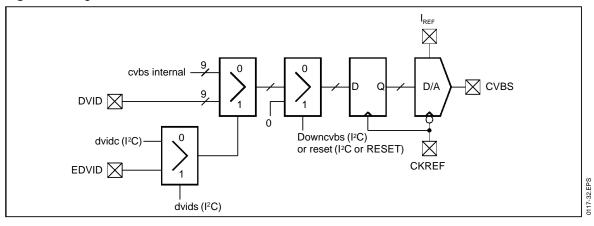

#### 14 - Digitized Video Input

DVID 9-bit digital input from a digitized analog video source can be directly routed to CVBS DAC input. DVID data is latched on the rising edge of CKREF clock signal.

This access is controlled by hardware (EDVID Pin) or by I<sup>2</sup>C programmation (see Figures 33 and 34).

Figure 33: Digitized Video Timing

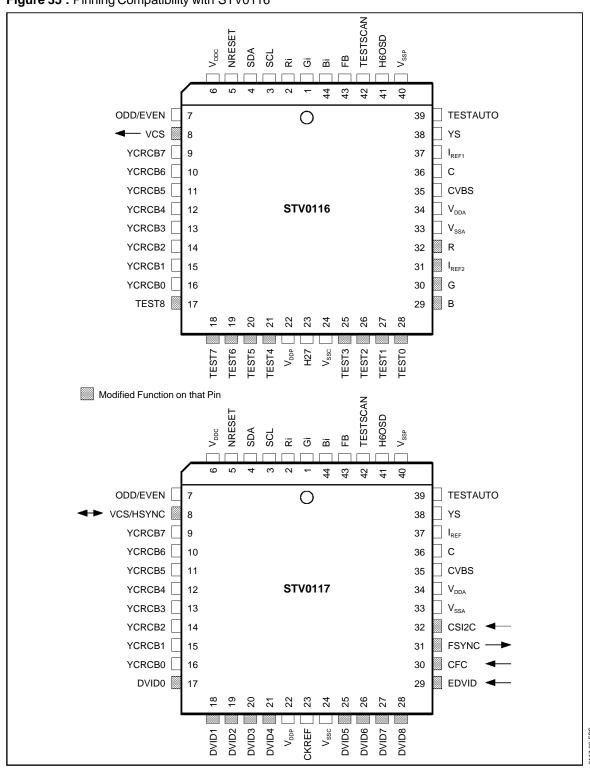

#### 15 - Pinning Compatibility with STV0116

The STV0116 is a PAL/NTSC digital encoder device that has 3 additional D/A converters for R, G, B encoded analog outputs. It does not support either closed captions encoding or MACROVISION™ copy protection process. It is a CCIR601 interlaced mode encoder. It does not offer the possibility to convert a digitized video input into an analog CVBS output, (like DVID in STV0117). It does not support the slave mode by ODDEVEN and HSYNC, (it has no HSYNC input) (see Figure 35).

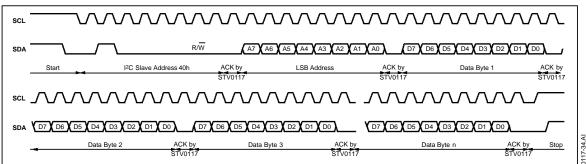

### 16 - I<sup>2</sup>C Bus Waveforms

STV0117 IC is controlled by an I<sup>2</sup>C bus and internal 8-bit registers can be addressed in write or read mode. Write and read operations are detailed in Figures 36 and 37.

Figure 34: Digitized Video Interface

SGS-THOMSON MICROELECTRONICS

23/45

Figure 35: Pinning Compatibility with STV0116

Figure 36 : STV0117/ $f^2$ C Write Operation (CSI2C = 0)

Figure 37:  $STV0117/l^2C$  Read Operation (CSI2C = 0)

#### MACROVISION™ COPY PROTECTION PROCESS

When enabled, the chrominance, the luminance and the composite video signals are simultaneously modified according to the MACROVISION™ copy protection process for PPV applications, revision 6.0/6.1 dated September, 18, 1995.

The control of this process is performed via I<sup>2</sup>C bus. For more information, please contact your nearest SGS-THOMSON Microelectronics sales office.

The programming document is provided to ONLY those customers of SGS-THOMSON who have executed a license or a non-disclosure agreement with MACROVISION Corporation. Sample request and sales orders require the following procedure:

# Sample Requests Procedure for Non-licensed Customers

- Contact VP Sales & Marketing, ACP-PPV MACROVISION Corporation Phone: (408) 743-86-00

- Fax: (408) 743-86-10

- MACROVISION will send an NDA to the customer

- The NDA will initiate the sampling process whereby the customer may receive MACROVI-SION capable ICs from SGS-THOMSON

- Samples will then be sent to the customer

#### Sales Orders

- If the customer has a MACROVISION™ license: The customer provides SGS-THOMSON with a written confirmation of the license.

- Marketing will retain the written confirmation. Customer can then purchase part.

- If the customer DOES NOT HAVE a MACROVI-SION™ license :

The customer must obtain a license or waiver from MACROVISION.

The customer must provide SGS-THOMSON with a written confirmation of the license or waiver from MACROVISION.

Marketing retains the written confirmation. Customer purchases part.

Neither parts nor programming information will be sent to the customer until the above conditions are met.

MACROVISION™ 6.0/6.1 copy protection process programming guide (a confidential document).

Contact Video Marketing SGS-THOMSON Microelectronics - Grenoble (France) - Fax : (33) 76-58-56-10

Note: For customers who do not need MACROVISION™ copy protection process, a modified version of STV0117 device can be available upon specific request.

25/45

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                      | Value                       | Unit |

|------------------|--------------------------------|-----------------------------|------|

| $V_{DDx}$        | DC Supply Voltage              | -0.3, 7.0                   | V    |

| V <sub>IN</sub>  | Digital Input Voltage          | -0.3, V <sub>DD</sub> + 0.3 | V    |

| Vout             | Digital Output Voltage         | 0, V <sub>DD</sub>          | V    |

| I <sub>REF</sub> | Analog Input Reference Current | 7                           | mA   |

| lout             | Analog Output Current          | 15                          | mA   |

| Toper            | Operating Temperature          | 0, +70                      | °C   |

| T <sub>stg</sub> | Storage Temperature            | -40, +150                   | °C   |

| P <sub>tot</sub> | Total Power Dissipation        | 1000                        | mW   |

### THERMAL DATA

| Symbol               | Parameter                                                                 | Value | Unit | ā         |

|----------------------|---------------------------------------------------------------------------|-------|------|-----------|

| R <sub>th(j-a)</sub> | DC Junction-Ambient Thermal Resistance Typ. with sample soldered on a PCB | 54    | °C/W | 0117-03.T |

DC ELECTRICAL CHARACTERISTICS

$(T_{amb} = 25^{\circ}C/70^{\circ}C, V_{DDA} = V_{DDC} = V_{DDP} = 5V, unless otherwise specified)$

| Symbol           | Parameter                                     | Test Conditions                                                  | Min. | Тур. | Max.                 | Unit |

|------------------|-----------------------------------------------|------------------------------------------------------------------|------|------|----------------------|------|

| SUPPLY           |                                               |                                                                  |      |      |                      |      |

| $V_{DDA}$        | Analog Positive Supply Voltage                |                                                                  | 4.75 | 5    | 5.25                 | V    |

| $V_{DDP}$        | Digital Output Buffer Supply Voltage          |                                                                  | 4.75 | 5    | 5.25                 | V    |

| VDDC             | Digital Core Supply Voltage                   |                                                                  | 4.75 | 5    | 5.25                 | V    |

| $I_{DDA}$        | Analog Current Consumption                    | $I_{REF} = 3.5 \text{mA}, R_L = 300\Omega,$                      | 10   |      | 28                   | mA   |

| $I_{DD}$         | Digital Current Consumption                   | $C_L$ = 50pF, CKREF = 30MHz, autotest mode, static input signals | 40   |      | 90                   | mA   |

| DIGITAL II       | NPUTS                                         |                                                                  |      |      |                      |      |

| V <sub>IL</sub>  | Input Voltage                                 | Low level (any other pins)                                       | -0.3 |      | 0.8                  | V    |

| V <sub>IH</sub>  | Input Voltage                                 | High level (any other pins)                                      | 2.4  |      | V <sub>DD</sub> -0.5 | V    |

| IL               | Input Leakage Current                         | V <sub>IL</sub> min or V <sub>IH</sub> max                       |      |      | ± 10                 | μΑ   |

| C <sub>IN</sub>  | Input Capacitance                             |                                                                  |      |      | 10                   | pF   |

| SDA OUTI         | PUT                                           |                                                                  |      |      |                      |      |

| $V_L$            | Output Voltage                                | Low level, I <sub>O</sub> = 3mA                                  |      |      | 0.4                  | V    |

| Ιο               | Output Current                                | During Acknowledge                                               | 3    |      |                      | mA   |

| DIGITAL C        | UTPUT                                         |                                                                  |      |      |                      |      |

| VoH              | Output Voltage                                | High level (standard TTL load)                                   | 2.4  |      | V <sub>DD</sub>      | V    |

| $V_{OL}$         | Output Voltage                                | Low level (standard TTL load)                                    | 0    |      | 0.6                  | V    |

| D/A CONV         | ERTER                                         |                                                                  |      |      |                      |      |

| I <sub>REF</sub> | Reference Current Source for 3 D/A Converters |                                                                  | 2    | 3    | 6                    | mA   |

| $R_L$            | External Load Resistance                      | with I <sub>REF</sub> = 2.9mA                                    |      | 300  |                      | Ω    |

| lG               | Current Gain                                  | $I_{REF}$ = 2.9mA, $R_L$ = 300 $\Omega$ , Max. code              | 1.9  | 2.1  | 2.3                  |      |

| GE               | DAC to DAC Gain Matching (YS, C)              | $I_{REF}$ = 2.9mA, $R_L$ = 300 $\Omega$                          | 0.5  | 3    | 3.5                  | %    |

| ILE              | LF Integral Non-linearity                     | $I_{REF}$ = 2.9mA, $R_L$ = 300 $\Omega$                          |      |      | ± 2                  | LSB  |

| DLE              | LF Differential Non-linearity                 | $I_{REF}$ = 2.9mA, $R_L$ = 300 $\Omega$                          |      |      | ± 1                  | LSB  |

|                  |                                               |                                                                  |      |      |                      |      |

### AC ELECTRICAL CHARACTERISTICS

$(T_{amb} = 25^{\circ}C/70^{\circ}C, V_{DDA} = V_{DDC} = V_{DDP} = 5V, unless otherwise specified)$

| Symbol                       | Parameter                      | Test Conditions                                                       | Min.    | Тур.                    | Max. | Unit           |

|------------------------------|--------------------------------|-----------------------------------------------------------------------|---------|-------------------------|------|----------------|

| DIGITAL INPUT (Y             | CRCB[7:0], SCL, SDA, NRE       | ESET, ODDEVEN, HSYNC, DVID[8:0], ED                                   | VID, CF | C)                      |      |                |

| tsu                          | Input Data Set-up Time         | CKREF rising edge, CKREF = 30MHz                                      | 5       |                         |      | ns             |

| tho                          | Input Data Hold Time           | CKREF rising edge, CKREF = 30MHz                                      | 5       |                         |      | ns             |

| ACTIVE PERIOD F              | FOR NRESET                     |                                                                       |         |                         |      |                |

| tRSTL                        | Input Low Time                 |                                                                       | 210     |                         |      | ns             |

| OSD DIGITAL INP              | UTS : Ri, Gi, Bi, FB (other in | puts are static : TESTSCAN, TESTAUTO,                                 | CSI2C)  | )                       |      |                |

| tsu                          | Input Data Set-up Time         | CKREF rising edge, CKREF = 30MHz                                      | 15      |                         |      | ns             |

| tho                          | Input Data Hold Time           | CKREF rising edge, CKREF = 30MHz                                      | 0       |                         |      | ns             |

| REFERENCE CLO                | CK : CKREF                     |                                                                       |         |                         |      |                |

| tC_REF                       | Clock Cycle Time               | CCIR601 application<br>Square pixel/525lines<br>Square pixel/625lines |         | 37.04<br>40.75<br>33.90 |      | ns<br>ns<br>ns |

| tD_REF                       | Clock Duty Cycle               |                                                                       |         | 50                      |      | %              |

| tR_REF                       | Clock Rise Time                |                                                                       |         |                         | 5    | ns             |

| tF_REF                       | Clock Fall Time                |                                                                       |         |                         | 5    | ns             |

| I <sup>2</sup> C CLOCK : SCL |                                |                                                                       |         |                         |      |                |

| tC_SCL                       | Clock Cycle Time               | Rpull_up = $4.7k\Omega$                                               |         |                         | 2    | MHz            |

| tD_SCL                       | Clock Duty Cycle               |                                                                       |         | 50                      |      | %              |

| tL_SCL                       | LOW Level Cycle                | Rpull_up = $4.7k\Omega$                                               | 250     |                         |      | ns             |

| DIGITAL OUTPUT               | S                              |                                                                       |         |                         |      |                |

| td_H6OSD                     | Delay Time                     | CKREF rising edge<br>CKREF = 30MHz, C <sub>L</sub> = 50pF             | 10      |                         | 25   | ns             |

| td_FSYNC                     | Delay Time                     | CKREF rising edge<br>CKREF = 30MHz, C <sub>L</sub> = 50pF             | 10      |                         | 22   | ns             |

| td_ODDEVEN                   | Delay Time                     | CKREF rising edge<br>CKREF = 30MHz, C <sub>L</sub> = 50pF             | 10      |                         | 22   | ns             |

| td_VCS_HSYNC                 | Delay Time                     | CKREF rising edge<br>CKREF = 30MHz, C <sub>L</sub> = 50pF             | 10      |                         | 22   | ns             |

### I<sup>2</sup>C REGISTERS DESCRIPTION

STV0117 IC is controlled by an I<sup>2</sup>C bus and internal REGISTERS can be read or written by an external microcontroller.

Encoder addresses are:

| if CSI2C Pin = '0' then: write 8-bit address | is | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | (40 hex) |

|----------------------------------------------|----|---|---|---|---|---|---|---|---|----------|

| read 8-bit address                           | is | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | (41 hex) |

| if CSI2C Pin = '1' then: write 8-bit address | is | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | (42 hex) |

| read 8-bit address                           | is | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | (43 hex) |

|              | read 8-bit address is 0 1 0 0 0 0 1 1 (43 hex)                                                                                                            |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| REGISTERS at | re organized as follows:                                                                                                                                  |

| Reg 0        | Standard selection, sync mode selection, sync polarity selection, master/slave mode                                                                       |

| Reg 1        | Sync output selection, VBI lines blanking, filter selection, sync enable in free-run, color killer, PALNsetup, closed caption/extended data encoding mode |

| Reg 2        | Non-interlaced mode, autotest, burst control, square pixel mode, oscillator reset value selection, oscillator reset, phase reset cycle definition         |

| Reg 3        | Color frequency control, DVID controls, luma delay adjustment                                                                                             |

| Reg 4        | Software reset, power-down mode for DACs, H6OSD control                                                                                                   |

| Reg 5-6      | Programmable delay for time base with reference to data                                                                                                   |

| Reg 7-8      | Synchro delay for time base with reference to synchronization mode                                                                                        |

| Reg 9-10-11  | Increment for color subcarrier frequencies                                                                                                                |

| Reg 12-13-14 | Offset for color subcarrier phase                                                                                                                         |

| Reg 1522     | Y clut for Ri, Gi, Bi inputs encoding                                                                                                                     |

| Reg 2330     | CR clut for Ri, Gi, Bi inputs encoding                                                                                                                    |

| Reg 3138     | CB clut for Ri, Gi, Bi inputs encoding                                                                                                                    |

| Reg 39-40    | Closed caption characters/extended data for field 1 (odd)                                                                                                 |

| Reg 41-42    | Closed caption characters/extended data for field 2 (even)                                                                                                |

| Reg 43       | Closed caption/extended data line insertion select for field 1 (odd)                                                                                      |

| Reg 44       | Closed caption/extended data line insertion select for field 2 (even)                                                                                     |

| Reg 4560     | Reserved                                                                                                                                                  |

| Reg 61       | Chip part identification number                                                                                                                           |

| Reg 62       | Chip revision identification number                                                                                                                       |

| Reg 63       | Status: Hamming decoding, frame synchro flag, closed caption data access, field counter, limit of adjustment value in Registers 5-6                       |

| Reg 64       | I <sup>2</sup> C read control and reserved modes                                                                                                          |

### www.DataSheet4U.com I<sup>2</sup>C REGISTERS DESCRIPTION (continued)

| Register       | Access | Address | MSB     |          |         |         |         |           |         | LSB        |

|----------------|--------|---------|---------|----------|---------|---------|---------|-----------|---------|------------|

| control        | R/W    | 00      | std1    | std0     | sym2    | sym1    | sym0    | sys1      | sys0    | mod        |

| configuration1 | R/W    | 01      | syncsel | blkli    | filred  | syncok  | coki    | PALNsetup | cc2     | cc1        |

| configuration2 | R/W    | 02      | nintrl  | testauto | bursten | sqpix   | selrst  | rstosc    | valrst1 | valrst0    |

| configuration3 | R/W    | 03      | cfc1    | cfc0     | dvids   | dvidc   | del3    | del2      | del1    | del0       |

| configuration4 | R/W    | 04      | softrst | downcvbs | downys  | downc   | enh6osd | XX        | XX      | XX         |

| delay_msb      | R/W    | 05      | d11     | d10      | d9      | d8      | d7      | d6        | d5      | d4         |

| delay_lsb      | R/W    | 06      | d3      | d2       | d1      | d0      | xx      | XX        | XX      | xx         |

| sync_delay_msb | R/W    | 07      | d11     | d10      | d9      | d8      | d7      | d6        | d5      | d4         |

| sync_delay_lsb | R/W    | 08      | d3      | d2       | d1      | d0      | xx      | XX        | XX      | xx         |

| increment Fsc  | R/W    | 09      | XX      | XX       | d21     | d20     | d19     | d18       | d17     | d16        |

| increment Fsc  | R/W    | 10      | d15     | d14      | d13     | d12     | d11     | d10       | d9      | d8         |

| increment Fsc  | R/W    | 11      | d7      | d6       | d5      | d4      | d3      | d2        | d1      | d0         |

| phase Fsc      | R/W    | 12      | XX      | XX       | 021     | 020     | 019     | 018       | 017     | 016        |

| phase Fsc      | R/W    | 13      | 015     | 014      | 013     | 012     | 011     | 010       | 09      | 08         |

| phase Fsc      | R/W    | 14      | 07      | 06       | 05      | 04      | 03      | 02        | 01      | 00         |

| palety         | R/W    | 15      | y75     | y74      | y73     | y72     | y71     | y70       | xx      | xx         |

| palety         | R/W    | 16      | y65     | y64      | y63     | y62     | y61     | y60       | XX      | XX         |

| palety         | R/W    | 17      | y55     | y54      | y53     | y52     | y51     | y50       | XX      | XX         |

| palety         | R/W    | 18      | y45     | y44      | y43     | y42     | y41     | y40       | XX      | XX         |

| palety         | R/W    | 19      | y35     | y34      | y33     | y32     | y31     | y30       | XX      | XX         |

| palety         | R/W    | 20      | y25     | y24      | y23     | y22     | y21     | y20       | XX      | XX         |

| palety         | R/W    | 21      | y15     | y14      | y13     | y12     | y11     | y10       | XX      | XX         |

| palety         | R/W    | 22      | y05     | y04      | y03     | y02     | y01     | y00       | XX      | XX         |

| paletcr        | R/W    | 23      | cr75    | cr74     | cr73    | cr72    | cr71    | cr70      | XX      | xx         |

| paletcr        | R/W    | 24      | cr65    | cr64     | cr63    | cr62    | cr61    | cr60      | XX      | XX         |

| paletcr        | R/W    | 25      | cr55    | cr54     | cr53    | cr52    | cr51    | cr50      | XX      | XX         |

| paletcr        | R/W    | 26      | cr45    | cr44     | cr43    | cr42    | cr41    | cr40      | XX      | XX         |

| paletcr        | R/W    | 27      | cr35    | cr34     | cr33    | cr32    | cr31    | cr30      | XX      | XX         |

| paletcr        | R/W    | 28      | cr25    | cr24     | cr23    | cr22    | cr21    | cr20      | XX      | XX         |

| paletcr        | R/W    | 29      | cr15    | cr14     | cr13    | cr12    | cr11    | cr10      | XX      | XX         |

| paletcr        | R/W    | 30      | cr05    | cr04     | cr03    | cr02    | cr01    | cr00      | XX      | XX         |

| paletcb        | R/W    | 31      | cb75    | cb74     | cb73    | cb72    | cb71    | cb70      | XX      | XX         |

| paletcb        | R/W    | 32      | cb65    | cb64     | cb63    | cb62    | cb61    | cb60      | XX      | XX         |

| paletcb        | R/W    | 33      | cb55    | cb54     | cb53    | cb52    | cb51    | cb50      | XX      | XX         |

| paletcb        | R/W    | 34      | cb45    | cb44     | cb43    | cb42    | cb41    | cb40      | XX      | XX         |

| paletcb        | R/W    | 35      | cb35    | cb34     | cb33    | cb32    | cb31    | cb30      | XX      | XX         |

| paletcb        | R/W    | 36      | cb25    | cb24     | cb23    | cb22    | cb21    | cb20      | XX      | XX         |

| paletcb        | R/W    | 37      | cb15    | cb14     | cb13    | cb12    | cb11    | cb10      | XX      | XX         |

| paletcb        | R/W    | 38      | cb05    | cb04     | cb03    | cb02    | cb01    | cb00      | XX      | XX         |

| c. c. char F1  | R/W    | 39      | opc11   | c117     | c116    | c115    | c114    | c113      | c112    | c111       |

| c. c. char F1  | R/W    | 40      | opc12   | c127     | c126    | c125    | c124    | c123      | c122    | c121       |

| c. c. char F2  | R/W    | 41      | opc21   | c217     | c216    | c215    | c214    | c213      | c212    | c211       |

| c. c. char F2  | R/W    | 42      | opc22   | c227     | c226    | c225    | c224    | c223      | c222    | c221       |

| c. c. line F1  | R/W    | 43      | XX      | XX       | XX      | 114     | I13     | 112       | 111     | 110        |

| c. c. line F2  | R/W    | 44      | XX      | XX       | XX      | 124     | 123     | 122       | 121     | 120        |

| reserved reg   |        | 45      |         | 1        | I       |         | erved   | ı         |         |            |

|                |        |         |         |          |         |         |         |           |         |            |

| reserved reg   |        | 60      |         |          |         | res     | erved   |           |         |            |

| chipID         | R      | 61      | 0       | 1        | 1       | 1       | 0       | 1         | 0       | 1          |

| revID          | R      | 62      | X       | x        | x       | x       | x       | x         | x       | x          |

| status         | R      | 63      | hok     | atfr     | b2 free | b1_free | fldct2  | fldct1    | fldct0  | over_delay |

| test           | R/W    | 64      | t7      | t6       | t5      | t4      | t3      | t2        | t1      | t0         |

| reserved reg   |        |         | - "     |          |         | • • • • | 1 .0    | I ——      | • • •   | 1          |

|                |        |         |         |          |         |         |         |           |         |            |

29/45

#### I<sup>2</sup>C REGISTERS DESCRIPTION (continued)

#### I<sup>2</sup>C Format

WRITE MODE (all Registers except STATUS, chipID, revID):

In case of CSI2C Pin = '0':

S Slave address W A Sub-address A Data 0 A ... Data N A P

S Start condition

Slave address 0100000

W = '0' Write flag

A Acknowledge, generated by slave (STV0117) when OK A = '0' else '1'

Sub-address Sub-address Register (content is made of one byte)

Data 0 First data byte

Data N Continued data bytes (address is automatically incremented) and A's

P Stop condition

#### READ MODE (STATUS, chipID and revID Registers):

In case of CSI2C Pin = '0':

| S   Slave address   W   AC   Sub-address N   AC   P |

|-----------------------------------------------------|

|-----------------------------------------------------|

#### then:

| S | Slave address | R | AC | Data N | AM | Data N + 1 |  | AM | Р |

|---|---------------|---|----|--------|----|------------|--|----|---|

|---|---------------|---|----|--------|----|------------|--|----|---|

S Start condition

Slave address 7-bit address for STV0117: 0100000

W = '0' Write flac

AC Acknowledge, generated by slave (STV0117) when OK A = '0', else '1'

R = '1' Read flag

Sub-address N 8-bit register sub-address

Data N Data byte of Register N, sent by STV0117

Data N +1 Data byte of Register N+1 (address automatically incremented)

AM Acknowledge, generated by the microcontroller AM = '0' when Acknowledge is OK, else

11

P Stop condition (when last AM = '1')

### Remarks

In case of CSI2C Pin = '0':

Writing of a Register: Registers 0, 1, ..., 44 dec can be loaded sequentially with only one start/stop condition followed by the sub-address of the first Register desired.

Example: loading of the 4 configuration Registers: start followed by address 40 hexa and sub-address 1 and then 4 bytes of data and stop.

As specified, the  $I^2C$  registers can be loaded sequentially in one run in most cases. However, when this would involve performing a soft reset by writing a "1" into the "softrst" bit of register 4, it is necessary to stop after register 4 and start a new  $I^2C$  transfer sequence to send the next registers.

Reading of a REGISTER:

Example: reading of Register 63 dec (STATUS): start followed by address 40 hexa, AC = '0' then sub-address 63 dec, AC = 0' and stop. Then start, address 41 hexa, AC = '0', and then data of Register 63 dec, AM = '1' and stop condition.

LSB

MSB

### **REGISTERS MAPPING AND DESCRIPTION**

(\*) Default Mode when NRESET Pin is active (LOW level)

### Register 0 : Control (read/write)

| _                                                      |                     |                     |                                  |                                 |                                                   |                                 |                                           |              |             |  |  |  |

|--------------------------------------------------------|---------------------|---------------------|----------------------------------|---------------------------------|---------------------------------------------------|---------------------------------|-------------------------------------------|--------------|-------------|--|--|--|

|                                                        | std1                |                     | std0                             | sym2                            | sym1                                              | sym0                            | sys1                                      | sys0         | mod         |  |  |  |

| (*)                                                    | std1<br>0<br>0<br>1 | std0<br>0<br>1<br>0 | PAL BDGI                         |                                 | •                                                 | uay - see set                   | up bit in Regis                           | ster1)       |             |  |  |  |

| (*)                                                    | sym2<br>0<br>1      | 2                   | Synchro s                        | ource define                    | e in Slave Mo<br>d by sym0, V0<br>ation, STV01    | CS/HSYNC is                     | s output only<br>IINPUT + ODI             | DEVEN inputs | 3           |  |  |  |

| (*)                                                    | sym1<br>0<br>1      |                     | Must contains same value as sym2 |                                 |                                                   |                                 |                                           |              |             |  |  |  |

| (*)                                                    | sym0<br>0<br>1      | )                   | ODDEVÉ                           | N is the sync                   | hro input, VC                                     | S/HSYNC is a                    | ode (see Note<br>an output<br>DDDEVEN and | ,            | C are outpu |  |  |  |

| (*)                                                    | sys1<br>0<br>1      |                     | Positive (I                      | eading edge                     | tputs: VCS/F<br>is the rising e<br>is the falling | dge) `                          | n sym2 = '0'),                            | FSYNC        |             |  |  |  |

|                                                        | sys0<br>0           |                     | when HS                          | YNC is an inp                   | out (i.e. sym2 :                                  | = 1 and mod                     | of ODDEVEN i<br>= 0)<br>d field) and (i   |              |             |  |  |  |