# **AK4318**

# 18Bit Stereo $\Delta$ $\Sigma$ DAC for Digital Audio

## General Description

The AK4318 i a high performance 1bit stereo DAC for digital audio systems. A 1bit DAC can achieve monotonicity and low distortion with no adjustment and is superior to traditional R-2R ladder based DACs. In the AK4318, the loss of accuracy from clock jitter is also improved by using SCF techniques for on-chip post filter. The AK4318 includes digital de-emphasis filter corresponding to 3 sampling frequencies and soft mute. The master clock can be either 256fs or 384fs, supporting various audio environment. The AK4318 is ideal for digital broadcasting application, DBS, CATV and digital recording application, DAT, MD, DCC etc.

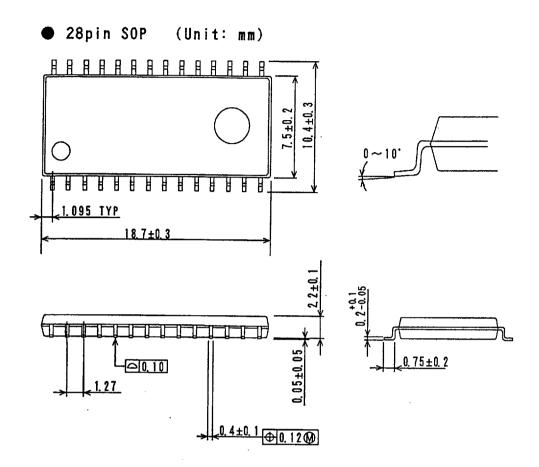

# Features High Performance Stereo 1bit DAC 64 times Oversampling On chip 8 times Interpolation Filter On chip Post Filter (SCF) High Tolerance to Clock Jitter Digital de-emphasis for 32, 44.1, 48kHz sampling Soft mute Master Clock: 256fs or 384fs THD+N: -92dB Dynamic Range, S/N: 97dB 28pin SOP Pakage

# ■ Ordering Guide

AK4318-VS  $-10\sim +70^{\circ}$ C 28pin SOP(1.27mm pitch) AK4318-VM  $-10\sim +70^{\circ}$ C 28pin SSOP(0.65mm pitch) AKD4318 Evaluation Board

# ■ Pin Layout

|       | 1 |    |   |             |   |    | 7 |        |

|-------|---|----|---|-------------|---|----|---|--------|

| NC    |   | 1  | • |             |   | 28 |   | NC     |

| VREF  |   | 2  |   |             |   | 27 |   | NC     |

| NC    |   | 3  |   |             |   | 26 |   | AOUTL+ |

| AVDD  |   | 4  |   |             |   | 25 |   | AOUTL- |

| AVSS  |   | 5  |   |             |   | 24 |   | AOUTR+ |

| TST   |   | 6  |   |             |   | 23 |   | AOUTR- |

| ZMUTE |   | 7  |   | Top<br>View |   | 22 |   | DZF    |

| DIF0  |   | 8  |   |             |   | 21 |   | CKS    |

| DIFI  |   | 9  |   |             |   | 20 |   | DEM1   |

| DVSS  |   | 10 |   |             |   | 19 |   | DEMO   |

| DVDD  |   | 11 |   |             |   | 18 |   | SMUTE  |

| LRCK  |   | 12 |   |             |   | 17 |   | XT0    |

| BICK  |   | 13 |   |             | • | 16 |   | XTI    |

| SDATA |   | 14 |   | ·           |   | 15 |   | PD     |

|       | L |    |   | -           |   |    |   |        |

|     |              |          | PIN/FUNCTION .                                                                                  |

|-----|--------------|----------|-------------------------------------------------------------------------------------------------|

| No. | Pin Name     | 1/0      | Function                                                                                        |

| 2   | VREF         | 0        | Voltage Reference Output Pin, (AVDD)-3.6V                                                       |

|     |              |          | Normally connected to AVDD with a 0. luF ceramic capacitor in                                   |

| ł   |              |          | parallel with a 10uF electrolytic capacitor.                                                    |

| 4   | AVDD         | _        | Analog Supply, +5V                                                                              |

| 5   | AVSS         | -        | Analog Ground Pin                                                                               |

| 6   | TST          | I        |                                                                                                 |

|     |              | 1        | Test Pin (Pull-down pin)  Must be left floating or tied to DGND.                                |

| 7   | ZMUTE        | I        | GDD 0 11                                                                                        |

|     |              | ^        |                                                                                                 |

| 8   | DIFO         | I        | When "H", analog outputs are muted by zero detection.  Digital Input Format Pins                |

| 9   | DIF1         | Í        |                                                                                                 |

| ľ   | 21           | 1        | These two pins select one of four formats for the incoming serial data stream.                  |

| 10  | DVSS         |          | Digital Ground Pin                                                                              |

| 11  | DVDD         |          |                                                                                                 |

| 12  | LRCK         | I        | Digital Power Supply Pin, +5V                                                                   |

|     | <b>D</b> KOK |          |                                                                                                 |

|     | 1 1          |          | This input determines which channel is currently being input                                    |

| 13  | BICK         | I        | on the Serial Data Input pin, SDATA. "H": Lch, "L": Rch<br>Serial Data Clock Pin                |

| "   | J Blok       | 1        | 1                                                                                               |

| 14  | SDATA        | I        | This clock is used to latch SDATA.                                                              |

| ^ . | ODMIN        | •        | Serial Data Input Pin                                                                           |

| 15  | PD           | I        | 2's complement MSB-first data is input on this pin. Power-Down Pin                              |

| 10  | "            |          | 1                                                                                               |

|     | 1            |          | When "L", the AK4318 is in power-down mode and is held in                                       |

| 16  | XTI          | I        | reset. The AK4318 should always be reset upon power-up.  Master Clock Input Pin                 |

| 10  | "            | •        |                                                                                                 |

|     | ] . [        |          | A crystal can be connected between this pin and XTO, or an                                      |

|     | 1            |          | external CMOS clock can be input on XTI. The fs is selected by CKS pin.                         |

| 17  | XTO          | 0        | Crystal Oscillator Output Pin                                                                   |

| • • | "10          |          |                                                                                                 |

|     |              |          | When a crystal is used, it is tied between this pin and XTI.                                    |

|     |              |          | When an external clock is input, this pin should be left floating.                              |

| 18  | SMUTE        | I        |                                                                                                 |

| 10  | Sinolin      | •        | (1 max 40 m pxm)                                                                                |

|     | 1 1          |          | When this pin goes "H", soft mute cycle is initiated. When                                      |

| 19  | DEMO         | I        | returning "L", the output mute releases.  De-emphasis Mode Pins                                 |

| 20  | DEM1         | Î        |                                                                                                 |

| 21  | CKS          | ī        | This function corresponds to 3 types of sampling rate.  Master Clock Select Pin (Pull-down pin) |

|     |              | 1        | · · · · · · · · · · · · · · · · · · ·                                                           |

| 22  | DZF          | 0        | "L": XTI=256fs, "H": XTI=384fs                                                                  |

|     | DE1          | ١ ١      | Zero Input Detect Pin                                                                           |

|     |              |          | When SDATA of both channels follow a total 8192 LRCK cycles                                     |

| 23  | AOUTR-       | 0        | with "0" input data, this pin goes "H".                                                         |

| 24  | AOUTR+       | 0        | Rch analog negative output pin                                                                  |

| 25  | AOUTL-       | 0        | Rch analog positive output pin                                                                  |

| 26  | AOUTL+       | 0        | Lch analog negative output pin                                                                  |

| 20  | VACTEL       | <u> </u> | Lch analog positive output pin                                                                  |

f \* All pins except the above pins are NC pins. These pins are not bonded internally.

# ABSOLUTE MAXIMUM RATINGS

(AVSS, DVSS=0V; Note 1)

| Parameter                              | Symbol | min  | max      | Units |

|----------------------------------------|--------|------|----------|-------|

| Power Supplies: Analog                 | AVDD   |      | 6. 0     | V     |

| Digital                                | DVDD   | -0.3 | AVDD     | V     |

| Input Current, Any Pin Except Supplies | Iin    |      | ±10      | mA    |

| Input Voltage                          | Vind   | -0.3 | DVDD+0.3 | V     |

| Ambient Operating Temperature          | Ta     | -10  | 70       | °C    |

| Storage Temperature                    | Tstg   | -65  | 150      | °C    |

Note: 1. All voltages with respect to ground.

WARNING: Operation at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

# RECOMMENDED OPERATING CONDITIONS

(AVSS, DVSS=0V; Note 1)

| Parameter              | Symbol | min | typ  | max  | Units |

|------------------------|--------|-----|------|------|-------|

| Power Supplies: Analog | AVDD   | 4.5 | 5.0  | 5.5  | V     |

| Digital                | DVDD   | 4.5 | 5. 0 | AVDD | v     |

Notes: 1. All voltages with respect to ground.

- \* Specifications are subject to change without notice.

- \* AKM assumes no responsibility for the usage beyond the conditions in this data sheet.

#### ANALOG CHARACTERISTICS

(Ta=25°C; AVDD, DVDD=5.0V; fs=48kHz; Signal Frequency=1kHz; 18bit Input Data; Differential Outputs; Measurement Bandwidth=10Hz∼20kHz; unless otherwise specified)

| Parameter                     | arement band                          |           | 1                                     | unitess offic |          |

|-------------------------------|---------------------------------------|-----------|---------------------------------------|---------------|----------|

|                               | · · · · · · · · · · · · · · · · · · · | min       | typ                                   | max           | Units    |

| Resolution                    |                                       |           | 18                                    | Bits          |          |

| Dynamic Characteristics (Plea | ise refer to                          | the measu | ıring syste                           | em section)   | <u> </u> |

| THD+N (OdB Output)            | (Note 2)                              | 0.005     | 0.0025                                |               | %        |

|                               |                                       | -86       | -92                                   |               | dB       |

| Dynamic Range (-60dB Output)  | (Note 3)                              | 90        | 97                                    |               | dB       |

| S/N                           | (Note 4)                              | 90        | 97                                    |               | dB       |

| S/N at Muting (ZMUTE="H")     | (Note 4)                              |           | 110                                   |               | dB       |

| Interchannel Isolation        | 90                                    | 100       |                                       | dB            |          |

| Interchannel Gain Mismatch    |                                       |           | 0.1                                   |               | dB       |

| DC Accuracy                   |                                       |           | <del></del>                           | <del></del>   |          |

| Gain Drift                    |                                       |           | 60                                    |               | ppm/℃    |

| Output Voltage Range          | (Note 5)                              | ± 2. 20   | ± 2. 35                               | ± 2.50        | Vp-p     |

| Power Supplies                |                                       | ***       | · · · · · · · · · · · · · · · · · · · |               | • • •    |

| Power Supply Current          |                                       |           |                                       |               |          |

| Normal Operation (PD="H")     | AVDD                                  |           | 17                                    | 25            | mA       |

|                               | DVDD                                  |           | 6                                     | 9             | mA       |

| Power-Down-Mode (PD="L")      | AVDD+DVDD                             |           | 20                                    |               | uА       |

| Power Dissipation (AVDD+DVDD) |                                       |           |                                       |               |          |

| Normal Operation              |                                       |           | 115                                   | 170           | ш¥       |

| Power-Down-Mode               |                                       |           | 0. 1                                  |               | m₩       |

| Power Supply Rejection        |                                       |           | 40                                    |               | dB       |

Notes: 2. Inverse of S/(N+D).

- 3. A-weighted. 96dB(typ) at 16bit input data.

- 4. A-weighted. Digital input all zeros.

- 5. Summation of the differential outputs, (AOUT+)-(AOUT-).  $R_L\!\ge\!10k\,\Omega$

# FILTER CHARACTERISTICS

| Paran         | Symbol                 | min         | typ   | max    | Units  |          |

|---------------|------------------------|-------------|-------|--------|--------|----------|

| Digital Filte | r                      | <del></del> |       |        |        | 1 011110 |

| Passband      | $\pm 0.04$ dB (Note 6) | PB          | 0     |        | 21.3   | kHz      |

|               | -0.23dB                |             | 0     |        | 21.7   | kHz      |

|               | -6.0dB                 |             | 0     |        | 24.0   | kHz      |

| Stopband      | (Note 6)               | SB          | 26. 3 |        |        | kHz      |

| Passband Ripp | le                     | PR          |       |        | ± 0.06 | dB       |

| Stopband Atte | nuation                | SA          | 45    |        | _ 0.00 | dB       |

| Group Delay   | (Note 7)               | GD          |       | 14.7   |        | 1/fs     |

| 2nd Order SCF |                        | <del></del> |       | 1 22 1 |        | 1/10     |

| Frequency Res | ponse 20kHz            |             |       | -0.04  |        | dB       |

|               | 24kHz                  |             |       | -0.32  |        | dB       |

|               | 48kHz                  |             |       | -6.0   |        | dB       |

Note: 6. The passband and stopband frequencies scale with fs. For example, PB=0.452\*fs(@±0.23dB), SB=0.548\*fs.

7. The calculating delay time which occurred by digital filtering. This time is from setting the 18bit data of both channels to input register to the output of analog signal.

# DIGITAL CHARACTERISTICS

(Ta=25°C; AVDD, DVDD=5.0V  $\pm$  10%)

| Parameter                     | S        | ymbol      | min      | typ | max     | Units |

|-------------------------------|----------|------------|----------|-----|---------|-------|

| High-Level Input Voltage      |          | VIH        | 70%DVDD  |     | -       | V     |

| Low-Level Input Voltage       |          | VIL        | -        | _   | 30%DVDD | v     |

| High-Level Output Voltage Iou | t=-20uA  | <b>Уон</b> | DVDD-0.1 |     | -       | V     |

| Low-Level Output Voltage Iou  | t=20uA   | VOL        | -        | _   | 0.1     | v     |

| Input Leakage Current         | (Note 8) | Iin        |          | _   | ±10     | uA    |

Note: 8. TST, ZMUTE, SMUTE, CKS pins have internal pull-down devices, nominally  $90k\Omega$ .

# SWITCHING CHARACTERISTICS

(Ta=25°C; AVDD, DVDD=5.  $0V \pm 10\%$ ;  $C_L = 20 pF$ )

| Parameter                | ··· <u> </u> | Symbol            | min   | typ     | max   | Unit                                               |

|--------------------------|--------------|-------------------|-------|---------|-------|----------------------------------------------------|

| Control Clock Frequency  |              |                   |       | 1       |       | <del>  • • • • • • • • • • • • • • • • • • •</del> |

| Crystal Resonator 256fs  | <b>::</b>    | fclx              | 7. 10 | 12. 288 | 13. 9 | MHz                                                |

| 384fs                    | ::           | fclk              | 10.70 | 18. 432 | 20. 7 | MHz                                                |

| External Clock 256fs     | :            | fclx              | 2.56  | 12. 288 | 13.9  | MHz                                                |

| Puls                     | e Width Low  | tclkl             | 28    |         |       | ns                                                 |

| Puls                     | e Width High | tclkh             | 28    |         |       | ns                                                 |

| 384fs                    |              | fclx              | 3.84  | 18. 432 | 20.7  | MHz                                                |

|                          | e Width Low  | tclkl             | 20    |         |       | ns                                                 |

|                          | e Width High | tclkh             | 20    |         |       | ns                                                 |

| LRCK Frequency           |              | fs                | 10    | 48      | 54    | kHz                                                |

| Serial Interface Timing  | (Note 9)     |                   |       |         |       | 1                                                  |

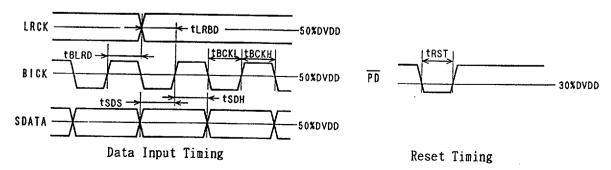

| BICK Period              |              | tBCK              | 290   | 1       |       | ns                                                 |

| BICK Pulse Width Low     |              | <b>t</b> BCKL     | 100   |         |       | ns                                                 |

| Pulse Width High         |              | t <sub>BCKH</sub> | 100   |         |       | ns                                                 |

| BICK rising to LRCK edge |              | tblrd             | 40    |         |       | ns                                                 |

| LRCK Edge to BICK rising | (Note 10)    | turbd             | 40    | 1       |       | ns                                                 |

| SDATA Hold Time          |              | tsde              | 40    |         |       | ns                                                 |

| SDATA Setup Time         |              | tsos              | 40    |         |       | ns                                                 |

| Reset Timing             |              |                   |       |         |       | 1                                                  |

| PD Pulse Width           | (Note 11)    | trst              | 100   |         |       | ns                                                 |

Notes: 9. Refer to the operating overview section "Serial Data Interface".

- 10. SCLK rising edge must not occur at the same time as  $L/\overline{R}$  edge.

- 11. AK4318 can be reset by bringing PD "L" to "H" only upon power up.

# ■ Timing Diagram

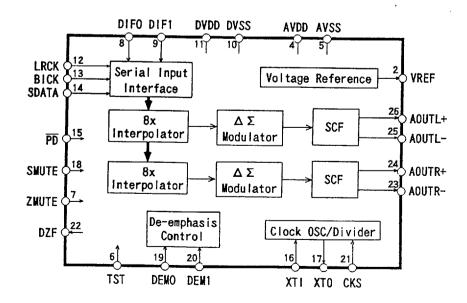

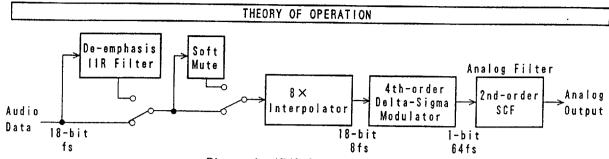

Figure 1. AK4318 Architecture

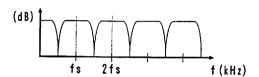

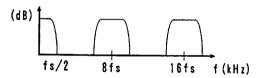

Audio data is input to the AK4318 digital interpolation filter which removes images of the input signal frequency,  $fs(Figure\ 2)$ . Following the interpolation stage, the resulting frequency spectrum has images of the input signal at multiples of eight times the input sample frequency,  $8 \times fs$  (Figure 3). Eliminating the images between fs and fs greatly relaxes the requirements of the analog filtering, allowing the suppression of images while leaving the audio band of interest unaltered.

Figure 2. Input Data Spectrum

Figure 3. 8% Interpolated Data Spectrum

The AK4318 interpolation stage is followed by a sample-and-hold function where the data points from the interpolator are held for eight( $64 \times fs$ ) clock cycles. The resulting frequency response is a sinx/x characteristics with zeros at  $8 \times fs$  multiples. The sinx/x zeros completely attenuate signal at  $8 \times fs$  and largely suppress the remaining energy of the images. The  $8 \times fs$  interpolation followed by the  $8 \times fs$  sample-and-hold results in data at a rate of  $64 \times fs$ .

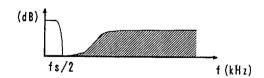

The delta-sigma modulator takes in the  $64 \times$  fs data and performs 4th order noise shaping. In the digital modulator of the AK4318, 18bit audio data is modulated to a 1-bit,  $64 \times$  fs signal. The 4th order noise shaper allows 1-bit quantization to support 18-bit audio processing by suppressing quantization noise in the bandwidth of interest. Figure 4 shows the frequency spectrum of the modulator output.

Figure 4. Modulator Output Spectrum

The AK4318's digital modulator is followed by a D-to-A converter that translates the 1-bit signal into a series of charge packets. The magnitude of the charge in each packet is determined by sampling of a voltage reference onto a switched capacitor, where the polarity of each packet is controlled by the 1-bit signal. The result is a 1-bit D/A conversion process that is very insensitive to clock jitter. This is a major improvement over previous generations of 1-bit D/A converters where the magnitude of charge in the D/A process is determined by switching a current reference for a period of time defined by periods of the master clock.

# OPERATION OVERVIEW

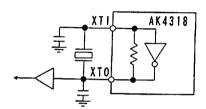

# Market System Clock Input

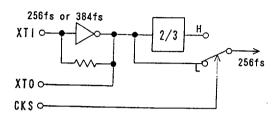

The external clocks which are required to operate the AK4318 are XTI(256fs/384fs), LRCK(fs), BICK(32fs~). The master clock (XTI) should be synchronized with LRCK but the phase is free of care. The XTI is used to operate the digital interpolation filter and the delta-sigma modulator. The frequency of XTI is determined by the sampling rate(LRCK), and the setting of the Clock Select, CKS pin. Setting CKS "L" selects an XTI frequency of 256fs while setting CKS "H" selects 384fs. When the 384fs is selected, the internal master clock becomes 256fs(=384fs\*2/3).

The master clock can be either a crystal resonator placed across the XTI and XTO pin, or external clock input to the XTI pin with the XTO pin left floating. Not only CMOS clock but sine wave signal with IVp-p can be input to the XTI pin by AC coupling. Table 1 illustrates standard audio word rates and corresponding frequencies used in the DAC.

As the AK4318 includes the phase detect circuit for LRCK, the AK4318 is reset automatically when the synchronization is out of phase by changing the clock frequencies. Therefore, the reset is not needed except only upon power-up. (Please refer to the "System Reset" section.)

Figure 5. Internal Clock Circuit

Figure 6. Crystal resonator connection

| LRCK (fs) | CKS | ITX      | _ |

|-----------|-----|----------|---|

| (kHz)     |     | (MHz)    |   |

| 32. 0     | L   | 8. 1920  |   |

|           | H   | 12. 2880 |   |

| 44. 1     | L   | 11. 2896 |   |

| 44.1      | H   | 16. 9344 |   |

| 48. 0     | L   | 12. 2880 |   |

| 40.0      | H   | 18. 4320 | 1 |

Table 1. Examples of System Clock

All external clocks(XTI.BICK, LRCK) should always be present whenever the AK4318 is in normal operation mode(PD="H"). If these clocks are not provided, the AK4318 may draw excess current and do not possibly operate properly because the device utilizes dynamic refreshed logic internally. If the external clocks are not present, the AK4318 should be in the power-down mode(PD="L").

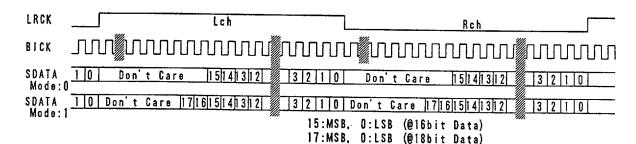

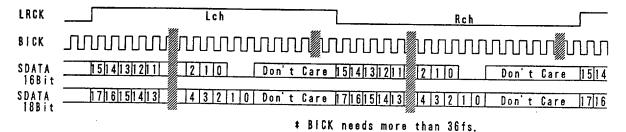

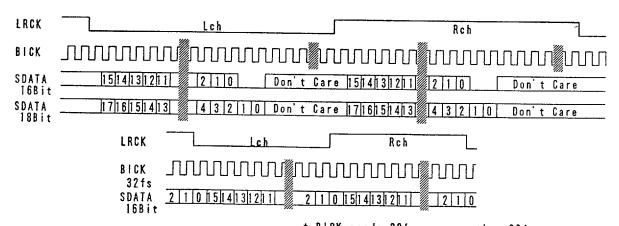

#### ■ Serial Data Interface

Data is input to the AK4318 via three serial input pins(SDATA, BICK, LRCK). The AK4318 supports four serial data formats which can be selected via DIFO and DIFI pins(Table 2). Format 0 is compatible with existing 16-bit DACs and digital filters. Format 1 is an 18-bit version of format 0. Format 2 is similar to AKM ADCs (AK5339/40/45/89/90) and many DSP serial ports. Format 3 is compatible with the I2S serial data protocol. Format 2 and 3 support 18-bit input or 16-bit followed

by two zeros. In all serial input modes. the serial data is MSB-first and 2's complement format.

| DIF1 | DIFO | Mode                           | Fig |

|------|------|--------------------------------|-----|

| 0    | 0    | 0: LSB Justified, 16bit        | 7   |

| 0    | 1    | 1: LSB Justified, 18bit        | 7   |

| 1    | 0    | 2: MSB Justified, 16-18bit     | 8   |

| 1    | 1    | 3: I <sup>2</sup> S Compatible | 9   |

Table 2. Digital Input Formats

# BICK needs more than 36fs at mode 1. Figure 7. Digital Input Formats 0 & 1

Figure 8. Digital Input Format 2

\* BICK needs 32fs or more than 36fs.

Figure 9. Digital Input Format 3

## ■ De-emphasis filter

The AK4318 includes the digital deemphasis filter(tc=50/15us) by IIR filter. This filter corresponds to three sampling frequencies(32kHz, 44.1kHz, 48kHz). The de-emphasis filter selected by DEMO and DEM1 is enabled for input audio data. The de-emphasis is also disabled at DEMO="1" and DEM1="0".

| DEM1 | DEM O | Mode     |

|------|-------|----------|

| 0    | 0     | 44. lkHz |

| 0    | 1     | OFF      |

| 1    | 0     | 48kHz    |

| 1    | 1     | 32kHz    |

Table 3. De-emphasis filter control

# ■ Zero detection & Zero mute operation

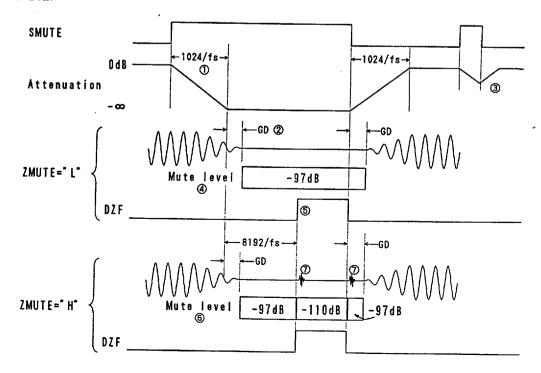

When the input data at both channels are continuously zeros for 8192 LRCK cycles, DZF goes to "H". DZF immediately goes "L" if input data are not zero after going DZF "H". Analog outputs condition at zero detection depends on the setting of ZMUTE pin. If ZMUTE is "H", analog outputs are muted by zero detection. When ZMUTE is "L", Analog outputs aren't muted by zero detection. When muting, the noise level on analog outputs is reduced up to the system noise level and the S/N is improved. However, the click noise occurs at the edges("  $\uparrow$   $\downarrow$ ") of DZF signal( $\circlearrowleft$  in Figure 10).

#### M Soft mute operation

When SMUTE goes "H", the output signal is attenuated by  $-\infty$  during 1024 LRCK cycles. If ZMUTE is set "H" at the same time, analog outputs are muted by zero detection. When SMUTE is returned to "L", the mute is cancelled and the output attenuation gradually changes to 0dB during 1024 LRCK cycles. If the soft mute is cancelled within 1024 LRCK cycles after starting the operation, the attenuation is discontinued and returned to 0dB. The soft mute is effective for changing the signal source without stopping the signal transmmission.

#### Notes:

- ①The output signal is attenuated by  $-\infty$  during 1024 LRCK cycles(1024/fs).

- ②Analog output corresponding to digital input have the group delay(GD).

- 3 If the soft mute is cancelled within 1024 LRCK cycles, the attenuation is discontinued and returned to 0dB.

- 4As analog outputs aren't muted at ZMUTE "L", the noise level on analog outputs is -97dB.

- (5) When the input data at both channels are continuously zeros for 8192 LRCK cycles, DZF goes to "H". DZF immediately goes "L" if input data are not zero after going DZF "H".

- ⑥As analog outputs are muted at ZMUTE "H", the noise level on analog outputs is about -110dB.

- OClick noise about -50dB occurs at the edges("  $\uparrow \downarrow$ ") of DZF signal. Please mute the analog output externally if the click noise influences system application(Figure 12).

Figure 10. Soft mute and zero detection

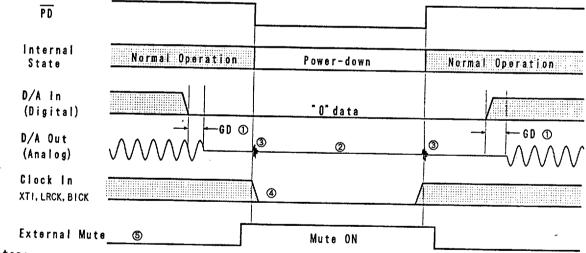

#### Power-Down

The AK4318 are placed in the power-down mode by bringing  $\overline{PD}$  pin "L" and the analog outputs are floating(Hi-Z). Figure 11 shows an example of the system timing at the power-down and power-up.

#### Notes:

- ①Analog output corresponding to digital input have the group delay(GD).

- ②Analog outputs are floating(Hi-Z) at the power-down mode. The output noise level is about -110dB.

- ③Click noise about -50dB occurs at the edges("↑  $\downarrow$ ") of  $\overline{PD}$  signal.

- (4) When the external clocks(XTI, BICK, LRCK) are stopped, the AK4318 should be in the power-down mode.

- ⑤Please mute the analog output externally if the click noise(③) influences system application. The timing example is shown in this figure. Please refer to Figure 12.

Figure 11. Power-down/up sequence example

ASAHI KASEI

#### ■ System Reset

The AK4318 should be reset once by bringing  $\overline{PD}$  "L" upon power-up. The internal timing starts clocking by LRCK " \( \)" upon exiting reset.

If the phase difference between LRCK and internal control signals is larger than  $\pm 1/16 \sim -1/16$  of word period(1/fs), the synchronization of internal control signals with LRCK is done automatically at the first rising edge of LRCK. Since RAM address shifts during this synchronization, correct data would not be output until 18 sampled data are input.

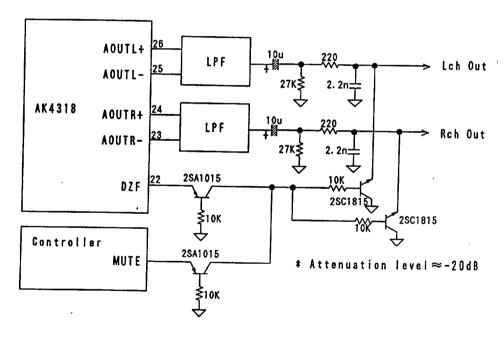

#### External mute circuit

Some click noise may occur at the edges("  $\uparrow \downarrow$ ") of PD signal and the zero detection with ZMUTE="H". The click noise which occurs at the edges("  $\uparrow \downarrow$ ") of PD signal can be avoided by controlling the external mute circuit using the signal like 5 in Figure 11. The click noise at the zero detection can be also avoided by muting the analog outputs using DZF signal. The external mute circuit example is shown in Figure 12.

Figure 12. External mute circuit example

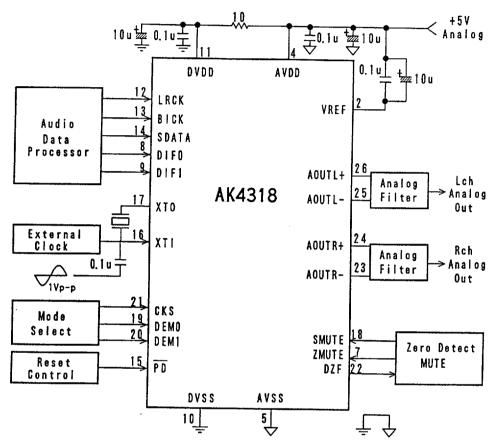

# SYSTEM DESIGN

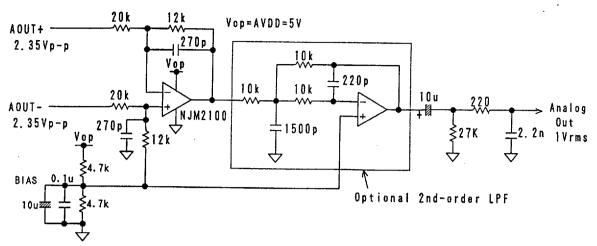

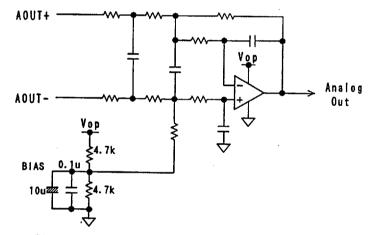

Figure 13 shows the system connection diagram. The examples of external analog filter are shown in Figure 15. An evaluation board[AKD4318] is available which demonstrates the optimum layout and power supply arrangements.

Figure 13. Typical Connection Diagram

ASAHI KASEI

# ■ System design consideration

# 1. Grounding and Power Supply Decoupling

To minimize coupling by digital noise, decoupling capacitors should be connected to AVDD and DVDD, respectively. AVDD is supplied from analog supply in system and DVDD is supplied from AVDD via  $10\,\Omega$  resistor. Decoupling capacitors should be as near to the AK4318 device as possible, with the low value ceramic capacitor being the nearest.

## 2. On-chip voltage reference

The on-chip voltage reference is output on the VREF pin. An electrolytic capacitor less than 10uF in parallel with a 0.1uF ceramic capacitor attached to this pin eliminates the effects of high frequency noise. Especially, the ceramic capacitor should be connected to VREF pin within a few mm as near as possible. No load current may be driven from the VREF output pin. All signals, especially clocks, should be kept away from the VREF pin in order to avoid unwanted coupling into the AK4318.

## 3. Output analog filter circuit

The analog signals are output from the differential output pins of each channel. The both outputs are summed externally. The analog outputs are the differential voltage,  $\Delta V_{\text{AOUT}}=(\text{AOUT}+)-(\text{AOUT}-)$  between AOUT+ and AOUT-. The bias voltage of the external summing circuit is supplied externally. The output signal range is  $\pm 1.175V(\text{typ})$  centered at an internal common voltage. If the summing gain is 1, the output range is  $\pm 2.35V(\text{typ})$ . The input data format is 2's complement. The output voltage( $\Delta V_{\text{AOUT}}$ ) is a positive full scale for 7FFFH(@16bit) and a negative full scale for 8000H(@16bit). The ideal  $\Delta V_{\text{AOUT}}$  is 0V for 0000H(@16bit).

DC offsets on analog outputs are eliminated by AC coupling since DAC outputs have DC offsets of a few mV.

The primary function of the additional analog filter is to attenuate the noise generated by the delta-sigma modulator beyond the audio passband. The AK4318 performance within the audio passband(DC~20kHz, @fs=48kHz) is constant regardless of the outband attenuation of the additional analog filter. Figure 14-1 shows the external 3rd-order LPF for the differential outputs of the AK4318. Only the 1st summing stage is necessary to achieve the specified characteristics of the AK4318 in the audio passband. However, as the outband noise moves into the audible band at low sampling rate, careful attention is required. Another example by one op-amp is shown in Figure 14-2.

Figure 14-1. 3rd-order LPF example for the differential output

Figure 14-2. 3rd-order LPF example by one op-amp

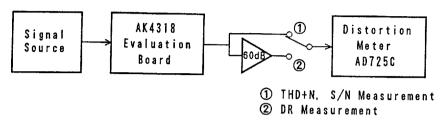

# MEASURING SYSTEM

The measuring system consists of an evaluation board[AKD4318], a digital signal source and a distortion meter[SHIBASOKU, AD725C or equivalent]. The digital signal is taken from the CD test disk or the AKD43XX which generates sine wave using ROM data.

Figure 15. Measuring Block Diagram

The effects of out-of-band noise must be well taken care of when measuring THD+N, dynamic range and S/N. Table 4 shows the conditions of input signal and measurement filter used in the above measurement block. The proper use of a measurement bandlimiting filter is critical for evaluating the in-band performance of systems with low-order analog filters. The measurement bandwidth must be properly limited to prevent outband energy from influencing the measurement. The dynamic characteristics are specified at fs=48kHz. Please refer to the manual of the evaluation board about the measurement example.

| parameter              | Input signal      | Measurement Filter  |  |  |

|------------------------|-------------------|---------------------|--|--|

|                        |                   | (Shibasoku 725C)    |  |  |

| THD+N                  | 1kHz, OdB         | 20kHz LPF           |  |  |

| Dynamic Range          | 1kHz,-60dB        | 20kHz LPF, A-Weight |  |  |

| S/N                    | 1kHz, 0dB/"0"data | 20kHz LPF, A-Weight |  |  |

| Interchannel Isolation | 1kHz, OdB         | 20kHz LPF           |  |  |

Table 4. Measuring Conditions

# PACKAGE