# MOS INTEGRATED CIRCUIT $\mu$ PD70423

# V55SC™ 16-BIT MICROPROCESSOR

## **DESCRIPTION**

The  $\mu$ PD70423 (also called V55SC) is a microprocessor with a 16-bit CPU, RAM UART, timer, DMA controller, and interrupt controller all integrated on one chip.

The V55SC is one in the V55 family and is software compatible with the single-chip microcomputer mPD70322, and (also called V25™ and V35™). The V55 family is a high-order V25 model and is capable of higher functions, and higher performance and can be used in all application fields.

Especially, the serial data communication function in the V55SC is enhanced.

#### **FEATURES**

- Internal 16-bit architecture

- External 16/8-bit selectable data bus width

- Software compatible with the V20™, V30™ (native mode), V25, and V35 (There are additional instructions.)

- Minimum instruction cycle: 160 ns/12.5 MHz (for an external clock of 25 MHz)

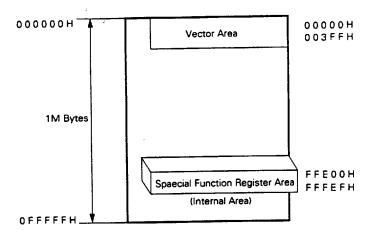

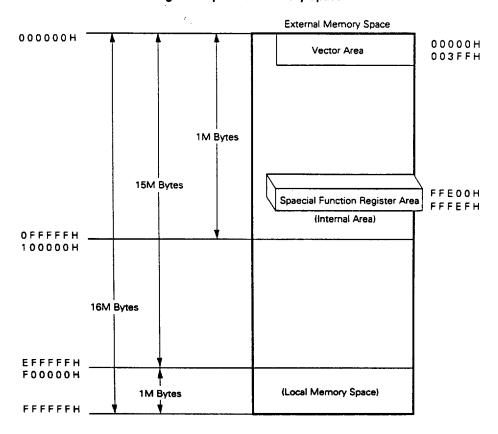

- Memory space: Mainmemory space: 15M bytes

Local memory space: 1M byte (mapping onto an area contiguous with the main memory

space)

• Register file space (in on-chip RAM) : 512 bytes/16 register banks

I/O space

: 64K bytes

- Partitioning the memory in varisble sizes (maximum of 6 blocks) and automatic wait control

- I/O line (input port: 5-bit, input/output port: 51 bits)

- Universal asynchronous receiver/transmitter (UART): 1 channel

- On-chip exclusive baudrate generator

- Start-up transmission mode

- Multiprotocol serial controller (MPSC): 2 channels

- μPD72001/72002 subset functions

- · On-chip exclusive baud rate generator

- · SYNC mode, ASYNC mode, HDLC mode

- DMA controller (DMAC): 2 channels

- 4 types of DMA transmission modes (single transfer, demand release, single step, burst)

- Intelligent DMA mode (ring buffer management operation)

- DMA transmission rate: Maximum 4.1M word/sec (during I/O memory transmission in the burst mode)

- · DMA memory address register (linear): 24 bits

- Terminal counter: 21 bits

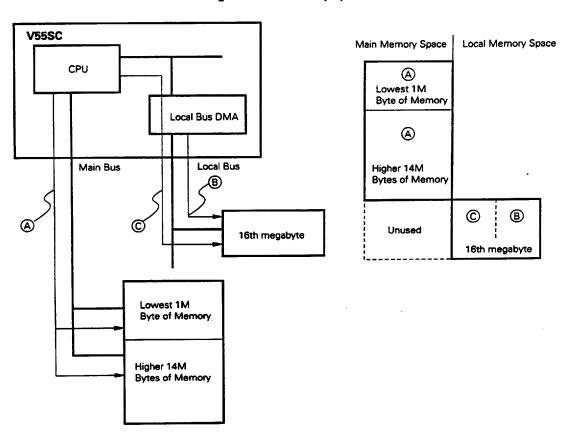

- Local bus DMA controller (LDMAC): 4 channels

- · Block chain operation

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

The mark 🖈 shows major revised points

Document No. (O.D.No. ID-8206A) Date Published March 1993 P Printed in Japan

NEC Corporation 1991

**■ 6427525 0066473 937 ■**

- Interrupt controller

- Multiple interrupt serving control according to programmable priority (4 levels)

- 3 types of interrupt response formats

Vector interrupt function, register bank switching function, macro service function

- Dram and pseudo SRAM refresh function

- Wachdog timer function

- Standby function (STOP mode, HALT mode, IDLE mode)

- · On-chip clock generation circuit

- 16-bit timer/counter: 4 channels

- Software interval timer (16 bits)

- · Address block wait insertion function and RAS/CAS switching timing generation function

## **USES**

• It can be used in sysyem control for data processing which uses serial communication (Data processing terminals, G4 facsimiles, switching devices, television telephones, etc.)

### **ORDING INFORMATION**

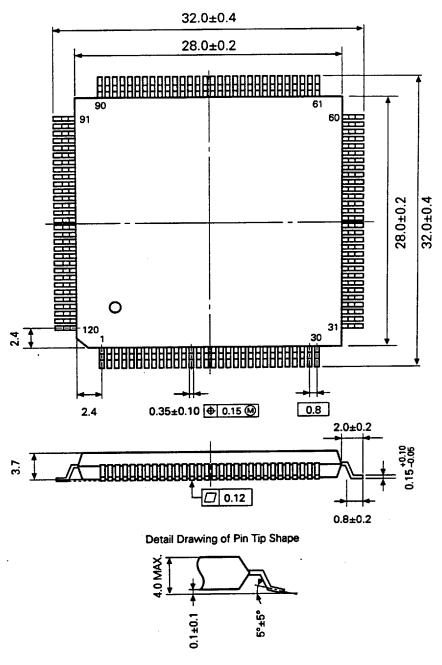

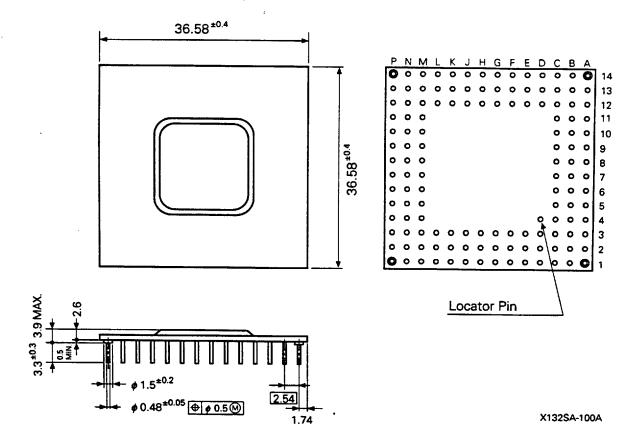

| Ordering Name  | Package                   | Maximum Operating Frequency (MHz) | Quality Grade |

|----------------|---------------------------|-----------------------------------|---------------|

| μPD70423GD-5BB | 120-pin plastic QFP (□28) | 12.5                              | Standard      |

| μPD70423SA     | 132-pin plastic PGA       | 12.5                              | Standard      |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

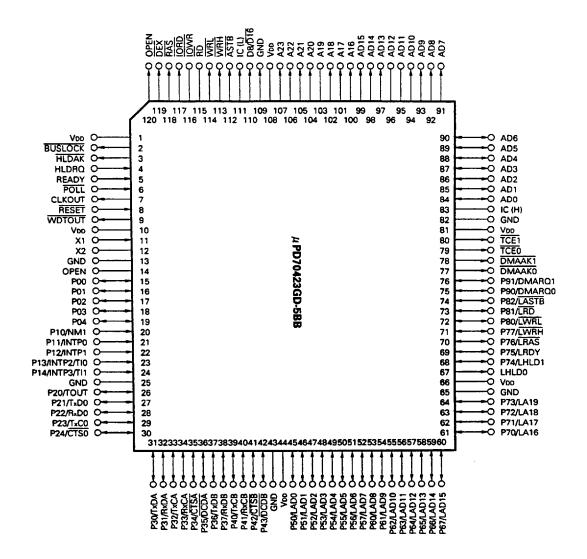

### PIN CONNECTION DIAGRAM (TOP VIEW)

## (1) 120-Pin Plastic QFP

Remarks IC: Internally Connected

Note 1. The IC (H) pin should be connected to  $V\infty$  externally by way of a pull-up resister (1 to 10 k $\Omega$ ).

2. The IC (L) pin should be connected to GND externally by way of a pull-up resister (1 to 10 k $\Omega$ ).

3. The OPEN pin should not be connected to anything.

| Na  | Cional Nama | Port         | No. | Signal Name | Port | No.        | Signal Name | Port |

|-----|-------------|--------------|-----|-------------|------|------------|-------------|------|

| No. | Signal Nane | <u> </u>     | -   | Signal Name | Pon  | <u> </u>   | Signal Name | Port |

| F1  | LRD         | P81          | К3  | AD2         | _    | N3         | AD9         |      |

| F2  | LWRL        | P80          | K12 | POLL        | -    | N4         | AD11        |      |

| F3  | LRAS        | P76          | K13 | WDTOUT      | _    | N5         | AD14        | _    |

| F12 | INTP1       | P12          | K14 | X1          | _    | N6         | A18         | _    |

| F13 | NMI         | P10          | L1  | AD0         | _    | N7         | A21         | _    |

| F14 | -           | P04          | L2  | AD3         | _    | N8         | A23         | _    |

| G1  | NC          | 1            | L3  | AD6         | _    | N9         | D8/D16      | _    |

| G2  | DMARQ0      | P90          | L12 | BUSLOCK     | _    | N10        | ASTB        | _    |

| G3  | LASTB       | P82          | L13 | READY       | -    | N11        | IOWR        | _    |

| G12 | _           | P03          | L14 | RESET       | _    | N12        | DEX         | _    |

| G13 | _           | P02          | M1  | AD1         | _    | N13        | Voo         | _    |

| G14 | _           | P01          | M2  | AD5         | _    | N14        | HLDRQ       | -    |

| Н1  | DMARQ1      | P91          | МЗ  | NC          | _    | P1         | AD7         | _    |

| H2  | DMAAK0      | _            | M4  | AD8         | _    | P2         | AD10        | _    |

| НЗ  | DMAAK1      | _            | M5  | AD12        | _    | Р3         | AD13        | _    |

| H12 | OPEN        | _            | M6  | A16         | _    | P4         | AD15        | -    |

| H13 |             | P00          | M7  | A20         | _    | P5         | A17         | -    |

| H14 | NC          | _            | M8  | Voo         | _    | P6         | A19         | _    |

| J1  | TCE0        | _            | М9  | WRH         | _    | <b>P</b> 7 | NC          | _    |

| J2  | TCE1        | _            | M10 | IORD        | _    | P8         | A22         | _    |

| J3  | GND         | _            | M11 | NC          | -    | P9         | GND         | _    |

| J12 | Voo         | _            | M12 | NC          | _    | P10        | IC (L)      |      |

| J13 | X2          | _            | M13 | HLDAK       | -    | P11        | WRL         | -    |

| J14 | GND         | <del>-</del> | M14 | CLKOUT      | _    | P12        | RD          | _]   |

| K1  | Voo         | _            | N1  | AD4         | _    | P13        | RAS         | _    |

| K2  | IC (H)      | _            | N2  | NC          | _    | P14        | OPEN        | _    |

Remarks IC: Internally Connected

NC: Non-Connection

Note 1. The IC (H) pin should be connected to V $\infty$  externally by way of a pull-up resister (1 to 10  $k\Omega$ ).

2. The IC (L) pin should be connected to GND externally by way of a pull-up resister (1 to 10  $k\Omega$ ).

3. The OPEN pin should not be connected to anything.

**■** 6427525 0066476 646 **■**

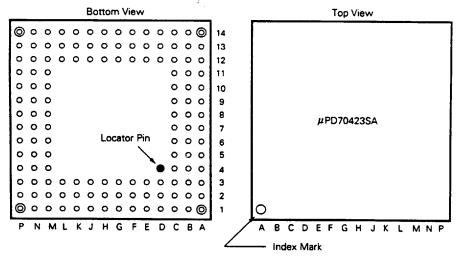

## (2) 132-Pin Plastic PGA

Remarks The locator pin is not included in the pin numbers.

| No.        | Signal Nane | Port | No.        | Signal Name | Port | No.        | Signal Name | Port |

|------------|-------------|------|------------|-------------|------|------------|-------------|------|

| Ai         | LAD15       | P67  | <b>B</b> 5 | LAD7        | P57  | C9         | RxCB        | P41  |

| A2         | LAD13       | P65  | B6         | LAD5        | P55  | C10        | DCDA        | P35  |

| А3         | LAD10       | P62  | B7         | LAD2        | P52  | C11        | RxDA        | P31  |

| A4         | LAD9        | P61  | B8         | LAD0        | P50  | C12        | NC          | _    |

| <b>A</b> 5 | LAD6        | P56  | B9         | DCDB        | P43  | C13        | TxC0        | P23  |

| <b>A</b> 6 | LAD4        | P54  | B10        | RxDB        | P37  | C14        | GND         | _    |

| A7         | LAD1        | P51  | B11        | CTSA        | P34  | D1         | LHLD1       | P74  |

| <b>A8</b>  | NC          |      | B12        | TxCA        | P32  | D2         | GND         | _    |

| A9         | GND         | _    | B13        | NC          | _    | DЗ         | LA17        | P71  |

| A10        | CTSB        | P42  | B14        | RxD0        | P22  | D12        | CTS0        | P24  |

| A11        | TxCB        | P40  | C1         | LHLD0       | _    | D13        | TxD0        | P21  |

| A12        | TxDB        | P36  | C2         | LA18        | P72  | D14        | INTP3/TI1   | P14  |

| A13        | RxCA        | P33  | СЗ         | NC          | _    | E1         | LWRH        | P77  |

| A14        | TxDA        | P30  | C4         | NC          | _    | E2         | LRDY        | P75  |

| B1         | LA19        | P73  | C5         | LAD12       | P64  | <b>E</b> 3 | Voo         | 1    |

| B2         | LA16        | P70  | C6         | LAD8        | P60  | E12        | TOUT        | P20  |

| <b>B</b> 3 | LAD14       | P66  | <b>C</b> 7 | LAD3        | P53  | E13        | INTP2/TI0   | P13  |

| B4         | LAD11       | P63  | C8         | Voo         | _    | E14        | INTPO       | P11  |

**■** 6427525 0066478 419 **■**

# **CONTENTS**

| 1.         | PIN  | FUNCTI  | ONS                                            | 10         |

|------------|------|---------|------------------------------------------------|------------|

|            | 1.1  | PIN FU  | NCTION LIST                                    | 10         |

|            |      | 1.1.1   | Port Functions                                 | 10         |

|            |      | 1.1.2   | Non-Port Functions                             | 12         |

| _          |      |         |                                                |            |

| 2.         | BLO  | CKCON   | FIGURATION                                     | 15         |

|            | 2.1  | BUS C   | ONTROL UNIT (BCU)                              | 45         |

|            | 2.2  | EXECU   | TION UNIT (EXU)                                | 46         |

|            | 2.3  | LUCAL   | BUS HANDLER (LBH)                              | 45         |

|            | 2.4  | INTERP  | RUPT CONTROLLER (INTC)                         | 15         |

|            | 2.5  | UMA C   | UNIROLLER (DMAC)                               | 4-         |

|            | 2.6  | LOCAL   | BUS DMA CONTROLLER (LDMAC)                     |            |

|            | 2.7  | OMIVE   | RSAL ASYNCRONOUS TRANSMITTER (UATR)            | 15         |

|            | 2.8  | MOLI    | PROTOCOL SERIAL CONTROLLER (MPSC)              | 16         |

|            | 2.9  | TIMER/  | COUNTER UNIT (TCU)                             | 15         |

|            | 2.10 | WAICH   | IDOG TIMER (WDT)                               | 46         |

|            | 2.11 | PORTS   | (PORT)                                         | 45         |

|            | 2.12 | CLOCK   | GENERATOR (CG)                                 | 40         |

|            | 2.13 | SOFTW   | ARE INTERVAL TIMER (SIT)                       | 16         |

| _          |      |         |                                                |            |

| 3.         | CPU  | FUNCT   | ions                                           | 17         |

|            | 3.1  | FEATU   | RES                                            | 17         |

|            | 3.2  | REGIST  | ERS                                            | 18         |

|            |      | 3.2.1   | Register Banks                                 | 18         |

|            |      | 3.2.2   | General Registers (AW, BW, CW, DW)             | 20         |

|            |      | 3.2.3   | Pointers (SP, BP) and Index Registers (IX, IY) | 20         |

|            |      | 3.2.4   | Segment Registers (PS, SS, DS0, DS1)           | 21         |

|            |      | 3.2.5   | Expansion Segment Registers (DS2, DS3)         | 22         |

|            | 2.2  | 3.2.6   | Special Function Registers (SFR)               | :3         |

|            | 3.3  | PROCE   | AM COUNTER (PC)2                               | <u>'</u> 4 |

|            | 3.5  | PACAGO  | AM STATUS WORDS (PSW)2                         | <b>!4</b>  |

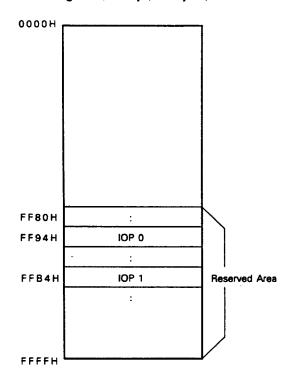

|            | 3.5  | 3.5.1   | RY SPACE2                                      | :5         |

|            |      |         | Main Memory Space                              | :5         |

|            |      | 3.5.3   | Special Function Register Area                 | :7         |

|            |      | 354     | Local Memory Space                             | Ð          |

|            | 3.6  | REGIST  | ER FILE SPACE                                  | 1          |

|            | 3.7  | I/O SPA | CE4                                            | 3          |

|            |      |         |                                                |            |

| 4.         |      | N BUS C | ONTROL FUNCTION4                               | 6          |

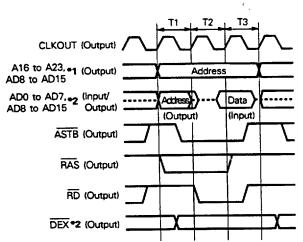

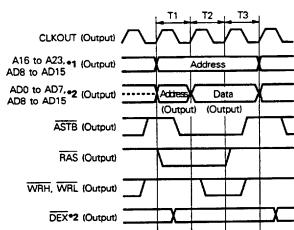

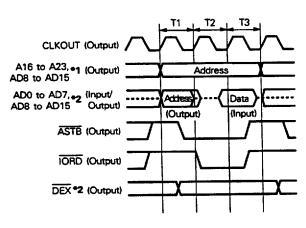

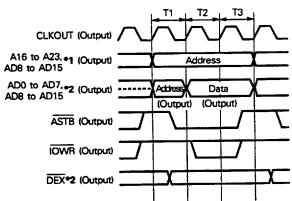

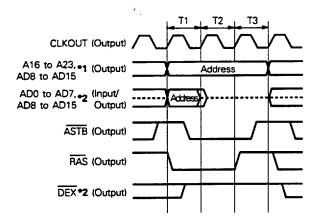

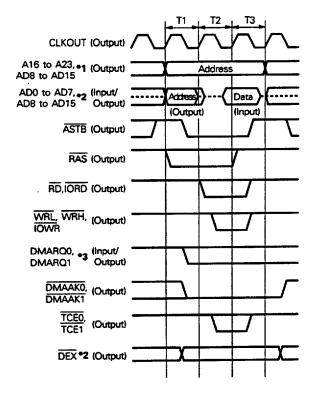

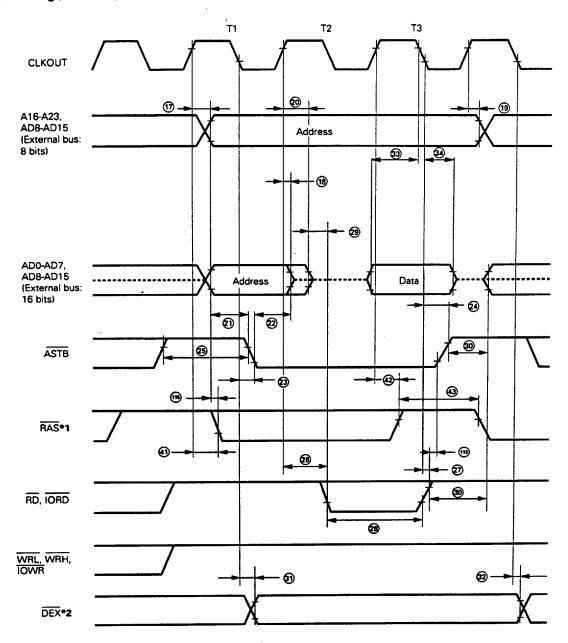

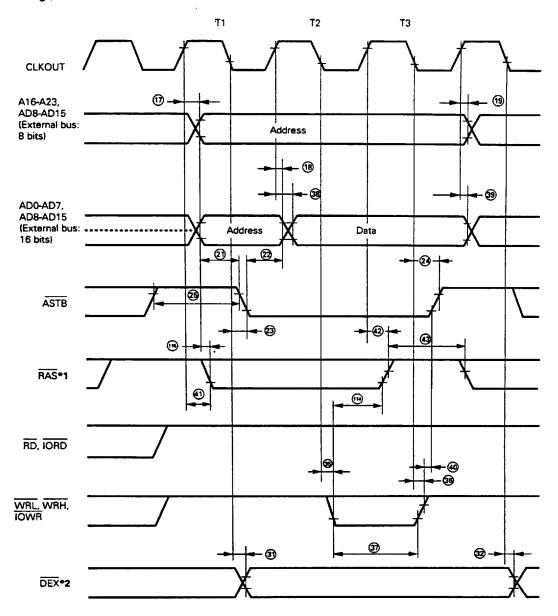

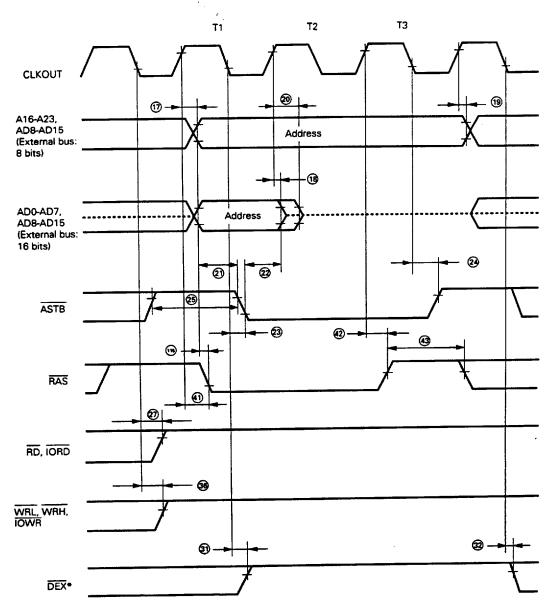

|            | 4.1  | BASICE  | BUS CYCLE4                                     | 6          |

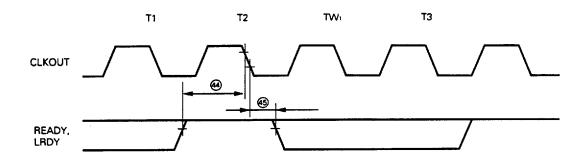

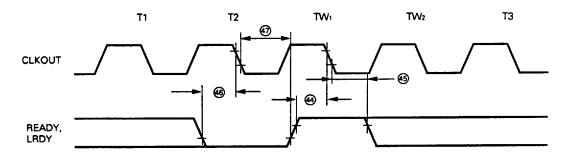

|            | 4.2  | MAIN B  | US WAIT4                                       | 9          |

| 5          | 100  | Al Dile | CONTROL EURICTION                              |            |

| <b>5</b> . | EUC/ | AL BUS  | CONTROL FUNCTION5                              | 1          |

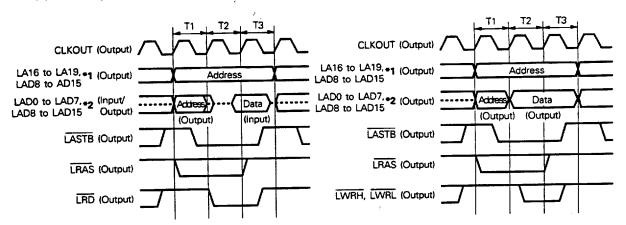

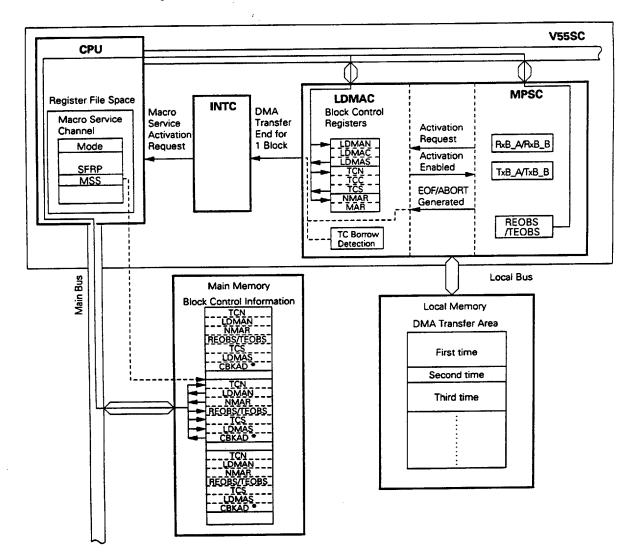

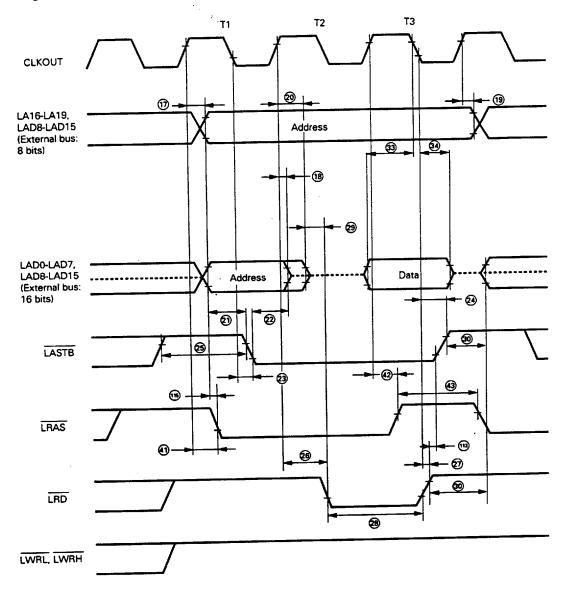

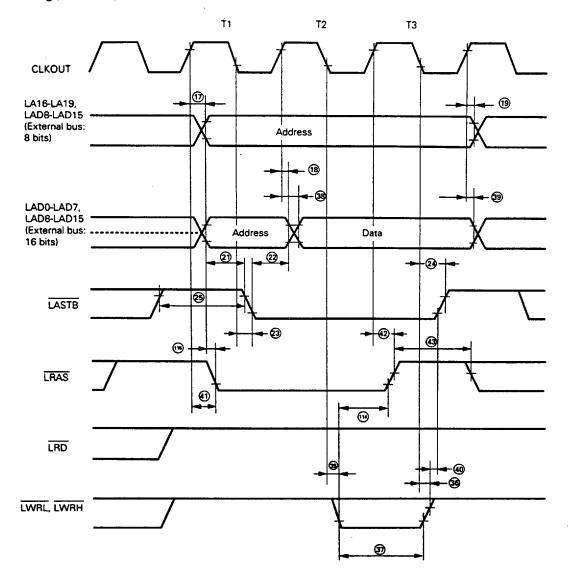

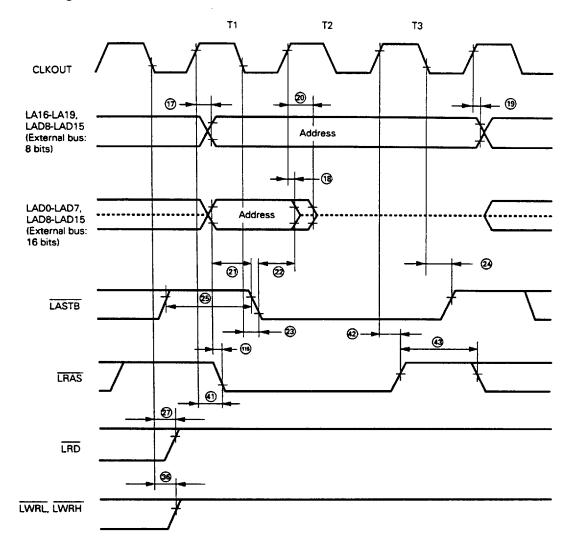

|            | 5.7  | RASIC I | BUS CYCLE5                                     | 1          |

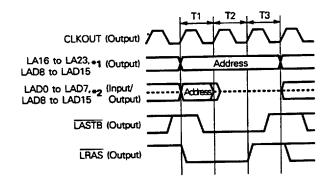

|            | 5.2  | LUCAL   | BUS WAIT5                                      | 3          |

| 6.  |       | RRUPT FUNCTION                                       |          |

|-----|-------|------------------------------------------------------|----------|

|     | 6.1   | FEATURES                                             | 54       |

| _   | D144  | FUNCTION (DMA CONTROLLER)                            |          |

| 7.  |       | FUNCTION (DMA CONTROLLER)                            |          |

|     | 7.1   | FEATURES                                             | 57       |

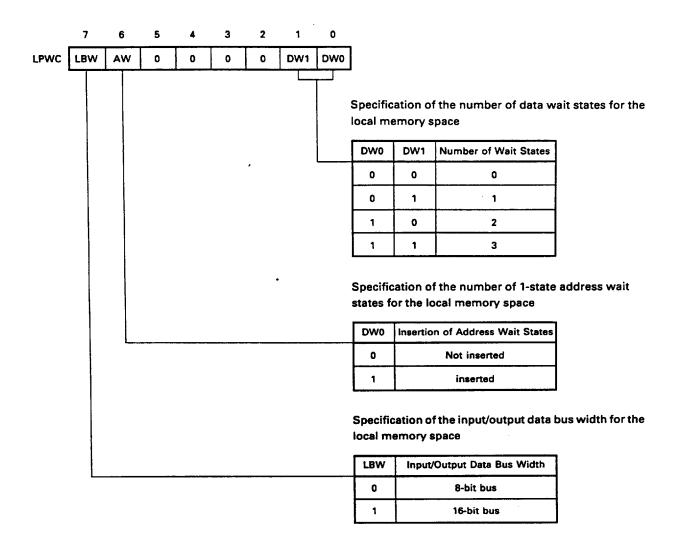

| 8.  | LOC   | AL BUS DMA FUNCTION (LOCAL BUS DMA CONTROLLER)       | EO       |

|     | 8.1   |                                                      | 55<br>En |

|     | 8.2   | LOCAL BUS DMA CONTROLLER (LDMAC) CONFIGURATION       | 59       |

| _   | HAD   | TELINOTION                                           |          |

| 9.  | 9.1   | T FUNCTION                                           |          |

|     |       |                                                      | 61       |

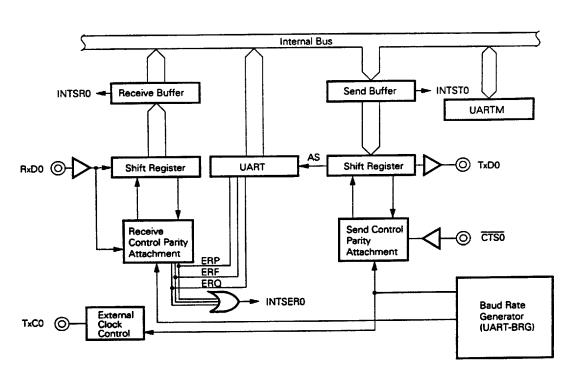

|     | 9.2   | UART CONFIGURATION                                   | 62       |

| 10. | MPS   | C FUNCTION                                           | 63       |

|     | 10.1  | FEATURES                                             | 63       |

|     | 10.2  | SUMMARY                                              | 65       |

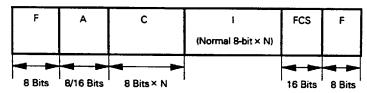

|     |       | 10.2.1 Bit Oriented Protocol (HDLC mode)             | 65       |

|     |       | 10.2.2 Character Oriented Protocol (SYNC mode)       | 66       |

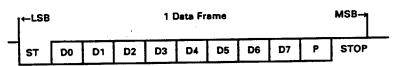

|     |       | 10.2.3 Start-stop Synchronized Format (ASYNCmode)    | 66       |

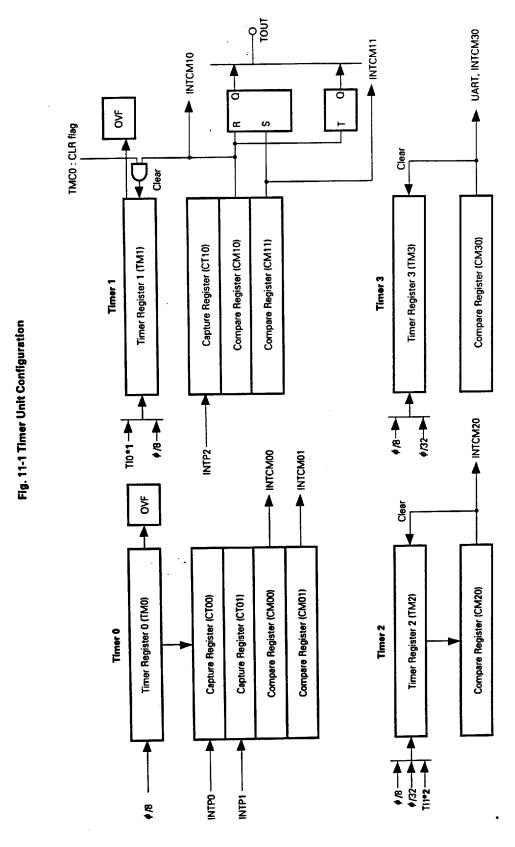

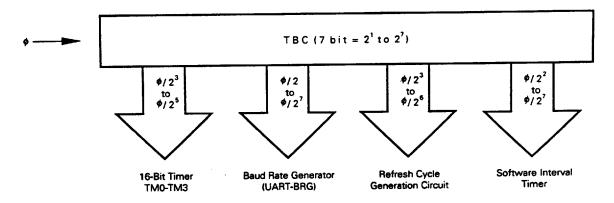

| 11. | TIME  | R FUNCTION                                           | 67       |

|     |       | FEATURES                                             |          |

|     | 11.2  | TIMER UNIT CONFIGURATION                             | 67       |

| 12. | WAT   | CHDOG TIMER FUNCTION                                 | 69       |

|     |       | FEATURES                                             |          |

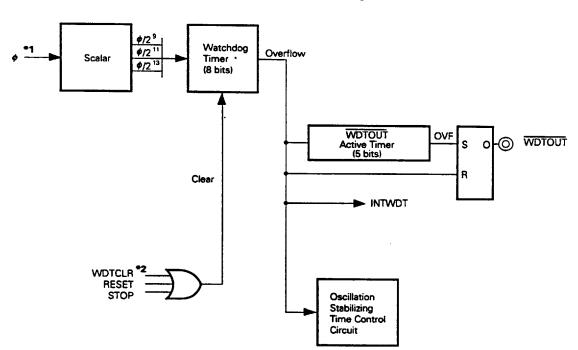

|     |       | WATCHDOG TIMER CONFIGURATION AND OPERATION           |          |

| 13. | STAI  | NDBY FUNCTION                                        | 70       |

|     |       | HALT MODE                                            |          |

|     |       | STOP MODE                                            |          |

|     |       | IDLE MODE                                            |          |

| 14  | CI OC | K GENERATION CIRCUIT                                 | 74       |

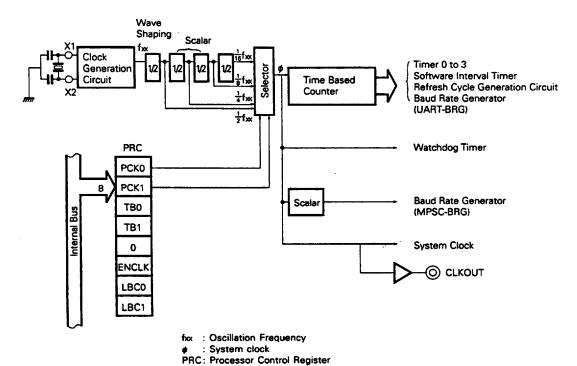

|     |       | CLOCK GENERATION CIRCUIT CONFIGURATION AND OPERATION |          |

|     |       |                                                      |          |

| 15. |       | WARE INTERVAL TIMER FUNCTION                         |          |

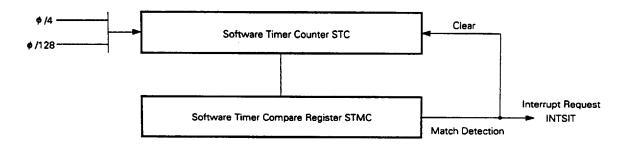

|     | 15.1  | SOFTWARE INTERVAL TIMER CONFIGURATION                | 73       |

| 16. |       | RUCTION SET                                          |          |

|     |       | INSTRUCTION ADDED TO V20 AND V30, OR V25 AND V35     |          |

|     |       | INSTRUCTION OPERATIONS                               |          |

|     | 16.3  | LIST OF THE INSTRUCTION SET                          | 105      |

| 17. | ELEC  | TRICAL SPECIFICATIONS (PRELIMINARY)                  | 128      |

| 18. | AC C  | HARACTERISTICS (TARGET VALUES)                       | 159      |

| 19. PACKAGE INFORMATION              |   |

|--------------------------------------|---|

| *.                                   |   |

| 20. RECOMMENDED SOLDERING CONDITIONS | 1 |

# **★ 1. PIN FUNCTIONS**

# 1.1 PIN FUNCTION LIST

# 1.1.1 Port Functions

| Pin Name   | Input/Output | Function                                                                     | Dual-Function Pin |

|------------|--------------|------------------------------------------------------------------------------|-------------------|

| P00 to P04 | Input/output | Port 0<br>Input/output specifiable bit-wise<br>5-bit input/output port       | _                 |

| P10 *      |              |                                                                              | NM1               |

| P11        |              |                                                                              | INTP0             |

| P12        | Input        | Port 1 5-bit input/output port                                               | INTP2             |

| P13        |              |                                                                              | INTP2/TI0         |

| P14        | 1            |                                                                              | INTP3/TI1         |

| P20        |              |                                                                              | TOUT              |

| P21        | 1            |                                                                              | TxD0              |

| P22        | 1            | Port 2<br>Input/output specifiable bit-wise                                  | RxD0              |

| P23        |              | 5-bit input/output port                                                      | TxC0              |

| P24        |              |                                                                              | CTS0              |

| P30        | -<br> <br> - |                                                                              | TxDA              |

| P31        | -            |                                                                              | RxDA              |

| P32        |              |                                                                              | TxCA              |

| P33        |              | Port 3                                                                       | RxCA              |

| P34        |              | Input/output specifiable bit-wise 8-bit input/output port                    | CTSA              |

| P35        | Input/output |                                                                              | DCDA              |

| P36        |              |                                                                              | TxDB              |

| P37        |              |                                                                              | RxDB              |

| P40        |              |                                                                              | ТхСВ              |

| P41        |              | Port 4                                                                       | RxCB              |

| P42        | 1            | Input/output specifiable bit-wise 4-bit input/output port                    | CTSB              |

| P43        |              |                                                                              | DCDB              |

| P50 to P57 |              | Port 5<br>Input/output specifiable in 8-bit units<br>8-bit input/output port | LAD0 to LAD7      |

| P60 to P67 |              | Port 6 Input/output specifiable in 8-bit units 8-bit input/output port       | LAD8 to LAD15     |

<sup>\*</sup> Cannot be used as a general-purpose port (non-maskable interrupt)

| Pin Name   | Input/Output | Function                                                  | Dual-Function Pin |

|------------|--------------|-----------------------------------------------------------|-------------------|

| P70 to P73 |              |                                                           | LA16 to LA19      |

| P74        |              |                                                           | LHLD1             |

| P75        |              | Port 7<br>Input/output specifiable bit-wise               | LRDY              |

| P76        | 1            | 8-bit input/output port                                   | LRAS              |

| P77        |              |                                                           | LWRH              |

| P80        | Input/output | _                                                         | LRWL              |

| P81        |              | Port 8<br>Input/output specifiable bit-wise               | LRD               |

| P82        |              | 3-bit input/output port                                   | LASTB             |

| P90        | 7            | Port 9                                                    | DMARQ0            |

| P91        | 7            | Input/output specifiable bit-wise 2-bit input/output port | DMARQ1            |

# 1.1.2 Non-Port Functions

# (1) Pin function for main bus control

| Pin Name    | Input/Output         | Function                                                                   | Dual-Function Pin |

|-------------|----------------------|----------------------------------------------------------------------------|-------------------|

| ASTB        |                      | Main bus external bus cycle address stobe signal output                    |                   |

| RD          |                      | Main bus external memory cycle address stobe signal output                 |                   |

| WRL         | Output               | Main bus external memory cycle lower byte data write strobe signal output  | 7                 |

| WRH         |                      | Main bus external memory cycle upperr byte data write strobe signal output |                   |

| READY       | Input                | Main bus external bus cycle ready signal input                             |                   |

| DEX         |                      | External bus cycle upper byte data enable signal output                    | 7                 |

| RAS         | Output               | DRAM row address latch timing signal output                                | 7                 |

| D8/D16      | Input                | External main bus data bus width selection signal input                    | 7                 |

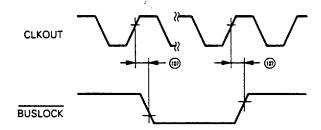

| BUSLOCK     | Output               | External main bus bus lock signal output                                   | <b>-</b>          |

| POLL        |                      | POLL signal (sampling in excution of POLL instruction) input               |                   |

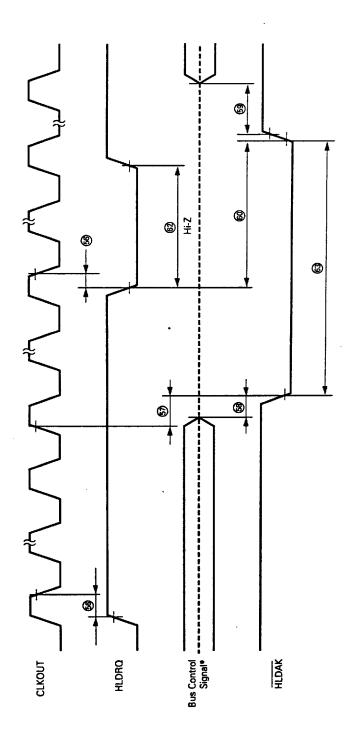

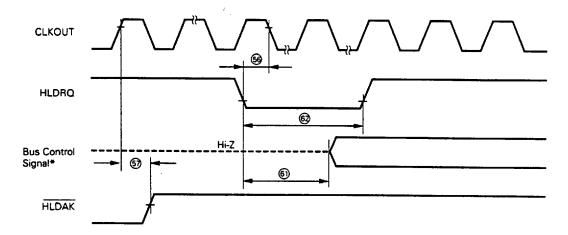

| HLDRQ       | Input                | Main bus hold request signal input                                         | 1                 |

| HLDAK       | Output               | Main bus hold acknowledge signal output                                    |                   |

| AD0 to AD15 | 3-state input/output | Main bus external bus cycle address/data multiplex signal input /output    |                   |

| A16 to A23  | 3-state output       | Main bus external bus cycle address signal output                          |                   |

| IORD        |                      | External I/O cycle data read strobe signal output                          |                   |

| IOWR        | Output               | External I/O cycle data write strobe signal output                         |                   |

| DMARQ0      |                      | DMA request signal output (channel 0)                                      | P90               |

| DMARQ1      | Input                | DMA request signal output (channel 1)                                      | P91               |

| DMAAK0      |                      | DMA acknowledge signal output (channel 0)                                  |                   |

| DMAAK1      | Output               | DMA acknowledge signal output (channel 1)                                  | ]                 |

| TCE0        | Output               | DMA end signal output (channel 0)                                          | ] -               |

| TCE1        |                      | DMA end signal output (channel 1)                                          |                   |

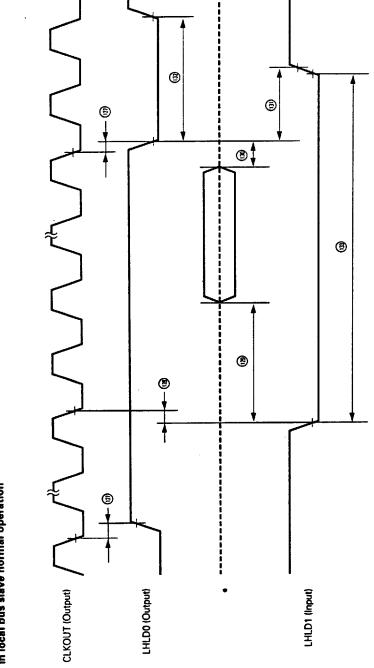

## (2) Pin function for local bus control

| Pin Name      | Input/Output | Function                                                    | Dual-Function Pin      |

|---------------|--------------|-------------------------------------------------------------|------------------------|

| LA16 to LA19  | Output       | Local bus cycle address signal output                       | P70 to P73             |

| LAD0 to LAD15 | Input/output | Local bus cycle address/data multiplex signal input/output  | P50 to P57, P60 to P67 |

| LRD           | Output       | Local bus cycle data read strobe signal output              | P81                    |

| LWRL          | Output       | Local bus cycle lower byte data write strobe signal output  | P80                    |

| LWRH          | Output       | Local bus cycle upper byte data write strobe signal output  | P77                    |

| LASTB         | Output       | Local bus cycle address strobe signal output                | P82                    |

| LRDY          | Input        | Local bus cycle ready signal input                          | P75                    |

| LRAS          | Output       | Local bus cycle DRAM row address latch timing signal output | P76                    |

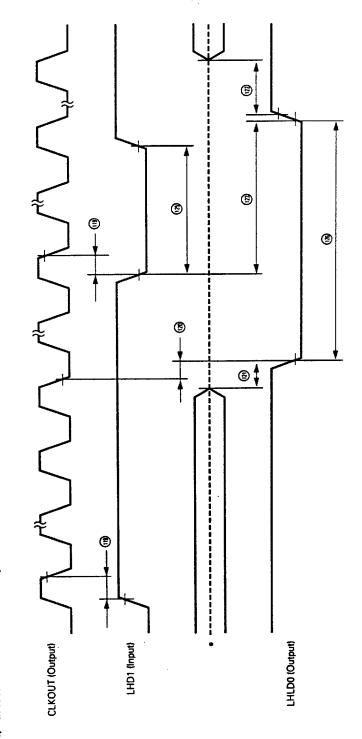

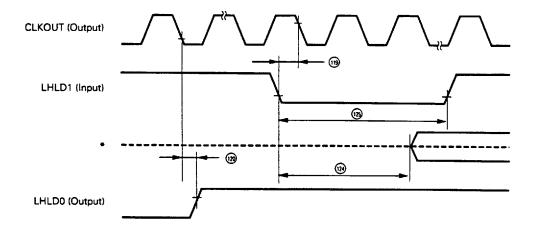

| LHLD1         | Input        | Local bus cycle hold request/acknowledge signal input       | P74                    |

| LHLD0         | Output       | Local bus cycle hold request/acknowledge signal output      | _                      |

# (3) Other pin f unctions

| Pin Name | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Dual-Function Pin |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| GND      |              | GND potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

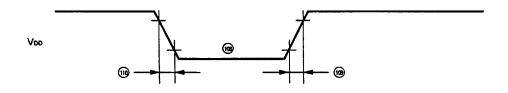

| Voo      |              | Positive power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ]                 |

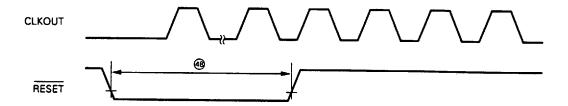

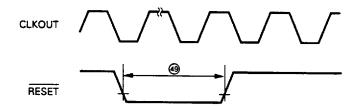

| RESET    | Input        | System reset signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                 |

| X1       | Input        | System clock generation crystal resonator/ceramic resonator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b></b>           |

| X2       | _            | connection pin. When an external clock is supplied, input to X1 and leave X2 open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| CLKOUT   | Output       | Internal system clock ø output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

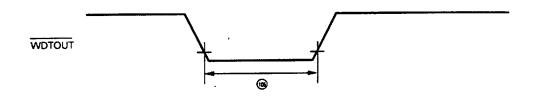

| WDTOUT   | Output       | Watchdog timer overflow signal output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| NMI      |              | Non-maskable interrupt request input *1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P10               |

| INTP0    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P11               |

| INTP1    |              | Francis in the second s | P12               |

| INTP2    | ] –          | External interrupt request input *2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P13/TI0           |

| INTP3    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P14/TI1           |

| TIO      |              | External event clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P13/TI0           |

| TI1      |              | External event clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P14/Ti1           |

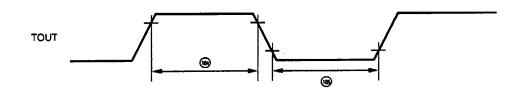

| тоит     | Output       | Timer unit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P20               |

| TxDo     | Output       | UART transmit data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P21               |

- \* 1. Since an NMI interrupt cannot be masked, an NMI interrupy is always started by valid edge detection (the pin level is read during the port 1 read operation).

- 2. Masking or disabling each interrupy (IE = 0) enables these pins to be used as a general-purpose input port.

| Pin Name | Input/Output | Function                                    | Dual-Function Pin |

|----------|--------------|---------------------------------------------|-------------------|

| RxD0     | Input        | UART receive data input                     | P22               |

| TxC0     | Output       | UART transmit clock output                  | P23               |

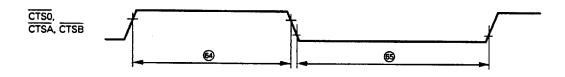

| CTS0     | Input        | UART transmit enable signal input           | P24               |

| TxDA     | Output       | MPSC channel A transmit data output         | P30               |

| RxDA     | Input        | MPSC channel A receive data input           | P31               |

| TxCA     | 1            | MPSC channel A transmit clock input/output  | P32               |

| RxCA     | Input/output | MPSC channel A receive clock input/output   | P33               |

| CTSA     | 1            | MPSC channel A transmit enable signal input | P34               |

| DCDA     | Input        | MPSC channel A receive enable signal input  | P35               |

| TxDB     | Output       | MPSC channel B transmit data output         | P36               |

| RxDB     | Input        | MPSC channel B receive data input           | P37               |

| TxCB     | lanut/num    | MPSC channel B transmit clock input/output  | P40               |

| RxCB     | Input/output | MPSC channel B receive clock input/output   | P41               |

| CTSB     | Input        | MPSC channel B transmit enable signal input | P42               |

| DCDB     | - Input      | MPSC channel A receive enable signal input  | P43               |

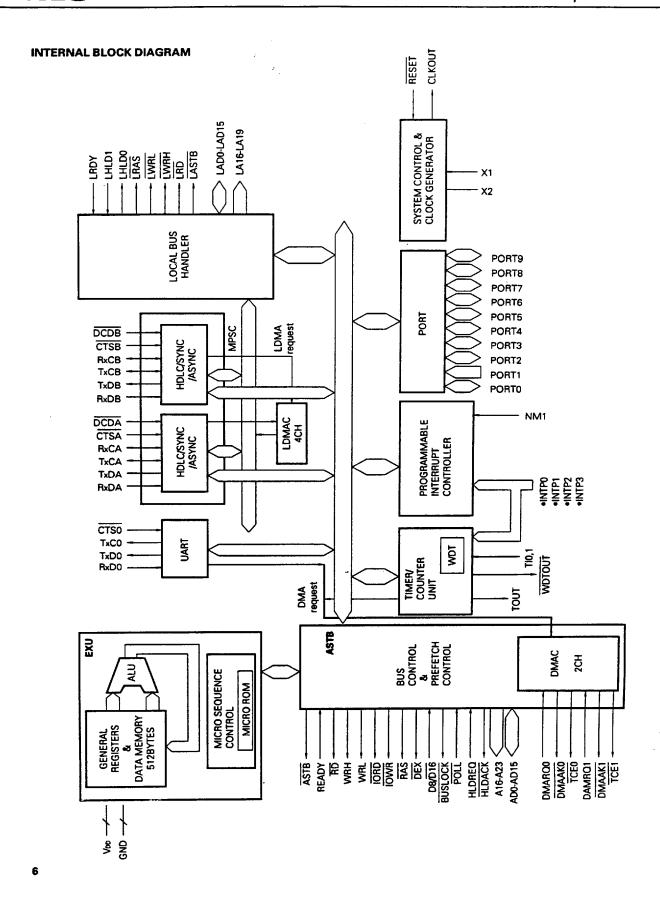

## 2. BLOCK CONFIGURATION

### 2.1 BUS CONTROL UNIT (BCU)

The BCU controls the main bus. The necessary bus cycles are activated in the BCU based on the physical addresses obtained by the execution unit (EXU).

#### 2.2 EXECUTION UNIT (EXU)

The EXU controls address calculation, arithmetic logical calculations, and data transfer using a microprogram (firm ware to control the micro sequencer based on the operation code decode calculations). Inside the EXU is an built-in 512-byte RAM (register file space).

#### 2.3 LOCAL BUS HANDLER (LBH)

The LBH controls the local bus.

## 2.4 INTERRUPT CONTROLLER (INTC)

All kinds of hardware interrupts generated by the on-chip peripheral hardware or generated externally are processed by either switching register banks, vectored interrupts, of macro-services. The priority of programmable 4-level interrupts can be controlled and multiple servicing control of the interrupt sources is also possible.

# 2.5 DMA CONTROLLER (DMAC)

The DMAC is a general-purpose DMA controller, and can handle the memory space 16M bytes linearly. Besides the I/O memory transfer mode and memory-to-memory transfer mode, the operating modes consist of an intelligent DMA (ring buffer format) mode and next address specification mode.

# 2.6 LOCAL BUS DMA CONTROLLER (LDMAC)

The LDMAC is a MPSC-only DMA controller and performs DMA transfer between the local bus and MPSC. The operating modes consist of a normal transfer mode and a block-chain operating mode.

# 2.7 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

The UART obtains data synchronization from the start-stop bit of the serial data communication function and it supports the start-stop transmission format.

# 2.8 MULTIPROTOCOL SERIAL CONTROLLER (MPSC)

The MPSC supports the start-stop transmission format (ASYNC mode) of the serial data communication function, and it supports character oriented protocol (SYNC mode) and bit oriented protocol (HDLC mode). ASYNC of the MPSC supports the same communication protocol as the UART, however, the method for setting commands and some functions are different.

# 2.9 TIMER/COUNTER UNIT (TCU)

The TCUisanon-chip16-bittimer/counterandcan interval timer free running counter and eventcounter.

### 2.10 WATCHDOG TIMER (WDT)

The WDT is an on-chip 8-bit watchdog timer that detects inadvertent program loops and system abnormalities. It is equipped with a WDTOUT pin for external notification of the generation of a watchdog timer interrupt.

#### 2.11 PORTS (PORT)

Port is provided with 56 port pins and includes dual-function pins not only as the external interrupt input but as the control pins.

## 2.12 CLOCK GENERATOR (CG)

The CG generates the 1/2, 1/4, 1/8 and 1/16 frequency clock of the crystal oscillator/ceramic oscillator connected to pins X1 and X2, and supplies the CPUoperating clock.

### 2.13 SOFTWARE INTERVAL TIMER (SIT)

The SIT is an on-chip 16-bit interval timer which is used as the software timer function or the clock function. By selecting the input clock (count clock) and by setting the software timer compare register, the interval interrupt can be set.

16

**■** 6427525 0066488 368 **■**

### 3. CPU FUNCTION

The V55SC has as CPU which is software compatible with the V20 and V30 (native mode), and with the V25 and V35.

## 3.1 FEATURES

- Software upward compatible with the V20 and V30 (native mode), and with the V25 and V35. (has additional instructions)

- Minimum instruction cycle: 160 ns/12.5 MHz (using an external 25 MHz clock)

- Memory space: Main memory space: 16M bytes

Local memory space: 1M byte (mapped onto an area contiguous with the main memory space)

- Register file space (in on-chip RAM): 512 bytes/16 register banks

- I/O space: 64K bytes

- Register configuration (comparison with V20/V30 or V25/V35)

|         | ltem                                   | V20, V30 | V25, V35                                               | V55SC                                                  |

|---------|----------------------------------------|----------|--------------------------------------------------------|--------------------------------------------------------|

| Extend  | led segment register                   | No       | No                                                     | DS2. DS3                                               |

| Registe | er bank                                | No       | 8 banks (in memory space)                              | 16 banks (in register file space)                      |

|         | Mode flag                              | MD       | No                                                     | No                                                     |

|         | Register bank flag                     | No       | RB0 to RB2                                             | RB0 to RB3                                             |

| PSW     | Input/output instruction trapping flag | No       | IBRK                                                   | IBRK                                                   |

|         | User flag                              | No       | F0, F1                                                 | No                                                     |

| Specia  | I function register area               | No       | 240 bytes<br>(memory mapping onto<br>FFF00H to FFFEFH) | 496 bytes<br>(memory mapping onto<br>FFE00H to FFFEFH) |

- Internal 16-bit architecture, 16/8-bit selectable external data bus width

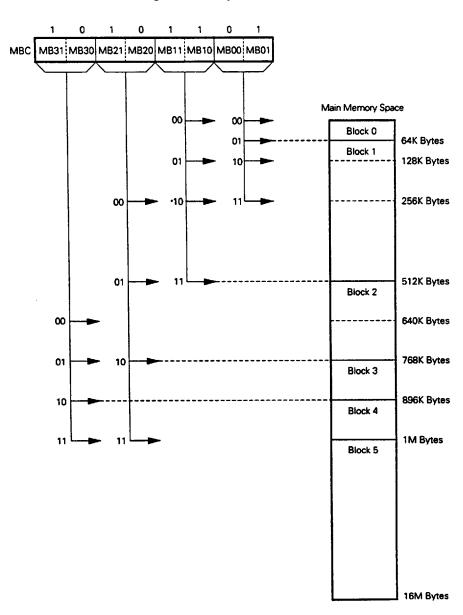

- Main memory is partitioned in variable sizes (maximum of 6 blocks) and automatic wait control

- Programmable wait function

- Ready pin wait function

- RAS pin function

RAS, LRAS pins

→RAS timing of the DRAM

RD, WRH, WRL, LRD, LWRL, LWRH pins →CAS timing of the DRAM

ASTB, LASTB pins

→Row/column address switch timing of the DRAM

- Refresh function

- Automatic generation of refresh cycle (RAS only)

#### 3.2 REGISTERS

The CPU of the V55SC has a general register set that is compatible with V20 and V30 (native mode) and with V25 and V35. Also, it has various special function registers for controlling the on-chip peripheral hardware. The general register set is mapped in the register file space. This general register set has dual-function as built-in RAM, and besides built-in RAM can have bank format using up to a maximum of 16 register sets. On the other hand, the special function registers are mapped in the main memory space 0FFE00H to 0FFFEFH.

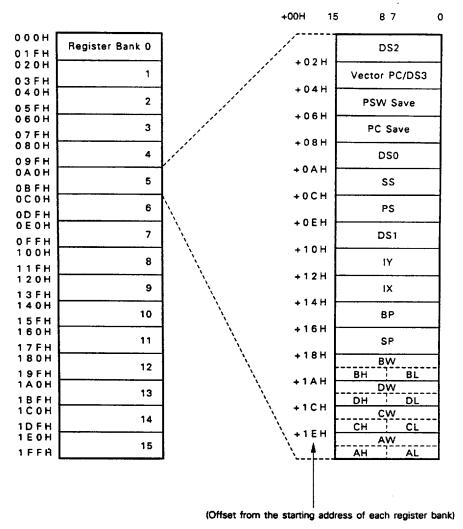

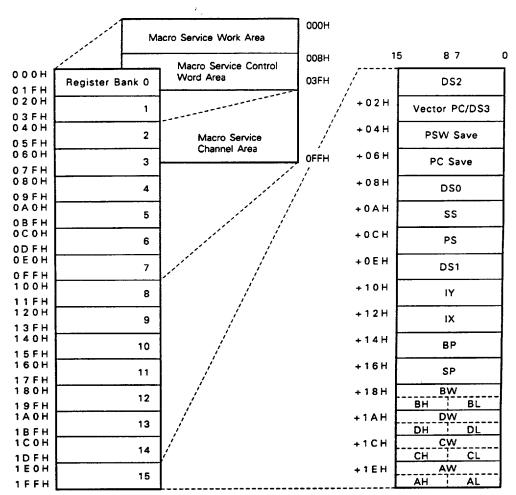

## 3.2.1 Register Banks

The general register set is mapped in the register file space (in the built-in RAM). The general register set take bank format and 1 bank uses 32 bytes and it is possible to set up to 16 banks. Of these 16 banks, bank 0 to bank 7 can also be used for macro service. Also, by attaching an exclusive prefix (IRAM:) to the memory transfer instruction, they can be used for accessing the data memory.

During program execution, it is possible to automatically switch to another register bank using maskable hardware interrupts or software interrupts (BRKCS instruction). To return to the original register bank from the register bank switched to using the interrupt, the instruction to return from an interrupt (RETRBI) is used.

The register bank configuration is as shown in Figure 3-1. The general register set is mapped in the area (+0.8H) to (+1FH) of the offset from the start address of each register bank. The word area from the start of a register bank becomes the expansion segment register (DS2) area. The vector PC/DS3 area is the value loaded into the PC when the register bank is switched, or in other words, it is the area for setting the offset value of the starting address of the interrupt process routine. This area can also be used as an expansion segment register (DS3) area. The PSW save area is an area used for saving the PSW when the register bank is switched. The PC save area is an area for saving the PC when the register bank is switched.

After reset, register bank 15 is selected automatically. Also, initialization of the segment register after reset is performed only for register bank 15.

In addition, the macro channels (parameter and work areas for macro service) are assigned in duplication to bank 0 and bank 1 of the 16 sets of register bank.

Fig. 3-1 Register bank Configuration

Register File Space (512 bytes)

# 3.2.2 General Registers (AW, BW, CW, DW)

The general registers are made up of four 16-bit registers. These registers can of course access as 16-bit registers, and can also access as 8-bit registers (AH, AL, BH, BL, CH, CL, DH, DL) by dividing the upper and lower 8 bits of each registers.

These registers can be used as 8-bit registers or 16-bit registers for a wide range of instructions such as transfer instructions, calculation instructions, and logical operation instructions.

Also, each register can be used as a default registers for processing the following specific instructions.

AW: Word multiplication/division, word input/output, data exchange

AL: Byte multiplication/division, byte input/output, BCD rotation, data exchange

AH: Byte multiplication/division BW: Translation

BW: Data conversion

CW: Loop control routine, repeat prefix

CL: Shift instruction, rotate instruction, BCD operation

DW: Word multiplication/division, indirect addressing input/output

These registers are mapped in the register file space (in the built-in RAM). The address is the value of the register bank number x 32 with the offset for each register added.

**Table 3-1 General-Purpose Register Offset**

| Register | Offset | Register | Offset |

|----------|--------|----------|--------|

|          |        | AL       | 1EH    |

| AW       | 1EH    | АН       | 1FH    |

|          |        | BL       | 18H    |

| 8W       | 18H    | ВН       | 19H    |

|          |        | CL       | 1CH    |

| cw       | 1CH    | СН       | 1DH    |

|          | 4.411  | DL       | 1AH    |

| DW       | 1AH    | DH       | 1BH    |

# 3.2.3 Pointers (SP, BP) and Index Registers (IX, IY)

These are 16-bit registers used as base pointers or index registers when the memory is accessed by based addressing (BP), indexed addressing (IX, IY), or based indexed addressing (BP, IX, IY). Also, SP can be used as a pointer during stack manipulation. They can also be used in the same way as the general registers for instructions such as transfer instructions or arithmetic operation instructions, however, in that case, they cannot be used as 8-bit registers. Also, each register is used as a fixed address pointer in the following specific processes.

SP: Stack manipulation

IX: Block transfer, address specification of BCD operation source

IY: Block transfer, address specification of BCD operation destination

These registers are mapped in the register file space (on the built-in RAM) and their address are the value of the register bank number x 32 with the offset for each register added.

**Table 3-2 Pointer and Index Register Offsets**

| Register | Offset |

|----------|--------|

| SP       | 16H    |

| ВР       | 14H    |

| IX       | 12H    |

| ΙΥ       | 10H    |

## 3.2.4 Segment Registers (PS, SS, DS0, DS1)

The CPU divides and controls the 1M byte basic memory space into logical segments of 64K bytes. The CPU indicates the start address of each segment using a segment register, and indicates the relative address from the start address as the offset using a different register or the effective address.

The physical address is comprised as follows.

|   |    | Se | gmer | it Reg | ister         | 4-b |   |     |                       |

|---|----|----|------|--------|---------------|-----|---|-----|-----------------------|

|   |    | ×  | ×    | ×      | $\overline{}$ | Ô   | H | ••• | Segment Start Address |

|   | +) | 0  | ×    | ×      | ×             |     |   |     | Offset Value          |

| - |    | ×  | ×    | ×      | ×             | ×   | Н | -   | Physical Address      |

The segment registers are comprised of a PS (program segment), SS (stack segment), DS0 (data segment 0), and DS1 (data segment 1).

PS: Program fetch

SS: Stack manipulation instruction, addressing with BP as the base register.

DS0: General variable access, access of source block data of the block transfer instruction.

DS1: Access of destination block data of the block transfer instruction.

By using the segment override prefix instruction, it is possible for general variable access to change from DS0 to another register. Also, for addressing using BP as the base register, another segment register can be used in the same way as the SS register.

Example MOV AW, 1000H

MOV DS1, AW

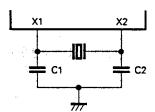

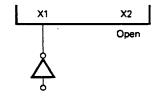

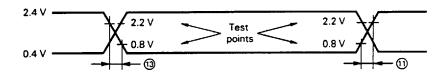

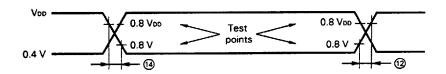

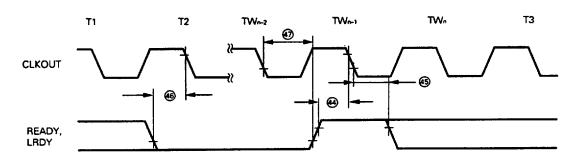

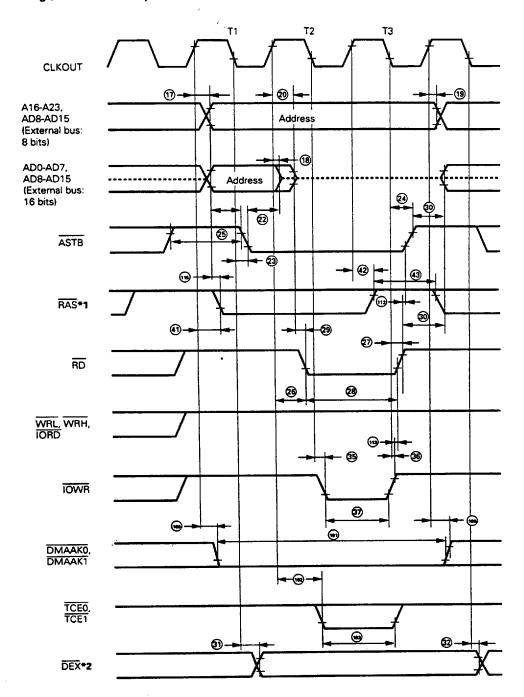

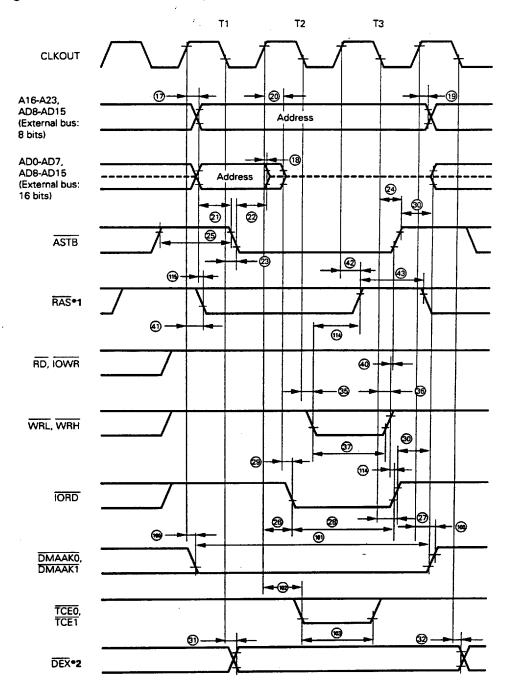

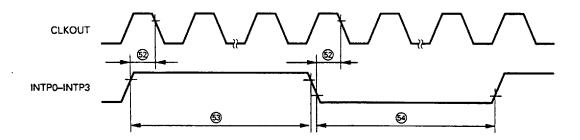

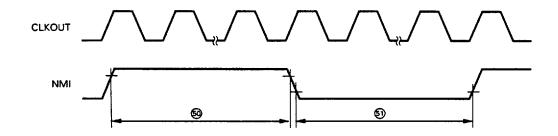

MOV BL, DS1, BYTE PTR [IX]; Byte data read from DS1:IX