TEL-98-A002

April 1998

# APPLICATION INFORMATION for KA8515

Provided by : Sung Bum Cho

MEDIA APPLICATION Eng. LSI DIVISION San #24 Nongseo-Ri, Kiheung-Eup Yongin-City, Kyungki-Do KOREA

Tel: 82-331-209-2879 Fax: 82-331-209-2899

E-mail: sungbum@samsung.co.kr

APPLICATION Eng.

MEDIA Team LSI Division

# I.General Description

The previously used POCSAG (Post-Office Code Standardization Advisory Group) protocol showed many problems in areas such as Data Transmission, User Capacity per channel, and Battery Consumption.

The newly selected FLEX protocol uses the synchronous method instead of the previous asynchronous method. This improves Battery efficiency and increases a variates the relatively slow transmission speed from 1200 bps (2 Level) to 1600 (2 Level)/ 3200 (2 or 4 Level)/ 6400 (4 Level) bps, setting a new standard in the Wireless transmission of Data / Information.

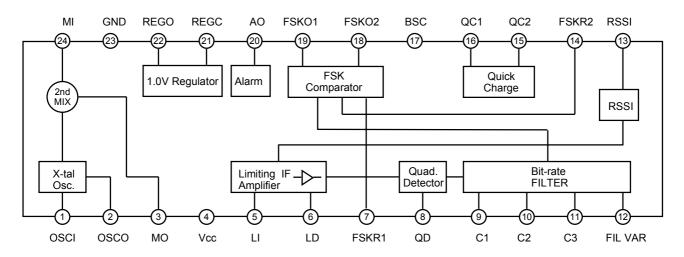

KA8515 is linear IC designed for a FLEX Pager, that provides the various functions of a 2nd Mixer, Limiting IF Amp, Quadrature Detector, Bit-Rate Filter, Data Shaping, Quick Charge, Battery Saving, Low Battery Detector, Voltage Regulator and the RSSI function that is useful for Wide Area Pagers.

Specially, it includes 4-level FSK comparator which converts 4-level analog signal to 2-bit Digital outputs .

## || .Principle of the IF Detector

The high Frequency signal (21.4 MHz) input into the 2nd Mixer (Double Balanced Multiplier) is converted to 455kHz, and is input into the Ceramic Filter, 7th order IF Amp, Limiting IF Amp, and the Quadrature detection. The Limiting Amp is used for removing AM components due to the Fading effect by obstacles or changes in amplitude caused by the noise effect.

The Quadrature Detector detects audio signal by using the voltage variation due to phase difference between the signal output by the Ceramic Resonator or Quadrature Coil, and the signal output by the Limiting IF Amp. The audio signal passed through the Bit rate Filter is converted to 2-bit Digital outputs by the 4-level FSK comparator.

At this time, if there is no Quick charge circuit, some data will be lost due to the capacitor charge time ( $\tau = RC$ : Time Constant)

Fig 1. Block Diagram of IF Detector

# III.Application Information

### 1) Current Consumption

```

KA8515 needs only 1 power source; Vcc

```

ex 1) When you are using an Alkaline Battery (AAA:1.5 V), what is the Total Power Consumption?

Power Consumption per day = (Active Power) + (Standby Power) + (Alert Power)

(1) (2) (3)

- 1 Active Power

- = (Active Current x Optimum Active Time per Day ) ; Collapse Value = 4

- = (5.0 mA) x {[(1 Day / Time for 128 Frame) x Time for 1 Frame] x Efficiency }

- = (5.0 mA) x {[(1440 min./4 min.) x 30 sec.] x 30 % }

- = 5.0 mA x 3240 sec. = 16200 mAsec. = 4.5mAh

- 2 Standby Power

- = (Standby Current x Standby Time per Day )

- = (0.5 mA) x (1 Day Optimum Active Time)

- $= (5.0 \text{ mA}) \times (86400 \text{ sec.} 3240 \text{ sec.})$

- = 0.5 mA x 83160 sec. = 41580 mAsec. = 11.55 mAh

- 3 Alert Power

- = (Alert Current x Alert Time per Day ) ; 3 Calls per Day

- = (110 mA) x (10 sec. x 3 Times) = 3300 mAsec. = 0.9166 mAh

- ∴ Power Consumption per Day = 4.5 mAh + 11.55 mAh + 0.9166 mAh = 16.9667 mA

- ⇒ Total Battery life = (1800 mAh / 16.9667 mAh) = 106.09 days

- Total Power of Alkaline battery (AAA:1.5V) is 1800 mAh (Normally).

ex2) When the current consumption of IF-IC is Increased to 100 μA, what is the Power Consumption?

```

(5.1 \text{ mA} \times 3240 \text{ sec.}) + (0.5 \text{ mA} \times 83160 \text{ sec.}) + (110 \text{ mA} \times 30 \text{ sec.})

```

- = 61404 mAsec. = 17.0567 mAh

- ∴ Battery Life = (1800 mAh / 17.0567 mAh) = 105.53 days (A Decrease around 0.56 days)

- Finally, if the Current Consumption of IF IC is increased by 100 uA, Battery Life is decreased by 0.56 days.

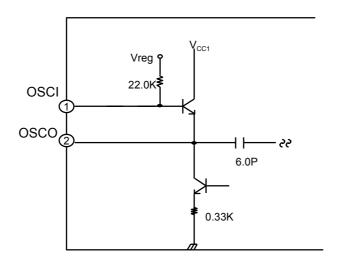

#### 2) Local Oscillator

The COLPITTS TYPE Local oscillator which generates 20.945 MHz Local Frequency generally uses the crystal oscillator, and if you need to control the amplitude or the frequency of that oscillator,

you can do so by the changing the value of load capacitor connected to the OSCI/OSCO (pin1, pin2).

There is no need to use an external Bias Resistor because the KA8515 already has an internal resistor (22  $\mbox{k}\Omega$ ) between the internal VREG block and the Colpitts Oscillator block.

Fig 2. Crystal Oscillator block

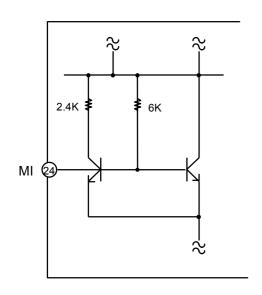

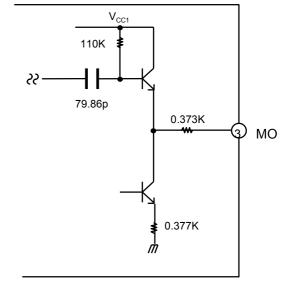

### 3) Mixer

Normally, the 2nd intermediate frequency (455 KHz) is input into the Limiting amp and the Quadrature detection circuit passing through the 2nd mixer(Double Balanced Multiplier) which has a 10 ~ 50 MHz input frequency band and 13 dB Mixer Conversion Gain, and the Ceramic filter.

The 2nd Mixer has a 5.0  $k\Omega$  input impedance and a 1.2  $k\Omega$  output impedance. (The output impedance has been lowered to 1.2  $k\Omega$ , taking into consideration the recent tendency for the Ceramic filter towards changing from the bulky through hole type to the smaller SMD type )

For input impedance matching, it is advantageous to use the LC matching to decrease the loss of input signals, rather than using Lossy matching by the resistor.

(When Impedance Mismatching occurs, the input sensitivity will be decrease by the reflection)

Fig 3. Mixer Input

Fig 4. Mixer Output

\* The output impedance of Mixer output block

The mixer output impedance is designed to have 1.5  $\mbox{k}\Omega$  impedance at the frequency of 455 kHz

### 4) Limiting IF Amplifier

The signal that passed through the 455 kHz Ceramic Filter and the Limiting Amp(pin5) which has a 7th order IF Amp and Limiter Amp, is input into the Quadrature Detection circuit.

After passing through the IF Amp, the signal will be amplified and limited by the Limiter Amp; the Voltage Gain is 76.48 dB.

Until the transmit signal is input into the antenna block of the pager set from the Base Station, the Limiting IF Amplifier unifies the changed FM signal caused by Fading, Static, or the adding unwanted AM components.

The Receiver which uses the limiter circuit and makes possible a maximum of 0.12 V voltage swing, is particulary strong against static.

The Limiting IF circuit has the input sensitivity of 6 uVrms (12 dB SINAD)

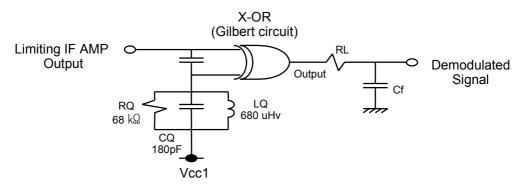

#### 5) Quadrature Detector & Audio Amplifier

The signal input into the Quadrature Detector Block is output from either the Ceramic Resonator or the Quadrature Coil, and has passed through the Limiting IF Amplifier.

The Quadrature Detector compares the input signal [455 kHz + fdev(1.6 kHz or 4.8 kHz)], to the 455 kHz reference signal made in the Ceramic Resonator or Quad. Coil to output the respective voltage level (Audio type) according to each frequency difference.

Since varying the value of the damping resistor connected to the Ceramic Resonator results in a change in sensitivity or AF LEVEL. Hence, it is necessary that the resistor value is suitably adjusted to get the AF level wanted and the optimum sensitivity by tuning the set.

Fig 5. Quadrature Detector block

Fig 6. Output Signal of Quad. Det. & Audio Amp.

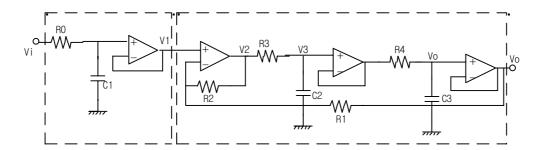

#### 6) Bit-Rate Filter

Unlike the previous POCSAG Protocol which was limited to one Transmission speed (1200 bps), the FLEX Protocol is designed to change from 1600/3200/6400 bps by program control.

(Consequently, in order to effectively transmit the respective signals, filtering for each Bit Rate is necessary). Although there are 3 kinds of transmit speeds, the frequency band is 800Hz(1600 or 3200 bps / 4 Level) and 1600Hz(3200 bps/2 Level or 6400 bps/4 Level), and each needs a different filter.

In the case of KA8515, the cut-off frequency of KA8515 is designed for 1.4 kHz, and you should decide on the value of the external capacitor connected to pin9/10/11 for optimum sensitivity.

If you set to Higher level to the FIL\_VAR pin, the cut-off frequency of the internal LPF is 800 Hz.In opposition, set to Low level, the cut-off frequency of the internal LPF is 1600 Hz.

Also, the FIL\_VAR which is connected to the NPN TR using the internal resistor(300  $\mbox{k}\Omega$ ), has High input Impedance and low driving power, so it is used to CMOS output same as MICOM.

Fig 7. The Architecture of the Bit Rate Filter

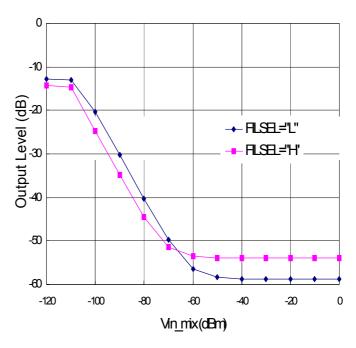

The Bit-rate Filter is a 3rd order Bessel Filter, composed of 1st and 2nd LPFs.

When you lower the Cut-off frequency, it improves S/N ratio, but it may be harmful to the FSK OUT2 duty of the entire system connected to the external A/D Converter.

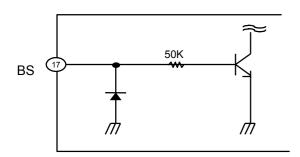

#### 7) Battery Saving

Battery Saving means the cut-off battery power during unnecessary times to the powerconsumption.

The Battery Saving Block(pin17) connected to the NPN TR using the internal resistor(50  $k\Omega$ ), has High input impedance and low driving power, so it is used to CMOS output same as MICOM.

| Status | BS Function           | IF-IC   | Current Consumption |  |

|--------|-----------------------|---------|---------------------|--|

| HIGH   | Battery Saving<br>ON  | Disable | 0 uA (Typ.)         |  |

| LOW    | Battery Saving<br>OFF | Enable  | 1.5 mA (Typ.)       |  |

Fig 8. Battery Saving Block

Table 1. Status of Battery Saving

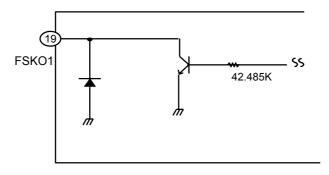

## 8) 4-LEVEL FSK(Frequency Shift Keying) Comparator

Since the audio signal is consists of 4-level, the 4level FSK comparator needs 3 references(upper, center,lower) to produce 2-bit Digital outputs.

Therefore the 4-FSK comparator has 2 comparators in its internal circuit.

One is comparation block between audio signal and its center reference, and the other is comparator between audio signal and its upper and lower references.

The comparation methodology is like this; the 1st bit of the Digital output is produced by the center comparator block(Zero cossing detection), and the 2nd bit of the Digital output is produced by the upper and lower comparator block.

Fig 9. FSK Output

#### 9) Quick Charge

When the Mode is changed from Battery Saving mode to Normal mode, and the input signal is impressed on the FSK comparator, some error data can be output because the reference voltage level of FSK comparator is unstable due to the time delay produced by the external capacitor and internal resistor value. In other words, some error data will be send to the Decoder because of the changes in the duty cycle of FSK data.

The voltage of FSK reference input terminal (pin 7 & pin14) can be stabilized after a period of time, even without the Quick charge circuit, but the Quick charge circuit reduces that period by increasing the input signal to quickly charge the capacitor of the FSK reference input terminal. When the value of the capacitors connected to Pin7 & Pin14 are small, it is better to shorten the charge time, but the discharge time is too short and the reference level is unstable during the Battery saving OFF, so you must consider the appropriate charge / discharge time for characteristics of entire system ( When you are using a  $10\,\mu$ F external capacitor, the RC timeconstant is 3.9 mS because the internal resistance of the signal route is 3900hm )

The Quick Charge block connected to the NPN Transistor using the internal resistor(370  $k\Omega$ ), has High input impedance and low driving power, so it is used to CMOS output same as MICOM.

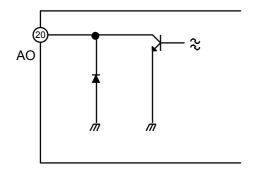

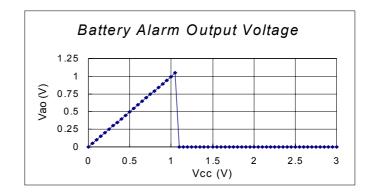

#### 10) Alarm Sense

When the power level of battery goes below 1.05 V, the Alarm sense output terminal (pin20) is set to High, letting you know the battery status.

This circuit always needs an external pull-up resistor (100  $k\Omega$ ) because it is designed to Open Collector architecture.

Fig 10. Alarm Sense

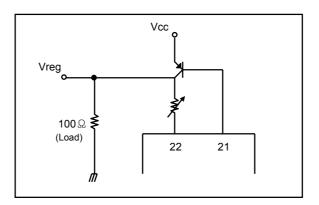

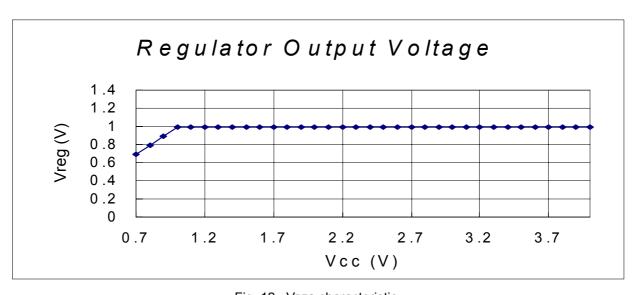

## 11) 1V Regulator

This circuit is mainly for stablizing the power source.

Some products of other companies require an external TR for the normal function of the regulator block, but the KA8515 already has a built-in Driving TR, so there is no need of another external TR for the regulating function.

The constant voltage output level by the Regulator Ouput terminal (PIN22) is 1.0V(@ 5mA), but if there is not enough driving current, you can also use an external PNP TR.

In this case, you can adjust the output voltage around 0.15 V, but you must consider Oscillation as well.

Fig 11. VREG Level Control

Fig 12. VREG characteristic

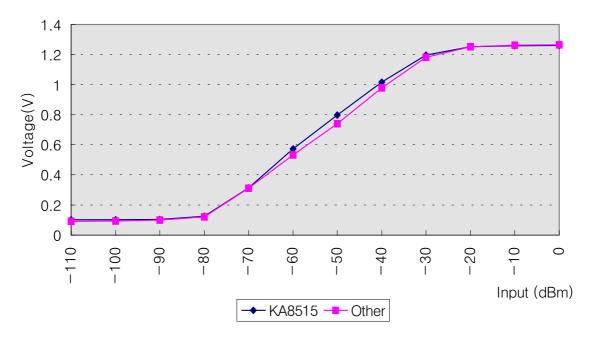

## 12) RSSI( Received signal strength indicator )

The DC voltage level of the RSSI(Received signal strength indicator) changes according to the RF input power. Therefore, the RSSI output terminal outputs a current following the amplitude of the received signal for the Pager set.

The RSSI output current is induced by adding the currents of the Limiting IF Amplifier.

If you use RSSI function, it is possible to perform an Automatic Gain Control(AGC) which controls the RF amp gain of the Pager Set, Input Level Meter and Call Triggering function at border-line areas.

The output level of the RSSI block(pin13) according to the input signal level is shown below.

| Input<br>(dBm) | -110   | -100   | -90    | -80    | -70    | -60    | -47    | -40    | -30    | -20    |

|----------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| KA8515         | 0.102V | 0.103V | 0.104V | 0.124V | 0.315V | 0.573V | 0.864V | 1.016V | 1.196V | 1.250V |

| Others         | 0.092V | 0.093V | 0.099V | 0.121V | 0.311V | 0.533V | 0.814V | 0.978V | 1.182V | 1.252V |

Table 2. Input Level vs. RSSI Output Level

Fig 13. RSSI Curve

# **IV.Test Performance**

25 2 Icc (mA) 1 - FLSEL="L" ⊢FLSEL≓'H' 0.5 0 0.8 1.2 2 24 28 1.6 3.2 36 4 Vcc(V)

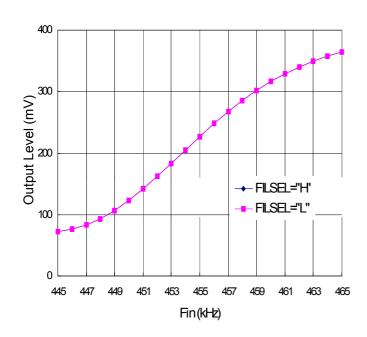

Fig 14. Discriminator Characteristic

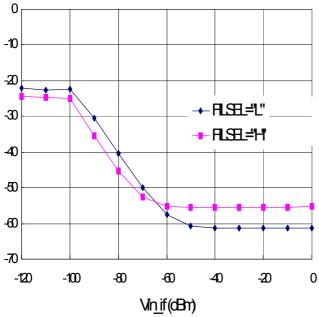

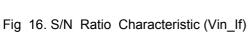

Fig 17. S/N Ratio Characteristic (Vin\_Mixer)

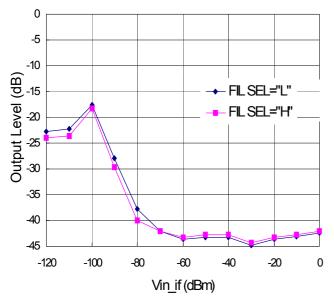

Fig 18. AMRR Characteristic (Vin\_If)

Fig 19. AMRR Characteristic (Vin\_Mixer)

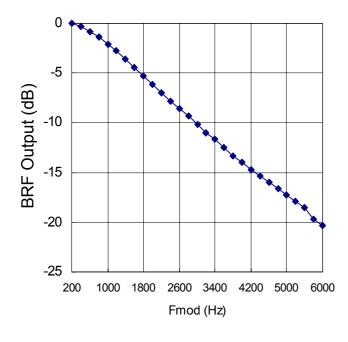

Fig 20. Bit rate filter Characteristic 1

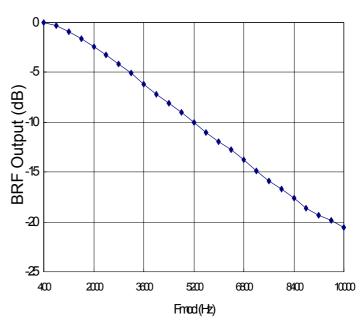

Fig 21. Bit rate filter Characteristic 2

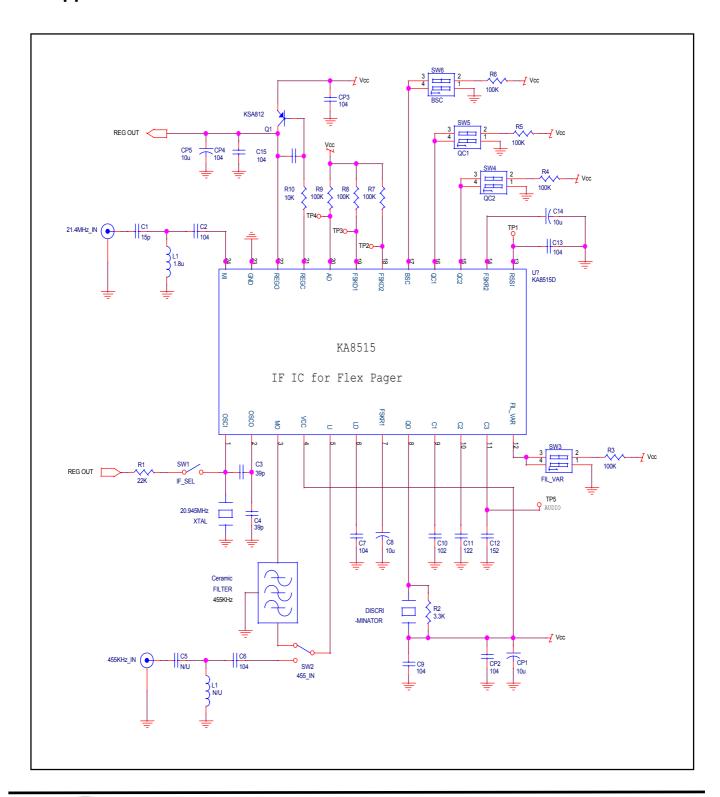

# **V.Application Circuit**

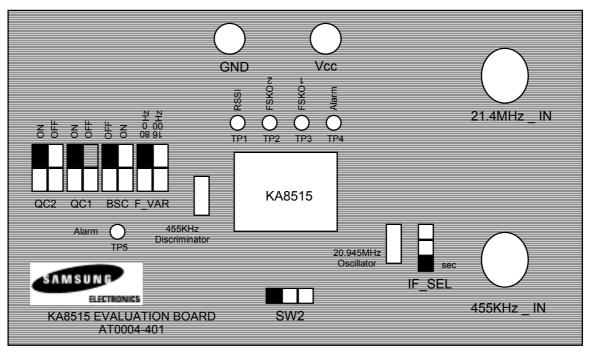

# VI. Operating Manual for KA8515 Evaluation Board

The KA8515 Evaluation Board has been designed with your convenience in mind so that you can easily test the electric characteristics of the SAMSUNG IF Detector IC.

1) Needs only 1 power supply for the normal function of Evaluation Board.

Vcc - 1.1 ~ 4.0V; Battery Input

2) Use 5 Test point to monitor the normal function of IF Detector IC.

Test Point1 - RSSI Level output

Test Point2 - FSK1 Signal output

Test Point3 - FSK2 Signal output

Test Point4 - Alarm Signal output

Test Point5 - Recovered Audio Signal output

3) It is possible to test in various environments.

| Switch   | Function        | SW Status | Meaning               |

|----------|-----------------|-----------|-----------------------|

| Switch 1 | IF IC Selection | Up        | KA8515                |

|          |                 | Down      | Other                 |

| Switch 2 | 455 kt Source   | Left      | Using 2'nd Mixer Out  |

|          |                 | Right     | Using External Source |

4) It is possible to test in different modes

| Switch  | Function     | Switch Status | Meaning                                        |

|---------|--------------|---------------|------------------------------------------------|

| FIL_VAR | Fiter Select | High          | Internal cut-off frequency will be set to Low  |

|         |              | Low           | Internal cut-off frequency will be set to High |

| BSC     | Battery Save | High          | Battery Saving function - OFF                  |

|         | Control      | Low           | Battery Saving function - ON                   |

| QC1/    | Quick Charge | High          | Quick Charge 1 / 2 - ON                        |

| QC2     | Control      | Low           | Quick Charge 1 / 2 - OFF                       |

Fig 22. KA8515 Evaluation Board

Fig 23. PCB Layout for KA8515 Evaluation Board