## AHA5140 QIC® Tape Data Format Controller Advanced Change Notice

**Advanced Hardware Architectures**

This document represents advanced changes to the AHA5140 QIC Tape Data Format Controller (PS5140-0496) Product Specification.

- 1) Section 11.1 Register Summary on Page 22 and Section 11.2.2 Read Channel Control on Page 23 -Changed the register address of Read Channel Control from 0x6F to 0x53.

- 2) Table in Section 11.1 Register Summary on Page 22 and Section 11.8.9 ECC Format on Page 46 Changed the register address of ECC Format from 0x79 to 0x4D.

- 3) Section 11.2.3 Tape Format on Page 24 Clarification to bits PAL[1:0]. These bits are only operative when writing to tape.

- 4) Section 11.2.4 Tape Control on Page 24 Fixed typographical error in the text for the register. It incorrectly implies that there are only two MODE bits.

- 5) Section 11.4.4 GIO Control on Page 34 Clarification to the GEL74 and GEL30 bit descriptions is "... are edge-sensitive interrupts..."; was "...are edge level interrupts..."

- 6) Section 11.5.2 Counter Config on Page 35 Clarification to the table for the CNTS[1:0] bits programming "01" is "Amble Found Events. Increments every time an Amble Found Interrupt is posted regardless of whether that interrupt is masked or already set"; was "Amble Found Interrupt. Increments every time an Amble Found interrupt is posted."

- 7) Section 11.8.1 ECC DMA Address on Page 42 Fixed typographical error in description of EDA[21:0] bits is "...the offset between consecutive bytes in the code word is 1040 (8 control bytes + 512 data bytes times 2 interleaves)."; was "...the offset between consecutive bytes in the code word is 520 (8 control bytes and 512 data bytes)."

- 8) Section 11.8.9 ECC Format on Page 46 Fixed typographical error in the table for the programming of the ECC\_FRMT[1:0]. Incorrectly lists the redundancy at 8, 9 and 10. Corrected table is:

| ECC_FRMT[1:0] | REDUNDANCY |

|---------------|------------|

| 00            | 6          |

| 01            | 8          |

| 10            | 10         |

| 11            | reserved   |

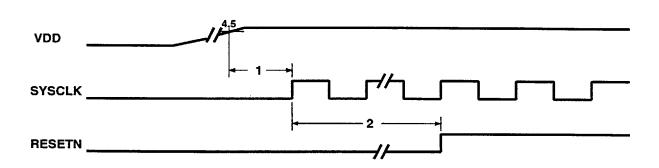

9) Section 12.1 System Signals on Page 47 - Additional functionality to aid drive reset. Added output pin **RESETO** and description as follows:

| SIGNAL | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                     |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETO | 0    | Active low when <b>RESETN</b> is active or when <b>S_ENABLE</b> bit is changed by the microprocessor. This signal should be used as the power-on-reset for any device using <b>SYSCLK</b> for a clock. The reason for this is that <b>SYSCLK</b> may glitch anytime <b>S_ENABLE</b> is changed. |

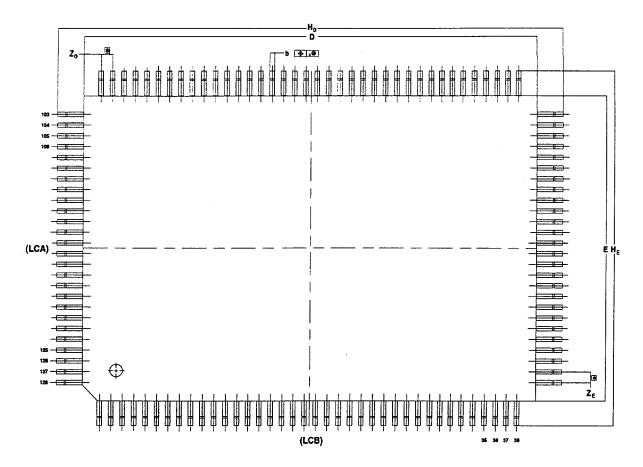

Section 13.0 Pinout on Page 50 - RESETO replaces pin TESTO in pin list. Changed pinout as follows: Removed TEST0 pin 63. RESETO now pin 54. Renumbered pins 54 through 62 to pins 55 through 63.

- 10) Section 11.7.3 Clock Configuration on Page 42 Additional functionality to aid drive reset. Added the following to description of S\_ENABLE bit: "When S\_ENABLE is changed by the microprocessor, a 15 clock cycle low pulse is generated on the RESETO pin. The clock used for this is the output of the system crystal oscillator, **SREF** (see Figure 2 on Page 4).".

- 11) Section 13.0 Pinout on Page 50 The pin names for TAPE TEST0 and TAPE TEST1 have been shortened to TAPE[0:1].

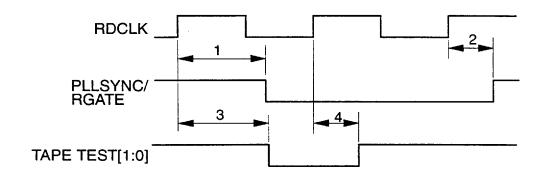

advchang.066 Page 1 of 5 June 27, 1996 12) Section 11.0 Registers on Page 21 – New register added to control the output on the **TAPE[1:0**] pins, Section 11.2.16 Tape Test Configuration as follows:

Read/Write

Reset Value (hex)=00

|      | bit7     | bit6     | bit5 | bit4     | bit3 | bit2 | bit1     | bit0 |

|------|----------|----------|------|----------|------|------|----------|------|

| 0x4C | reserved | reserved |      | TT1[2:0] |      |      | TT0[2:0] |      |

| TTx[2:0] | DESCRIPTION                                                         |

|----------|---------------------------------------------------------------------|

|          | BLKSTN - Active Low block start. Indicates the detection of         |

| 000      | the block marker by the read channel. Driven from rising edge       |

|          | of RDCLK. Active for one RDCLK period                               |

|          | CRCBN - Active Low CRC Bad. Indicates a block with a                |

| 001      | invalid CRC was read from tape. Driven from rising edge of          |

|          | RDCLK. Active for one RDCLK period                                  |

|          | CRCGN - Active Low CRC Good. Indicates a block with a               |

| 010      | valid CRC was read from tape. Driven from rising edge of            |

|          | RDCLK. Active for one RDCLK period                                  |

|          | MERRN - Active Low modulation error. Indicates a                    |

| 011      | modulation error occurred during a read from tape. Pulses for       |

| 011      | each decode error. Driven from rising edge of <b>RDCLK</b> . Active |

|          | for one RDCLK period                                                |

| 100      | Reserved                                                            |

| 101      | Reserved                                                            |

| 110      | Reserved                                                            |

| 111      | Reserved                                                            |

- TT1[2:0] Selects the source for the TAPE[1] output signal. The source is determined according to the above table.

- TT0[2:0] Selects the source for the TAPE[0] output signal. The source is determined according to the above table.

- 13) Section 15.3.3 Read Status Outputs on Page 55 TAPE TEST[1:0] signal has been shortened to TAPE[1:0].

- 14) Section 12.5 *DRAM Signals* on Page 49 Changed connection of **MDP** pin when parity is disabled. If DRAM Parity is not used, **MDP** must be unconnected.

- 15) Section 13.0 Pinout on Page 50 Reversed the ordering of pins WCI and WCIXT.

- 16) Section 13.0 *Pinout* on Page 50 Changed pins WRCLK, BITCLK, WRDATA, WGATEN, RGATE, PLLSYNC, RDATA and RDCLK to CMOS voltage levels from TTL levels. This matches the Philips read/write channel IC's requirements.

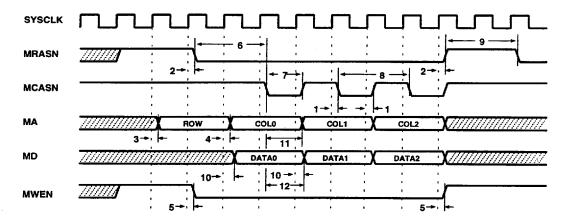

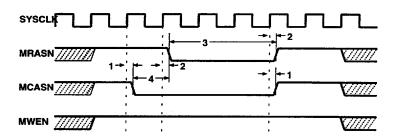

- 17) Section 11.1 Register Summary on Page 22 and new Section 11.3.6 DRAM Wait State on Page 33 Add new register DRAM Wait State, address 0x47.

Reset Value (hex)=00

|      | bit7     | bit6     | bit5  | bit4     | bit3     | bit2     | bit1     | bit0     |

|------|----------|----------|-------|----------|----------|----------|----------|----------|

| 0x47 | reserved | reserved | CASWS | reserved | reserved | reserved | reserved | reserved |

advchang.066

Page 2 of 5

June 27, 1996

■ 0255381 0001037 9TO ■

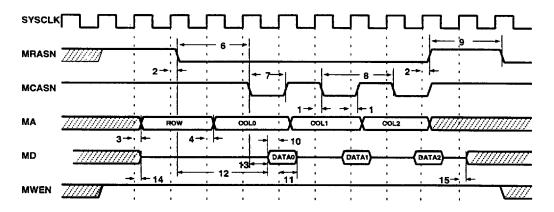

- CASWS Controls insertion of extra clock pulse in the MCASN low timing. This bit must be programmed high for support of 1Megabit DRAMs (1M x1 or 256K x 4).

- 18) New Section 11.3.6 DRAM Wait State on Page 33 Support for 1Mbit DRAMs (in 1M x 1 or 256K x 4 configurations) has been added with the addition of a DRAM wait state in the MCASN timing. The wait state is enabled by setting the CASWS bit in the DRAM Wait State register. When the DRAM wait state is active, the total available DRAM bandwidth is decreased. The available bandwidth by channel is as follows:

Tape Control - 1.0MB/s (12.0 Mb/s) Microprocessor Interface - 1.0 MB/s

Host Interface - 6.9 MB/s

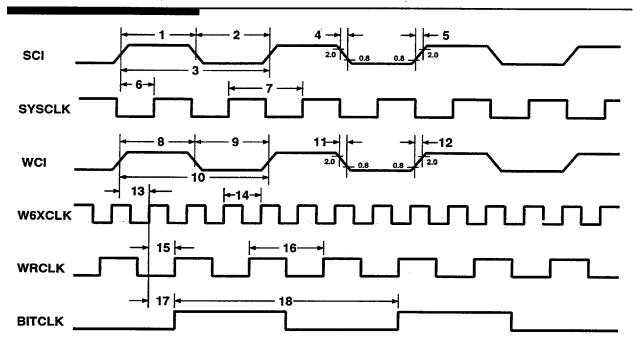

- 19) Specification for SCI, SCIXT, WCI and WCIXT:

- Connection to external crystal: Up to a 30MHz crystal can be connected between SCI and SCIXT or WCI and WCIXT with no external components.

- Connection to external clock source: Up to a 24MHz external clock source can be driven into

either SCI or WCI. These pins must be driven with CMOS voltage levels and SCIXT and/or

WCIXT pins must be unconnected.

- PLL de-coupling: The power supplies for the two PLLs must be de-coupled separately. Connect de-coupling capacitor between pins 75 and 78 and between pins 79 and 82.

- The input capacitance for SCI and WCI is 50pF each.

- Overall jitter on the internal PLLs is reduced if the mode that drives the tape PLL from the system PLL is not used.

The above parameter limits will be specified upon completion of device characterization.

- 20) Section 9.4.1 Frame Level Read-While-Write on Page 18 Clarification of timing on Max Rewrites interrupt: is "After the 15th rewrite fails..."; was "If 16 rewrites are attempted without success..."

- 21) Section 9.6.1 Frame Level Read on Page 20 Remove paragraph that states: "To improve response time in the normal case, a Frame 0(1) Done interrupt is also issued if all blocks in a frame are read with a good CRC." In this case, the Frame 0(1) Done interrupt is generated after reading 8 blocks into the next frame.

- 22) Section 9.6.2 Block Level Read on Page 21 Clarification with respect to the Frame 0(1) Done interrupt: For block-level reads, the Frame 0(1) Done interrupt is generated when the CRC is checked. The Frame 0(1) Done is not affected by the writing of the last byte to DRAM.

- 23) Section 11.2.8 Frame Control on Page 26 Clarification of bit FDIS: The tape MODE must be toggled to "off" after a frame disable command is received prior to the next frame 0(1) enable command. In addition, the URC bit must be cleared when writing the frame disable command.

- 24) Section 11.2.1 *Drive Format* on Page 23 Added bit to register; were bit 7 reserved and bit 6 **WNRZI**; are bit 7 and 6 **WNRZI**[1:0] as shown below.

Reset Value (hex)=XX

|      | bit7 | bit6   | bit5  | bit4     | bit3 | bit2 | bit1  | bit0 |

|------|------|--------|-------|----------|------|------|-------|------|

| 0x54 | WNRZ | I[1:0] | RNRZI | reserved |      | GAP  | [3:0] |      |

WNRZI[1:0] -Controls data format on WRDATA output pin according to the following table:

| WNRZI[1:0] | FORMAT                    |  |  |  |  |  |

|------------|---------------------------|--|--|--|--|--|

| 00         | Output is in pulse format |  |  |  |  |  |

| 01         | Output is in NRZI format  |  |  |  |  |  |

| 10         | Output is in raw format   |  |  |  |  |  |

| 11         | reserved                  |  |  |  |  |  |

advchang.066

Page 3 of 5

June 27, 1996

**=** 0255381 0001038 837 **=**

25) Section 11.3.3 DRAM Config on Page 32 – Added bits to register; were bit 6 DPSZ, bits 5-3 reserved; are bits 6 and 5 DPSZ[1:0], bit 4 DINIT and bit 3 DPO as shown below.

Reset Value (hex)=00

|      | bit7 | bit6 | bit5  | bit4  | bit3 | bit2 | bit1 | bit0  |

|------|------|------|-------|-------|------|------|------|-------|

| 0x49 | DPE  | DPSZ | [1:0] | DINIT | DPO  | DDBS | DWTE | DBUSY |

- **DPE** DRAM Parity Enable. When active, DRAM parity is checked (according to **DPO**). When inactive, the output enable for the **MDP** pin is always enabled. Parity is always generated but not checked.

- **DPSZ[1:0]** -DRAM Page Size. Selects the starting position in the 22-bit internal address for the DRAM row address. The address bits are numbered from 0 to 21 therefore if the row address starts at bit 9, the DRAM column has 9 bits (bits 0 to 8).

| DPSZ | ROW ADDRESS START POSITION |

|------|----------------------------|

| 00   | bit 9                      |

| 01   | bit 10                     |

| 10   | bit 11                     |

| 11   | reserved                   |

- DINIT Enable DRAM initialization sequence. When this is active, the interface to the external DRAM is reset thus preventing all DRAM activity. Many DRAMs require a period of inactivity after power on before normal operation can be performed. This bit should be active during the DRAM initializing sequence.

- **DPO** DRAM Parity odd. When active, odd parity is generated and checked (if **DPE** is active). When inactive even parity is enabled.

- 26) Section 11.6.7 Host Command on Page 38 Added reset bit to register; was bit 4 reserved; is bit 4 RST as shown below.

Reset Value (hex)=00

|      | bit7     | bit6     | bit5     | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|----------|----------|----------|------|------|------|------|------|

| 0x42 | reserved | reserved | reserved | RST  | HBE  | HBD  | HAE  | HAD  |

- RST Reset. Writing a '1' to this bit initiates a reset of the data path elements and state machines in the Host Interface. Writing a '0' has no effect.

- 27) Section 11.6.8 *Host Status* on Page 38 Removed **HNA** bit. The information it provided was redundant.

- 28) Section 11.6.9 Host Configuration 1 on Page 40 Added polarity control for the HRD pin. Bit 2 was reserved; is HRAL.

Reset Value (hex)=48

|      | bit7     | bit6 | bit5  | bit4 | bit3   | bit2 | bit1 | bit0 |

|------|----------|------|-------|------|--------|------|------|------|

| 0x40 | reserved | HAL  | [1:0] | HAH  | [[1:0] | HRAL | HPE  | HRD  |

advchang.066

Page 4 of 5

June 27, 1996

**■ 0255381 0001039 773** ■

## AHA5140 QIC® Tape Data Format Controller Advanced Change Notice

**Advanced Hardware Architectures**

- HRAL Host Read Active Low. When this bit is set the HRD signal is active low (i.e. low when reading from DRAM, high when writing to DRAM). When clear, the HRD is active high. Note that this signal does *not* affect the polarity of the HRD register bit.

- 29) Section 11.8.2 ECC Erasure Address on Page 43 ECC Interleave selection is now done with one bit. Bit 7 and 6 were INTR[1:0]; are bit 7 reserved and bit 6 INTR as shown below.

Reset Value (hex)=XX

|      | bit7     | bit6 | bit5 | bit4 | bit3  | bit2   | bit1 | bit0 |

|------|----------|------|------|------|-------|--------|------|------|

| 0x2A | reserved | INTR |      |      | EEA[2 | 21:16] |      |      |

**INTR** - ECC Interleave selection. Bit is high when processing the odd number blocks and low when processing the even blocks.

advchang.066

Page 5 of 5

June 27, 1996

**m** 0255381 0001040 495 **m**

**TARGET**

# **Product Specification**

AHA5140

© Tape Data Format Controller

Advanced Hardware Architectures, Inc. 2365 NE Hopkins Court Pullman, WA 99163-5601 509.334.1000 FAX 509.334.9000 e-mail: sales@aha.com http://www.aha.com

## **AHA CONFIDENTIAL**

This document represents a product in the first stages of a design cycle. The specification is an initial disclosure of design goals for the product.

PS5140-0496

**-** 0255381 0001041 321 **-**

A

# Table of Contents

| 1.0 | Intro                    | ale ca di a se |                                                             | 4  |  |  |  |  |  |  |

|-----|--------------------------|----------------|-------------------------------------------------------------|----|--|--|--|--|--|--|

| 1.0 |                          | Introduction   |                                                             |    |  |  |  |  |  |  |

|     | 1.2 Document Conventions |                |                                                             |    |  |  |  |  |  |  |

|     |                          |                |                                                             |    |  |  |  |  |  |  |

| 2.0 |                          |                | ssor Interface                                              |    |  |  |  |  |  |  |

|     |                          |                | er Reads and Writes                                         |    |  |  |  |  |  |  |

|     |                          |                | Emulation                                                   |    |  |  |  |  |  |  |

|     | 2.3                      |                | ing DRAM Buffer                                             |    |  |  |  |  |  |  |

|     |                          | 2.3.1          | DRAM Writes                                                 |    |  |  |  |  |  |  |

|     |                          | 2.3.2          | DRAM Read                                                   |    |  |  |  |  |  |  |

|     |                          | 2.3.3          | Data Byte Skipping                                          |    |  |  |  |  |  |  |

|     |                          | 2.3.4          | Bandwidth                                                   |    |  |  |  |  |  |  |

| 3.0 | Cloc                     | ks             |                                                             | 3  |  |  |  |  |  |  |

| 4.0 | Gene                     | eral I/O       | Port                                                        | 4  |  |  |  |  |  |  |

| 5.0 | Com                      | nter / Ti      | mer                                                         | 4  |  |  |  |  |  |  |

|     |                          |                |                                                             |    |  |  |  |  |  |  |

| 6.0 |                          |                | ger                                                         |    |  |  |  |  |  |  |

| 7.0 |                          |                |                                                             |    |  |  |  |  |  |  |

|     | 7.1                      |                | ata Manager                                                 |    |  |  |  |  |  |  |

|     |                          | 7.1.1          | Non-Blocked Transfers                                       |    |  |  |  |  |  |  |

|     |                          | 7.1.2          | Blocked Transfers                                           |    |  |  |  |  |  |  |

|     |                          |                | 7.1.2.1 Crossing Frame Boundaries                           |    |  |  |  |  |  |  |

|     |                          |                | 7.1.2.2 Transfer Does not Start at the Beginning of a Block |    |  |  |  |  |  |  |

|     |                          |                | 7.1.2.3 Logical Block is not Multiple of Physical Block     |    |  |  |  |  |  |  |

|     |                          | 7.1.3          | Memory-to-Memory Copy                                       |    |  |  |  |  |  |  |

|     |                          | 7.1.4          | Parity Errors                                               |    |  |  |  |  |  |  |

| 8.0 |                          |                |                                                             |    |  |  |  |  |  |  |

|     |                          |                | ound                                                        |    |  |  |  |  |  |  |

|     |                          |                | ncoding                                                     |    |  |  |  |  |  |  |

|     | 8.3                      | ECC D          | ecoding1                                                    | 0  |  |  |  |  |  |  |

| 9.0 | Tape                     | <b>9</b>       |                                                             | C  |  |  |  |  |  |  |

|     | 9. i                     | Tape C         | Overview                                                    | C  |  |  |  |  |  |  |

|     |                          | 9.1.1          | Tape Block Diagram1                                         | C  |  |  |  |  |  |  |

|     |                          | 9.1.2          | Tape Channel Modes                                          | 11 |  |  |  |  |  |  |

|     |                          | 9.1.3          | Data Transfers                                              | 11 |  |  |  |  |  |  |

|     |                          | 9.1.4          | Frame Format1                                               | 11 |  |  |  |  |  |  |

|     | 9.2                      | Physica        | al Formats                                                  | 11 |  |  |  |  |  |  |

|     |                          | 9.2.1          | RLL Support                                                 | 12 |  |  |  |  |  |  |

|     |                          |                | 9.2.1.1 Amble (RLL)                                         |    |  |  |  |  |  |  |

|     |                          |                | 9.2.1.2 Block Marker (RLL)                                  |    |  |  |  |  |  |  |

|     |                          |                | 9.2.1.3 Modulation Code (RLL)                               |    |  |  |  |  |  |  |

|     |                          |                | 9.2.1.4 Randomization (RLL)                                 |    |  |  |  |  |  |  |

|     |                          |                | 9.2.1.5 Control Bytes (RLL)                                 |    |  |  |  |  |  |  |

|     |                          |                | 9.2.1.6 Data Bytes (RLL)                                    |    |  |  |  |  |  |  |

|     |                          |                | 9.2.1.7 CRC (RLL)                                           |    |  |  |  |  |  |  |

|     |                          |                | 9.2.1.8 Output Format (RLL)                                 |    |  |  |  |  |  |  |

|     |                          |                | 9.2.1.9 Input Format (RLL)                                  |    |  |  |  |  |  |  |

|     |                          | 9.2.2          | MFM Support                                                 |    |  |  |  |  |  |  |

|     |                          |                | 9.2.2.1 Segment Header (MFM)                                |    |  |  |  |  |  |  |

|     |                          |                | 9.2.2.2 Track Sector ID (MFM)                               | 14 |  |  |  |  |  |  |

|     |                          |                |                                                             |    |  |  |  |  |  |  |

|     |                          |                |                                                             |    |  |  |  |  |  |  |

0255381 0001042 268 🖿

AHA CONFIDENTIAL

PS5140-0496

## The Data Coding Leader

| i    |      |         | AHA CONFIDENTIAL                    | PS5140-0496 |

|------|------|---------|-------------------------------------|-------------|

|      |      |         |                                     |             |

|      |      | 11.6.3  | Host DMA B Address                  | 36          |

|      |      |         | Host DMA A Counter                  |             |

| ,    |      |         | Host DMA A Address                  |             |

|      | 11 6 |         | Counter Config                      |             |

|      |      |         | Counter Timer                       |             |

|      | 11.5 |         | Registers                           |             |

|      |      |         | GIO Control                         |             |

|      |      |         | GIO Mask                            |             |

|      |      | 11.4.2  | GIO Interrupt                       |             |

|      |      | 11.4.1  | GIO Data                            |             |

|      | 11.4 |         | gisters                             |             |

|      |      |         | Version                             |             |

|      |      |         | System Config                       |             |

|      |      |         | DRAM Config                         |             |

|      |      |         | DRAM Data                           |             |

|      | 11.3 | •       | ocessor Interface Registers         |             |

|      | 11 0 |         | Tape Block Interrupt Mask           |             |

|      |      |         | Frame Interrupt Mask                |             |

|      |      |         | Tape Block Interrupts               |             |

|      |      |         | Tape Frame Interrupts               |             |

|      |      |         | P. Tape Current Memory Address      |             |

|      |      | 11.2.11 | Outgoing Block                      | 27          |

|      |      | 11.2.10 | Cast Incoming Block                 | 27          |

|      |      | 11.2.9  | Incoming Block                      | 26          |

|      |      |         | Frame Control                       |             |

|      |      |         | Frame 1 Pointer                     |             |

|      |      |         | Frame 0 Pointer                     |             |

|      |      |         | Tape Control  Expected Block        |             |

|      |      |         | Tape Control                        |             |

|      |      |         | Read Channel Control                |             |

|      |      |         | Drive Format                        |             |

|      | 11.2 |         | Registers                           |             |

|      |      |         | er Summary                          |             |

| 11.0 | _    |         |                                     |             |

|      |      |         | er                                  |             |

|      | _    | 9.6.2   | Block Level Read                    |             |

|      |      | 9.6.1   | Frame Level Read                    |             |

|      | 9.6  |         | - <u></u>                           |             |

|      |      |         | d                                   |             |

|      |      | 9.4.2   | Block Level Read-While-Write        | 19          |

|      |      | 9.4.1   | Frame Level Read-While-Write        | 18          |

|      | 9.4  | Read-l  | While-Write                         | 18          |

|      |      | 9.3.2   | Block Level Write                   |             |

|      | 0.0  | 9.3.1   | Frame Level Write                   |             |

|      | 9.3  | Write . | Thead Ghanner Data Necovery Control |             |

|      |      | 9.2.4   | Read Channel Data Recovery Control  |             |

|      |      | 9.2.3   | 9.2.2.5 CRC (MFM)                   |             |

|      |      |         | 9.2.2.4 Modulation Code (MFM)       |             |

|      |      |         | 9.2.2.3 Data Block (MFM)            |             |

|      |      |         | 0.0.0.0. Dete Die et. (AELA)        |             |

■ 0255381 0001043 1T4 ■

## Advanced Hardware Architectures. Inc.

|           | 11.6.4 Host DMA B Counter              |            |

|-----------|----------------------------------------|------------|

|           | 11.6.5 Host Interface Interrupts       |            |

|           | 11.6.6 Host Interrupts Mask            |            |

|           | 11.6.7 Host Command                    |            |

|           | 11.6.8 Host Status                     |            |

|           | 11.6.9 Host Configuration 1            |            |

|           | 11.6.10 Host Configuration 2           | 4U<br>41   |

| 11./      | Clock Configuration Registers          | 41<br>11   |

|           | 11.7.2 Tape PLL Control                | 71<br>⊿1   |

|           | 11.7.3 Clock Configuration             | 42         |

| 11.8      | B ECC Registers                        | 42         |

| 77.0      | 11.8.1 ECC DMA Address                 | 42         |

|           | 11.8.2 ECC Erasure Address             |            |

|           | 11.8.3 ECC Code Words                  |            |

|           | 11.8.4 ECC Configuration               |            |

|           | 11.8.5 ECC Command                     | 44         |

|           | 11.8.6 ECC Status                      |            |

|           | 11.8.7 ECC and Other Interrupts        | 45         |

|           | 11.8.8 ECC and Other Interrupts Mask   |            |

|           | 11.8.9 ECC FORMAT                      |            |

| 12.0 Sign | nal Descriptions and Specifications    | 47         |

| 12.       | 1 System Signals                       | 47         |

| 12.2      | 2 Microprocessor Signals               | 47         |

| 12.3      | 3 Host Signals                         | 48         |

| 12.4      | 4 Tape Signals                         | 48         |

|           | 5 DRAM Signals                         |            |

|           | 6 Other Signals                        |            |

|           | out                                    |            |

| 14.0 DC   | Electrical Characteristics             | . 51       |

| 15.0 AC   | Electrical Characteristics             | . 52       |

| 15.       | 1 Clock Timing                         | . 52       |

| 15.2      | 2 Reset Timing                         | . 53       |

| 15.3      | 3 Tape Timing                          | . 54       |

|           | 15.3.1 Write Data Output               | . 54       |

|           | 15.3.2 Read Clock and Data             |            |

|           | 15.3.3 Read Status Outputs             | . 55       |

| 15.       | 4 Microprocessor Timing                | . 56       |

|           | 15.4.1 Microprocessor Read Timing      | . 56       |

|           | 15.4.2 Microprocessor Write Timing     |            |

| 10        | 15.4.3 MIcroprocessor Interrupt Timing | . 5/<br>50 |

| 15.       | 5 Host Timing                          |            |

| 15        | 6 DRAM Timing                          |            |

| 13.       | 15.6.1 Dram Read                       | . 59       |

|           | 15.6.2 DRAM Write Timing               |            |

|           | 15.6.3 DRAM Refresh                    |            |

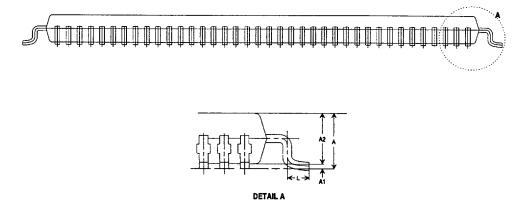

| 16 0 Pa   | ckaging                                |            |

|           | dering Information                     |            |

|           | · · · · · · · · · · · · · · · · · · ·  |            |

| 18.0 Re   | lated Technical Publications           | . 63       |

|           |                                        |            |

|           |                                        |            |

| PS5140-0  | 0496 AHA CONFIDENTIAL                  | iii        |

|           | ■ 0255381 0001044 030 ■                |            |

# Figures

| Figure 1:  | Block Diagram                            | .2  |

|------------|------------------------------------------|-----|

| Figure 2:  | AHA5140 Clock Generation Block Diagram   | . 4 |

| Figure 3:  | DMA Sub-System                           | . 5 |

| Figure 4:  | Memory Matrix for QIC-3095 Format        | .9  |

| Figure 5:  | Memory Matrix for QIC-95-73 Rev C Format | .9  |

| Figure 6:  | Tape Block Diagram                       | 11  |

| Figure 7:  | Read-While-Write Process Flow            | 11  |

| Figure 8:  | Tape Channel Output Data Waveforms       | 13  |

| Figure 9:  | Tape Channel Input Waveforms             | 14  |

| Figure 10: | Tape Channel Clocks                      | 16  |

|            | Read Channel Data Recovery Control       |     |

| Figure 12: | Tape Write Process                       | 17  |

| Figure 13: | Package Cross-Section Diagram            | 61  |

| Figure 14: | Package Diagram                          | 62  |

AHA CONFIDENTIAL

PS5140-0496

## 1.0 INTRODUCTION

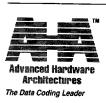

The AHA5140 is a single-chip Reed-Solomon error corrector, buffer manager and  $QIC_{\circledR}$  tape formatter.

The device provides a frame-level control interface to free the microprocessor for other tasks. Individual block-level transfers are handled in hardware. During read-while-write, block rewrites are automatically scheduled. During reads incoming blocks are automatically directed to the appropriate DRAM location. In addition to frame-level control, the microprocessor can still take direct control of transfers to handle unusual or proprietary operations.

Host data transfers are through DMA connection to an external controller. DMA rates support up to ATAPI PIO mode 3 (11.1 MB/s).

The tape formatter has read/write compatibility with QIC-3095 and read compatibility with QIC-80, QIC-3010 and QIC-3020. In addition, several features within the IC allow reading and writing of the proposed TR5 (QIC-95-75 rev C, QIC-95-91, QIC-93) format.

## 1.1 FEATURES

#### **HOST INTERFACE:**

- Support connection to external SCSI or ATAPI chips

- Host data rate of up to 11.1 MB/s while maintaining worst case microprocessor and tape data rates and DRAM refresh

- Pre-armable host DMA allows for multi-frame transfers

- Intelligent host DMA that optionally skips memory locations that are reserved for control bytes

#### TAPE CONTROL:

- Microprocessor has optional frame-level control of tape read and write operations

- Optional read-while-write support to fully meet QIC-3095 standard

- During unusual or proprietary operations, the microprocessor can take block-level control of all tape DMA operations

- During tape read, automatic re-mapping of outof-order blocks and recording of erasure (CRC vector) for incoming blocks

#### TAPE FORMATTING:

- Read of QIC-80, QIC-3010, QIC-3020, and QIC-3095 format standards

- · Write of QIC-3095 format standard

- Read and write support for proposed TR5 format (QIC-95-75 rev C, QIC-95-91, QIC-95-93)

- Output either NRZI or pulse data

- · Optional write equalization

- Connection to popular read/write channel ICs REED-SOLOMON ECC:

- Programmable redundancy of 6 to 10 to support QIC-3095 and proposed TR5 format (QIC-95-75 rev C)

- Interleave-level control of ECC encoding operation

- ECC decoding performed on basis of erasures detected by CRC

- ECC erasure information (CRC vector) automatically stored in DRAM for off-line decoding when necessary

#### MICROPROCESSOR INTERFACE:

- Direct connection to Intel 80188, 80186, 80196 microprocessors

- Microprocessor has low latency, high bandwidth PIO access to DRAM. DRAM access paced with READY signal or with polling loop

- Automatic increment DRAM address register provides easy access to a frames control bytes

- High speed block copy operation can be done when the host DMA is inactive

- SRAM Emulation mode eliminates the need for separate SRAM in the system

## DRÂM INTERFACE

- Support for 60ns 512KB, 1MB, 2MB and 4MB of DRAM with and CAS-before-RAS refresh

- EDO DRAMs are supported but not required **GENERAL**:

- General purpose, programmable counter/timer

- Programmable clock generation for system, tape write channel and data separator reference

- · All IC outputs tristated with pin assertion

- 8-bit General purpose I/O port with programmable direction and interrupt capability

- 5.0 volt power supply

## 1.2 DOCUMENT CONVENTIONS

The following typographic conventions were followed in the generation of this specification.

- SIGNALS OR PINS

- Register Names

- INDIVIDUAL REGISTER BITS

- Interrupts

- Commands

PS5140-0496 AHA CONFIDENTIAL Page 1 of 63

Figure 1: Block Diagram

## 2.0 MICROPROCESSOR INTERFACE

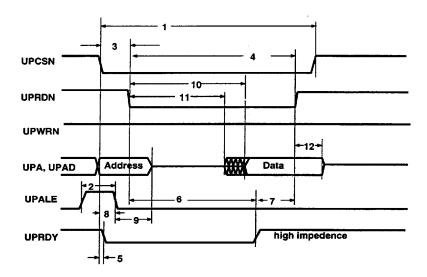

The AHA5140 provides a generic 8-bit multiplexed address/data port compatible with common microcontrollers. All internal register reads and writes go through this port. The microprocessor interface is also responsible for two types of transfers with the DRAM buffer. Firstly the processor can indirectly access the buffer through an address and data register. Secondly the chip can emulate a SRAM using part of the buffer. The following sections discuss all three responsibilities of the microprocessor interface.

## 2.1 REGISTER READS AND WRITES

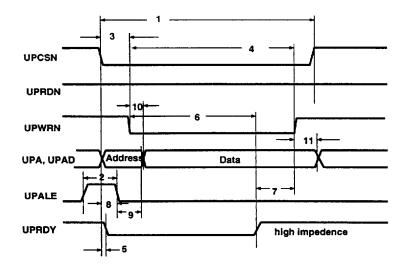

Register accesses follow a standard multiplexed address/data flow. An access is initiated by driving UPCSN low. The address on UPAD[7:0] is latched on the falling edge of the address latch enable UPALE. UPRDN and UPWRN indicate reads and writes respectively. The microprocessor wait line, UPRDY, is driven active as soon as UPCSN goes low. UPRDY releases synchronous to SYSCLK.

The microprocessor can also use fixed internal wait states for register accesses. The only exceptions are the *DRAM Address* and *DRAM Data* registers with wait generation enabled. See the "Accessing DRAM Buffer" section below.

The internal register map takes up 128 address locations. Therefore **UPCSN** must be a decode of no less than seven bits of address.

Some 16-bit processors do not fully support operation with 8-bit ports. These processors can only write even addresses to the least significant byte of the data bus. To support such processors, the AHA5140 can shift the address bus right 1 bit. Then the external firmware sees adjacent registers at addresses 0,2,4,...etc. This feature is enabled in the *System Config* register.

#### 2.2 SRAM EMULATION

The AHA5140 emulates a 64Kx8 SRAM. The data is actually stored in the first 64K of the DRAM buffer. A separate chip select, **UPSCSN** is provided to distinguish these accesses from the internal register.

UPRDY will always assert after UPSCSN asserts. In the case of a read, UPRDY will remain active until the DRAM arbitration occurs and the read data is present on UPAD[7:0]. In the case of a write, UPRDY will remain active until SRAM controller has arbitrated for a DRAM access. Waiting a write prevents coherency problems with a write followed by a read to the same address. It also prevents the next read from having to wait for a previous write to finish.

For SRAM emulation accesses the minimum bandwidth to the DRAM buffer is 1 MB/s. This occurs when Tape, Host, and ECC DMAs are all active.

If SRAM emulation is not desired, UPSCSN should be tied high and UPA[15:8] tied high or low.

Page 2 of 63 AHA CONFIDENTIAL PS5140-0496

## 2.3 ACCESSING DRAM BUFFER

The DRAM buffer is accessed through an address pointer and data register. To read or write a range of memory, the microprocessor writes the address pointer and then repeatedly reads or writes the data register. DRAM arbitrations are variable in length so wait states or polling are required to pace the transfers.

#### 2.3.1 DRAM WRITES

To write a location the microprocessor programs the desired address into *DRAM Address* from least to most significant byte with bit 23 clear. Then the processor writes the data byte to *DRAM Data*. This causes the controller to schedule a DRAM access and leaves the microcontroller free to perform other tasks. After completing the write, *DRAM Address* is automatically incremented. A subsequent write to *DRAM Data* will go to the next location in DRAM. Hence the microprocessor only needs to write the address once to write a range of memory.

While the buffer interface is busy writing a DRAM location, the microprocessor must not write DRAM Address or DRAM Data. In all modes, the DBUSY bit in DRAM Config will be set if it is not safe to write. The microprocessor can poll this register and wait for DBUSY to clear before writing either register. In addition, automatic wait state insertion can be enabled via DWTE in DRAM Config. The AHA5140 will then use UPRDY to insert wait states during write cycles to ensure any pending DRAM access has finished before completing a write to DRAM Address or DRAM Data.

## 2.3.2 DRAM READ

To read a location, the microprocessor programs the desired address into DRAM Address from least to most significant byte with bit 23 set. This initiates a DRAM access to prefetch the data into DRAM Data. The processor then reads the data from DRAM Data. After the read, DRAM Address is automatically incremented and a prefetch of the new address initiated. Hence the microprocessor only needs to write the address once to read a range of memory.

While the buffer interface is busy prefetching a DRAM location, the microprocessor must not read *DRAM Data*. Also if the buffer interface is still completing a previous access, the microprocessor must not yet write *DRAM Address*. In all modes, the **DBUSY** bit in *DRAM Config* will be set if it is not

safe to read *DRAM Data* or write *DRAM Address*. The microprocessor can poll this register and wait for **DBUSY** to clear before accessing either register. In addition, automatic wait state insertion can be enabled via **DWTE** in *DRAM Config*. The AHA5140 will then use **UPRDY** to insert wait states during read or write cycles to ensure any pending access completes before updating *DRAM Address* or reading *DRAM Data*.

### 2.3.3 DATA BYTE SKIPPING

To facilitate reading and writing QIC-3095 control bytes, AHA5140 can modify the automatic-increment feature of *DRAM Address* to skip over data bytes in a frame. When **DDBS** in *DRAM Config* is set, *DRAM Address* will increment by 512 instead of by 1 after each eight bytes. This allows the microprocessor to write all of the control bytes for a frame with only one write to *DRAM Address*. The required byte counter is reset each time the most significant byte of *DRAM Address* is written.

## 2.3.4 BANDWIDTH

For indirect accesses the minimum DRAM buffer bandwidth is 1 MB/s. This occurs when Tape, Host, and ECC are all active.

## 3.0 CLOCKS

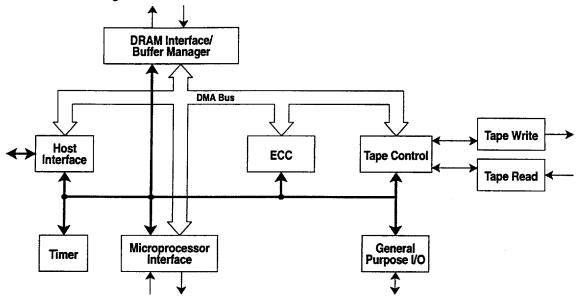

The AHA5140 has two on-board clock generation phase locked loops (PLLs). One of the PLLs generates the system clock, **SYSCLK**, and the other generates the tape clock. Figure 2 shows a block diagram of the clock generation on the AHA5140. This clock structure allows for considerable flexibility in the system design.

The System PLL is driven from a crystal oscillator which can either be connected to an external crystal or driven directly with an external clock source. The SN[2:0] and SD[3:0] inputs to the System PLL are programmable by the microprocessor in the System PLL Control register. The output of this clock generation circuit can optionally be used to generate SYSCLK. SYSCLK can also be generated directly from the crystal oscillator output. After a power-on reset SYSCLK is driven from the oscillator.

The clock network for the tape interface can either be fed from the SYSCLK or from a crystal oscillator. As with the other oscillator, this one can be connected to a crystal or driven directly from an external source. After power-on reset, the **Tape** PLL is driven from SYSCLK.

PS5140-0496 AHA CONFIDENTIAL Page 3 of 63

l 0255381 0001048786 📟

Figure 2: AHA5140 Clock Generation Block Diagram

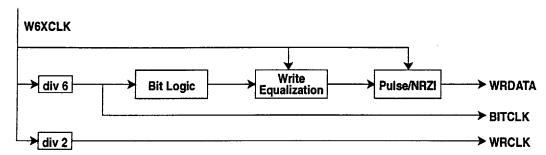

The **Tape PLL** is programmable with **TN[2:0]** and **TD[4:0]** in *Tape PLL Control* to generate a wide range of frequencies. The PLL output can optionally be used to generate the write clock, **W6XCLK**, or the PLL can be bypassed and **W6XCLK** can be generated from the PLL input. After power-on reset the PLL is bypassed.

W6XCLK is a 6-times over frequency version of the bit clock, BITCLK. The over frequency clock is necessary for the optional insertion of write equalization into the write data stream. The WRCLK output from the AHA5140 is formed by dividing W6XCLK by two.

## 4.0 GENERAL I/O PORT

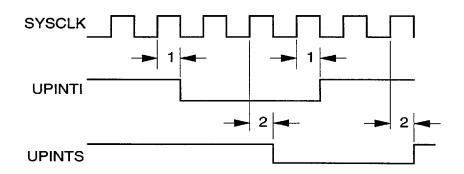

The AHA5140 provides a general purpose 8-bit I/O port for communicating with the drive mechanism or other parts of the system. The GIO[7:0] pins can always be read in the GIO Data register. All of the pins can become outputs. The direction is programmable in pairs of bits by GIO Control. Each pin also acts as an interrupt. Interrupts can be edge or level sensitive. Interrupt sensitivity is programmable by nibble in the GIO Control register. A pin not used as an interrupt can be masked via the GIO Mask register.

Level sensitive interrupts can be used to combine other system interrupts into the AHA5140's **UPINTI** interrupt output.

## 5.0 COUNTER / TIMER

The AHA5140 provides a general purpose 16-bit counter/timer for use by the drive firmware. In addition, hardware support is added to utilize the counter for tape operations. The counter can be enabled to count or halted. When enabled, it counts every time a selectable event occurs. This can be every SYSCLK, every low-frequency amble pattern written to tape, every Amble Found interrupt, or every Rewrite interrupt. The event source can also be prescaled (divided) by 1, 4, 64, or 1024. The counter can only be written when halted but can be safely read at any time.

PS5140-0496

Page 4 of 63 AHA CONFIDENTIAL

## 6.0 BUFFER MANAGER

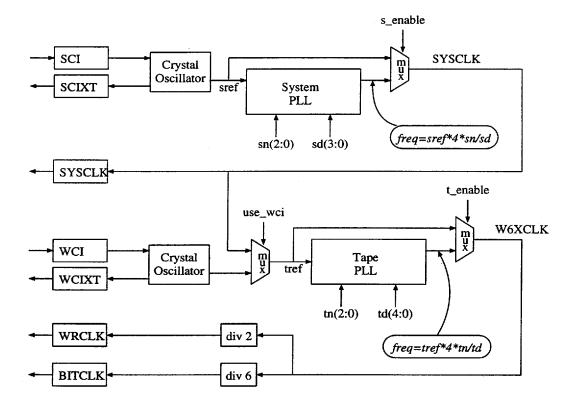

All access to the external DRAM buffer memory is done through the DMA sub-system and controlled by the buffer manager. Figure 3 shows a block diagram of the DMA sub-system. It is the buffer manager that arbitrates between the DRAM requests and assigns access according to the arbitration rules. The design of the system assures none of the rules are violated. The rules governing arbitration are listed below. All times and rates assume SYSCLK is operating at 40 MHz.

- 1) Allow a CAS-before-RAS DRAM refresh cycle to occur at least every 620 **SYSCLK** cycles.

- 2) The Tape Control receives enough bandwidth to assure that the supported formats can be read or written at a channel rate of up to 1.66 MB/s (19.9 Mb/s).

- 3) The Processor Interface has rules for both bandwidth and latency. The microprocessor is allowed up to 1.0 MB/s of DRAM bandwidth with a typical latency of 1.5µs. The typical latency is assured for all microprocessors accesses accept when a DRAM refresh is scheduled to occur. When the refresh and microprocessor are both requested, the latency is less then 2.5µs. If the microprocessor is

- using all of its bandwidth, the average latency is less than 1.6µs.

- 4) The Host Interface is allowed up to 11.1 MB/s of DRAM bandwidth. The AHA5140 could sustain this host rate indefinitely while maintaining the Tape Control, the Processor Interface and the Refresh channels at their maximum rates. In practice, however, a host transfer at this rate would exhaust the external DRAM buffer memory relatively quickly. It is this fact that allows the ECC channel sufficient bandwidth to operate.

- The ECC Channel operates at a lower priority than all of the other channels. It only gets DRAM bandwidth not used by the other channels. When all of the other channels are operating at their maximum rate, the ECC Channel will not get any DRAM bandwidth. However, as soon as any of the channels drops below peak performance, the ECC channel will grab the available cycles. As a rule of thumb, the ECC channel get one byte for every two bytes not transferred by the sum of the other channels. Under normal circumstances, it is the Host Interface that is unable to sustain its maximum rate. As soon as the host transfer exhausts the external DRAM buffer memory, the ECC channel data rate increases to about 5 MB/s.

Figure 3: DMA Sub-System

PS5140-0496

AHA CONFIDENTIAL

Page 5 of 63

**255381 0001050 334**

## **7.0 HOST**

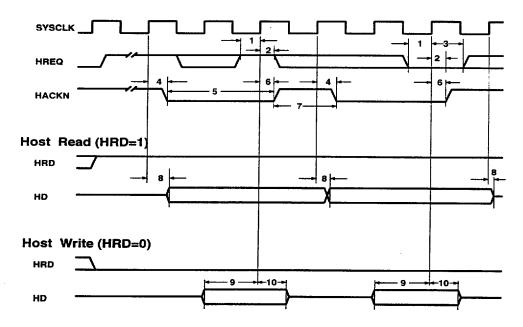

The host interface to the IC is through a generic DMA-style interface. The DMA-style interface allows for connection to an external controller such as a SCSI or ATAPI chip.

When host transfers are idle, the memory address and transfer count registers can be used to copy data from one section of the external buffer memory to another.

#### 7.1 HOST DATA MANAGER

This module controls all aspects of the host data flow. This includes the memory address, transfer counts, transfer direction and data format.

The Host Data Manager has two DMA channels for accessing the external buffer memory. Each DMA channel has a memory address pointer and a data transfer count as well as control, status and interrupts. However, the channels do share the same data path and consequently only one can be active at a time. The two channels can be configured so that one channel starts immediately upon the completion of the other. This allows a host data transfer to be mapped into non-contiguous memory locations without interruption. This feature is needed to split a host transfer into frames. The channels are referred to as DMA A and DMA B. The microprocessor can determine which channel is scheduled to be used next and the status of the channels by reading the Host Status register.

Host data transfers can be non-blocked or blocked as controlled by the **HBM** (Host Block Mode) bit in the Host Configuration 2 register. Non-blocked transfers always place host data in consecutive memory locations. In blocked transfer

mode, the DMA system reserves room in the external buffer memory for the microprocessor to later fill with the control bytes.

#### 7.1.1 NON-BLOCKED TRANSFERS

Non-blocked transfers are used for transferring sections of contiguous memory to or from the host. This type of transfer would not normally be used for tape data which is blocked. In addition, Sector copies are performed with non-block transfers.

Non-blocked transfers can be performed on either DMA A or DMA B when the HBM (Host Block Mode) bit is inactive. However, the DMA channels are not separately configurable for block mode: either both are blocked or both are non-blocked. With non-blocked transfers, the DMA address register is incremented by one and the DMA count register is decremented by one for each byte transferred to or from external buffer memory. When the DMA count expires, a DMA Done interrupt (either Host DMA A Done or Host DMA B Done) is generated.

#### 7.1.2 BLOCKED TRANSFERS

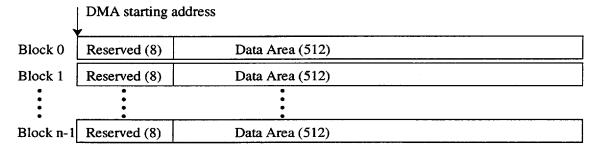

Blocked transfers are used to transfer data formatted for the tape to or from the host. Tape formatted data has an area reserved for control bytes placed before the data area for the block. A block mode transfer will transfer only bytes from the data area. The figure below shows the memory structure for an 'n' block transfer in QIC-3095. The memory structure depends upon the tape format selected in the *Tape Format* register.

Transfer Count =  $n \times 512$

Blocked transfers can be performed on either DMA A or DMA B when the **HBM** (Host Block Mode) bit in Host Configuration 2 is active. However, the DMA channels are not separately configurable for block mode: either both are

blocked or both are non-blocked. To accomplish block mode transfers, the DMA address register automatically skips the locations that are reserved for control bytes. The algorithm used to do this adds the number of control bytes (8 for QIC-3095)

Page 6 of 63

AHA CONFIDENTIAL

PS5140-0496

**--** 0255381 0001051 270 **--**

to the address register when the DMA is enabled and after every full block (512 bytes for QIC-3095) is transferred. Since the reserved area is skipped when the DMA is enabled, the starting address for a DMA should be the address for the first control byte not the address of the first data byte. For every byte in the data area, the address register increments by one. The DMA counter register is decremented by one of every byte transferred. The counter is not decremented for bytes that are skipped (control bytes).

#### 7.1.2.1 CROSSING FRAME BOUNDARIES

The blocked transfer does not skip the positions reserved in the tape format for the ECC blocks. The microprocessor should setup the DMAs such that one completes at the end of the last data block in a frame. The next DMA should then start at the beginning of the next frame. The second DMA can be enabled before the first completes to avoid a gap in the data flow to the host. The following example demonstrates the steps to do this. It assumes a 32Kbyte transfer starting at block 30 and the HNA (Host Next A) bit in *Host Status* indicates that *DMA* A is next. Furthermore, this procedure assumes that both DMA channels start out disabled.

- Program Host DMA A Address for the beginning of block 30. Program Host DMA A Count for the number of data bytes remaining in the frame (for QIC-3095 that is 22 × 512=11,264 bytes). Mask Host DMA A Done interrupt.

- 2) Program Host DMA B Address for the beginning of the next frame. Program Host DMA B Count for the number of data bytes remaining in the transfer (for QIC-3095 that is 32,768-11,264=21,504 bytes).

- 3) Enable DMA A with *Host A Enable* and enable DMA B with *Host B Enable*.

- 4) Wait for **Host DMA B Done** interrupt.

# 7.1.2.2 TRANSFER DOES NOT START AT THE BEGINNING OF A BLOCK

The DMA address generation algorithm assumes that host transfers start at the beginning of a block. While this is almost always the case, situations may arise where the host transfer must start at a location other than the beginning of a block. The following example demonstrates the steps to do this. This procedure assumes a 1K byte transfers starting at byte 20 of a block, a QIC-3095 format and that the HNA (Host Next A) bit in Host Status indicates that DMA A is next. If DMA B is next, reverse the roll of DMA A and DMA B:

- 1) Program Host DMA A Address for the address of the first byte minus 8 (8 is automatically added when the DMA is enabled). Program Host DMA A Count for the number of bytes between the first byte and the end of the data area of the block. For the example, Host DMA A Address would be programmed to 20-8=12 and Host DMA A Count to 512-20=492. Enable DMA with the Host A Enable command.

- 2) Program Host DMA B Address for the beginning (first control byte not the first data byte) of the second block. Program Host DMA B Count for the remainder of the transfer. For the example, Host DMA B Address would be programmed for the beginning of the next block and Host DMA B Count to 1024-492=532. Enable DMA with the Host B Enable command.

- 3) Wait for **Host DMA A Done** and **Host DMA B Done** interrupts.

# 7.1.2.3 LOGICAL BLOCK IS NOT MULTIPLE OF PHYSICAL BLOCK

The QIC tape formats required that every logical block begins on at the beginning of a physical block. When the logical block length is multiple of the physical block length, this also means that every logical block will end at the end of the physical block. However, when the logical block length is not a multiple of the physical block length, the end of logical block will not be aligned with the end of physical block. This fact necessitates gaps in the memory map. As an example, the figure below shows how the two, 700 byte logical blocks would be DMA'ed. The steps involved in setting up these transfers are:

- Set the Host DMA A Address register for the beginning of a block. Set the Host DMA A Count register for the length of the transfer, 700 bytes. Enable the transfer with the Host DMA A Enable command.

- 2) Either before or after the Host DMA A Done interrupt, setup DMA B. Set the Host DMA B Address register for beginning of the third physical block. Set the Host DMA B Count to 700 bytes. Enable with Host DMA B Enable command.

- After the Host DMA A Done interrupt, another the DMA A channel can be reinitialized and enabled.

PS5140-0496 AHA CONFIDENTIAL Page 7 of 63

| DMA A starting address Transfer count=700 |          |                                       |     |  |  |  |

|-------------------------------------------|----------|---------------------------------------|-----|--|--|--|

| Physical Block 0                          | Reserved | rved Logical Block 0 (bytes 0 to 511) |     |  |  |  |

| Physical Block 1                          | Reserved | Logical Block 0 (bytes 512 to 699 Gap |     |  |  |  |

| DMA B starting address Transfer count=700 |          |                                       |     |  |  |  |

| Physical Block 2                          | Reserved | Logical Block 1 (bytes 0 to 51        | 11) |  |  |  |

| Physical Block 3                          | Reserved | Logical Block 1 (bytes 512 to 699)    | Gap |  |  |  |

## 7.1.3 MEMORY-TO-MEMORY COPY

The host DMA channels can be used to copy data from one section of memory to another. This copy is performed at a rate of approximately one half the maximum host data rate. This mode is enabled with the **COPY** bit in *Host Configuration 2*.

In copy mode, the source of the data is specified with Host DMA A Address and the destination with Host DMA B Address. The number of bytes to be transferred must be specified in both Host DMA A Count and Host DMA B Count. Block mode transfers must be disabled during a copy operation and the Host DMA A Done interrupt should be masked.

To start the copy operation, enable issue *Host A Enable* and *Host B Enable* commands during the same microprocessor write cycle. The **Host DMA B Done** interrupt will occur when the copy is finished.

## 7.1.4 PARITY ERRORS

Parity errors can occur on either the host interface pins or on the DRAM interface. Each source of parity errors has its own interrupt; Host Bus Parity Error and Host DRAM Parity Error. Other than the interrupt, the module handles parity errors from either source the same way.

When a parity error is detected the enabled **DMA** is put in the *error* state.

## 8.0 ECC

The ECC module performs both the encoding and decoding operations for the QIC-3095 format as well as several of the TR5 proposals (QIC-95-75 rev C, QIC-95-91, QIC-95-93). The error correction code implemented by the module is a

Reed-Solomon code in GF(256). The field is generated from the following primitive polynomial:

$$F(x) = x^8 + x^7 + x^2 + x + 1$$

The generator polynomial for the code is a function of the redundancy, r, and therefore depends upon the programming of the *ECC Format* register. However, the general form of the polynomial is:

$$G(x) = \prod_{i=0}^{r-1} (x+2^{i})$$

A redundancy of either 6, 8 or 10 is supported.

## 8.1 BACKGROUND

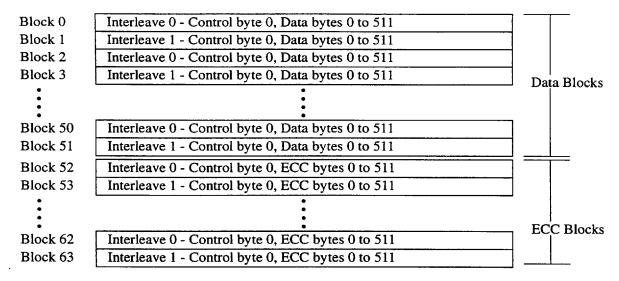

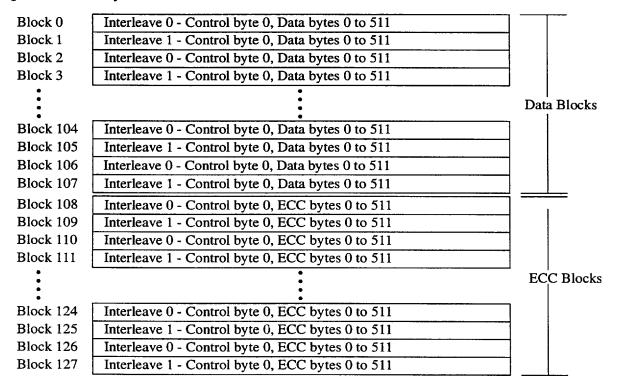

The memory format expected by the ECC is determined by the programming of the ECC Format register. Figure 4 and Figure 5 show the memory matrix for the supported tape formats. Encoding and decoding are performed on ECC code words which are columns when the frame is viewed as this matrix. The bytes in a column in the same interleave are in the same code word. The bytes in that column from a different interleave are part of a different code word. Processing on one code word completes before the next code word is started. Multiple code words, up to an entire interleave, can be processed in one operation before an interrupt is generated. The number of code words in an operation is programmed in ECC Code Words.

In addition to specifying the number of blocks, the starting address for the operation needs to be programmed in *ECC DMA Address*. The starting address for a code word is the memory address for the first byte in the block. This byte is always in the first block of the interleave. When performing ECC on an entire interleave, program the starting address to the memory address of the control byte of the first block.

Selection between encoding and decoding is done with **ENCODE** bit in the *ECC Configuration* register. The *ECC Command* register controls the starting and stopping of the ECC.

Page 8 of 63

AHA CONFIDENTIAL

PS5140-0496

**.** 0255381 0001053 043 **.**

Figure 4: Memory Matrix for QIC-3095 Format

Figure 5: Memory Matrix for QIC-95-73 Rev C Format

## 8.2 ECC ENCODING

The ECC encoding operation generates the code words for a frame and writes them to external buffer memory. After encoding, the frame is ready to be written to tape. The module can be programmed to process up to one interleave at a time. For QIC-3095, this means the microprocessor needs to initiate two processes and will receive two

interrupts. The following procedure can be used to ECC encode a frame:

Setup interleave 0 by programming ECC DMA Address with the address for control byte 0 of block 0 and the code word counter register, ECC Code Words with the number code words in the interleave, 513 (201hex). Select ECC encoding with the ENCODE bit. Start the operation with the START command.

- 2) Wait for ECC Done interrupt.

- 3) Setup interleave 1 by programming ECC DMA Address with the address for control byte 0 of block 1 and the code word counter register, ECC Code Words with the number blocks in the interleave, 513 (201hex). ECC encoding should already be selected in the ENCODE bit. Start the operation with the START command.

- 4) Wait for *ECC Done* interrupt.

If DRAM parity checking is enabled, a parity error is possible. If a parity error is detected, an **ECC Parity Error** interrupt is generated and encoding terminates as if a **STOP** command was received. The code word containing the parity error can be determined by reading the *ECC Code Words* register. If desired, the encoding operation can be re-started on the code word with the error.

## 8.3 ECC DECODING

The ECC decoding operation corrects the data bytes that are flagged as being in error. The error flags for a frame are referred to as the "erasure vector." The TAPE module generates the erasure vector from the CRC check and stores it in external buffer memory. The memory address for the erasure vector must be programmed in the ECC erasure address register. In addition, the decoding operation must know which interleave is being decoded. This is programmed in the Interleave register. The ECC module loads the erasure vector immediately after a START command is received.

The module can be programmed to decode up to one interleave at a time. Upon the successful decoding of each code word, an ECC Code Word Done interrupt is generated. If the module is unable to decode a code word it generates an ECC Code Word Uncorrectable interrupt. An uncorrectable code word causes the decode operation to terminate. The ECC Code Words register can be read to determine which code word caused the error. Since under certain circumstances the decoder does not know a code word will cause an error until after correction has been attempted, several bytes in the code word may be modified before the operation is terminated.

A general procedure for decoding a QIC-3095 frame is shown below. This procedure assumes that all code words in the frame are correctable by the decoder:

1) Setup interleave 0 by programming ECC DMA Address with the address for control byte 0 of

- block 0 and the code word counter register,  $ECC\ Code\ Words$  with the number code words in the interleave, 513 (201hex). Program the erasure vector location in  $ECC\ Erasure\ Address$  (for this case, EEA = EDA + 33, 273). Program the interleave, INTR to zero. Select ECC decoding by setting the ENCODE bit to zero. Start the operation with the START command.

- 2) Wait for **ECC Done** interrupt.

- 3) Setup interleave 1 by programming ECC DMA Address with the address for control byte 0 of block 1 and the code word counter register, ECC Code Words with the number of code words in the interleave, 513 (201hex). The ECC Erasure Address register must be re-programmed with the same value as was written in step 1. Program the interleave, INTR to one. ECC decoding should already be selected. Start the operation with the START command.

- 4) Wait for ECC Done interrupt.

If DRAM parity checking is enabled, a parity error is possible. If a parity error is detected, an ECC Parity Error interrupt is generated and decoding terminates as if a STOP command was received. During decoding, parity errors can occur while reading the erasure vector, while reading in a code word or while performing corrections on a code word. The code word containing the parity error can be determined by reading the ECC Code Words register. If desired, the decoding operation can be re-started on the code word with the error.

## 9.0 TAPE

## 9.1 TAPE OVERVIEW

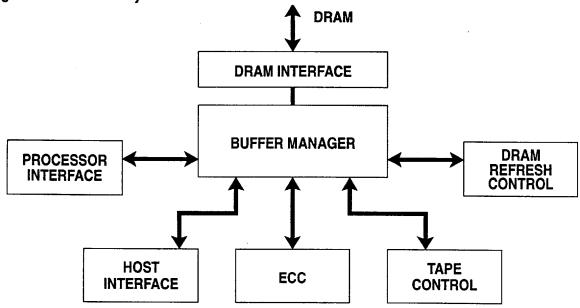

## 9.1.1 TAPE BLOCK DIAGRAM

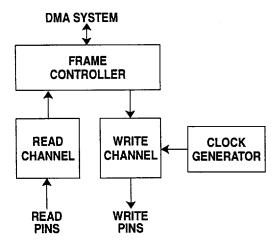

The tape channel formats data going to and from tape. It supports read and write for both QIC-3095 and the proposed TR5 format (QIC-95-75 rev C, QIC-95-91, QIC-93) as well as read compatibility for QIC-80, QIC-3010 and QIC-3020. The tape channel provides frame level control logic to provide a high-level user interface. The tape channel consists of four main sections: a write channel, read channel, frame controller, and clock generator as shown in Figure 6.

As the figure above indicates, the read and write channels are independent. This provides for full read-while-write support.

Page 10 of 63 AHA CONFIDENTIAL PS5140-0496

Figure 6: Tape Block Diagram

#### 9.1.2 TAPE CHANNEL MODES

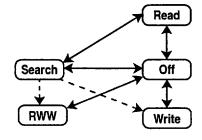

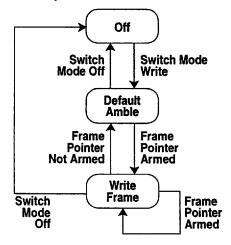

The tape channel has five modes of operation selected by the Tape Control register. These are Off, Write, Read-While-Write, Search, and Read. The simplest is Off which acts as a reset preventing any data transfers or interrupts and clearing all state machines and internal storage. In Write mode, data is sent from DRAM to tape but no read channel interrupts occur. In Read-While-Write mode, data is written to tape and the read channel reports all interrupt and status information. In Search mode, all of the read interrupts and status are reported but no data is sent to DRAM. In Read mode, all read channel interrupts are active and data is sent to DRAM. The mode can be switched from Off to any other mode and vice versa. In addition the controller can go from Off to Search to Write or Read-While-Write as shown in Figure 7.

Figure 7: Read-While-Write Process Flow

#### 9.1.3 DATA TRANSFERS

A tape operation is performed by first setting the appropriate mode and then enabling a data transfer. The tape controller contains two address pointers which are used as initial addresses for DMA transfers. One is for the "current" and one for the "next" transfer. Transfers are single blocks or entire frames. Since the AHA5140 is intended for frame level operation, these pointers are called frame pointers. A frame is enabled by writing the *Frame Control* register. As each block/frame completes, the other pointer becomes the current pointer. The *Frame Control* register provides a bit indicating which pointer is the next. The microprocessor enables the first frame, prearms the second, and then only needs to prearm a new frame as each one finishes.

#### 9.1.4 FRAME FORMAT

The Frame controller assumes a particular frame format in memory. Each block is placed sequentially in memory with no gaps. The erasure vector (CRC status) information used for reads is stored immediately after the last block of the frame. The CRC status of each block is stored as a single bit. Each byte represents eight blocks. The first block is stored in bit 7 and the eighth block in bit 0. The microprocessor can examine erasure information by indirectly accessing DRAM.

The following subsections describe the physical formats supported and then discusses each of the tape operations.

## 9.2 PHYSICAL FORMATS

The physical formats used by the tape channel are selected in the *Tape Format* register. The particular block marker, modulation scheme, control bytes, data bytes, and CRC are set according to the selected format. There are two formats supported. One is a RLL format defined by QIC-3095. The other is an MFM format defined by QIC-80, QIC-3010 and QIC-3020. The following sections describe the details of each format.

PS5140-0496 AHA CONFIDENTIAL Page 11 of 63

🖿 025538l 000l056 852 🖿

#### 9.2.1 RLL SUPPORT

The block format for QIC-3095 has the following fields and (unencoded) byte lengths.

| 2      | 8       | 512   | 4   |

|--------|---------|-------|-----|

| Block  | Control | Data  | CRC |

| Marker | Bytes   | Bytes |     |

A two block write would have the following sequence and byte lengths.

| TIMED            | 13,20,30 |       | 1         | 13,20,30 |       | 1         | TIMED            |

|------------------|----------|-------|-----------|----------|-------|-----------|------------------|

| Default<br>Amble | Preamble | Block | Postamble | Preamble | Block | Postamble | Default<br>Amble |

## 9.2.1.1 AMBLE (RLL)

After enabling a Write or Read-While-Write, the tape channel will output a default amble pattern. The default pattern is:

000000010000000100000001

(low frequency amble)

When a frame or block is enabled, the tape controller will complete the current 24-bit default amble pattern and then switch to high frequency amble (normal preamble). The pattern is:

010101010101

The number of bytes (12 bit patterns) of normal preamble is selected in *Tape Format*. At the end of a block, the normal postamble is always one byte (12 bits).

## 9.2.1.2 BLOCK MARKER (RLL)

The block marker pattern is:

010 101 010 000 000 100 000 010

During a read, the block marker must be preceded by 24 bits of high frequency preamble to be considered valid.

#### 9.2.1.3 MODULATION CODE (RLL)

The modulation code is RLL 1:7 as defined by the following table where "X" means the inverse of the previous bit:

| DATA BITS | ENCODED BITS    |

|-----------|-----------------|

| 01        | X00             |

| 10        | 010             |

| 11        | X01             |

| 0001      | X00 001         |

| 0010      | X00 000         |

| 0011      | 010 001         |

| 0000      | 010 000         |

| 1110 1110 | 010 000 001 001 |

| 1011 1011 | 010 000 001 010 |

During a write, if the CRC ends in 00, an extra 01 will be inserted in the data stream to form a valid RLL encoding.

#### 9.2.1.4 RANDOMIZATION (RLL)

Control and Data bytes can be randomized as selected in *Tape Control*. The polynomial used for randomization is:

$$x^{12} + x^6 + x^4 + x + 1$$

If enabled, randomization starts from the MSB of Control Byte 7 and goes through the LSB of Data Byte 511. All bits of the randomizer circuit are set to 1 prior to encoding. The same holds for derandomization.

PS5140-0496

Page 12 of 63 AHA CONFIDENTIAL

**■** 0255381 0001057 799 **■**

#### 9.2.1.5 CONTROL BYTES (RLL)

There are always 8 control bytes in a block. The physical block number is expected to be in first three control bytes (7, 6, and 5) and stored LSB first. When performing reads, the physical block number is extracted from the control bytes and stored in the *Incoming Block* register. When the third byte is loaded a **Control Bytes Available** interrupt is issued.

## **9.2.1.6 DATA BYTES (RLL)**

The data field is always 512 bytes long.

## 9.2.1.7 CRC (RLL)

The CRC is generated bitwise on the data starting from the MSB of control byte 7 through the LSB of data byte 511. The CRC is calculated before

randomization and RLL encoding. The generator polynomial is:

$$x^{32} + x^{28} + x^{26} + x^{19} + x^{17} + x^{10} + x^{6} + x^{2} + 1$$

All bits are set to 1 prior to CRC calculations. In the read channel, every block reports a CRC interrupt, either good or bad (CRC Good and CRC Bad respectively).

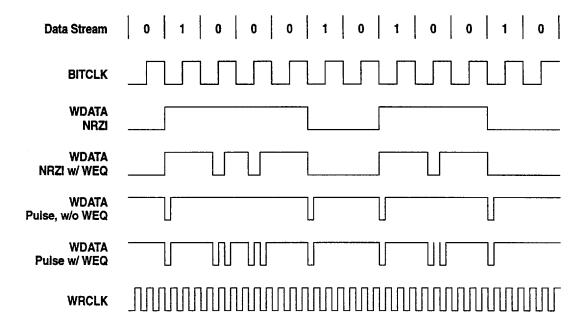

## 9.2.1.8 OUTPUT FORMAT (RLL)

The output stream can be in a NRZI or Pulse format. Either mode may also be write equalized. In Pulse format, each "1" in the data stream is a 1/6 bit cell pulse. If write equalization is enabled, two extra 1/6 cell pulses are inserted between any pair of zeros. In NRZI format, the output toggles for each "1" and, if write equalization is enabled, the output pulses for 1/3 a bit cell between any pairs of zeros. NRZI data changes with the falling edge of WRCLK. Figure 8 illustrates the output format.

Figure 8: Tape Channel Output Data Waveforms

Write equalization can be turned on and off on the fly. The tape channel will change equalization modes on bit cell boundaries.

PS5140-0496

AHA CONFIDENTIAL

Page 13 of 63

🗷 025538l 000l058 625 📟

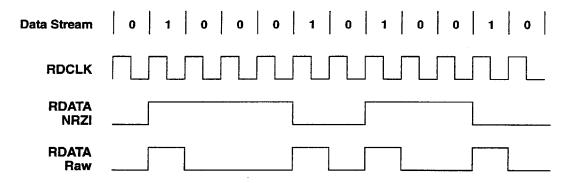

## 9.2.1.9 INPUT FORMAT (RLL)

Read channel input data can be in NRZI or raw data form. The value on **RDATA** is sampled on the rising edge of each **RDCLK**. Selection between the two modes is made in *Tape Control*. The following diagram illustrates the two modes.

Figure 9: Tape Channel Input Waveforms

#### 9.2.2 MFM SUPPORT

The AHA5140 offers read compatibility for QIC-80, QIC-3010 and QIC-3020 formats (MFM). These formats read at low data rates so only block level support is provided. The chip must be placed in block mode and each DMA enabled seperately. The current and next block (frame) pointers can be thought of as active and prearm DMAs.

QIC-80, QIC-3010 and QIC-3020 contain three different block types, Segment Headers, Track Sector IDs, and Data Blocks. The AHA5140 detects all three and generates an interrupt for each. For each Segment Header, a Segment Header Found interrupt is generated. For a Track Sector ID block, the floppy track, side, and sector are stored into the *Incoming Block* register and a Control Bytes Available interrupt issued. A bad CRC for a Track Sector ID is reported via the Track ID CRC Bad interrupt. At the end of a Data Block the CRC is checked and a CRC Good or CRC Bad interrupt issued.

#### 9.2.2.1 SEGMENT HEADER (MFM)

A Segment Header contains no information but the AHA5140 issues a Segment Header Found interrupt each time an Index Address Mark is detected on tape. An Index Address Mark is a specially encoded C2C2C2FC:

The index address mark must be preceded by 24 bits of sync mark 0x00, (1.5 bytes). The read channel does not search for Segment Headers while reading Track Sector IDs or Data Blocks.

## 9.2.2.2 TRACK SECTOR ID (MFM)

A Track Sector ID starts with a Sector ID Address Mark and contains the floppy track, side, and sector numbers for the following Data Block. The Sector ID Address Mark is a specially encoded 0xA1A1A1FE:

Page 14 of 63

AHA CONFIDENTIAL

PS5140-0496

**■** 0255381 0001059 561 **■**

When the read channel recognizes a Sector Address ID Mark preceded by 24 bits of sync mark (0x00, 1.5 bytes), it places the floppy track, side, and sector numbers into the *Incoming Block* register and issues a **Control Bytes Available** interrupt. These bytes are never written to DRAM. The CRC for the Track Sector ID is reported via the **Track ID CRC Bad** interrupt. This can be sampled as a status bit after the **Block Marker Found** for the following Data Block.

## 9.2.2.3 DATA BLOCK (MFM)

A Data Block starts with a Data Address Mark and contains 1024 bytes of data. The Data Address Mark is a specially encoded 0xA1A1A1FB:

When the read channel recognizes a Data Address Mark preceded with 24 bits of sync mark (0x00, 1.5 bytes), it issues a **Block Marker Found** interrupt and reads the next 1024 bytes of data off tape. If the tape mode is set to Read, these bytes are sent to DRAM. At the end of the block it verifies the CRC and issues a **CRC Good** or **CRC Bad** interrupt.

## 9.2.2.4 MODULATION CODE (MFM)

The AHA5140 expects an input clock with a frequency twice that of the bit rate off tape. In particular "data" and "clock" bits are both sampled by RDCLK. The MFM decoder converts 2 bit pairs into single bits according to the following table:

| UNENCODED PATTERN CURRENT (NEXT) | ENCODED<br>PATTERN |

|----------------------------------|--------------------|

| 00 (0)                           | Error              |

| 00 (1)                           | 0                  |

| 01 (0)                           | 0                  |

| 01 (1)                           | Error              |

| 10                               | 1                  |

| 11                               | Error              |

If any modulation errors are found within a Data Block, a **Modulation Error** interrupt is reported. Only one interrupt is generated per block.

#### 9.2.2.5 CRC (MFM)

The CRC is calculated after MFM decoding and is based on the following polynomial:

$$x^{16} + x^{12} + x^5 + 1$$

All CRC calculation bits are initialized to 1. For a Track Sector ID block the CRC is calculated from the most significant bit of the first Sector ID Address Mark byte to the least significant bit of the bytes per sector (4th) byte. For a Data Block the CRC is calculated from the most significant bit of the first Data Address Mark to the least significant bit of the 1024th data byte. Separate interrupts are generated for good and bad CRCs (CRC Good and CRC Bad respectively).

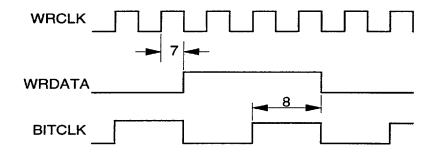

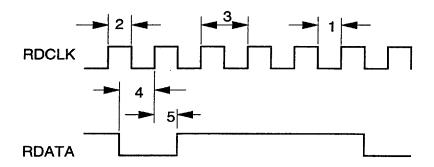

#### 9.2.3 TAPE CHANNEL CLOCKS

The Tape Interface receives the W6XCLK. This clock is divided by 6 and optionally output as BITCLK. BITCLK is also used to clock the bitlevel logic in the Tape Write Channel. In order to generate the write equalization pulses required by the format, the W6XCLK is used. The output data, WRDATA, is driven off chip from the rising edge of W6XCLK.

The read data input pin, **RDATA**, is sampled off the rising edge of each **RDCLK**. During normal operation, the internal read channel logic is clocked with **RDCLK**. For chip self test, an internal loopback mode is provided. In loopback mode, **RDCLK** is effectively driven by **BITCLK** and **RDATA** by the **WRDATA**. The selection between normal and loopback mode is made in the *Tape Clock* register.

PS5140-0496

AHA CONFIDENTIAL

Page 15 of 63

📰 025538l 000l060 283 빼

Figure 10: Tape Channel Clocks

The read data input pin, RDATA, is sampled of the rising edge of each RDCLK. During normal operation, the internal read channel logic is run off RDCLK. For chip self test, an internal loopback mode is provided. In loopback mode, RDCLK is effectively driven by BITCLK and RDATA by the write channel. The selection between normal and loopback mode is made in the Clock Configuration register.

# 9.2.4 READ CHANNEL DATA RECOVERY CONTROL

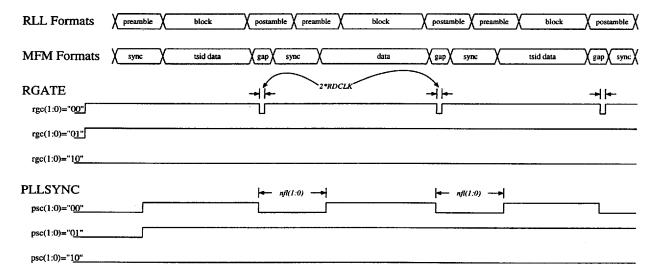

The AHA5140 outputs two signals for data recovery control in the read channel IC. These signals are RGATE and PLLSYNC. RGATE is intended to switch the data recovery circuit from fixed to closed-loop clock mode and reset the VCO.