Technical Data

Document Number: MPC17531A Rev. 4.0, 5/2009

# 700 mA Dual H-Bridge Motor Driver with 3.0 V Compatible Logic I/O

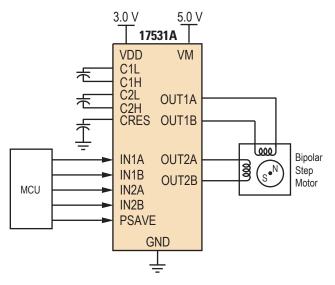

The 17531A is a monolithic dual H-Bridge power IC ideal for portable electronic applications containing bipolar step motors and/or brush DC-motors (e.g., cameras and disk drive head positioners).

The 17531A operates from 2.0 V to 8.6 V using the internal charge pump, with independent control of each H-Bridge via parallel MCU interface. The device features built-in shoot-through current protection and an undervoltage shutdown function.

The 17531A has four operating modes: Forward, Reverse, Brake, and Tri-Stated (High Impedance). The 17531A has a low total  $R_{DS(ON)}$  of 1.2  $\Omega$  (max @ 25°C).

The 17531A efficiently drives many types of micromotors with low power dissipation owing to its low output resistance and high output slew rates. The H-Bridge outputs can be independently pulse width modulated (PWM'ed) at up to 200 kHz for speed/torque and current control.

#### **Features**

- Low Total RDS(ON) 0.8 W (Typ), 1.2 Ω (Max) @ 25°C

- Output Current 0.7 A (DC)

- · Shoot-Through Current Protection Circuit

- PWM Control Input Frequency up to 200 kHz

- · Built-In Charge Pump Circuit

- · Low Power Consumption

- · Undervoltage Detection and Shutdown Circuit

- Power Save Mode with Current Draw  $\leq$  2.0  $\mu$ A

- Pb-Free Packaging Designated by Suffix Codes EV and EP

## 17531A

#### **DUAL H-BRIDGE**

VMFP SUFFIX EV SUFFIX (PB-FREE) 98ASA10616D 20-TERMINAL VMFP

QFN SUFFIX EP SUFFIX (PB-FREE) 98ARL10577D 24-TERMINAL QFN

| ORDERING INFORMATION                               |               |         |  |  |

|----------------------------------------------------|---------------|---------|--|--|

| Device Temperature Range (T <sub>A</sub> ) Package |               |         |  |  |

| MPC17531AEV/EL                                     | -20°C to 65°C | 20 VMFP |  |  |

| MPC17531AEP/R2                                     | 20 0 10 00 0  | 24 QFN  |  |  |

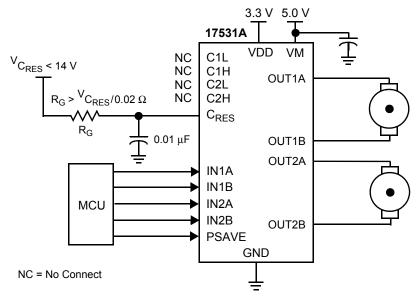

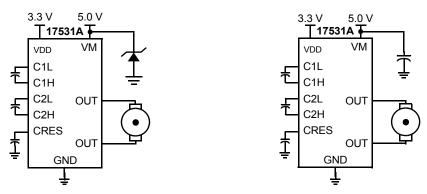

Figure 1. 17531A Simplified Application Diagram

Freescale Semiconductor, Inc. reserves the right to change the detail specifications, as may be required, to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2005 - 2009. All rights reserved.

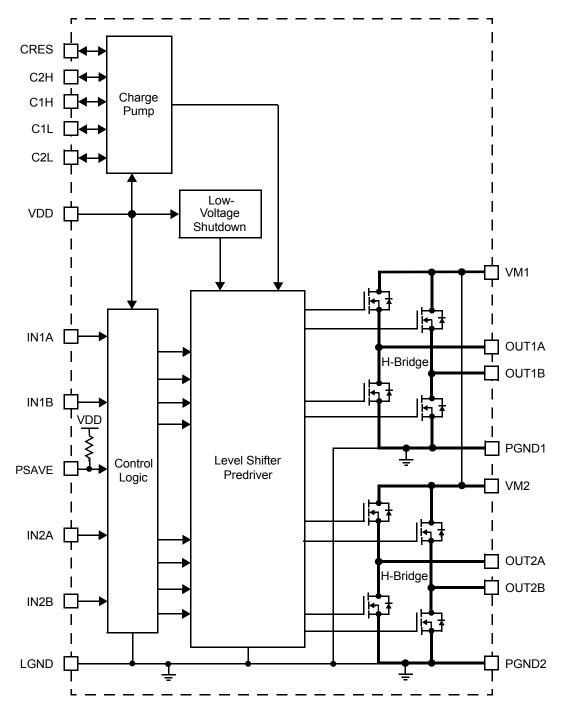

## INTERNAL BLOCK DIAGRAM

Figure 2. 17531A Simplified Internal Block Diagram

## **TERMINAL CONNECTIONS**

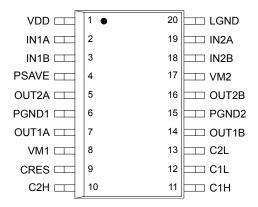

Figure 3. 17531A, 20-Terminal VMFP Connections

## Table 1. 17531A, 20-Terminal VMFP Definitions

A functional description of each terminal can be found in the Functional Terminal Description section beginning on page 10.

| Terminal<br>Number | Terminal<br>Name | Formal Name                | Definition                                                                  |

|--------------------|------------------|----------------------------|-----------------------------------------------------------------------------|

| 1                  | VDD              | Logic Supply               | Control circuit power supply terminal.                                      |

| 2                  | IN1A             | Logic Input Control 1A     | Logic input control of OUT1A (refer to Table 6, Truth Table, page 9).       |

| 3                  | IN1B             | Logic Input Control 1B     | Logic input control of OUT1B (refer to Table 6, Truth Table, page 9).       |

| 4                  | PSAVE            | Power Save                 | Logic input controlling power save mode.                                    |

| 5                  | OUT2A            | H-Bridge Output 2A         | Output A of H-Bridge channel 2.                                             |

| 6                  | PGND1            | Power Ground 1             | High-current power ground 1.                                                |

| 7                  | OUT1A            | H-Bridge Output 1A         | Output A of H-Bridge channel 1.                                             |

| 8                  | VM1              | Motor Drive Power Supply 1 | Positive power source connection for H-Bridge 1 (Motor Drive Power Supply). |

| 9                  | CRES             | Predriver Power Supply     | Internal triple charge pump output as predriver power supply.               |

| 10                 | C2H              | Charge Pump 2H             | Charge pump bucket capacitor 2 (positive pole).                             |

| 11                 | C1H              | Charge Pump 1H             | Charge pump bucket capacitor 1 (positive pole).                             |

| 12                 | C1L              | Charge Pump 1L             | Charge pump bucket capacitor 1 (negative pole).                             |

| 13                 | C2L              | Charge Pump 2L             | Charge pump bucket capacitor 2 (negative pole).                             |

| 14                 | OUT1B            | H-Bridge Output 1B         | Output B of H-Bridge channel 1.                                             |

| 15                 | PGND2            | Power Ground 2             | High-current power ground 2.                                                |

| 16                 | OUT2B            | H-Bridge Output 2B         | Output B of H-Bridge channel 2.                                             |

| 17                 | VM2              | Motor Drive Power Supply 2 | Positive power source connection for H-Bridge 2 (Motor Drive Power Supply). |

| 18                 | IN2B             | Logic Input Control 2B     | Logic input control of OUT2B (refer to Table 6, Truth Table, page 9).       |

| 19                 | IN2A             | Logic Input Control 2A     | Logic input control of OUT2A (refer to Table 6, Truth Table, page 9).       |

| 20                 | LGND             | Logic Ground               | Low-current logic signal ground.                                            |

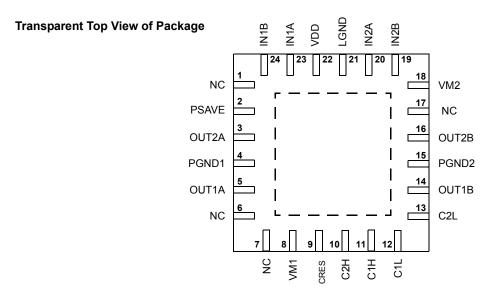

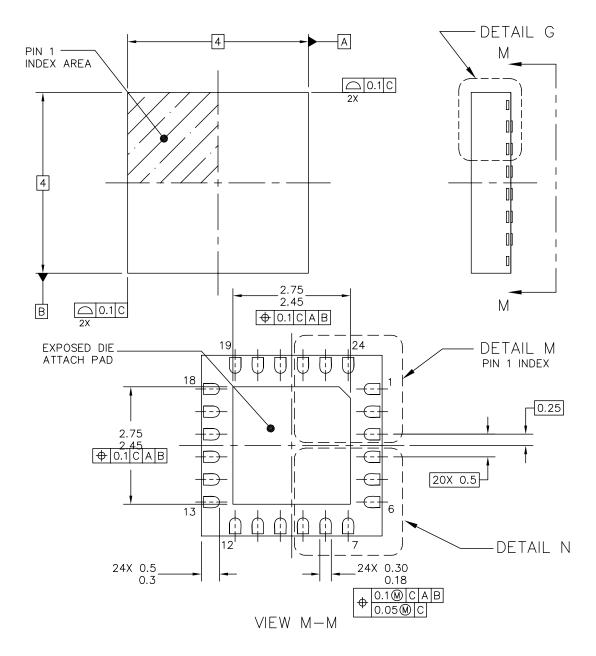

Figure 4. 17531A, 24-Terminal QFN Connections

Table 2. 17531A, 24-Terminal QFN Definitions

A functional description of each terminal can be found in the Functional Terminal Description section beginning on page 10.

| Terminal<br>Number | Terminal<br>Name | Formal Name                | Definition                                                                  |

|--------------------|------------------|----------------------------|-----------------------------------------------------------------------------|

| 1, 6, 7, 17        | NC               | No Connect                 | This terminal is not used.                                                  |

| 2                  | PSAVE            | Power Save                 | Logic input controlling power save mode.                                    |

| 3                  | OUT2A            | H-Bridge Output 2A         | Output A of H-Bridge channel 2.                                             |

| 4                  | PGND1            | Power Ground 1             | High-current power ground 1.                                                |

| 5                  | OUT1A            | H-Bridge Output 1A         | Output A of H-Bridge channel 1.                                             |

| 8                  | VM1              | Motor Drive Power Supply 1 | Positive power source connection for H-Bridge 1 (Motor Drive Power Supply). |

| 9                  | C <sub>RES</sub> | Predriver Power Supply     | Internal triple charge pump output as pre-driver power supply.              |

| 10                 | C2H              | Charge Pump 2H             | Charge pump bucket capacitor 2 (positive pole).                             |

| 11                 | C1H              | Charge Pump 1H             | Charge pump bucket capacitor 1 (positive pole).                             |

| 12                 | C1L              | Charge Pump 1L             | Charge pump bucket capacitor 1 (negative pole).                             |

| 13                 | C2L              | Charge Pump 2L             | Charge pump bucket capacitor 2 (negative pole).                             |

| 14                 | OUT1B            | H-Bridge Output 1B         | Output B of H-Bridge channel 1.                                             |

| 15                 | PGND2            | Power Ground 2             | High-current power ground 2.                                                |

| 16                 | OUT2B            | H-Bridge Output 2B         | Output B of H-Bridge channel 2.                                             |

| 18                 | VM2              | Motor Drive Power Supply 2 | Positive power source connection for H-Bridge 2 (Motor Drive Power Supply). |

| 19                 | IN2B             | Logic Input Control 2B     | Logic input control of OUT2B (refer to Table 6. Truth Table, page 9).       |

| 20                 | IN2A             | Logic Input Control 2A     | Logic input control of OUT2A (refer to Table 6. Truth Table, page 9).       |

| 21                 | LGND             | Logic Ground               | Low-current logic signal ground.                                            |

| 22                 | V <sub>DD</sub>  | Logic Supply               | Control circuit power supply terminal.                                      |

| 23                 | IN1A             | Logic Input Control 1A     | Logic input control of OUT1A (refer to Table 6. Truth Table, page 9).       |

| 24                 | IN1B             | Logic Input Control 1B     | Logic input control of OUT1B (refer to Table 6, Truth Table, page 9).       |

## **MAXIMUM RATINGS**

## **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                       | Symbol              | Value                        | Unit |

|-----------------------------------------------|---------------------|------------------------------|------|

| Motor Supply Voltage                          | $V_{M}$             | -0.5 to 11.0                 | V    |

| Charge Pump Output Voltage                    | $V_{C_{RES}}$       | -0.5 to 14.0                 | V    |

| Logic Supply Voltage                          | V <sub>DD</sub>     | -0.5 to 5.0                  | V    |

| Signal Input Voltage                          | V <sub>IN</sub>     | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Driver Output Current                         |                     |                              | Α    |

| Continuous                                    | I <sub>O</sub>      | 0.7                          |      |

| Peak <sup>(1)</sup>                           | l <sub>OPK</sub>    | 1.4                          |      |

| ESD Voltage                                   |                     |                              | V    |

| Human Body Model (2)                          | V <sub>ESD1</sub>   | ±1200                        |      |

| Machine Model (3)                             | V <sub>ESD2</sub>   | ±150                         |      |

| Operating Junction Temperature                | T <sub>J</sub>      | -20 to 150                   | °C   |

| Operating Ambient Temperature                 | T <sub>A</sub>      | -20 to 65                    | °C   |

| Storage Temperature Range                     | T <sub>STG</sub>    | -65 to 150                   | °C   |

| Thermal Resistance <sup>(4)</sup>             | $R_{	heta JA}$      | 50                           | °C/W |

| Power Dissipation <sup>(5)</sup>              | P <sub>D</sub>      |                              | W    |

| WMFP                                          |                     | 1.0                          |      |

| QFN                                           |                     | 2.5                          |      |

| Terminal Soldering Temperature <sup>(6)</sup> | T <sub>SOLDER</sub> | 260                          | °C   |

## Notes

- 1.  $T_A = 25$ °C. Pulse width = 10 ms at 200 ms intervals.

- 2. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ).

- 3. ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ).

- 4. For QFN only, mounted on 37 x 50 Cu area (1.6 mm FR-4 PCB).

- 5.  $T_A = 25^{\circ}C$ .

- 6. Terminal soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

## STATIC ELECTRICAL CHARACTERISTICS

**Table 4. Static Electrical Characteristics**

Characteristics noted under conditions  $T_A$  = 25°C,  $V_{DD}$  = 3.0 V,  $V_M$  = 5.0 V, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                     | Symbol                                           | Min    | Тур    | Max        | Unit |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------|--------|--------|------------|------|

| POWER INPUT                                                                                        | 1                                                |        |        |            | 1    |

| Motor Supply Voltage (Using Internal Charge Pump) (7)                                              | V <sub>M-CP</sub>                                | 2.0    | 5.0    | 8.6        | V    |

| Motor Supply Voltage (V <sub>CRES</sub> Applied Externally) (8)                                    | V <sub>M-NCP</sub>                               | -      | _      | 10         | V    |

| Gate Drive Voltage - Motor Supply Voltage (V <sub>CRES</sub> Applied Externally) (9)               | VCRES-VM                                         | 5.0    | 6.0    | _          | V    |

| Logic Supply Voltage                                                                               | V <sub>DD</sub>                                  | 2.7    | 3.0    | 3.6        | V    |

| Driver Quiescent Supply Current No Signal Input Power Save Mode                                    | IQM<br>IQM-PSAVE                                 | -      |        | 100<br>1.0 | μА   |

| Logic Quiescent Supply Current  No Signal Input <sup>(10)</sup> Power Save Mode                    | <sup>I</sup> QVDD<br><sup>I</sup> QVDD-<br>PSAVE | -<br>- | -<br>- | 1.0<br>1.0 | mA   |

| Operating Power Supply Current  Logic Supply Current (11)  Charge Pump Circuit Supply Current (12) | I <sub>VDD</sub>                                 | -      | -<br>- | 3.0<br>0.7 | mA   |

| Low V <sub>DD</sub> Detection Voltage <sup>(13)</sup>                                              | <sup>∨</sup> DDDET                               | 1.0    | 1.6    | 2.5        | V    |

| Driver Output ON Resistance (14)                                                                   | R <sub>DS(ON)</sub>                              | _      | 0.8    | 1.2        | Ohms |

| GATE DRIVE                                                                                         |                                                  |        |        |            |      |

| Gate Drive Voltage <sup>(12)</sup> No Current Load                                                 | VCRES                                            | 12     | 13     | 13.5       | V    |

| Gate Drive Ability (Internally Supplied)    C <sub>RES</sub> = -1.0 mA                             | VCRESIoad                                        | 8.5    | 9.2    | _          | V    |

| Recommended External Capacitance (C1L-C1H, C2L-C2H, C <sub>RES</sub> -GND)                         | C <sub>CP</sub>                                  | 0.01   | 0.1    | 1.0        | μF   |

## Notes

- 7. Gate drive voltage  $^{V}C_{RES}$  is generated internally. 2 x  $^{V}DD$  +  $^{V}M$  must be <  $^{V}C_{RES}$  max (13.5 V).

- 8. No internal charge pump used.  ${}^{

m V}{}_{

m CRES}$  is applied from an external source.

- 9.  $R_{DS(ON)}$  is not guaranteed if  $V_{CRES} V_{M} < 5.0 \text{ V}$ . Also, function is not guaranteed if  $V_{CRES} V_{M} < 3.0 \text{ V}$ .

- 10. IQ<sub>VDD</sub> includes the current to pre-driver circuit.

- 11.  ${}^{I}V_{DD}$  includes the current to predriver circuit at  $f_{IN}$  = 100 kHz.

- 12. At  $f_{IN} = 20 \text{ kHz}$ .

- 13. Detection voltage is defined as when the output becomes high-impedance after  $V_{DD}$  drops below the detection threshold.  $^{V}C_{RES}$  is applied from an external source. 2 x  $V_{DD}$  +  $V_{M}$  must be <  $^{V}C_{RES}$  max (13.5 V).

- 14.  $I_O = 0.7 \text{ A source + sink.}$

#### 17531A

## **Table 4. Static Electrical Characteristics (continued)**

Characteristics noted under conditions  $T_A$  = 25°C,  $V_{DD}$  = 3.0 V,  $V_M$  = 5.0 V, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                 | Symbol                 | Min            | Тур | Max                 | Unit |

|------------------------------------------------|------------------------|----------------|-----|---------------------|------|

| CONTROL LOGIC                                  |                        |                |     |                     |      |

| Logic Input Voltage                            | V <sub>IN</sub>        | 0              | _   | $V_{DD}$            | V    |

| Logic Inputs (2.7 V < V <sub>DD</sub> < 3.3 V) |                        |                |     |                     |      |

| High-Level Input Voltage                       | $V_{IH}$               | $V_{DD} x 0.7$ | _   | _                   | V    |

| Low-Level Input Voltage                        | $V_{IL}$               | _              | _   | $V_{DD} \times 0.3$ | V    |

| High-Level Input Current                       | I <sub>IH</sub>        | _              | _   | 1.0                 | μΑ   |

| Low-Level Input Current                        | I <sub>IL</sub>        | -1.0           | _   | -                   | μΑ   |

| PSAVE Terminal Input Current Low               | I <sub>IL</sub> -PSAVE | _              | 50  | 100                 | μΑ   |

## DYNAMIC ELECTRICAL CHARACTERISTICS

## **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions  $T_A$  = 25°C,  $V_{DD}$  = 3.0 V,  $V_M$  = 5.0 V, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                    | Symbol            | Min    | Тур        | Max         | Unit |

|-------------------------------------------------------------------|-------------------|--------|------------|-------------|------|

| INPUT                                                             |                   |        |            |             |      |

| Pulse Input Frequency                                             | f <sub>IN</sub>   | _      | _          | 200         | kHz  |

| Input Pulse Rise Time (15)                                        | t <sub>R</sub>    | -      | -          | 1.0<br>(16) | μs   |

| Input Pulse Fall Time (17)                                        | t <sub>F</sub>    | -      | -          | 1.0<br>(16) | μs   |

| OUTPUT                                                            |                   |        |            |             |      |

| Propagation Delay Time <sup>(18)</sup> Turn-ON Time Turn-OFF Time | t <sub>PLH</sub>  | -<br>- | 0.1<br>0.1 | 0.5<br>0.5  | μs   |

| Charge Pump Wake-Up Time (19)                                     | t <sub>VGON</sub> | -      | 1.0        | 3.0         | ms   |

| Low-Voltage Detection Time                                        | tVDDDET           | _      | _          | 10          | ms   |

#### Notes

- 15. Time is defined between 10% and 90%.

- 16. That is, the input waveform slope must be steeper than this.

- 17. Time is defined between 90% and 10%.

- 18. Output load is 8.0  $\Omega$  DC.

- 19.  $C_{CP} = 0.1 \,\mu F$ .

## **TIMING DIAGRAMS**

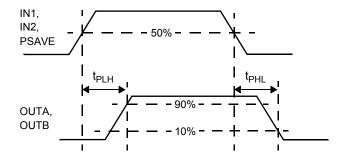

Figure 5.  $t_{PLH}$ ,  $t_{PHL}$ , and  $t_{PZH}$  Timing

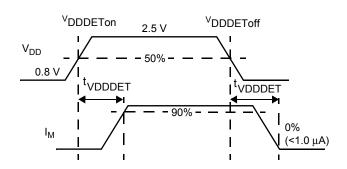

Figure 6. Low-Voltage Detection Timing

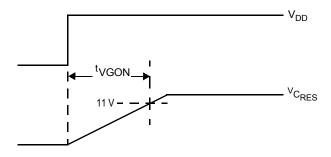

Figure 7. Charge Pump Timing

Table 6. Truth Table

|       | INPUT        |              |                | OUTPUT         |                  |  |

|-------|--------------|--------------|----------------|----------------|------------------|--|

| PSAVE | IN1A<br>IN2A | IN1B<br>IN2B | OUT1A<br>OUT2A | OUT1B<br>OUT2B | Voltage Detector |  |

| L     | L            | L            | L              | L              | RUN              |  |

| L     | Н            | L            | Н              | L              | RUN              |  |

| L     | L            | Н            | L              | Н              | RUN              |  |

| L     | Н            | Н            | Z              | Z              | RUN              |  |

| Н     | Х            | Х            | Z              | Z              | STOP             |  |

H = High.

L = Low.

Z = High impedance.

X = Don't care.

PSAVE terminal is pulled up to  $V_{\mbox{\scriptsize DD}}$  with internal resistance.

## **FUNCTIONAL DESCRIPTION**

## INTRODUCTION

The 17531A is a monolithic dual H-Bridge ideal for portable electronic applications to control bipolar step motors and brush DC motors such as those found in camera len assemblies, camera shutters, and optical disk drives. The device features an on-board charge pump, as well as built-in shoot-through current protection and undervoltage shutdown.

The 17531A has four operating modes: Forward, Reverse, Brake, and Tri-Stated (High Impedance). The MOSFETs comprising the output bridge have a total source + sink  $R_{DS(ON)} \leq$  1.2  $\Omega.$

The 17531A can simultaneously drive two brush DC motors or one bipolar step motor. The drivers are designed to be PWM'ed at frequencies up to 200 kHz.

## **FUNCTIONAL TERMINAL DESCRIPTION**

## LOGIC SUPPLY (VDD)

The  $V_{\rm DD}$  terminal carries the logic supply voltage and current into the logic sections of the IC. VDD has an undervoltage threshold. If the supply voltage drops below the undervoltage threshold, the output power stage switches to a tri-state condition. When the supply voltage returns to a level that is above the threshold, the power stage automatically resumes normal operation according to the established condition of the input terminals.

## LOGIC INPUT CONTROL (IN1A, IN1B, IN2A, AND IN2B)

These logic input terminals control each H-Bridge output. IN1A logic HIGH = OUT1A HIGH. However, if all inputs are taken HIGH, the outputs bridges are both tri-stated (refer to Table  $\underline{6}$ , Truth Table, page  $\underline{9}$ ).

## **POWER SAVE (PSAVE)**

The PSAVE terminal is a HIGH = TRUE power save mode input. When PSAVE = HIGH, all H-Bridge outputs (OUT1A, OUT1B, OUT2A, and OUT2B) are tri-stated (High-Z), regardless of logic inputs (IN1A, IN1B, IN2A, and IN2B) states, and the internal charge pump and low voltage detection current are shut off to save power.

# H-BRIDGE OUTPUT (OUT1A, OUT1B, OUT2A, AND OUT2B)

These terminals provide connection to the outputs of each of the internal H-Bridges (see <u>Figure 2, 17531A Simplified Internal Block Diagram</u>, page  $\underline{2}$ ).

## **MOTOR DRIVE POWER SUPPLY (VM1 AND VM2)**

The VM terminals carry the main supply voltage and current into the power sections of the IC. This supply then becomes controlled and/or modulated by the IC as it delivers the power to the loads attached between the OUTput terminals. All VM terminals must be connected together on the printed circuit board.

## CHARGE PUMP (C1L AND C1H, C2L AND C2H)

These two pairs of terminals, the C1L and C1H and the C2L and C2H, connect to the external bucket capacitors required by the internal charge pump. The typical value for the bucket capacitors is 0.1  $\mu$ F.

## PREDRIVER POWER SUPPLY (CRES)

The CRES terminal is the output of the internal charge pump. Its output voltage is approximately three times of VDD voltage. The VCRES voltage is power supply for the internal predriver circuit of H-Bridges.

## **POWER GROUND (PGND)**

Power ground terminals. They must be tied together on the PCB.

## LOGIC GROUND (LGND)

Logic ground terminal.

## TYPICAL APPLICATIONS

Figure 8 shows a typical application for the 17531A. When applying the gate voltage to the CRES terminal from an external source, be sure to connect it via a resistor equal to, or greater than,  $R_G = {}^{V}C_{RES}/0.02~\Omega$ .

The internal charge pump of this device is generated from the VDD supply; therefore, care must be taken to provide sufficient gate-source voltage for the high-side MOSFETs when  $V_M >> V_{DD}$  (e.g.,  $V_M = 5.0 \text{ V}$ ,  $V_{DD} = 3.3 \text{ V}$ ), in order to ensure full enhancement of the high-side MOSFET channels.

Figure 8. 17531A Typical Application Diagram

#### **CEMF SNUBBING TECHNIQUES**

Care must be taken to protect the IC from potentially damaging CEMF spikes induced when commutating currents in inductive loads. Typical practice is to provide snubbing of voltage transients via placing a capacitor or zener at the supply terminal (VM) (see Figure 9).

#### **PCB LAYOUT**

When designing the printed circuit board (PCB), connect sufficient capacitance between power supply and ground terminals to ensure proper filtering from transients. For all high-current paths, use wide copper traces and shortest possible distances.

Figure 9. CEMF Snubbing Techniques

## **PACKAGING**

## **PACKAGE DIMENSIONS**

$For the most current package revision, visit \underline{\textbf{www.freescale.com}} \ and \ perform \ a \ keyword \ search \ using \ the "98A" \ drawing \ number \ listed \ below.$

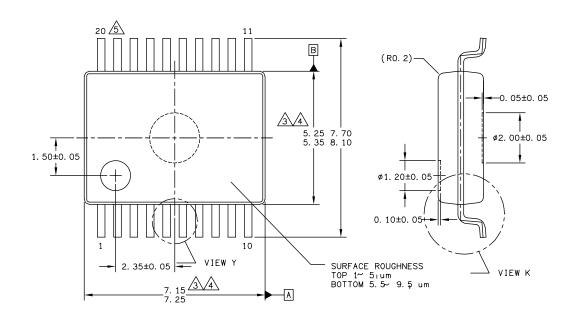

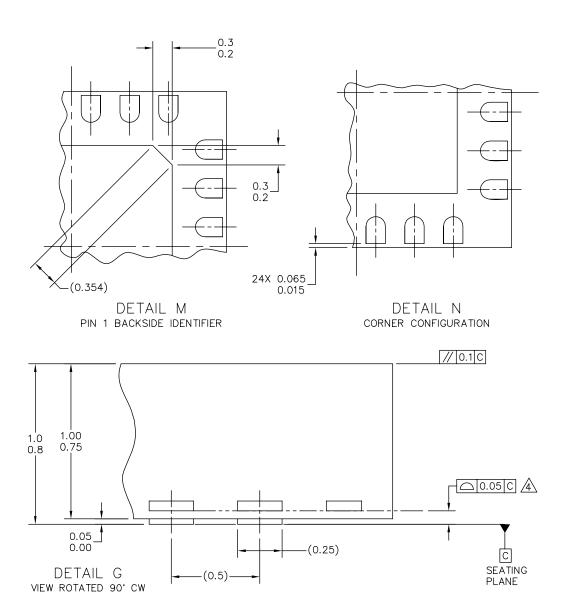

## EV (Pb-FREE) SUFFIX

20-LEAD VMFP PLASTIC PACKAGE 98ASA10816D ISSUE A

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANICA |  | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------------------|--|--------------|------------------|-------------|

| EIAJ VMFP 20LD,<br>0.65 PITCH                                    |  | DOCUMENT NO  | ): 98ASA10616D   | REV: A      |

|                                                                  |  | CASE NUMBER  | R: 1569–01       | 20 JUN 2005 |

|                                                                  |  | STANDARD: NO | N-JEDEC          |             |

EV (Pb-FREE) SUFFIX 20-LEAD VMFP PLASTIC PACKAGE 98ASA10816D ISSUE A

VIEW Y SECTION R-R

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICA |   | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|-----------------------------------------------------------------|---|--------------|------------------|-------------|

| TITLE: EIAJ VMFP 20LD, 0.65 PITCH                               |   | DOCUMENT NO  | ): 98ASA10616D   | REV: A      |

|                                                                 |   | CASE NUMBER  | R: 1569–01       | 20 JUN 2005 |

|                                                                 | • | STANDARD: NO | N-JEDEC          |             |

## EV (Pb-FREE) SUFFIX

20-LEAD VMFP PLASTIC PACKAGE 98ASA10816D **ISSUE A**

#### NOTES:

- 1 DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- ALL DIMENSIONS ARE IN MILLIMETERS.

DIMENSIONS DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0. 10 ANY SIDE. DIMENSIONS DO NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.15 PER SIDE.

DIMENSIONS ARE DETERMINED AT THE OUTMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS, AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

5 TERMINAL NUMBER ARE SHOWN FOR REFERENCE ONLY.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|--------------------|------------------|-------------|

| TITLE:                                               |                    | 0: 98ASA10616D   | REV: A      |

| EIAJ VMFP 20<br>0.65 PITCH                           | . LONGE NIIMBE     | R: 1569–01       | 20 JUN 2005 |

|                                                      | STANDARD: N        | ON-JEDEC         |             |

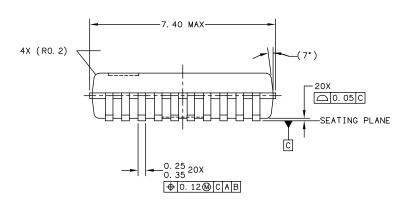

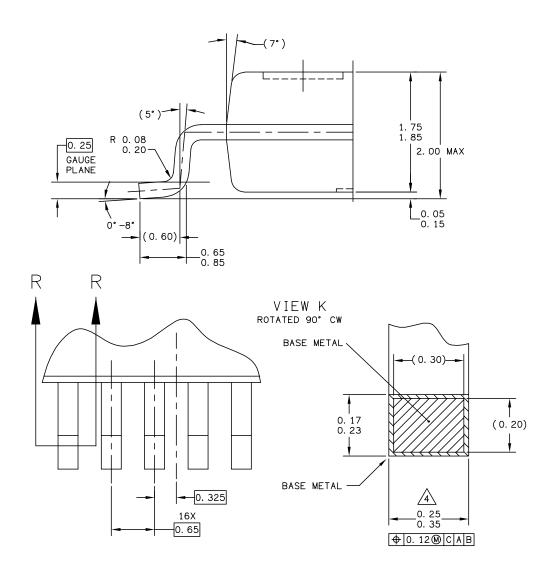

## EP (Pb-FREE) SUFFIX 24-LEAD QFN PLASTIC PACKAGE 98ARL10577D ISSUE A

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA                        | L OUTLINE                | PRINT VERSION NO | T TO SCALE |

|------------------------------------------------------|----------------------------------|--------------------------|------------------|------------|

| TITLE: THERMALLY ENHANCED QUAD                       |                                  | DOCUMENT NO: 98ARL10577D |                  | REV: A     |

| FLAT NON-LEADED PACKAGE                              | CASE NUMBER: 1508-01 03 AUG 2009 |                          |                  |            |

| 24 TERMINAL, 0.5 PITCH (4 X 4 X 1)                   |                                  | STANDARD: NO             | N-JEDEC          |            |

EP (Pb-FREE) SUFFIX 24-LEAD QFN PLASTIC PACKAGE 98ARL10577D ISSUE A

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                            | MECHANICAL OUTLINE |                     | PRINT VERSION NOT TO SCALE |             |

|-------------------------------------------------------------------------------------------------|--------------------|---------------------|----------------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD FLAT NON-LEADED PACKAGE (QFN) 24 TERMINAL, 0.5 PITCH (4 X 4 X 1) |                    | DOCUMENT NO         | ): 98ARL10577D             | REV: A      |

|                                                                                                 |                    | CASE NUMBER         | 2: 1508–01                 | 03 AUG 2005 |

|                                                                                                 |                    | STANDARD: NON-JEDEC |                            |             |

## EP (Pb-FREE) SUFFIX 24-LEAD QFN PLASTIC PACKAGE CASE 1508-01 ISSUE A

## NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFP-N.

4. COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                         | MECHANICA | L OUTLINE            | PRINT VERSION NO | T TO SCALE  |

|-------------------------------------------------------------------------------------------------|-----------|----------------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD FLAT NON-LEADED PACKAGE (QFN) 24 TERMINAL, 0.5 PITCH (4 X 4 X 1) |           | DOCUMENT NO          | ): 98ARL10577D   | REV: A      |

|                                                                                                 |           | CASE NUMBER: 1508-01 |                  | 03 AUG 2005 |

|                                                                                                 |           | STANDARD: NON-JEDEC  |                  |             |

## **REVISION HISTORY**

| REVISION | DATE   | DESCRIPTION OF CHANGES                                                                    |

|----------|--------|-------------------------------------------------------------------------------------------|

| 2.0      | 9/2005 | <ul><li>Implemented Revision History page</li><li>Converted to Freescale format</li></ul> |

| 3.0      | 2/2008 | Corrected Table 2, Pin Definitions on page 4.                                             |

| 4.0      | 5/2009 | Corrected Note 7, in Static Electrical Characteristics table.                             |

#### How to Reach Us:

#### **Home Page:**

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

## Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or +1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2009. All rights reserved.

MPC17531A Rev. 4.0 5/2009