T-46-35

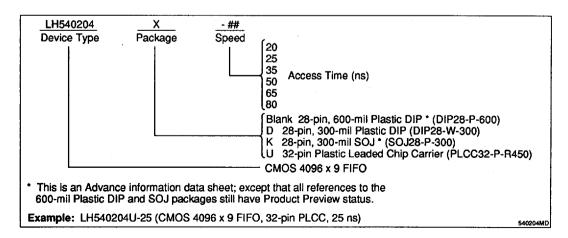

# LH540204

## ADVANCE INFORMATION

CMOS 4096 × 9 Asynchronous FIFO

#### **FEATURES**

- Fast Access Times: 20/25/35/50/65/80 ns

- Fast-Fall-Through Time Architecture Based on CMOS Dual-Port SRAM Technology

- Input Port and Output Port Have Entirely Independent Timing

- Expandable in Width and Depth

- Full, Half-Full, and Empty Status Flags

- Data Retransmission Capability

- TTL-Compatible I/O

- Pin and Functionally Compatible with Sharp LH5499 and with Am/IDT/MS7204

- Control Signals Assertive-LOW for Noise Immunity

- Packages:

28-Pin, 300-mil PDIP

28-Pin, 600-mil PDIP \*

28-Pin, 300-mil SOJ \*

32-Pin, 300-mil PLCC

#### PIN CONNECTIONS

| 28-PIN PDIP  |                     |                     | TOP VIEW  |

|--------------|---------------------|---------------------|-----------|

| 28-PIN SOJ * | ₩ 🗖 1 🌢             | 28 □ V <sub>∞</sub> |           |

|              | D <sub>8</sub> 🗖 2  | 27 🗖 ◘₄             |           |

|              | D₃ □ 3              | 26 🗖 D₅             |           |

|              | D <sub>2</sub> 🗖 4  | 25 🗆 D <sub>6</sub> |           |

|              | D <sub>1</sub> 🗖 5  | 24 🗖 D7             |           |

|              | ₽₀ 🗖 6              | 23 🗀 FT/RT          |           |

|              | ᄁᅜ                  | 22 🗖 🗟              |           |

|              | FF □ 8              | 21 T 🛱              |           |

|              | ಎ,⊏!೨               | 20 XO/HF            |           |

|              | Q₁ <b>□</b> 10      | 19 🗖 🔾              |           |

|              | Q₂ ☐11              | 18 🗖 🔾 6            |           |

|              | Q₃ □12              | 17 □ Q <sub>5</sub> |           |

|              | <b>Q</b> ₀ □13      | 16 □ Q₄             |           |

|              | V <sub>S8</sub> □14 | 15 🗖 🛱              |           |

|              |                     |                     | 540204-2D |

Figure 1. Pin Connections for PDIP \* and SOJ \* Packages

#### **FUNCTIONAL DESCRIPTION**

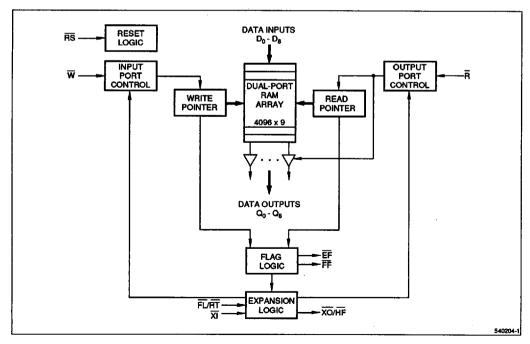

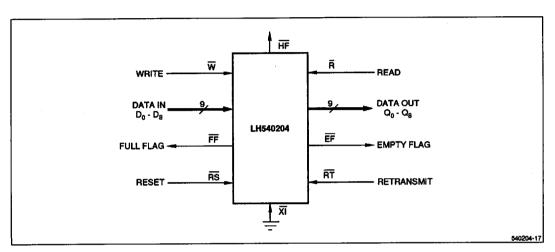

The LH540204 is a FIFO (First-In, First-Out) memory device, based on fully-static CMOS dual-port SRAM technology, capable of storing up to 4096 nine-bit words. It follows the industry-standard architecture and package pinouts for nine-bit asynchronous FIFOs. Each nine-bit LH540204 word may consist of a standard eight-bit byte, together with a parity bit or a block-marking/framing bit.

The input and output ports operate entirely independently of each other, unless the LH540204 becomes either totally full or else totally empty. Data flow at a port is initiated by asserting either of two asynchronous, assertive-LOW control inputs: Write  $(\overline{W})$  for data entry at the input port, or Read  $(\overline{R})$  for data retrieval at the output port.

Full, Half-Full, and Empty status flags monitor the extent to which the internal memory has been filled. The system may make use of these status outputs to avoid the risk of data loss, which otherwise might occur either by attempting to write additional words into an already-full LH540204, or by attempting to read additional words from an already-empty LH540204. When an LH540204 is operating in a depth-cascaded configuration, the Half-Full Flag is not available.

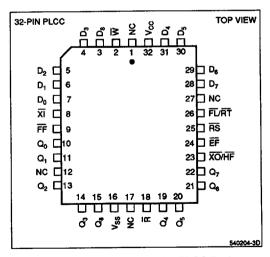

Figure 2. Pin Connections for PLCC Package

<sup>\*</sup> This is an Advance Information data sheet; except that all references to the 600-mil PDIP and SOJ packages still have Product Preview status.

T-46-35

LH540204

#### **FUNCTIONAL DESCRIPTION (cont'd)**

Data words are read out from the LH540204's output port in precisely the same order that they were written in at its input port; that is, according to a First-In, First Out (FIFO) queue discipline. Since the addressing sequence for a FIFO device's memory is internally predefined, no external addressing information is required for the operation of the LH540204 device.

Drop-in-replacement compatibility is maintained with both larger sizes and smaller sizes of industry-standard nine-bit asynchronous FIFOs. The only change is in the number of internally-stored data words implied by the states of the Full Flag and the Half-Full Flag.

The Retransmit (RT) control signal causes the internal FIFO-memory-array read-address pointer to be set back to zero, to point to the LH540204's first physical memory location, without affecting the internal FIFO-memory-array write-address pointer. Thus, the Retransmit control signal provides a mechanism whereby a block of data, delimited by the zero physical address and the current write-address-pointer value, may be read out repeatedly an arbitrary number of times. The only restrictions are that neither the read-address pointer nor the write-address pointer may 'wrap around' during this entire process, i.e., advance past physical location zero after traversing the entire memory. The retransmit facility is not available

when an LH540204 is operating in a depth-expanded configuration.

The Reset (RS) control signal returns the LH540204 to an initial state, empty and ready to be filled. An LH540204 should be reset during every system power-up sequence. A reset operation causes the internal FIFO-memory-array write-address pointer, as well as the read-address pointer, to be set back to zero, to point to the LH540204's first physical memory location. Any information which previously had been stored within the LH540204 is not recoverable after a reset operation.

A cascading (depth-expansion) scheme may be implemented by using the Expansion In (XI) input signal and the Expansion Out (XO/HF) output signal. This scheme allows a deeper 'effective FIFO' to be implemented by using two or more individual LH540204 devices, without incurring additional latency ('fallthrough' or 'bubblethrough') delays, and without the necessity of storing and retrieving any given data word more than once. In this cascaded operating mode, one LH540204 device must be designated as the 'first-load' or 'master' device. by grounding its First-Load (FL/RT) control input: the remaining LH540204 devices are designated as 'slaves,' by tying their FL/RT inputs HIGH. Because of the need to share control signals on pins, the Half-Full Flag and the retransmission capability are not available for either 'master' or 'slave' LH540204 devices operating in cascaded mode.

Figure 3. LH540204 Block Diagram

#### PIN DESCRIPTIONS

| PIN                             | PIN TYPE * | DESCRIPTION     |

|---------------------------------|------------|-----------------|

| D <sub>0</sub> – D <sub>8</sub> | _          | Input Data Bus  |

| Q <sub>0</sub> - Q <sub>8</sub> | O/Z        | Output Data Bus |

| W                               | 1          | Write Request   |

| R                               | ı          | Read Request    |

| EF                              | 0          | Empty Flag      |

| FF                              | 0          | Full Flag       |

<sup>\*</sup> I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

#### T-46-35

| PIN   | PIN TYPE * | DESCRIPTION                  |

|-------|------------|------------------------------|

| XO/HF | 0          | Expansion Out/Half-Full Flag |

| ΧĪ    | ı          | Expansion In                 |

| FL/RT | 1          | First Load/Retransmit        |

| RS    | ı          | Reset                        |

| Vcc   | ٧          | Positive Power Supply        |

| Vss   | V          | Ground                       |

#### **OPERATIONAL DESCRIPTION**

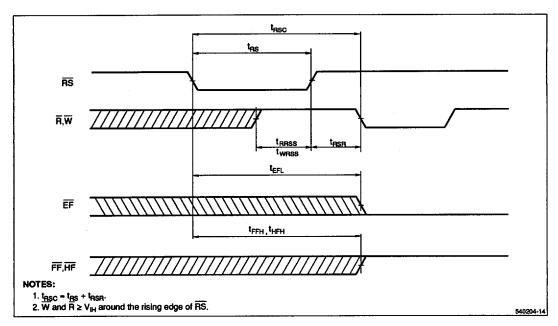

#### Reset

The LH540204 is reset whenever the Reset input (RS) is taken LOW. A reset operation initializes both the read-address pointer and the write-address pointer to point to location zero, the first physical memory location. During a reset operation, the state of the XI and FL/RT inputs determines whether the device is in standalone mode or in depth-cascaded mode. (See Tables 1 and 2.)

A reset operation is required whenever the LH540204 first is powered up. The Read  $(\overline{R})$  and Write  $(\overline{W})$  inputs may be in any state when the reset operation is initiated; but they must be HIGH, before the reset operation is terminated by a rising edge of  $\overline{RS}$ , by a time transs (for Read) or twass (for Write) respectively. (See Figure 10.)

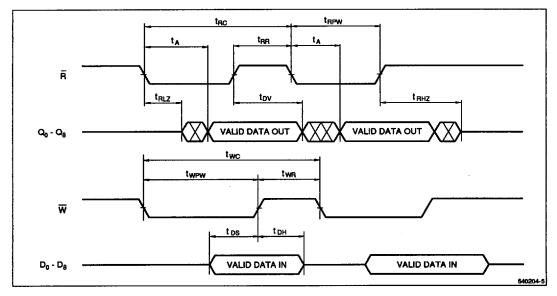

#### Write

A write cycle is initiated by a falling edge of the Write (W) control input. Data setup times and hold times must be observed for the data inputs (Do – Da). Write operations may occur independently of any ongoing read operations. However, a write operation is possible only if the FIFO is not full, (i.e., if the Full Flag FF is HIGH).

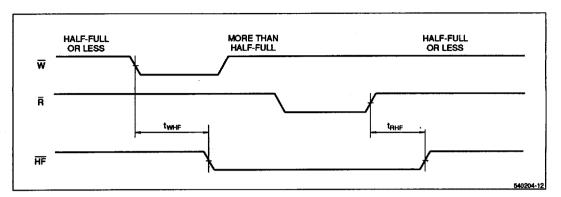

At the falling edge of  $\overline{W}$  for the first write operation after the memory is half filled, the Half-Full Flag is asserted ( $\overline{HF}$  = LOW). It remains asserted until the difference between the write pointer and the read pointer indicates that the data words remaining in the LH540204 are filling the FIFO memory to less than or equal to one-half of its total capacity. The Half-Full Flag is deasserted ( $\overline{HF}$  = HIGH) by the appropriate rising edge of  $\overline{R}$ . (See Table 3.)

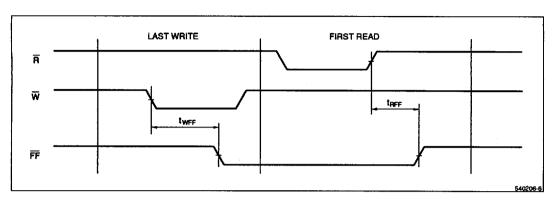

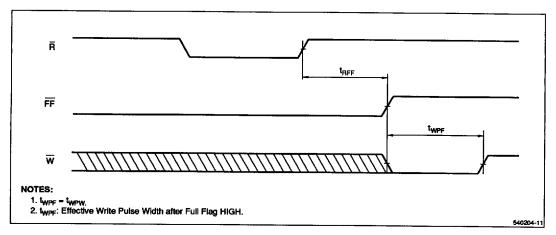

The Full Flag is asserted ( $\overline{FF}$  = LOW) at the falling edge of  $\overline{W}$  for the write operation which fills the last available location in the FIFO memory array.  $\overline{FF}$  = LOW inhibits further write operations until  $\overline{FF}$  is cleared by a valid read operation. The Full Flag is deasserted ( $\overline{FF}$  = HIGH) after the next rising edge of  $\overline{R}$  releases another memory location. (See Table 3.)

#### Read

A read cycle is initiated by a falling edge of the Read  $(\overline{R})$  control input. Read data becomes valid at the data outputs  $(Q_0 - Q_8)$  after a time  $t_A$  from the falling edge of  $\overline{R}$ . After  $\overline{R}$  goes HIGH, the data outputs return to a high-impedance state. Read operations may occur independently of any ongoing write operations. However, a read operation is possible only if the FIFO is not empty (i.e., if the Empty Flag  $\overline{EF}$  is HIGH).

The LH540204's internal read-address and write-address pointers operate in such a way that consecutive read operations always access data words in the same order that they were written. The Empty Flag is asserted ( $\overline{\text{EF}}$  = LOW) after that falling edge of  $\overline{\text{R}}$  which accesses the last available data word in the FIFO memory.  $\overline{\text{EF}}$  is deasserted ( $\overline{\text{EF}}$  = HIGH) after the next rising edge of  $\overline{\text{W}}$  loads another valid data word. (See Table 3.)

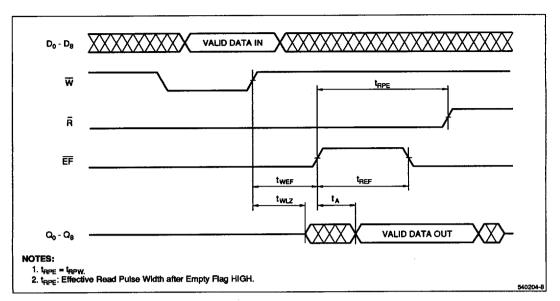

#### **Data Flow-Through**

Read-data flow-through mode occurs when the Read  $(\overline{R})$  control input is brought LOW while the FIFO is empty, and is held LOW in anticipation of a write cycle. At the end of the next write cycle, the Empty Flag  $\overline{EF}$  momentarily is deasserted, and the data word just written becomes available at the data outputs  $(Q_0 - Q_8)$  after a maximum time of twef+ ta. Additional write operations may occur while the  $\overline{R}$  input remains LOW; but only data from the first write operation flows through to the data outputs. Additional data words, if any, may be accessed only by togoling  $\overline{R}$ .

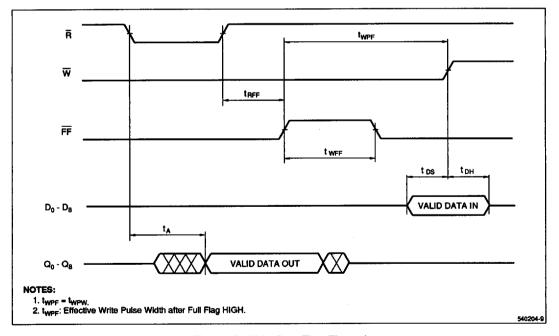

Write-data flow-through mode occurs when the Write  $(\overline{W})$  input is brought LOW while the FIFO is full, and is held LOW in anticipation of a read cycle. At the end of the read cycle, the Full Flag momentarily is deasserted, but then immediately is reasserted in response to  $\overline{W}$  being held LOW. A data word is written into the FIFO on the rising edge of  $\overline{W}$ , which may occur no sooner than the three types after the read operation.

T - 46 - 35

LH540204

## OPERATIONAL DESCRIPTION (cont'd)

#### Retransmit

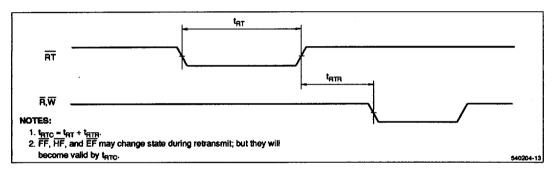

The FIFO can be made to reread previously-read data by means of the Retransmit function. A retransmit operation is initiated by pulsing the RT input LOW. Both R and W must be deasserted (HIGH) for the duration of the retransmit pulse. The FIFO's internal read-address pointer is reset to point to location zero, the first physical memory location, while the internal write-address pointer remains unchanged.

After a retransmit operation, those data words in the region in between the read-address pointer and the write-address pointer may be reaccessed by subsequent read operations. A retransmit operation may affect the state of the status flags FF, HF, and EF, depending on the relocation of the read-address pointer. There is no restriction on the number of times that a block of data within an LH540204 may be read out, by repeating the retransmit operation and the subsequent read operations.

The maximum length of a data block which may be retransmitted is 4096 words. Note that if the write-address pointer ever 'wraps around' (i.e., passes location zero more than once) during a sequence of retransmit operations, some data words will be lost.

The Retransmit function is not available when the LH540204 is operating in depth-cascaded mode. because the FL/RT control pin must be used for first-load selection rather than for retransmission control.

Table 1. Grouping-Mode Determination **During a Reset Operation**

|                |    |                                 | •              |             |                |  |

|----------------|----|---------------------------------|----------------|-------------|----------------|--|

| Χī             | FL | MODE                            | XO/HF<br>USAGE | XI<br>USAGE | FL/RT<br>USAGE |  |

| H ¹            | Н  | Cascaded<br>Slave <sup>2</sup>  | xo             | ΧI          | FL             |  |

| H <sup>1</sup> | L  | Cascaded<br>Master <sup>2</sup> | ΧO             | Χī          | FL             |  |

| L              | Х  | Standalone                      | HF             | (none)      | RT             |  |

#### NOTES:

- 1. A reset operation forces XO HIGH for the nth FIFO, thus forcing XI HIGH for the n+1st FIFO.

- 2. The terms 'master' and 'slave' refer to operation in depth-cascaded grouping mode.

- 3. H = HiGH; L = LOW; X = Don't Care.

Table 2. Expansion-Pin Usage According to **Grouping Mode**

| vo | PIN   | STANDALONE    | CASCADED<br>MASTER         | CASCADED<br>SLAVE          |

|----|-------|---------------|----------------------------|----------------------------|

| ı  | ΧI    | Grounded      | From XO<br>(n-1st<br>FIFO) | From XO<br>(n-1st<br>FIFO) |

| 0  | XO/HF | Becomes<br>HF | To XI<br>(n+1st<br>FIFO)   | To XI<br>(n+1st<br>FIFO)   |

| ı  | FL/RT | Becomes<br>RT | Grounded<br>(Logic<br>LOW) | Logic<br>HIGH              |

Table 3. Status Flags

| NUMBER OF UNREAD DATA<br>WORDS PRESENT WITHIN<br>4096 × 9 FIFO | FF | HF | EF |

|----------------------------------------------------------------|----|----|----|

| 0                                                              | Н  | Н  | L  |

| 1 to 2048                                                      | Н  | Н  | Н  |

| 2049 to 4095                                                   | Н  | L  | Н  |

| 4096                                                           | L  | L  | Н  |

CMOS  $4096 \times 9$  Asynchronous FIFO

#### **OPERATIONAL MODES**

#### **Standalone Configuration**

When depth cascading is not required for a given application, the LH540204 is placed in standalone mode by tying the Expansion In input  $(\overline{XI})$  to ground. This input is internally sampled during a reset operation. (See Table 1.)

#### Width Expansion

T-46-35

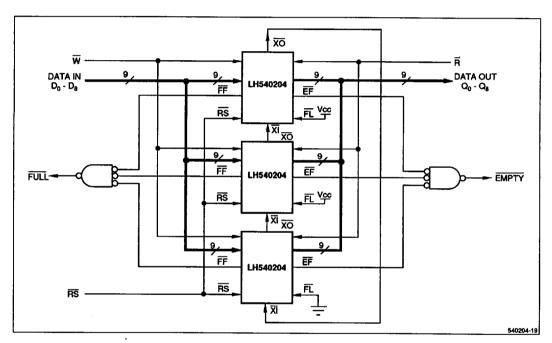

Word-width expansion is implemented by placing multiple LH540204 devices in parallel. Each LH540204 should be configured for standalone mode. In this arrangement, the behavior of the status flags is identical for all devices; so, in principle, a representative value for each of these flags could be derived from any one device. In practice, it is better to derive 'composite' flag values using external logic, since there may be minor speed variations between different actual devices. (See Figures 4, 5, and 6.)

Figure 4. Standalone FIFO (4096 × 9)

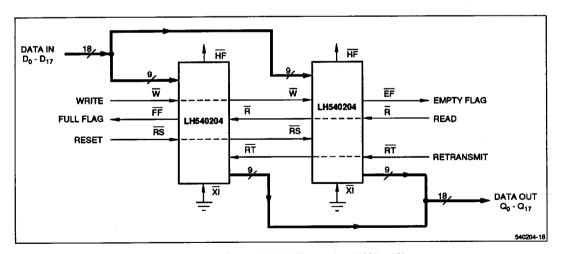

Figure 5. FIFO Word-Width Expansion (4096 × 18)

T-46-35

LH540204

## **OPERATIONAL MODES (cont'd)**

#### Depth Cascading

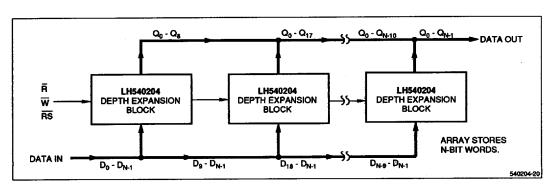

Depth cascading is implemented by configuring the required number of LH540204s in depth-cascaded mode. In this arrangement, the FIFOs are connected in a circular fashion, with the Expansion Out output  $(\overline{XO})$  of each device tied to the Expansion In input  $(\overline{XI})$  of the next device. One FIFO in the cascade must be designated as the 'first-load' device, by tying its First Load input  $(\overline{FL/RT})$  to ground. All other devices must have their  $\overline{FL/RT}$  inputs tied HIGH. In this mode,  $\overline{W}$  and  $\overline{R}$  signals are shared by all devices, while logic within each LH540204 controls the steering of data. Only one LH540204 is enabled during any given write cycle; thus, the common Data In inputs of

all devices are tied together. Likewise, only one LH540204 is enabled during any given read cycle; thus, the common Data Out outputs of all devices are wire-ORed together.

In depth-cascaded mode, external logic should be used to generate a composite Full Flag and a composite Empty Flag, by ANDing the  $\overline{FF}$  outputs of all LH540204 devices together and ANDing the  $\overline{EF}$  outputs of all devices together. Since  $\overline{FF}$  and  $\overline{EF}$  are assertive-LOW signals, this 'ANDing' actually is implemented using an assertive-HIGH physical OR gate. The Half-Full Flag and the Retransmit function are not available in depth-cascaded mode.

Figure 6. FIFO Depth Cascading (12288 × 9)

#### **OPERATIONAL MODES (cont'd)**

#### **Compound FIFO Expansion**

A combination of word-width expansion and depth cascading may be implemented easily by operating groups of depth-cascaded FIFOs in parallel.

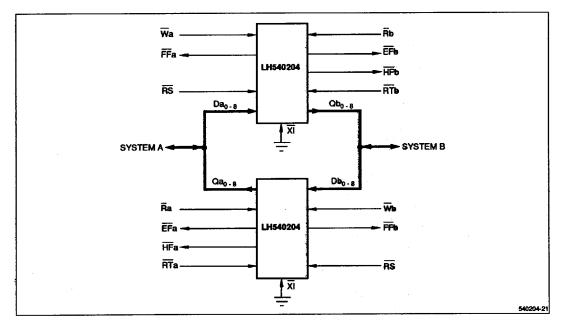

#### **Bidirectional FIFO Operation**

Bidirectional data buffering between two systems may be implemented by operating LH540204 devices in parallel, but in opposite directions. The Data In inputs of each LH540204 are tied to the corresponding Data Out outputs of another LH540204, which is operating in the opposite direction, to form a single bidirectional bus interface. Care must be taken to assure that the appropriate read, write, and flag signals are routed to each system. Both wordwidth expansion and depth cascading may be used in bidirectional applications.

$$T-46-35$$

Figure 7. Compound FIFO Expansion

Figure 8. Bidirectional FIFO Operation  $(4096 \times 9 \times 2)$

LH540204

#### ABSOLUTE MAXIMUM RATINGS 1

#### T-46-35

| PARAMETER                                     | RATING                                    |

|-----------------------------------------------|-------------------------------------------|

| Supply Voltage to Vss Potential               | -0.5 V to 7 V                             |

| Signal Pin Voltage to Vss Potential 2         | -0.5 V to Vcc + 0.5 V (not to exceed 7 V) |

| DC Output Current <sup>3</sup>                | ± 50 mA                                   |

| Storage Temperature Range                     | -65°C to 150°C                            |

| Power Dissipation (Package Limit)             | 1.0 W                                     |

| DC Voltage Applied to Outputs In High-Z State | -0.5 V to Vcc + 0.5 V (not to exceed 7 V) |

#### NOTES:

- Stresses greater than those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. This is a stress rating for transient conditions only. Functional operation of the device at these or any other conditions outside of those indicated in the 'Operating Range' of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Negative undershoots of 1.5 V in amplitude are permitted for up to 10 ns once per cycle.

- 3. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

#### **OPERATING RANGE**

| SYMBOL             | PARAMETER                 | MIN  | MAX       | UNIT |

|--------------------|---------------------------|------|-----------|------|

| TA                 | Temperature, Ambient      | 0    | 70        | °C   |

| Vcc                | Supply Voltage            | 4.5  | 5.5       | v    |

| Vss Supply Voltage |                           | 0    | 0         | V    |

| VIL                | Logic LOW Input Voltage 1 | -0.5 | 0.8       | ٧    |

| VIH                | Logic HIGH Input Voltage  | 2.0  | Vcc + 0.5 | ٧    |

#### NOTES:

### DC ELECTRICAL CHARACTERISTICS (Over Operating Range)

| SYMBOL      | PARAMETER                 | TEST CONDITIONS               | MIN | MAX | UNIT |  |

|-------------|---------------------------|-------------------------------|-----|-----|------|--|

| l <u>Li</u> | Input Leakage Current     | Vcc = 5.5 V, VIN = 0 V to Vcc | -10 | 10  |      |  |

| اله         | Output Leakage Current    | R ≥ VIH, 0 V ≤ VOUT ≤ VCC     | -10 | 10  | μА   |  |

| Vон         | Output HIGH Voltage       | IOH = −2.0 mA                 | 2.4 |     | ٧    |  |

| VoL         | Output LOW Voltage        | loL = 8.0 mA                  |     | 0.4 | V    |  |

| lcc         | Average Supply Current 1  | Measured at f = 40 MHz        |     | 110 | mA   |  |

| Icc2        | Average Standby Current 1 | All Inputs = ViH              |     | 15  | mA   |  |

| Іссз        | Power Down Current 1      | All Inputs = Vcc - 0.2V       |     | 8   | mA   |  |

#### NOTES:

1. Icc, Icc2, and Icc3 are dependent upon actual output loading and cycle rates. Specified values are with outputs open.

<sup>1.</sup> Negative undershoots of 1.5 V in amplitude are permitted for up to 10 ns once per cycle.

CMOS 4096 × 9 Asynchronous FIFO

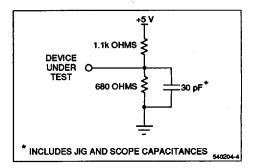

#### **AC TEST CONDITIONS**

| PARAMETER                              | RATING     |

|----------------------------------------|------------|

| Input Pulse Levels                     | Vss to 3 V |

| Input Rise and Fall Times (10% to 90%) | 5 ns       |

| Input Timing Reference Levels          | 1.5 V      |

| Output Reference Levels                | 1.5 V      |

| Output Load, Timing Tests              | Figure 9   |

## CAPACITANCE 1,2

| PARAMETER                   | RATING |

|-----------------------------|--------|

| CIN MAX (Input Capacitance) | 5 pF   |

| Co MAX (Output Capacitance) | 7 pF   |

## T-46-35

Figure 9. Output Load Circuit

#### NOTES:

- 1. Sample tested only.

- 2. Capacitances are maximum values at 25°C, measured at 1.0MHz, with  $V_{\text{IN}}$  = 0 V.

CMOS 4096 × 9 Asynchronous FIFO

**ADVANCE INFORMATION**

LH540204

## AC ELECTRICAL CHARACTERISTICS) 1 (Over Operating Range)

T-46-35

| ta<br>tar<br>tapw   | PARAMETER  Read Cycle Time Access Time Read Recovery Time |    | MAX               | MIN    | 25 ns<br>MAX |                | 35 ns<br>MAX |    | 50 ns |    | 65 ns    |     | 80 ns          | UNIT |  |

|---------------------|-----------------------------------------------------------|----|-------------------|--------|--------------|----------------|--------------|----|-------|----|----------|-----|----------------|------|--|

| ta<br>trir<br>tripw | Access Time                                               |    | READ              | AVA.   |              |                |              |    |       |    |          |     |                |      |  |

| ta<br>tar<br>tapw   | Access Time                                               |    | READ CYCLE TIMING |        |              |                |              |    |       |    |          |     |                |      |  |

| ter<br>terw         |                                                           |    | _                 | 35     | _            | 45             | _            | 65 | _     | 80 | Τ_       | 100 | 1 =            | ns   |  |

| t <sub>RPW</sub>    | Read Recovery Time                                        | _  | 20                | -      | 25           | _              | 35           | -  | 50    | _  | 65       |     | 80             | ns   |  |

| t <sub>RLZ</sub>    | TIOGO TIOCOVOLY TILLIO                                    | 10 | -                 | 10     | _            | 10             | -            | 15 | -     | 15 | -        | 15  |                | ns   |  |

|                     | Read Pulse Width 2                                        | 20 | -                 | 25     | _            | 35             | _            | 50 | -     | 65 | <u> </u> | 80  |                | ns   |  |

|                     | Data Bus Active from Read LOW <sup>3</sup>                | 5  | _                 | 5      | -            | 5              |              | 5  |       | 5  | _        | 10  | <del>  _</del> | ns   |  |

| twiz                | Data Bus Active from Write HIGH 3,4                       | 10 | -                 | 10     | _            | 10             |              | 10 | _     | 10 | _        | 20  | _              | ns   |  |

|                     | Data Held Valid from Read Pulse<br>HIGH                   | 5  | -                 | 5      | _            | 5              | -            | 5  | -     | 5  | -        | 5   | _              | ns   |  |

| trinz               | Data Bus High-Z from Read HIGH 3                          | _  | 15                | _      | 15           | _              | 15           | _  | 20    | _  | 30       |     | 30             | ns   |  |

|                     |                                                           | W  | /RITE             | CYCL   | E TIMI       | NG             |              |    |       |    |          |     |                | 113  |  |

| two                 | Write Cycle Time                                          | 30 |                   | 35     | _            | 45             | T - 1        | 65 | I -   | 80 |          | 100 | Γ <u>-</u>     | ns   |  |

|                     | Write Pulse Width 2                                       | 20 | _                 | 25     | _            | 35             | _            | 50 | _     | 65 | _        | 80  | _              | ns   |  |

| twa                 | Write Recovery Time                                       | 10 | _                 | 10     |              | 10             | _            | 15 | _     | 15 | _        | 15  | _              | ns   |  |

|                     | Data Setup Time                                           | 10 | -                 | 10     | _            | 15             |              | 20 | _     | 20 | _        | 20  | _              | ns   |  |

| t <sub>DH</sub>     | Data Hold Time                                            | 0  | _                 | 0      | _            | 0              | - 1          | 0  | _     | 5  | _        | 5   | _              | ns   |  |

|                     |                                                           |    | RES               | ET TII | MING         |                |              |    | اا    |    |          |     |                | 113  |  |

| trsc                | Reset Cycle Time                                          | 30 | -                 | 35     | _            | 45             | - 1          | 65 | _     | 80 | _        | 100 | _              | ns   |  |

|                     | Reset Pulse Width <sup>2</sup>                            | 20 | _                 | 25     | _            | 35             | _            | 50 |       | 65 | _        | 80  | _              | ns   |  |

| trsr                | Reset Recovery Time                                       | 10 | -                 | 10     | -            | 10             | _            | 15 | _     | 15 | _        | 15  |                | ns   |  |

|                     | Read HIGH to RS HIGH                                      | 20 | _                 | 25     | _            | 35             | _            | 50 | _     | 65 |          | 80  | -              | ns   |  |

| twess \             | Write HIGH to RS HIGH                                     | 20 | -                 | 25     |              | 35             | _            | 50 | _     | 65 |          | 80  | _              | ns   |  |

|                     |                                                           | RI | ETRAN             | ISMIT  | TIMIN        | G <sup>5</sup> |              |    |       |    |          |     |                | 110  |  |

| terc I              | Retransmit Cycle Time                                     | 30 | _                 | 35     | _            | 45             | _            | 65 | _     | 80 |          | 100 | _ 1            | ns   |  |

| ter I               | Retransmit Pulse Width 2                                  | 20 | -                 | 25     | _            | 35             | _            | 50 | _     | 65 |          | 80  |                | ns   |  |

| tere f              | Retransmit Recovery Time                                  | 10 | -                 | 10     | _            | 10             | _            | 15 | _     | 15 | _        | 15  |                | ns   |  |

|                     |                                                           |    | FL/               | G TIM  | ING          |                |              |    |       |    |          |     |                | 110  |  |

| teru F              | Reset LOW to Empty Flag LOW                               |    | 30                | _      | 35           |                | 45           | _  | 65    | _  | 80       |     | 100            | ns   |  |

| tuen een   F        | Reset HIGH to Half-Full and Full<br>Flags HIGH            | -  | 30                | -      | 35           | -              | 45           |    | 65    | _  | 80       | _   | 100            | ns   |  |

| tree F              | Read LOW to Empty Flag LOW                                | -  | 20                | _      | 25           | _              | 35           | _  | 45    |    | 60       | _   | 60             | ns   |  |

|                     | Read HIGH to Full Flag HIGH                               | _  | 20                | _      | 25           | _              | 35           | _  | 45    |    | 60       |     | 60             | ns   |  |

|                     | Write HIGH to Empty Flag HIGH                             | _  | 20                | _      | 25           | _              | 35           |    | 45    |    | 60       | -   | 60             | ns   |  |

|                     | Write LOW to Full Flag LOW                                | _  | 20                |        | 25           | _              | 35           |    | 45    |    | 60       | =+  | 60             | ns   |  |

|                     | Write LOW to Half-Full Flag LOW                           | _  | 20                | _      | 25           |                | 35           | _  | 45    |    | 60       |     | 60             | ns   |  |

|                     | Read HIGH to Half-Full Flag HIGH                          | _  | 20                | _      | 25           | -              | 35           | _  | 45    |    | 60       | _   | 60             | ns   |  |

|                     |                                                           | E  |                   | SION   |              |                |              |    |       | !  |          |     | -00            | 113  |  |

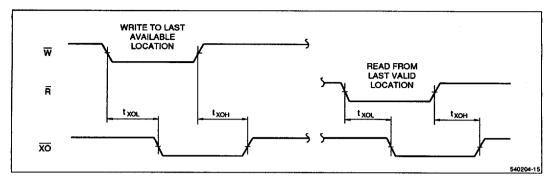

| txoL E              | Expansion Out LOW                                         |    | 20                | -      | 25           | <u>-</u>       | 35           |    | 50    |    | 65       |     | 80             | ns   |  |

|                     | Expansion Out HIGH                                        | _  | 20                |        | 25           |                | 35           |    | 50    |    | 65       | -   | 80             | ns   |  |

|                     | Expansion In Pulse Width                                  | 20 | -                 | 25     | -            | 35             | -            | 50 |       | 65 | -        | 80  |                | ns   |  |

| t <sub>XIR</sub> E  | Expansion in Recovery Time                                | 10 |                   | 10     | -1           | 10             |              | 10 | _     | 10 |          | 10  |                | ns   |  |

|                     | Expansion in Setup Time                                   | 10 | _                 | 10     | _            | 15             |              | 15 |       | 15 |          | 15  | =              | ns   |  |

#### NOTES:

- 1. All timing measurements are performed at 'AC Test Condition' levels.

- 2. Pulse widths less than minimum value are not allowed.

- 3. Values are guaranteed by design; not currently tested.

- 4. Only applies to read-data flow-through mode.

- 5. See also Note 2, Figure 19.

#### **TIMING DIAGRAMS**

Figure 10. Reset Timing

Figure 11. Asynchronous Write and Read Operation

LH540204

## TIMING DIAGRAMS (cont'd)

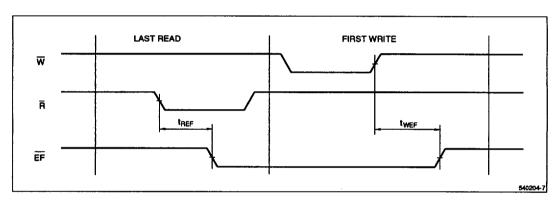

Figure 12. Full Flag From Last Write to First Read

Figure 13. Empty Flag From Last Read to First Write

TIMING DIAGRAMS (cont'd)

Figure 14. Read Data Flow-Through

Figure 15. Write Data Flow-Through

## TIMING DIAGRAMS (cont'd)

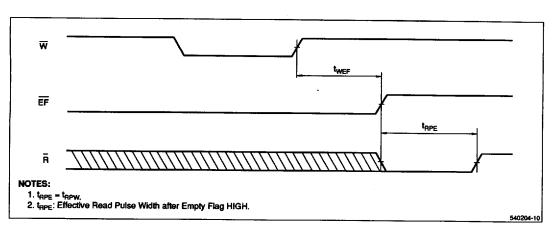

Figure 16. Empty Fiag Timing

Figure 17. Full Flag Timing

LH540204

## **TIMING DIAGRAMS (cont'd)**

Figure 18. Half-Full Flag Timing

Figure 19. Retransmit Timing

LH540204

## **TIMING DIAGRAMS (cont'd)**

Figure 20. Expansion-Out Timing

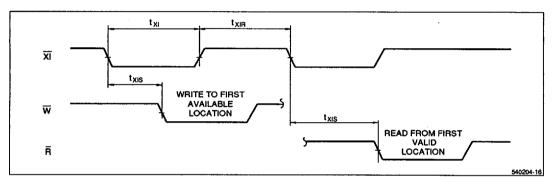

Figure 21. Expansion-In Timing

#### ORDERING INFORMATION