# HD74HC Series Common Information

# HITACHI

September 2000

Customer Service Division Semiconductor & Integrated Circuits Hitachi, Ltd.

#### Disclaimer

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

## Features of High-Speed CMOS Logic

Hitachi's HS-CMOS logics-the HD74HC series-and the HCT series based on the EIA/JEDEC specification. Their specification are shown in the Maximum Ratings and the Electrical Characteristics Tables. The HS-CMOS has the characteristics of both standard CMOS logic series and LS-TTL series.

The features of this logic are:

- High-Speed equivalent to the LS-TTL's

- Capable of driving 10LS-TTL loads (Capable of driving 15LS-TTL loads in bus drivers)

- Maximum input current of  $\pm 1 \mu A$  at 6 V power supply

- Wide supply voltage range: HC series 2 to 6 V

HCT series 4.5 to 5.5 V

- Wide noise margin

- V<sub>CC</sub> assurance of Electrical Characteristics at 2.0, 4.5 and 6.0 V

- Low Static Power Consumption 1/2 of EIA/JEDEC

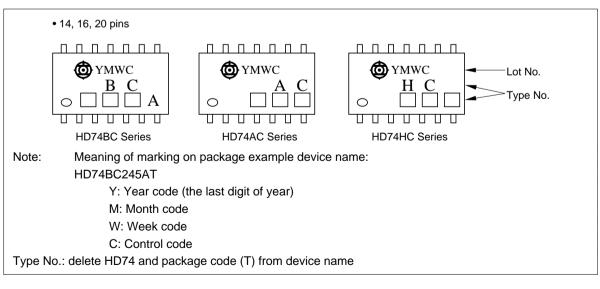

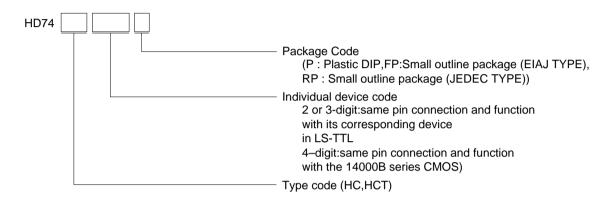

## Type Name of High-Speed CMOS Logic

The JEDEC has divided the HS-CMOS's into two types: HC and HCT. The HC type has the CMOS logic level for inputs and outputs with buffers. The HCT type has the TTL logic level for inputs and the outputs have buffers.

The industry-standarized maximum ratings and recommended operating range are shown below. Limits for the static characteristics are shown below (right): Table 1 is in the industry-standard and Table 2 is the Hitachi specifications.

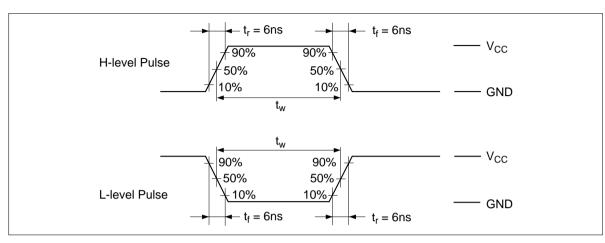

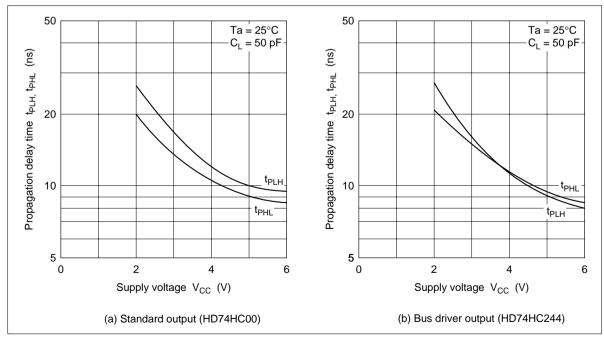

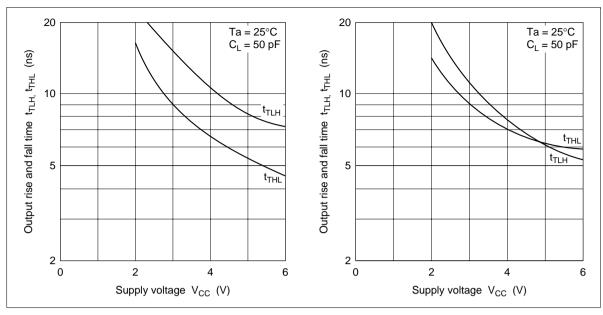

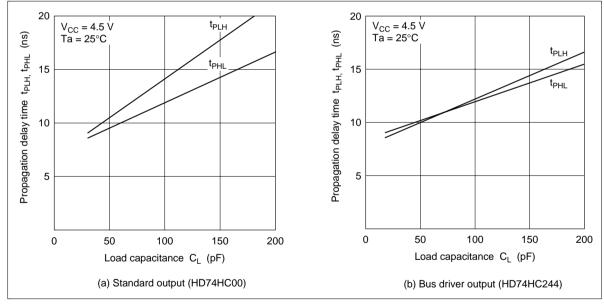

The Hitachi specifications is used throughout this data book. Additional specification are shown in the individual data sheets. Switching characteristics are specified under the following conditions:

- Input pulse voltage:  $+ V_{CC}$

- Load capacitance: 50 pF

- Input pulse rise/fall time: 6 ns

Switching times measured from 50% point of input voltage to 50% point of output voltage

• Three different supply voltages: 2.0, 4.5 and 6.0 V

## Input Levels of Each Series Type $(V_{CC} = 5 V)$

|            | Input level     |                 |                            |

|------------|-----------------|-----------------|----------------------------|

| Туре       | V <sub>IH</sub> | V <sub>IL</sub> | Remarks                    |

| HC series  | 3.5 V           | 1.5 V           | —                          |

| HCT series | 2.0 V           | 0.8 V           | TTL logic level for inputs |

#### **Type Name of HS-CMOS Logic**

#### Absolute Maximum Ratings (Voltages Referenced to GND)

| Item                          | Symbol                             | Rating                       | Unit |  |

|-------------------------------|------------------------------------|------------------------------|------|--|

| Supply voltage                | V <sub>cc</sub>                    | -0.5 to +7                   | V    |  |

| I/O voltage                   | V <sub>IN</sub> , V <sub>OUT</sub> | –0.5 to V <sub>cc</sub> +0.5 | V    |  |

| I/O diode current             | I <sub>IK</sub> , I <sub>OK</sub>  | ±20                          | mA   |  |

| Output current                | I <sub>o</sub>                     | ±25                          | mA   |  |

| V <sub>cc</sub> , GND current | I <sub>cc</sub> , I <sub>gnd</sub> | ±50                          | mA   |  |

| Power dissipation             | P <sub>T</sub>                     | 500                          | mW   |  |

| Storage temperature Range     | Tstg                               | -65 to +150                  | °C   |  |

Additional specification values are shown on the individual data sheets.

## **Recommended Operating Range**

### HD74HC

| Item                  | Symbol                             | Rating               | Unit | Condition        |

|-----------------------|------------------------------------|----------------------|------|------------------|

| Supply voltage        | V <sub>cc</sub>                    | 2 to 6               | V    |                  |

| I/O voltage           | V <sub>IN</sub> , V <sub>OUT</sub> | 0 to V <sub>cc</sub> | V    |                  |

| Operating temperature | Та                                 | -40 to +85           | °C   |                  |

| Input rise/fall time  | tr, tf                             | 0 to 1000            | ns   | $V_{cc} = 2.0 V$ |

|                       |                                    | 0 to 500             |      | $V_{cc}$ = 4.5 V |

|                       |                                    | 0 to 400             |      | $V_{cc} = 6.0 V$ |

#### HD74HCT

| Item                  | Symbol                    | Rating               | Unit | Condition               |

|-----------------------|---------------------------|----------------------|------|-------------------------|

| Supply voltage        | V <sub>cc</sub>           | 4.5 to 5.5           | V    |                         |

| I/O voltage           | $V_{\rm in}, V_{\rm out}$ | 0 to V <sub>cc</sub> | V    |                         |

| Operating temperature | Та                        | -40 to +85           | °C   |                         |

| Input rise/fall time  | tr, tf                    | 0 to 1000            | ns   | V <sub>cc</sub> = 2.0 V |

|                       |                           | 0 to 500             |      | V <sub>cc</sub> = 4.5 V |

|                       |                           | 0 to 400             |      | $V_{cc} = 6.0 V$        |

#### HD74HC14, HC132

| ltem                 | Symbol | Rating         | Unit | Condition        |

|----------------------|--------|----------------|------|------------------|

| Input rise/fall time | tr, tf | 0 to unlimited | ns   | $V_{cc} = 2.0 V$ |

|                      |        | 0 to unlimited |      | $V_{cc} = 4.5 V$ |

|                      |        | 0 to unlimited |      | $V_{cc} = 6.0 V$ |

#### HD74HC123A, HC221, HC423A

| Item                      | Symbol | Rating         | Unit | Condition               |

|---------------------------|--------|----------------|------|-------------------------|

| A, B Input rise/fall time | tr, tf | 0 to unlimited | ns   | $V_{cc} = 2.0 V$        |

|                           |        | 0 to unlimited |      | $V_{cc} = 4.5 V$        |

|                           |        | 0 to unlimited |      | $V_{cc} = 6.0 V$        |

| CLR Input rise/fall time  | tr, tf | 0 to 1000      | ns   | $V_{cc} = 2.0 V$        |

|                           |        | 0 to 500       |      | $V_{\rm cc}$ = 4.5 V    |

|                           |        | 0 to 400       |      | V <sub>cc</sub> = 6.0 V |

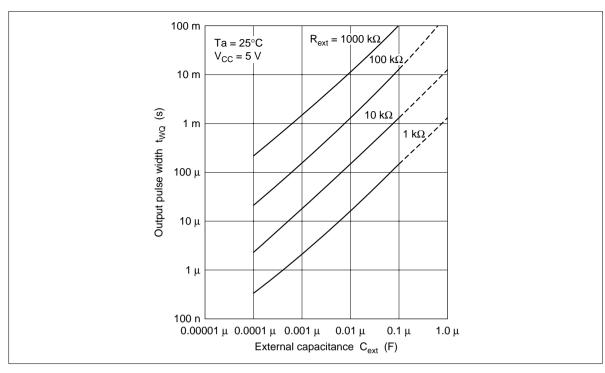

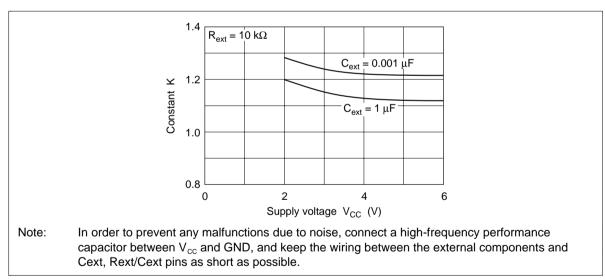

#### HD74HC4538

| Item                      | Symbol | Rating         | Unit | Condition               |

|---------------------------|--------|----------------|------|-------------------------|

| A, B Input rise/fall time | tr, tf | 0 to unlimited | ns   | $V_{cc} = 2.0 V$        |

|                           |        | 0 to unlimited |      | V <sub>cc</sub> = 4.5 V |

|                           |        | 0 to unlimited |      | $V_{cc} = 6.0 V$        |

| CD Input rise/fall time   | tr, tf | 0 to 1000      | ns   | V <sub>cc</sub> = 2.0 V |

|                           |        | 0 to 500       |      | V <sub>cc</sub> = 4.5 V |

|                           |        | 0 to 400       |      | $V_{cc} = 6.0 V$        |

#### HD74HC540, HC541

| Item                   | Symbol | Rating         | Unit | Condition        |

|------------------------|--------|----------------|------|------------------|

| A Input rise/fall time | tr, tf | 0 to unlimited | ns   | $V_{cc} = 2.0 V$ |

|                        |        | 0 to unlimited |      | $V_{cc} = 4.5 V$ |

|                        |        | 0 to unlimited |      | $V_{cc} = 6.0 V$ |

| G Input rise/fall time | tr, tf | 0 to 1000      | ns   | $V_{cc} = 2.0 V$ |

|                        |        | 0 to 500       |      | $V_{cc} = 4.5 V$ |

|                        |        | 0 to 400       |      | $V_{cc} = 6.0 V$ |

#### Table 1 EIA/JEDEC Format for High-Speed CMOS Specifications

|               |            |            |                 |                     | Limi | ts   |                |      |      |                                   |                                   |

|---------------|------------|------------|-----------------|---------------------|------|------|----------------|------|------|-----------------------------------|-----------------------------------|

|               |            |            |                 |                     | +25° | С    | –40 t<br>+85°( |      | •    |                                   |                                   |

| Paramete      | Parameters |            | Symbol          | V <sub>cc</sub> (V) | min  | max  | min            | max  | Unit | Test Condition                    | ns                                |

| Input voltage |            | HC Series  | $V_{\rm IH}$    | 2.0                 | 1.5  |      | 1.5            |      | V    |                                   |                                   |

|               |            |            |                 | 4.5                 | 3.15 |      | 3.15           |      | _    |                                   |                                   |

|               |            |            | _               | 6.0                 | 4.2  | _    | 4.2            |      | _    |                                   |                                   |

|               |            | HCT Series |                 | 4.5 to<br>5.5       | 2.0  | —    | 2.0            | —    |      |                                   |                                   |

|               |            | HC Series  | VIL             | 2.0                 | —    | 0.3  | —              | 0.3  | V    |                                   |                                   |

|               |            |            |                 | 4.5                 | —    | 0.9  | —              | 0.9  | _    |                                   |                                   |

|               |            |            |                 | 6.0                 | —    | 1.2  | _              | 1.2  | -    |                                   |                                   |

|               |            | HCT Series |                 | 4.5 to<br>5.5       | —    | 0.8  | —              | 0.8  |      |                                   |                                   |

| Output        | HC         | Standard   | V <sub>OH</sub> | 2.0                 | 1.9  |      | 1.9            |      | V    | $Vin = V_{IH} \text{ or } V_{IL}$ | lout = -20 μA                     |

| voltage       | Series     | type       |                 | 4.5                 | 4.4  | _    | 4.4            | _    | -    |                                   |                                   |

|               |            |            |                 | 6.0                 | 5.9  |      | 5.9            |      | -    |                                   |                                   |

|               |            |            |                 | 4.5                 | 3.98 |      | 3.84           |      | -    |                                   | lout = -4.0 mA                    |

|               |            |            |                 | 6.0                 | 5.48 | _    | 5.34           | —    | -    |                                   | lout = -5.2 mA                    |

|               |            | Bus driver | -               | 2.0                 | 1.9  |      | 1.9            | _    | -    | $Vin = V_{IH} \text{ or } V_{IL}$ | lout = -20 μA                     |

|               |            | type       |                 | 4.5                 | 4.4  | _    | 4.4            | —    | -    |                                   |                                   |

|               |            |            |                 | 6.0                 | 5.9  | _    | 5.9            | —    | -    |                                   |                                   |

|               |            |            |                 | 4.5                 | 3.98 | _    | 3.84           | —    | -    |                                   | lout = -6.0 mA                    |

|               |            |            |                 | 6.0                 | 5.48 | _    | 5.34           | _    | -    |                                   | lout = -7.8 mA                    |

|               | HCT        | Standard   | _               | 4.5                 | 4.4  | —    | 4.4            | —    | -    | $Vin = V_{IH} \text{ or } V_{IL}$ | lout = $-20 \ \mu A$              |

|               | Series     | type       |                 | 4.5                 | 3.98 | _    | 3.84           | —    | -    |                                   | lout = -4.0 mA                    |

|               |            | Bus driver |                 | 4.5                 | 4.4  | —    | 4.4            | —    | _    | $Vin=V_{IH} \text{ or } V_{IL}$   | $\text{lout} = -20 \ \mu\text{A}$ |

|               |            | type       |                 | 4.5                 | 3.98 |      | 3.84           | _    |      |                                   | lout = -6.0 mA                    |

|               | HC         | Standard   | V <sub>OL</sub> | 2.0                 | _    | 0.1  |                | 0.1  | V    | $Vin = V_{IH} \text{ or } V_{IL}$ | lout = 20 μA                      |

|               | Series     | type       |                 | 4.5                 | —    | 0.1  |                | 0.1  | _    |                                   |                                   |

|               |            |            |                 | 6.0                 |      | 0.1  |                | 0.1  | _    |                                   |                                   |

|               |            |            |                 | 4.5                 | _    | 0.26 |                | 0.33 | -    |                                   | lout = 4.0  mA                    |

|               |            |            | _               | 6.0                 | _    | 0.26 | _              | 0.33 | _    |                                   | lout = 5.2 mA                     |

|               |            | Bus driver |                 | 2.0                 | _    | 0.1  |                | 0.1  | _    | $Vin = V_{IH} \text{ or } V_{IL}$ | lout = 20 μA                      |

|               |            | type       |                 | 4.5                 |      | 0.1  |                | 0.1  | _    |                                   |                                   |

|               |            |            |                 | 6.0                 |      | 0.1  |                | 0.1  |      |                                   |                                   |

|             |          |            |                     |                     | Limit | s    |                |      |      |                                                            |

|-------------|----------|------------|---------------------|---------------------|-------|------|----------------|------|------|------------------------------------------------------------|

|             |          |            |                     |                     | +25°( | C    | –40 t<br>+85°0 | -    |      |                                                            |

| Parameter   | s        |            | Symbol              | V <sub>cc</sub> (V) | min   | max  | min            | max  | Unit | Test Conditions                                            |

| Output      | HC       | Bus driver |                     | 4.5                 |       | 0.26 |                | 0.33 | V    | Vin = $V_{IH}$ or $V_{IL}$ lout = 6.0 mA                   |

| voltage     | Series   | type       |                     | 6.0                 | _     | 0.26 | _              | 0.33 |      | lout = 7.8 mA                                              |

|             | HCT      | Standard   |                     | 4.5                 | _     | 0.1  |                | 0.1  |      | Vin = V <sub>IH</sub> or V <sub>IL</sub> lout = 20 $\mu$ A |

|             | Series   | type       |                     | 4.5                 | _     | 0.26 |                | 0.33 |      | lout = 4.0 mA                                              |

|             |          | Bus driver | -                   | 4.5                 | _     | 0.1  | _              | 0.1  |      | Vin = $V_{IH}$ or $V_{IL}$ lout = 20 $\mu$ A               |

|             |          | type       |                     | 4.5                 |       | 0.26 |                | 0.33 |      | lout = 6.0 mA                                              |

| Input leaka | ige      | HC Series  | I,                  | 6.0                 |       | ±0.1 |                | ±1.0 | μA   | Vin = V <sub>cc</sub> or GND                               |

| current     |          | HCT Series | -                   | 5.5                 | _     | ±0.1 | _              | ±1.0 |      |                                                            |

| Analog swi  | tch off- | HC Series  | I <sub>S(off)</sub> | 6.0                 |       | ±0.1 |                | ±1.0 | μΑ   | $Vin = V_{IH} \text{ or } V_{IL}$                          |

| state curre | nt       | HCT Series | _                   | 5.5                 | _     | ±0.1 | —              | ±1.0 |      | $ V_{s}  = V_{cc} \text{ or } V_{cc} - V_{ee}$             |

| 3-state out | put off- | HC Series  | I <sub>oz</sub>     | 6.0                 | _     | ±0.5 | _              | ±5.0 | μA   | $Vin = V_{IH} \text{ or } V_{IL}$                          |

| state curre | nt       | HCT Series | _                   | 5.5                 | _     | ±0.5 |                | ±5.0 |      | Vout = $V_{cc}$ or GND                                     |

| Quiescent   | HC       | SSI        | I <sub>cc</sub>     | 6.0                 |       | 2.0  |                | 20   | μA   | Vin = $V_{cc}$ or GND                                      |

| supply      | Series   | FF         | -                   | 6.0                 | _     | 4.0  | _              | 40   |      | lout = 0 $\mu$ A                                           |

| current     |          | MSI        | -                   | 6.0                 |       | 8.0  |                | 80   |      |                                                            |

|             | HCT      | SSI        | -                   | 5.5                 |       | 2.0  |                | 20   |      |                                                            |

|             | Series   | FF         | -                   | 5.5                 | _     | 4.0  |                | 40   |      |                                                            |

|             |          | MSI        | -                   | 5.5                 |       | 8.0  |                | 80   |      |                                                            |

## Table 2 Hitachi High-Speed CMOS Series Specifications

|             |        |            |                 |                     | Limi | ts   |                |      |      |                                                                 |

|-------------|--------|------------|-----------------|---------------------|------|------|----------------|------|------|-----------------------------------------------------------------|

|             |        |            |                 |                     | +25° | с    | –40 t<br>+85°0 |      |      |                                                                 |

| Paramete    | rs     |            | Symbol          | V <sub>cc</sub> (V) | min  | max  | min            | max  | Unit | Test Conditions                                                 |

| Input volta | ige    | HC Series  | $V_{\rm IH}$    | 2.0                 | 1.5  |      | 1.5            |      | V    |                                                                 |

|             |        |            |                 | 4.5                 | 3.15 | —    | 3.15           | —    |      |                                                                 |

|             |        |            | _               | 6.0                 | 4.2  | _    | 4.2            | —    |      |                                                                 |

|             |        | HCT Series |                 | 4.5 to<br>5.5       | 2.0  | —    | 2.0            | —    |      |                                                                 |

|             |        | HC Series  | V <sub>IL</sub> | 2.0                 | —    | 0.5  |                | 0.5  | V    |                                                                 |

|             |        |            |                 | 4.5                 | —    | 1.35 | _              | 1.35 |      |                                                                 |

|             |        |            | _               | 6.0                 | —    | 1.8  | _              | 1.8  |      |                                                                 |

|             |        | HCT Series |                 | 4.5 to<br>5.5       | —    | 0.8  | —              | 0.8  |      |                                                                 |

| Output      | HC     | Standard   | V <sub>OH</sub> | 2.0                 | 1.9  |      | 1.9            |      | V    | Vin = V <sub>IH</sub> or V <sub>IL</sub> $I_{OH}$ = -20 $\mu$ A |

| voltage     | Series | type       |                 | 4.5                 | 4.4  | _    | 4.4            |      |      |                                                                 |

|             |        |            |                 | 6.0                 | 5.9  | _    | 5.9            |      |      |                                                                 |

|             |        |            |                 | 4.5                 | 4.18 |      | 4.13           |      |      | $I_{OH} = -4.0 \text{ mA}$                                      |

|             |        |            |                 | 6.0                 | 5.68 | _    | 5.63           |      | -    | I <sub>он</sub> = -5.2 mA                                       |

|             |        | Bus driver | -               | 2.0                 | 1.9  |      | 1.9            |      |      | Vin = V <sub>IH</sub> or V <sub>IL</sub> $I_{OH}$ = -20 $\mu$ A |

|             |        | type       |                 | 4.5                 | 4.4  | _    | 4.4            |      |      |                                                                 |

|             |        |            |                 | 6.0                 | 5.9  | —    | 5.9            |      |      |                                                                 |

|             |        |            |                 | 4.5                 | 4.18 | _    | 4.13           | _    | -    | I <sub>он</sub> = -6.0 mA                                       |

|             |        |            |                 | 6.0                 | 5.68 | _    | 5.63           |      |      | I <sub>OH</sub> = -7.8 mA                                       |

|             | HCT    | Standard   | _               | 4.5                 | 4.4  | —    | 4.4            |      |      | Vin = V_{\rm IH} or V_{\rm IL} I_{\rm OH} = -20 \ \mu A         |

|             | Series | type       |                 | 4.5                 | 4.18 | _    | 4.13           | _    | -    | I <sub>он</sub> = -4.0 mA                                       |

|             |        | Bus driver |                 | 4.5                 | 4.4  |      | 4.4            | _    | -    | Vin = V_{\rm IH} or V_{\rm IL}  I_{\rm OH} = –20 $\mu A$        |

|             |        | type       |                 | 4.5                 | 4.18 | —    | 4.13           | —    |      | I <sub>он</sub> = -6.0 mА                                       |

|             | HC     | Standard   | V <sub>OL</sub> | 2.0                 | —    | 0.1  | _              | 0.1  | V    | Vin = $V_{IH}$ or $V_{IL}$ $I_{OL}$ = 20 $\mu$ A                |

|             | Series | type       |                 | 4.5                 | _    | 0.1  | _              | 0.1  |      |                                                                 |

|             |        |            |                 | 6.0                 | _    | 0.1  |                | 0.1  |      |                                                                 |

|             |        |            |                 | 4.5                 |      | 0.26 |                | 0.33 | V    | Vin = $V_{IH}$ or $V_{IL}$ $I_{OL}$ = 4.0 mA                    |

|             |        |            | _               | 6.0                 | _    | 0.26 | _              | 0.33 |      | I <sub>oL</sub> = 5.2 mA                                        |

|             |        | Bus driver |                 | 2.0                 | _    | 0.1  |                | 0.1  |      | Vin = V_{IH} or V_{IL} I_{OL} = 20 \ \mu A                      |

|             |        | type       |                 | 4.5                 | _    | 0.1  | _              | 0.1  |      |                                                                 |

|             |        |            |                 | 6.0                 | _    | 0.1  |                | 0.1  |      |                                                                 |

|             |          |            |                      |                     | Limits |      |                |      |      |                                                         |

|-------------|----------|------------|----------------------|---------------------|--------|------|----------------|------|------|---------------------------------------------------------|

|             |          |            |                      |                     | +25°   | с    | –40 t<br>+85°0 | -    | •    |                                                         |

| Parameter   | s        |            | Symbol               | V <sub>cc</sub> (V) | min    | max  | min            | max  | Unit | Test Conditions                                         |

| Output      | HC       | Bus driver | V <sub>ol</sub>      | 4.5                 | _      | 0.26 |                | 0.33 | V    | Vin = $V_{IH}$ or $V_{IL}$ I <sub>OL</sub> = 6.0 mA     |

| voltage     | Series   | type       |                      | 6.0                 | _      | 0.26 | _              | 0.33 |      | I <sub>oL</sub> = 7.8 mA                                |

|             | HCT      | Standard   | -                    | 4.5                 |        | 0.1  |                | 0.1  | -    | Vin = $V_{IH}$ or $V_{IL}$ I <sub>OL</sub> = 20 $\mu$ A |

|             | Series   | type       |                      | 4.5                 |        | 0.26 | _              | 0.33 | -    | $I_{oL} = 4.0 \text{ mA}$                               |

|             |          | Bus driver | -                    | 4.5                 |        | 0.1  | _              | 0.1  | -    | Vin = $V_{IH}$ or $V_{IL}$ $I_{OL}$ = 20 $\mu$ A        |

|             |          | type       |                      | 4.5                 | _      | 0.26 | _              | 0.33 | -    | $I_{OL} = 6.0 \text{ mA}$                               |

| Input leaka | ige      | HC Series  | I,                   | 6.0                 |        | ±0.1 |                | ±1.0 | μA   | $Vin = V_{cc} \text{ or } GND$                          |

| current     |          | HCT Series | -                    | 5.5                 |        | ±0.1 |                | ±1.0 | -    |                                                         |

| Analog Sw   | itch     | HC Series  | I <sub>s</sub> (off) | 6.0                 |        | ±0.1 |                | ±1.0 | μA   | $Vin = V_{IH} \text{ or } V_{IL}$                       |

| Off-state C | urrent   | HCT Series | -                    | 5.5                 | _      | ±0.1 |                | ±1.0 | -    | $ V_{s}  = V_{cc} \text{ or } V_{cc} - V_{ee}$          |

| 3-state out | put Off- | HC Series  | l <sub>oz</sub>      | 6.0                 |        | ±0.5 |                | ±5.0 | μA   | $Vin = V_{IH} \text{ or } V_{IL}$                       |

| state Curre | ent      | HCT Series | -                    | 5.5                 |        | ±0.5 |                | ±5.0 | -    | Vout = $V_{cc}$ or GND                                  |

| Quiescent   | HC       | SSI        | I <sub>cc</sub>      | 6.0                 |        | 1.0  |                | 10   | μA   | Vin = $V_{cc}$ or GND                                   |

| Supply      | Series   | FF         | -                    | 6.0                 |        | 2.0  | _              | 20   | -    | lout = 0 $\mu$ A                                        |

| Current     |          | MSI        | -                    | 6.0                 | _      | 4.0  |                | 40   | -    |                                                         |

|             | HCT      | SSI        | -                    | 5.5                 | _      | 1.0  | _              | 10   | -    |                                                         |

|             | Series   | FF         | -                    | 5.5                 | _      | 2.0  | _              | 20   | -    |                                                         |

|             |          | MSI        | -                    | 5.5                 |        | 4.0  |                | 40   | -    |                                                         |

## Symbols and Terms Defined for HD74HC Series

1. Explanation of Symbols Used in Electrical Characteristics and Recommended Operating Conditions

| 1.1 DC characteristic | cs |

|-----------------------|----|

|-----------------------|----|

| Symbol          | Term                                      | Description                                                                                                                                                                         |

|-----------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IH</sub> | "H" level input voltage                   | "H" level input voltage to ensure that a logic element operates under some constraint.                                                                                              |

| V <sub>IL</sub> | "L" level input voltage                   | "L" level input voltage to ensure that a logic element operates under some constraint.                                                                                              |

| V <sub>oL</sub> | "L" level output voltage                  | Output voltage in effect when, under the input condition for<br>bringing the output Low, the rated output current is allowed<br>to flow to the output terminal.                     |

| V <sub>OH</sub> | "H" level output voltage                  | Output voltage in effect when, under the input condition for<br>bringing the output High, the rated output current is allowed<br>to flow to the output terminal.                    |

| $V_{T}^{+}$     | Forward input threshold voltage           | Input voltage in effect when the operation of a logic element varies as the input is allowed to go up from a voltage level lower than the forward input threshold voltage $V_T$ .   |

| V <sub>T</sub>  | Reverse input threshold voltage           | Input voltage in effect when the operation of a logic element varies as the input is allowed to go up from a voltage level lower than the reverse input threshold voltage $V_T^+$ . |

| V <sub>H</sub>  | Hysteresis voltage                        | Differnce between forward input threshold voltage $V_{\tau}^{*}$ and reverse threshold voltage $V_{\tau}^{-}.$                                                                      |

| I <sub>OH</sub> | "H" level output current                  | Output current that flows out when, under the condition for<br>bringing the output High, the rated output voltage VOUT is<br>applied to the output terminal.                        |

| I <sub>OL</sub> | "L" level output current                  | Output current that flows out when, under the condition for bringing the output High, the rated output voltage $V_{\text{OUT}}$ is applied to the output terminal.                  |

| I <sub>IN</sub> | Input leakage current                     | Input current that flows in when the rated maximum input voltage is applied to the input terminal.                                                                                  |

| I <sub>IH</sub> | "H" level input current                   | Input current that flows in when the rated "H" level voltage is applied to the input.                                                                                               |

| I <sub>IL</sub> | "L" level input current                   | Input current that flows out when the rated "L" level voltage is applied to the input.                                                                                              |

| I <sub>oz</sub> | Off-state output current (high impedance) | Current that flows to the 3-state output of an element under<br>the input condition for briging the output to High impedance.                                                       |

| ls(off)         | Analog switch off-state current           | Current that flows to the analog switch of an element under<br>the input condition for bringing the switch to off-state.                                                            |

| I <sub>cc</sub> | Quiescent supply current                  | Current that flows to the supply terminal ( $V_{\rm cc}$ ) under the rated input condition.                                                                                         |

#### 1.2 AC characteristics

| Symbol           | Term                                      | Description                                                                                                                                                                               |

|------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>max</sub> | Maximum clock frequency                   | Maximum clock frequency that maintains the stable changes in output logic level in the rated sequence under the I/O condition allowing clock pulses to change the output state.           |

| t <sub>TLH</sub> | Rise (transient) time                     | Rated time from "L" level to "H" level of a waveform during the defined transient period changing from "L" level to "H" level.                                                            |

| t <sub>THL</sub> | Fall (transient) time                     | Rated time from "H" level to "L" level of a waveform during the defined transient period changing from "H" level to "L" level.                                                            |

| t <sub>PLH</sub> | Output rise propagation delay time        | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the output changing from "L" level to "H" level.                              |

| t <sub>PHL</sub> | Output fall propagation delay time        | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the output changing from "H" level to "L" level.                              |

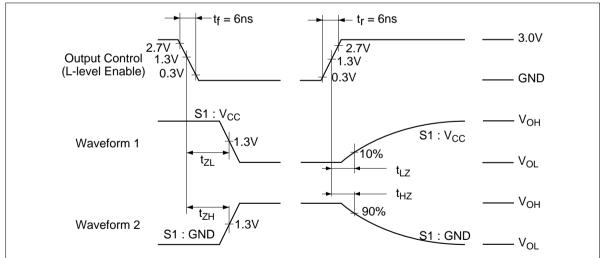

| t <sub>HZ</sub>  | 3-state output disable time ("H" level)   | Delay time between the rated voltage levels of an I/O voltage<br>waveform under a defined load condition, with the 3-state<br>output changing from "H" level to the high impedance state. |

| t <sub>LZ</sub>  | 3-state output disable time ("L" level)   | Delay time between the rated voltatge levels of an I/O voltage waveform under a defined load condition, with the 3-state output changing from "L" level to the high impedance state       |

| t <sub>zH</sub>  | 3-state output enable time ("H"<br>level) | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the 3-state output changing from the high impedance state to "H" level.       |

| t <sub>ZL</sub>  | 3-state output enable time ("L"<br>level) | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the 3-state output changing from the high impedance state to "L" level.       |

| t <sub>w</sub>   | Pulse width                               | Duration of time between the rated levels from a leading edge to a trailing edge of a pulse waveform.                                                                                     |

| t <sub>h</sub>   | Hold time                                 | Time in which to hold date at the specified input terminal after<br>a change at another related input terminal (e.g., clock input).                                                       |

| t <sub>su</sub>  | Setup time                                | Time in which to set up and keep data at the specified input<br>terminal before a change at another related input terminal<br>(e.g., clock input).                                        |

| t <sub>rm</sub>  | Removal time                              | Time period between the time when data at the specified input<br>terminal is released and the time when another related input<br>terminal (e.g., clock input) can be changed.             |

| C <sub>in</sub>  | Input capacitance                         | Capacitance between GND terminal and an input terminal to which 0 V is applied.                                                                                                           |

| Symbol         | Description                                                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------|

| Н              | High level (in steady state; noted "H" or "H" level in sentences)                                            |

| L              | Low level (in steady state; noted "L" or "L" level in sentences)                                             |

|                | Transition from L level to H level                                                                           |

|                | Transition from H level to L level                                                                           |

| Х              | Either H or L                                                                                                |

| Z              | 3-state output off (high impedance)                                                                          |

| ah             | Input level of steady state for each of inputs A-H                                                           |

| Q <sub>0</sub> | Q level immediately before the indicated input condition is established                                      |

| Q <sub>0</sub> | Complement of Q                                                                                              |

| Q <sub>n</sub> | Q level immediately before the latest active change ( $\_$ or $\_$ ) occurs                                  |

| <u></u>        | Single H level pulse                                                                                         |

|                | Single L level pulse                                                                                         |

| TOGGLE         | Each output is changed to the complement of the preceding state by an active input change ( $-\int$ or $-$ ) |

#### 2. Explanation of Symbols Used in Function Table

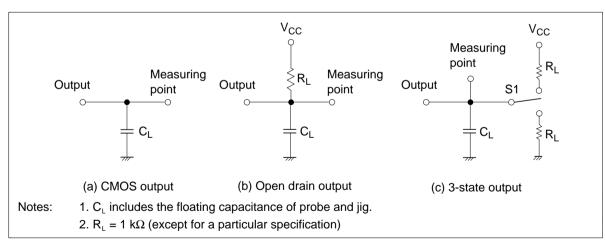

#### **Measuring Method of AC Characteristics**

#### Loading Circuit

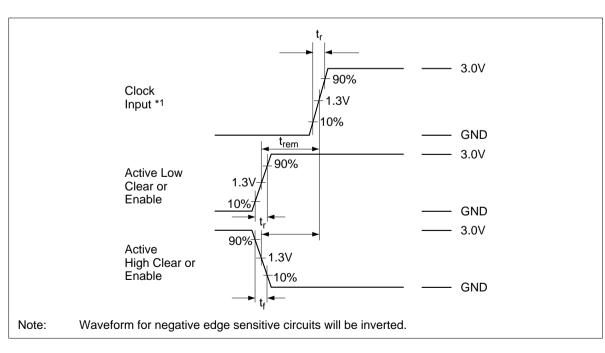

## Waveforms (Mutual relationship of waveforms)

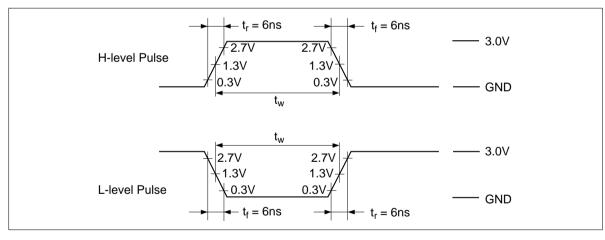

### Pulse Width (T<sub>w</sub>)

#### 74HC Series

#### 74HCT Series

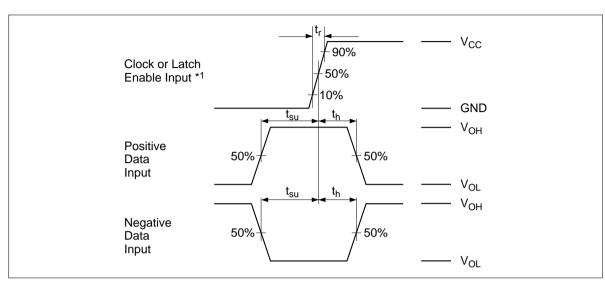

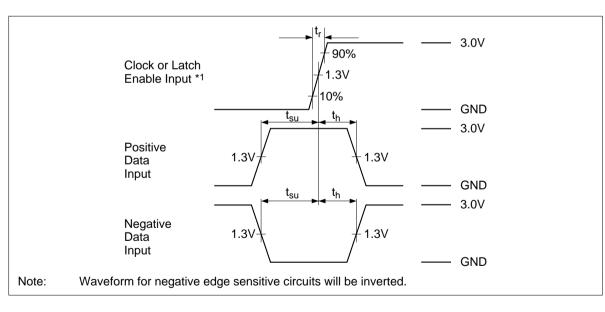

#### Setup Time and Hold Time

#### 74HC Series

#### 74HCT Series

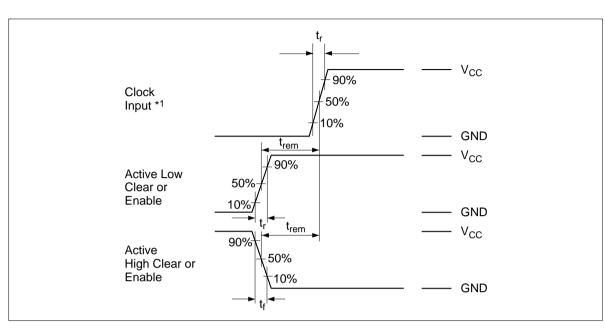

#### **Removal Time**

74HC Series

#### 74HCT Series

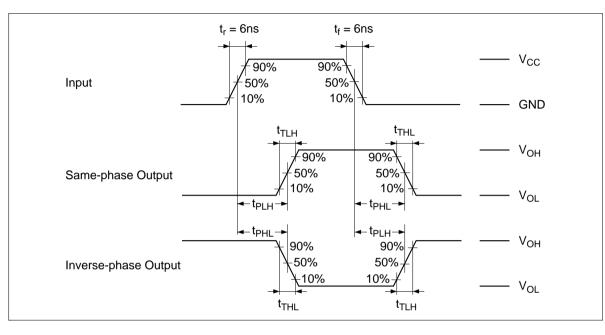

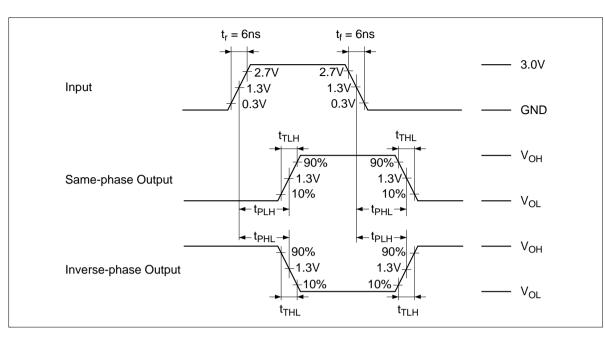

### Waveforms (Mutual relationship of waveforms)

#### Propagation Delay Time, Output Rise Time and Output Fall time

#### 74HC Series

#### 74 HCT Series

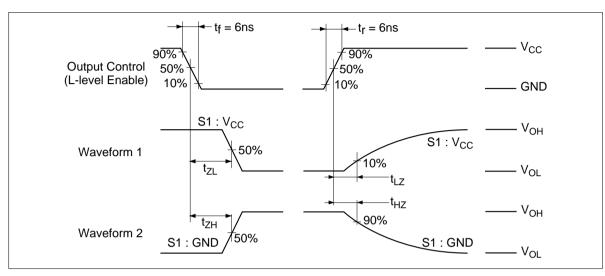

#### Waveforms (Mutual relationship of waveforms)

#### Three-state Output, Enable Time and Disable Time

#### 74HC Series

#### 74HCT Series

# Notes: 1. Waveform 1 is an output under the internal condition like "L" except for the output disabled by the output control.

2. Waveform 2 is an output under the internal condition like "H" except for the output disabled by the output control.

## **Precautions in System Design**

## Precautions in System Design

In the system design, the problems to be considered are described in the following items:

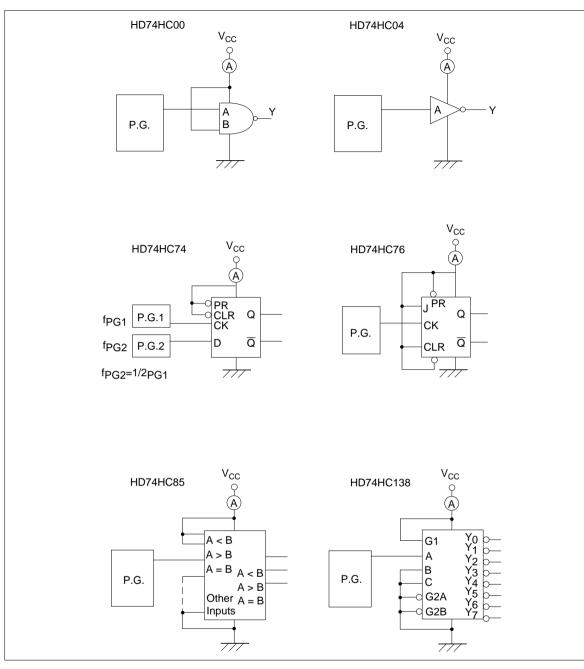

#### 1. Transfer Characteristics

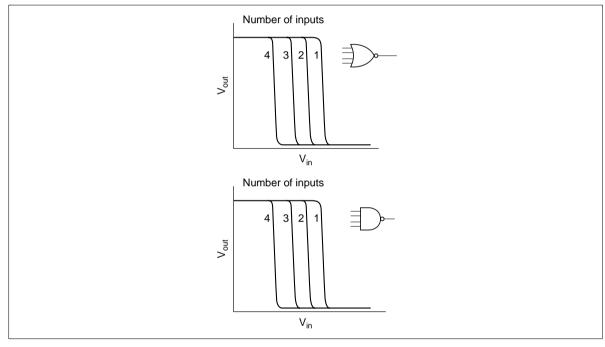

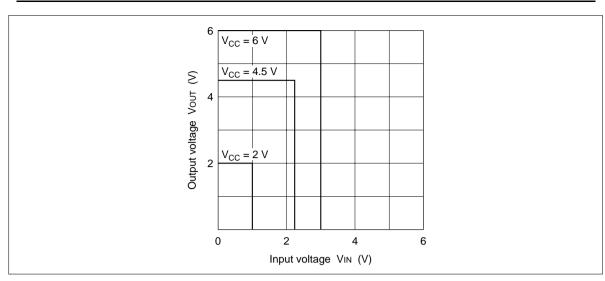

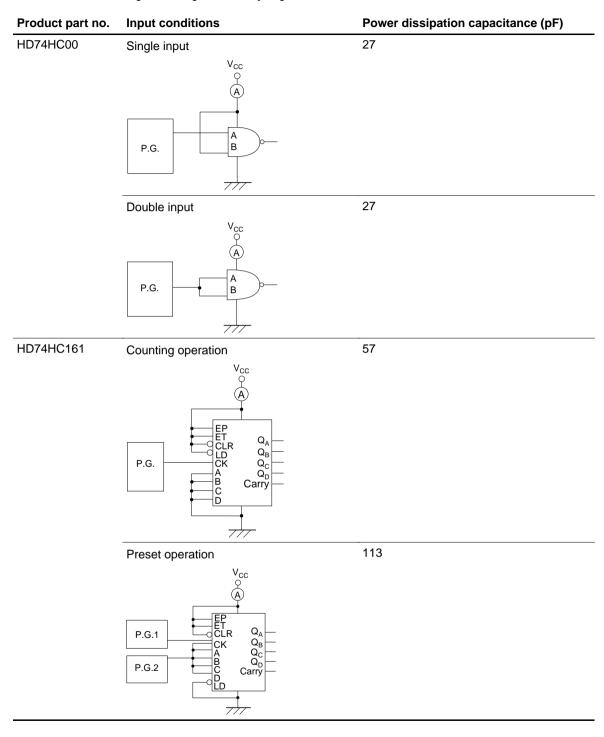

Since the transfer characteristics of gate circuit varies with the number of working inputs, care must be taken to the noise margin. In the multiple input NOR gate, the P channel MOS is connected to  $V_{CC}$  in series and the N channel MOS is connected to GND in parallel. In the NAND gate, the connection is reverse. The output voltage  $V_{OUT}$  in the transition area becomes a value obtained by distributing the supply voltage at a split ratio according to the ON resistance of P channel MOS and N channel MOS. In the multiple input NOR and NAND gates, the fall of transfer characteristic, that is,  $V_{IN}$  (voltage noise margin) that enters in the transition area changes according to the number of inputs as shown in Figure 1.

Figure 1

As seen from the above, it becomes clear that:

- In the NOR gate, "0" level noise margin  $V_{NL}$  decreases, and "1" level noise margin  $V_{NH}$  increases according to the number of working inputs.

- In the NAND gate, the noise margins are fully reversed.

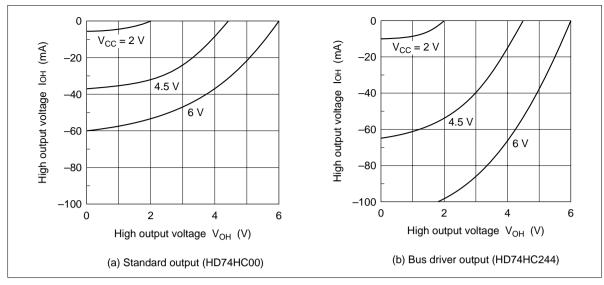

#### 2. Output Impedance

The output impedance of CMOS logic gate is influenced by the circuit configuration, the number of working inputs, logical state and supply voltage. There are two regions of output impedance depending on the operation:

- Constant impedance area in which P and N channel MOS' operate in the nonsaturated state.

- Constant current area in which P and N channel MOS' operate in the pinch-off state.

In designing a system including an interface circuit, the above must be considered.

### 3. Output Short-Circuit

Because no protective circuitry is provided to limit the output current, an output inadvertently shorted to  $V_{CC}$  or GND on the HS-CMOS logic IC is limited to the current value determined by the pinch-off effect of the P-channel MOS and N-channel MOS for the output. Notice that such output short-circuit current, if allowed to flow for a long time, could result in increased power dissipation or in a melted wire due to excessive current density through metalization or other performance failures. For operating stability and reliability, the maximum output current should remain within the maximum rating.

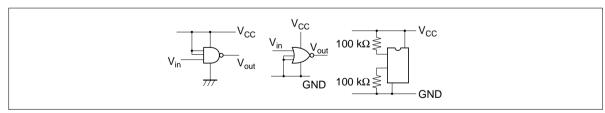

### 4. Unused Inputs

As shown in Figure 2, unused inputs must be:

- (1) Directly connected to  $V_{CC}$  for NAND gate circuits.

- (2) Directly connected to GND for NOR gate circuits.

- (3) Connected to  $V_{CC}$  or GND through a proper resistor (10 k $\Omega$  or 100 k $\Omega$ .).

This is required because the extremely high input impedance of CMOS logic makes it subject to noise. This noise causes the output logic level to be unstable. Furthermore, in some cases, if a gate is not used or a flip-flop is not used, both p-channel MOS and n-channel MOS may conduct, causing  $I_{CC}$  to flow.

Figure 2 Examples of Handling Unused Inputs

## **Precautions in System Design**

#### 5. Input Impedance

Since all the input protective diodes are biased reversely in the ordinary operations, the input impedance of CMOS logic IC is extremely high. When converted into a leak current, it is about several tens (pA) at a temperature of 25°C or about one (nA) even at 100°C. Thus, the matching for operating the CMOS logic IC has only to be considered at a voltage level. In the actual interface to other IC's, however, remember that fan-out is limited according to a capacitance value because inputs measured in capacity.

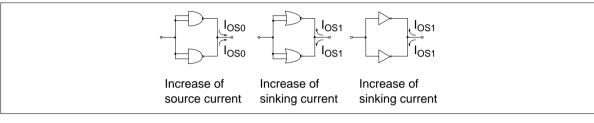

### 6. Parallel Connection of Gate Circuits

If it is necessary to increase source or sinking current, the same type gate circuits can be connected in parallel as shown in Figure 3.

Figure 3 Examples of Parallel Connection

The switching speed improved at the same time. The source and sinking current capacities also increase in proportion to the number of inputs.

#### 7. Wired OR Connection

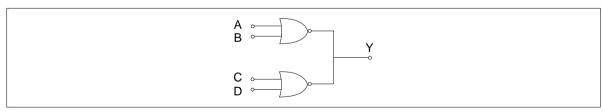

The wired OR connection is unrecommendable and shall not be used in CMOS logic IC's. The reason is that if the two gate outputs are connected with A = B = 0 and C = D = 1 as shown in Figure 4, the output voltage is a value with which the supply voltage is divided by each of the resistance values of active P and N channel MOS', on an about half level ( $V_{CC}$  - GND).

Figure 4 Wired OR Connection

### 8. Input Capacitance

In the CMOS logic IC, there is capacitance between the input and the GND. In addition to the major capacitance between the gate and the substrate, the capacitance of package, leads and input protection circuit are also included. The change input capacitance depending on the input voltage results mainly from the capacitance between the gate and the substrate. This input capacitance has an advantage of temporarily storing date in it by opening/closing the transmission gate. On the other hand, however, remember that the input capacitance may slow down switching speed of mutually connected gate and also may increase the power dissipation. The input capacitance is usually about 5 (pF) as specified in the standard.

### 9. Output Capacitance

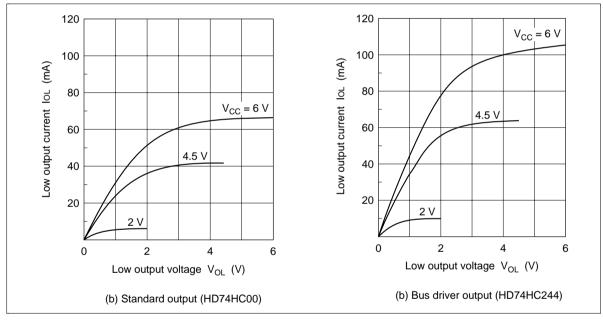

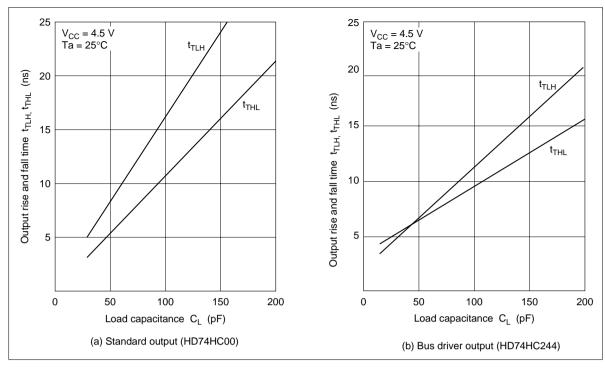

The whole output capacitance of CMOS logic IC is the sum of the drain capacitance of output MOS and the external load capacitance. It may be considered that the former is about 10 (pF) per output. The propagation delay time increases linealy in proportion to the increase of external load capacitance as described previously. The power dissipation also increases according to it. Especially, be careful in attaching a large capacity of around 1 (1 $\mu$ F) outside.

The peak current at the gate transition, as described previously, is limited by the output characteristics of P and N channel MOS'. In the buffer circuit, the peak current may increase (to 100 mA or more).

Pay sufficient attention to the fact that the rise of temperature in the chip may cause metal migration on the metal wiring layer. If the peak current for gate circuit is set to about 50 mA and the one for buffer circuit is set to about 100 mA, no consideration is required.

## **Precautions in System Design**

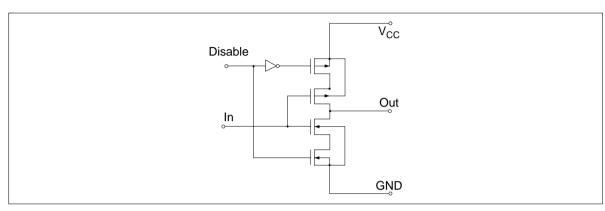

## 10. Features of 3-state Output Circuit

In a system that requires bus configuration, the 3-state output element is brought from the necessity to place unnecessary circuits in the high output impedance state through control input to operate necessary circuit selectively when tow or more circuit is connected to one bus line. Figure 5 shows the typical 3-state circuit. When the Disable input of control terminal is at "1" level, the output is at low impedance by the switch operation. When at "0" level, the output is at extremely high impedance of  $10^4$  (M $\Omega$ ) at a room temperature. Remember that the number of 3-state elements connectable to one bus line is limited by the switching speed and supply voltage.

Figure 5 3-state Output Circuit

### 11. Static Power Dissipation

In the CMOS logic IC, the P channel MOS and N channel MOS are mutually connected each other. Therefore, either P channel or N channel is cut off in the input potential level static state. There is no path in which the current from the power supply flows. Actually, the reverse bias leak current in all the P-N junction in the chip including parasitic P-N junction flows only. The supply current in this state is referred to as static current consumption, and the power dissipation as static power dissipation. The static current consumption is a total of leak currents, and its values are extremely small as listed in Table 1. Thus, the static current consumption is almost proportional to the supply voltage and increases exponentially in proportion to temperature.

#### Table 1

|     |                        | Static Curren                                                                                  | Static Current Consumption I <sub>CC(max)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-----|------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | V <sub>cc</sub>        | +25°C                                                                                          | –40 to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SSI | 6.0 V                  | 1.0 μA                                                                                         | 10 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| FF  |                        | 2.0 μΑ                                                                                         | 20 µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| MSI |                        | 4.0 μΑ                                                                                         | 40 μΑ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SSI | 5.5 V                  | 1.0 μA                                                                                         | 10 µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| FF  |                        | 2.0 μΑ                                                                                         | 20 µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| MSI |                        | 4.0 μΑ                                                                                         | 40 µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|     | FF<br>MSI<br>SSI<br>FF | SSI         6.0 V           FF         MSI           SSI         5.5 V           FF         FF | $\begin{tabular}{ c c c c c } \hline $V_{cc}$ & \hline $+25^{\circ}C$ \\ \hline $SSI$ & $6.0 \ V$ & $1.0 \ \mu A$ \\ \hline $FF$ & $2.0 \ \mu A$ \\ \hline $MSI$ & $4.0 \ \mu A$ \\ \hline $SSI$ & $5.5 \ V$ & $1.0 \ \mu A$ \\ \hline $FF$ & $2.0 \ \mu A$ \\ \hline $2.0 \ \mu A$ \\ \hline $2.0 \ \mu A$ \\ \hline $A$ & $$ |  |

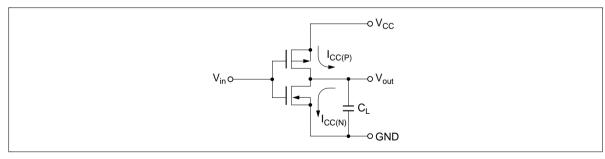

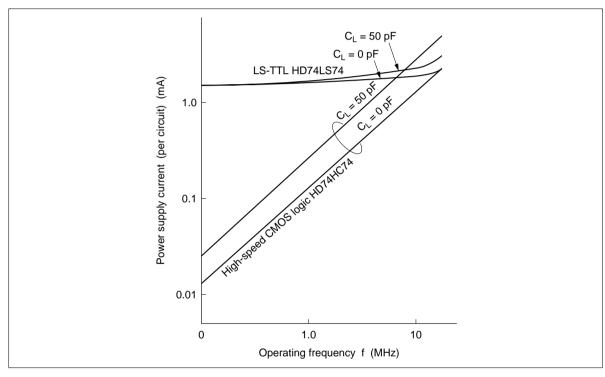

#### 12. Dynamic Power Dissipation

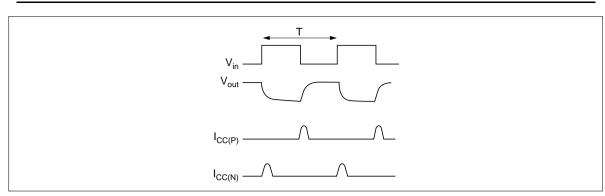

Assuming that the square pulse waves (tr =  $t_f = 0$ ) as shown in Figure 7 are applied to the input of the inverter shown in Figure 6, the output steps from "0" level to "1" level in response to the input fall from "1" level to "0" level.

Figure 6 Inveter circuit

## **Precautions in System Design**

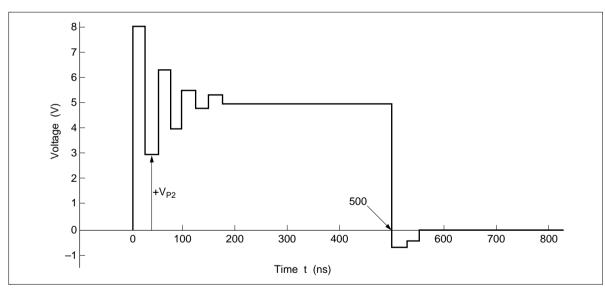

Figure 7 Operating Voltage and current of inverter circuit

Actually,  $V_{OUT}$  is not converted into square waveforms. The reason is that the sum total  $C_L$  of the outputs such as external load capacitance and drain capacitance are inverted by charging them from 0 to  $V_{CC}$ . For charging, supply current  $I_{CC(P)}$  flows through the active P channel MOS from  $V_{CC}$ . Contrary to this, when the input goes from "0" level to "1" level,  $C_L$  discharges and  $I_{CC(N)}$  flows into GND through the N channel MOS. The supply current caused by the charge/discharge is dynamic current dissipation, and the power dissipation is dynamic power dissipation. If the average power dissipation is taken as  $P_T$ , it is obtained theoritically as follows:

The power dissipation when  $I_{CC(P)}$  flows into the P channel MOS in Figure 6 is  $I_{CC(P)}$  ( $V_{CC} - V_{OUT}$ ). If an average is taken by the one cycle of input pulse, the average power dissipation  $P_{TP}$  of P channel MOS is:

$P_{TP} = 1/T \int_0^T I_{CC(P)} \cdot (V_{CC} - V_{OUT}) dt$  $I_{CC}(P) = C_1 \cdot d(V_{CC} - V_{OUT})/dt$

In the same manner, the average power dissipation of N channel MOS is:

$P_{TN} = 1/T \int_0^T I_{CC(N)} \cdot (V_{OUT} - GND) dt$

$I_{CC(N)} = C_{L} \cdot d(V_{OUT} - GND)/dt$

Thus, the average dynamic power dissipation  $P_T$  is:

$$P_{T} = P_{TP} + P_{TN}$$

$$= 1/T \cdot C_{L} \cdot V_{CC}^{2}$$

$$= f \cdot C_{L} \cdot V_{CC}^{2}$$

f: Input pulse frequency

It is clear that the dynamic power dissipation varies with the frequency, load capacitance and supply voltage.

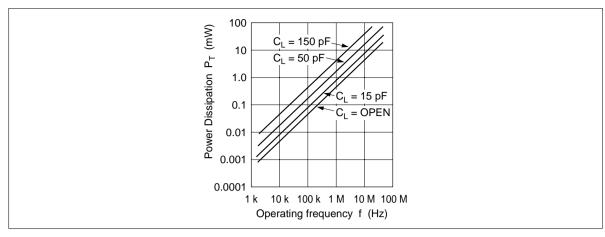

Figure 8 shows the aspect.

## **Precautions in System Design**

Figure 8 Power Dissipation VS. Operating Frequency

This relation shows a case where the square wave input with tr = tf = 0 is assumed. In an actual case, the input pulse is considered a trapezoidal waveform. Thus, remember that the transition state in which both P channel MOS and N channel MOS are simultaneously activate and DC current flows from V<sub>CC</sub> into GND during this time. If input is used at an intermediate level, such as crystal oscillator circuit and a linear amplifier, and if the circuits such as a differentiation circuit, an integration circuit and an oscillation circuit process gentle waveforms, pay attention to the increase of power dissipation.

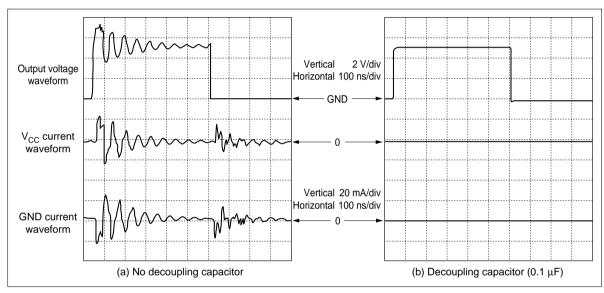

#### 13. Caution of Supply Voltage

To decouple noises, the capacitance of 0.01 to 0.1 ( $\mu$ F) should be attached externally between V<sub>CC</sub> and GND.

#### 14. Caution of Fan-out

The number of fan-outs of CMOS logic IC is virtually unlimited in terms of DC. The reason is that the input current is the P-N junction leak current of input protection circuit at most and its value is actually approximate to 0 because the input is connected to the gate electrodes and insulated from the substrate.

Therefore, the number of fan-outs is not a problem in terms of DC. In AC, there is a slightly different circumstance. Since the input has a capacity of about 5 (pF), the output capacitance increases if the input is connected to the output. If the input capacitance is taken as 5 (pF), for example, the whole load capacitance  $C_L$  (pF) at the time the number of fan-outs is n and load capacitance is  $C_0$  (pF) is:

$C_{\rm L} = 5 \bullet n + C_{\rm O} \, (pF)$

On the other hand, the propagation delay time increases in proportion to the output load capacitance  $C_L$ . The operating speed decreases according to the number of inputs (fan-outs) connected to the output. Therefore, remember that the number of fan-outs is fairly limited if a high-speed operation is required.

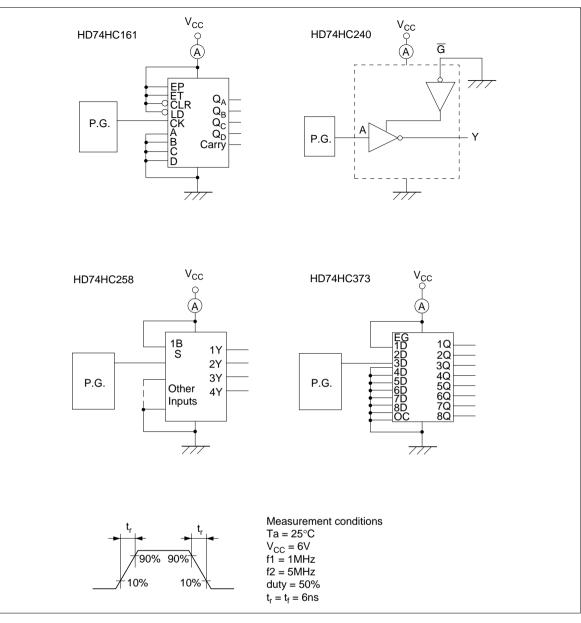

## 15. Cautions on Actual Operation

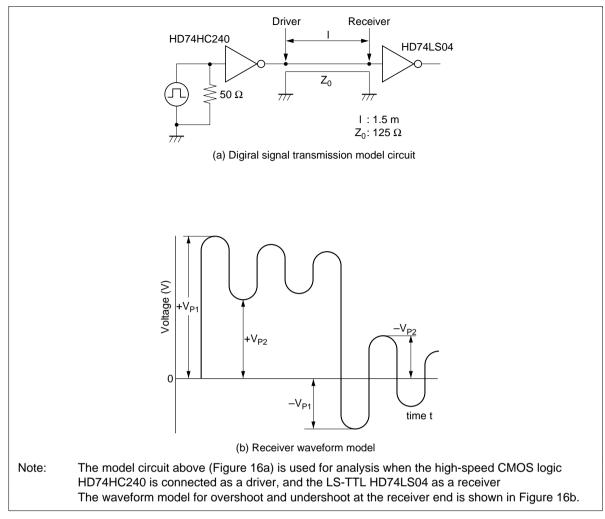

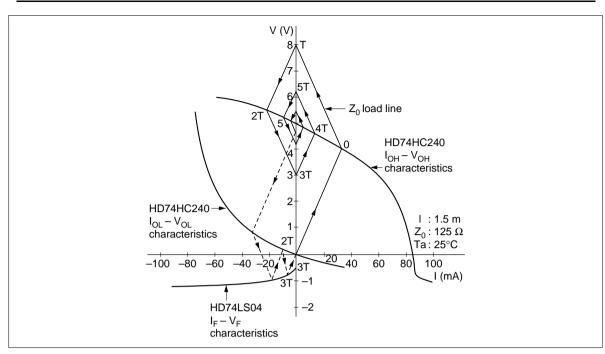

- (1) The rise time and fall time of input waveforms should be 500 ns or less. Since the voltage gain is very high near the threshold, the slightest ripples on the input voltage may cause the output to produce a corresponding waveform, making the output operation unstable.

- (2) The power line should be sufficiently filtered for the device. The input threshold voltage of the IC varies with the supply voltage. A ripple on the power line may change the input threshold, causing the same malfunction as noted in (1) above.

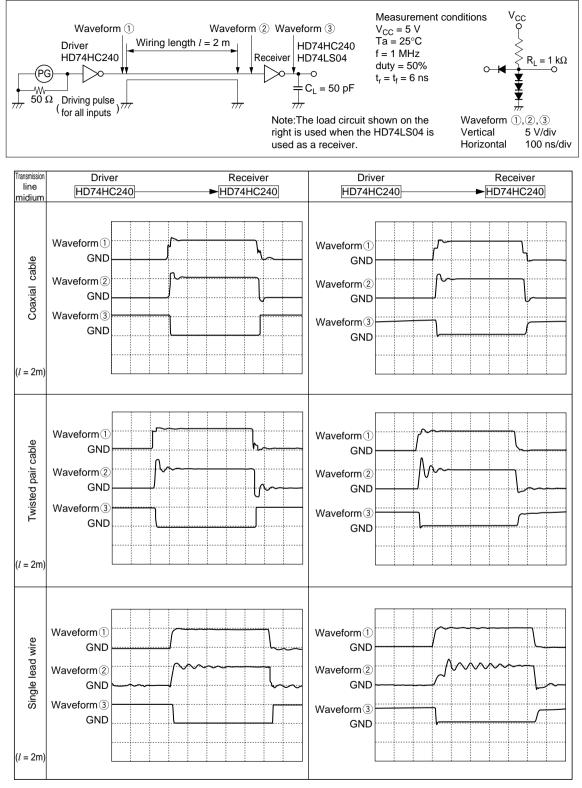

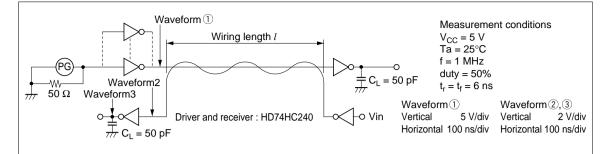

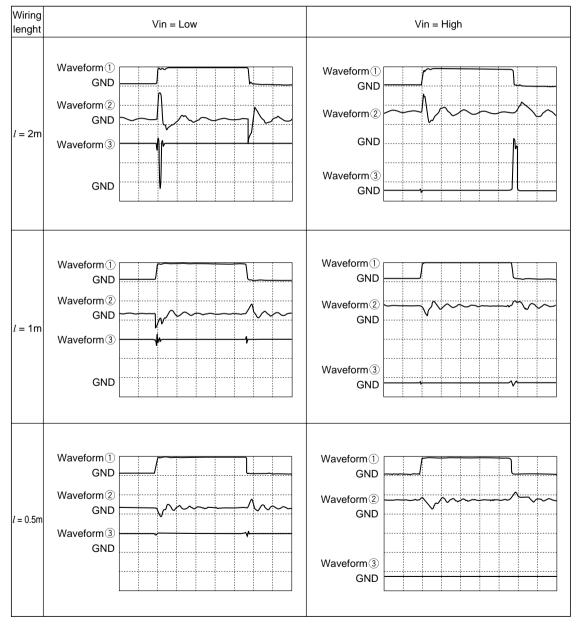

- (3) Beware of a ringing (waveform distortion). Because the switching from "1" level to "0" level on vice versa is very fast, the load capacitance plus the wiring inductance may cause a ringing. Care should be taken to arrange the circuit configuration, PCB layout and wiring appropriately.

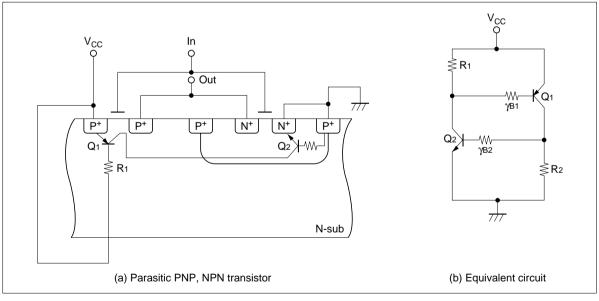

## 1. Input Protection Circuit

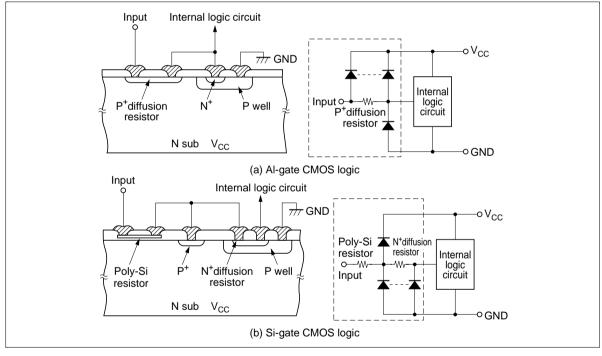

An Si-gate process is applied to Hitachi's high-speed CMOS logic ICs. They have a thinner gate oxide compared to conventional Al-gate CMOS logic ICs and are composed into finer patterns.

Therefore, an input protection circuit is necessary for the gate to be protected from surges at the input pins.

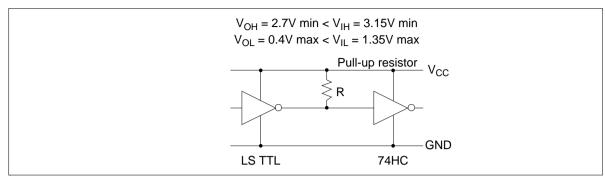

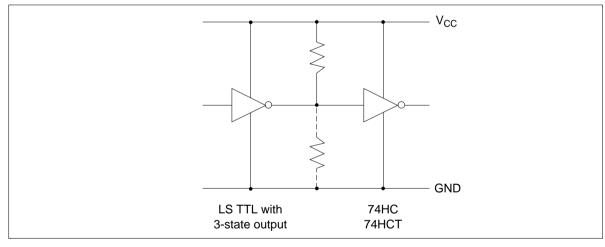

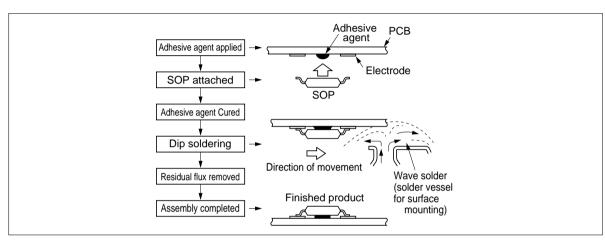

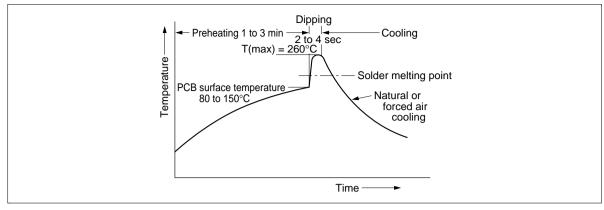

Since Al-gate CMOS logic ICs use a diffusion resistor as the input protection resistor (as shown in Figure 1a), input over-current flows directly to the power supply and the destruction of the protection diode may occur.